# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 64                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 8x8b, 13x10b; D/A 2x10b, 2x12b                                |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 100-TQFP                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f042-gq    |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | Figure 6.5. ADC0 Equivalent Input Circuits                                        | . 78     |

|-----|-----------------------------------------------------------------------------------|----------|

|     | Figure 6.6. Temperature Sensor Transfer Function                                  |          |

|     | Figure 6.7. ADC0 Data Word Example                                                | . 83     |

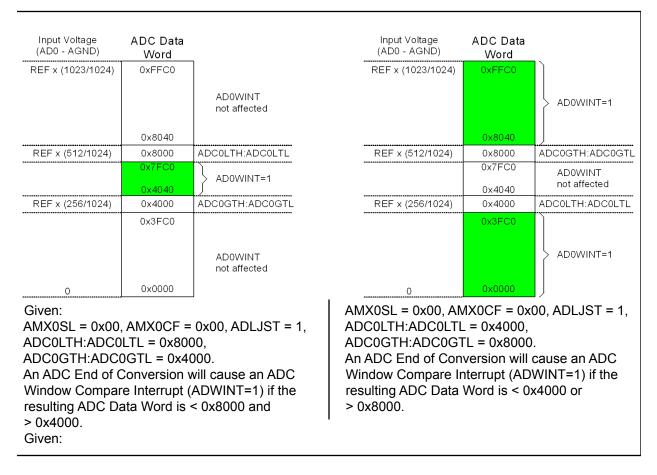

|     | Figure 6.8. 10-Bit ADC0 Window Interrupt Example:                                 |          |

|     | Right Justified Single-Ended Data                                                 | 85       |

|     | Figure 6.9. 10-Bit ADC0 Window Interrupt Example:                                 |          |

|     | Right Justified Differential Data                                                 | 86       |

|     | Figure 6.10. 10-Bit ADC0 Window Interrupt Example:                                |          |

|     | Left Justified Single-Ended Data                                                  | 87       |

|     | Figure 6.11. 10-Bit ADC0 Window Interrupt Example: Left Justified Differential Da |          |

|     | 88                                                                                |          |

| 7   | 8-Bit ADC (ADC2, C8051F040/1/2/3 Only)                                            |          |

| ••  | Figure 7.1. ADC2 Functional Block Diagram                                         | 91       |

|     | Figure 7.2. ADC2 Track and Conversion Example Timing                              |          |

|     | Figure 7.3. ADC2 Equivalent Input Circuit                                         |          |

|     | Figure 7.4. ADC2 Data Word Example                                                |          |

|     | Figure 7.5. ADC Window Compare Examples, Single-Ended Mode                        |          |

|     | Figure 7.6. ADC Window Compare Examples, Differential Mode                        |          |

| 8.  | DACs, 12-Bit Voltage Mode (C8051F040/1/2/3 Only)                                  | 102      |

| 0.  | Figure 8.1. DAC Functional Block Diagram                                          | 105      |

| 9.  | Voltage Reference (C8051F040/2/4/6)                                               |          |

| • • | Figure 9.1. Voltage Reference Functional Block Diagram                            | 113      |

| 10  | Voltage Reference (C8051F041/3/5/7)                                               | -        |

|     | Figure 10.1. Voltage Reference Functional Block Diagram                           | 117      |

| 11. | .Comparators                                                                      |          |

|     | Figure 11.1. Comparator Functional Block Diagram                                  | 121      |

|     | Figure 11.2. Comparator Hysteresis Plot                                           |          |

| 12  | CIP-51 Microcontroller                                                            |          |

|     | Figure 12.1. CIP-51 Block Diagram                                                 | 127      |

|     | Figure 12.2. Memory Map                                                           |          |

|     | Figure 12.3. SFR Page Stack                                                       |          |

|     | Figure 12.4. SFR Page Stack While Using SFR Page 0x0F To Access Port 5            | 137      |

|     | Figure 12.5. SFR Page Stack After ADC2 Window Comparator Interrupt Occurs.        |          |

|     | Figure 12.6. SFR Page Stack Upon PCA Interrupt Occurring During an ADC2 ISR       | <b>R</b> |

|     | 139                                                                               |          |

|     | Figure 12.7. SFR Page Stack Upon Return From PCA Interrupt                        | 140      |

|     | Figure 12.8. SFR Page Stack Upon Return From ADC2 Window Interrupt                | 141      |

| 13  | Reset Sources                                                                     |          |

|     | Figure 13.1. Reset Sources                                                        |          |

|     | Figure 13.2. Reset Timing                                                         | 166      |

| 14  | Oscillators                                                                       |          |

|     | Figure 14.1. Oscillator Diagram                                                   |          |

|     | Figure 14.2. 32.768 kHz External Crystal Example                                  | 177      |

| 15  | Flash Memory                                                                      |          |

|     | Figure 15.1. Flash Program Memory Map and Security Bytes                          | 181      |

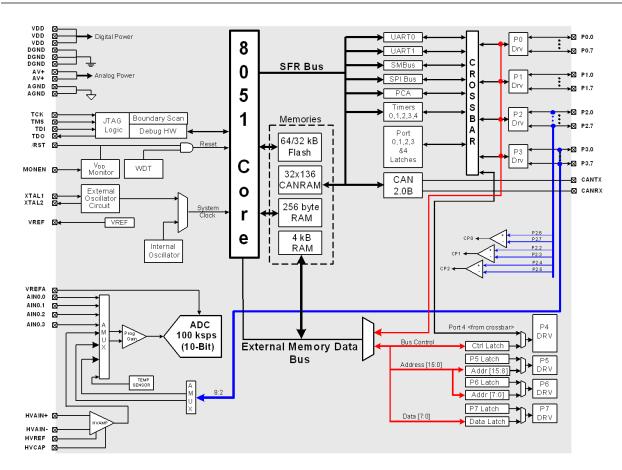

Figure 1.4. C8051F045/7 Block Diagram

### 2. Absolute Maximum Ratings

#### Table 2.1. Absolute Maximum Ratings\*

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Conditions | Min  | Тур | Max                      | Units |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|--------------------------|-------|--|--|--|

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | -55  | —   | 125                      | °C    |  |  |  |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            | -65  | —   | 150                      | °C    |  |  |  |

| Voltage on any Pin (except V <sub>DD</sub> , Port I/O, and JTAG pins) with respect to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | -0.3 |     | V <sub>DD</sub> +<br>0.3 | V     |  |  |  |

| Voltage on any Port I/O Pin, /RST, and JTAG pins with respect to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | -0.3 | _   | 5.8                      | V     |  |  |  |

| Voltage on V <sub>DD</sub> with respect to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | -0.3 | _   | 4.2                      | V     |  |  |  |

| Maximum Total current through V <sub>DD</sub> , AV+, DGND, and AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |      | _   | 800                      | mA    |  |  |  |

| Maximum output current sunk by any Port pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | —    | —   | 100                      | mA    |  |  |  |

| Maximum output current sunk by any other I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | _    | _   | 50                       | mA    |  |  |  |

| Maximum output current sourced by any Port pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |      | —   | 100                      | mA    |  |  |  |

| Maximum output current sourced by any other I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            | —    | —   | 50                       | mA    |  |  |  |

| Maximum output current sourced by any other I/O pin       —       —       50       mA         *Note:       Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.<br>This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.         Due to special I/O design requirements of the High Voltage Difference Amplifier, undue electrical over-voltage stress (i.e., ESD) experienced by these pads may result in impedance degradation of these inputs (HVAIN+ and HVAIN–). For this reason, care should be taken to ensure proper handling and use as typically required to prevent ESD damage to electrostatically sensitive CMOS devices (e.g., static-free workstations, use of |            |      |     |                          |       |  |  |  |

grounding straps, over-voltage protection in end-applications, etc.)

#### **Global DC Electrical Characteristic** 3.

#### **Table 3.1. Global DC Electrical Characteristics**

-40 to +85 °C, 25 MHz System Clock unless otherwise specified.

| Parameter                                                                        | Conditions                                                                                              | Min | Тур             | Max | Units          |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----------------|-----|----------------|

| Analog Supply Voltage <sup>1</sup>                                               |                                                                                                         | 2.7 | 3.0             | 3.6 | V              |

| Analog Supply Current                                                            | Internal REF, ADC, DAC, Com-<br>parators all active                                                     | _   | 1.7             | _   | mA             |

| Analog Supply Current with<br>analog sub-systems inactive                        | Internal REF, ADC, DAC, Com-<br>parators all disabled, oscillator<br>disabled                           |     | 0.2             | —   | μA             |

| Analog-to-Digital Supply<br>Delta ( V <sub>DD</sub> - AV+ )                      |                                                                                                         | _   | _               | 0.5 | V              |

| Digital Supply Voltage                                                           |                                                                                                         | 2.7 | 3.0             | 3.6 | V              |

| Digital Supply Current with<br>CPU active<br>(Normal Mode)                       | $V_{DD}$ = 2.7 V, Clock = 25 MHz<br>$V_{DD}$ = 2.7 V, Clock = 1 MHz<br>$V_{DD}$ = 2.7 V, Clock = 32 kHz |     | 10<br>0.5<br>20 |     | mA<br>mA<br>μA |

| Digital Supply Current with<br>CPU inactive (not accessing<br>Flash) (Idle Mode) | $V_{DD}$ = 2.7 V, Clock = 25 MHz<br>$V_{DD}$ = 2.7 V, Clock = 1 MHz<br>$V_{DD}$ = 2.7 V, Clock = 32 kHz |     | 5<br>0.2<br>10  |     | mA<br>mA<br>μA |

| Digital Supply Current<br>(shutdown) (Stop Mode)                                 | Oscillator not running                                                                                  | _   | 0.2             | _   | μA             |

| Digital Supply RAM Data<br>Retention Voltage                                     |                                                                                                         | _   | 1.5             | _   | V              |

| Specified Operating<br>Temperature Range                                         |                                                                                                         | -40 | _               | +85 | °C             |

| SYSCLK (system clock<br>frequency) <sup>2</sup>                                  |                                                                                                         | 0   | _               | 25  | MHz            |

| Tsysl (SYSCLK low time)                                                          |                                                                                                         | 18  | _               | _   | ns             |

| Tsysh (SYSCLK high time)                                                         |                                                                                                         | 18  |                 |     | ns             |

1. Analog Supply AV+ must be greater than 1 V for  $V_{DD}$  monitor to operate. 2. SYSCLK must be at least 32 kHz to enable debugging.

#### Figure 6.10. 10-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data

#### Table 6.2. 10-Bit ADC0 Electrical Characteristics

$V_{DD}$  = 3.0 V, AV+ = 3.0 V,  $V_{REF}$  = 2.40 V (REFBE = 0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                     | Conditions                         | Min        | Тур             | Max   | Units  |

|-----------------------------------------------|------------------------------------|------------|-----------------|-------|--------|

| DC Accuracy                                   |                                    |            |                 |       |        |

| Resolution                                    |                                    |            | 10              |       | bits   |

| Integral Nonlinearity                         |                                    |            | _               | ±1    | LSB    |

| Differential Nonlinearity                     | Guaranteed Monotonic               |            |                 | ±1    | LSB    |

| Offset Error                                  |                                    |            | 0.2±1           | _     | LSB    |

| Full Scale Error                              | Differential mode                  |            | 0.1±1           | —     | LSB    |

| Offset Temperature Coefficient                |                                    |            | ±0.25           | _     | ppm/°C |

| Dynamic Performance (10 kHz                   | sine-wave input, 0 to 1 dB bel     | ow Full So | cale, 100       | ksps) |        |

| Signal-to-Noise Plus Distortion               |                                    | 59         | —               | —     | dB     |

| Total Harmonic Distortion                     | Up to the 5 <sup>th</sup> harmonic | —          | -70             | —     | dB     |

| Spurious-Free Dynamic Range                   |                                    |            | 80              |       | dB     |

| Conversion Rate                               | 1                                  | I          | 1               |       |        |

| SAR Clock Frequency                           |                                    |            | —               | 2.5   | MHz    |

| Conversion Time in SAR Clocks                 |                                    | 16         | _               | —     | clocks |

| Track/Hold Acquisition Time                   |                                    | 1.5        |                 | _     | μs     |

| Throughput Rate                               |                                    |            |                 | 100   | ksps   |

| Analog Inputs                                 |                                    |            |                 |       |        |

| Input Voltage Range                           | Single-ended operation             | 0          | —               | VREF  | V      |

| Common-mode Voltage Range                     | Differential operation             | AGND       | —               | AV+   | V      |

| Input Capacitance                             |                                    | —          | 10              | —     | pF     |

| Temperature Sensor                            |                                    |            | 1               | I     |        |

| Nonlinearity <sup>1,2</sup>                   |                                    | —          | ±1              | —     | °C     |

| Absolute Accuracy <sup>1,2</sup>              |                                    |            | ±3              | —     | °C     |

| Gain <sup>1,2</sup>                           |                                    | _          | 2.86<br>±0.034  | —     | mV/°C  |

| Offset <sup>1,2</sup>                         | Temp = 0 °C                        | -          | 0.776<br>±0.009 | —     | V      |

| Power Specifications                          | 1                                  | I          | 1               |       |        |

| Power Supply Current<br>(AV+ supplied to ADC) | Operating Mode, 100 ksps           | —          | 450             | 900   | μA     |

| Power Supply Rejection                        |                                    | <u> </u>   | ±0.3            | _     | mV/V   |

#### 7.3. ADC2 Programmable Window Detector

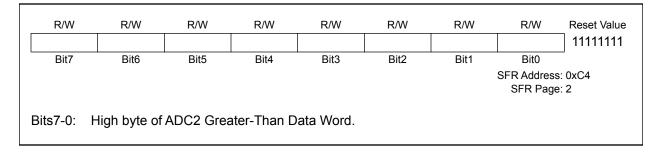

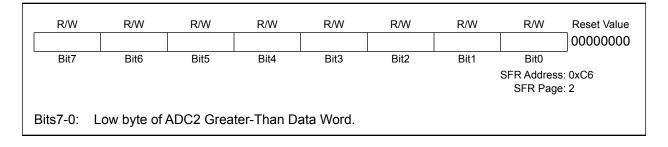

The ADC2 Programmable Window Detector continuously compares the ADC2 output to user-programmed limits, and notifies the system when an out-of-bound condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD2WINT in ADC2CN) can also be used in polled mode. The reference words are loaded into the ADC2 Greater-Than and ADC2 Less-Than registers (ADC2GT and ADC2LT). Notice that the window detector flag can be asserted when the measured data is inside or outside the user-programmed limits, depending on the programming of the ADC2GT and ADC2LT registers.

#### SFR Definition 7.6. ADC2GT: ADC2 Greater-Than Data

#### SFR Definition 7.7. ADC2LT: ADC2 Less-Than Data

#### 7.3.1. Window Detector in Single-Ended Mode

Figure 7.5 shows two example window comparisons for Single-ended mode, with ADC2LT = 0x20 and ADC2GT = 0x10. In Single-ended mode, the codes vary from 0 to VREF x (255/256) and are represented as 8-bit unsigned integers. In the left example, an AD2WINT interrupt will be generated if the ADC2 conversion word (ADC2) is within the range defined by ADC2GT and ADC2LT (if 0x10 < ADC2 < 0x20). In the right example, and AD2WINT interrupt will be generated if ADC2 is outside of the range defined by ADC2GT and ADC2LT (if ADC2 < 0x20). In the right example, and AD2WINT interrupt will be generated if ADC2 is outside of the range defined by ADC2GT and ADC2LT (if ADC2 < 0x10 or ADC2 > 0x20).

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 3/4             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/4             |

| NOP                  | No operation                                        | 1     | 1               |

#### Table 12.1. CIP-51 Instruction Set Summary (Continued)

Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 64 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

#### SFR Definition 12.8. PSW: Program Status Word

| R/W      | R/W                                                                                                                                                          | R/W                                                                                                                                                                                                                                               | R/W                                                                                                      | R/W                                                                                                                   | R/W                                                                                                            | R/W           | R/W                                | Reset Value           |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------|------------------------------------|-----------------------|--|

| CY       | AC                                                                                                                                                           | F0                                                                                                                                                                                                                                                | RS1                                                                                                      | RS0                                                                                                                   | OV                                                                                                             | F1            | PARITY                             | 0000000               |  |

| Bit7     | Bit6                                                                                                                                                         | Bit5                                                                                                                                                                                                                                              | Bit4                                                                                                     | Bit3                                                                                                                  | Bit2                                                                                                           | Bit1          | Bit0                               | Bit<br>Addressable    |  |

|          |                                                                                                                                                              |                                                                                                                                                                                                                                                   |                                                                                                          |                                                                                                                       |                                                                                                                |               | SFR Address<br>SFR Page            | : 0xD0<br>: All Pages |  |

| Bit7:    | CY: Carry I                                                                                                                                                  | -lag.                                                                                                                                                                                                                                             |                                                                                                          |                                                                                                                       |                                                                                                                |               |                                    |                       |  |

|          |                                                                                                                                                              | •                                                                                                                                                                                                                                                 | e last arithmet                                                                                          | tic operatio                                                                                                          | n resulted                                                                                                     | in a carry (a | ddition) or a                      | borrow                |  |

|          | •                                                                                                                                                            | ,                                                                                                                                                                                                                                                 | red to 0 by all                                                                                          | other arith                                                                                                           | metic oper                                                                                                     | ations.       |                                    |                       |  |

| Bit6:    |                                                                                                                                                              | ry Carry Fla                                                                                                                                                                                                                                      | 0                                                                                                        |                                                                                                                       |                                                                                                                |               |                                    |                       |  |

|          |                                                                                                                                                              |                                                                                                                                                                                                                                                   | last arithmeti                                                                                           |                                                                                                                       |                                                                                                                |               |                                    |                       |  |

|          |                                                                                                                                                              |                                                                                                                                                                                                                                                   | nigh order nib                                                                                           | ble. It is clo                                                                                                        | eared to 0                                                                                                     | by all other  | arithmetic o                       | perations.            |  |

| Bit5:    | F0: User Fl                                                                                                                                                  | 0                                                                                                                                                                                                                                                 |                                                                                                          |                                                                                                                       |                                                                                                                |               |                                    |                       |  |

|          |                                                                                                                                                              |                                                                                                                                                                                                                                                   | le, general pu                                                                                           | urpose flag                                                                                                           | for use un                                                                                                     | der software  | e control.                         |                       |  |

| Bits4-3: |                                                                                                                                                              | Register Ba                                                                                                                                                                                                                                       |                                                                                                          | 1                                                                                                                     |                                                                                                                |               | _                                  |                       |  |

|          | These bits select which register bank is used during register accesses.                                                                                      |                                                                                                                                                                                                                                                   |                                                                                                          |                                                                                                                       |                                                                                                                |               |                                    |                       |  |

|          |                                                                                                                                                              |                                                                                                                                                                                                                                                   |                                                                                                          |                                                                                                                       |                                                                                                                |               |                                    |                       |  |

|          | RS1                                                                                                                                                          | RS0 R                                                                                                                                                                                                                                             | egister Bank                                                                                             | Addr                                                                                                                  | ess                                                                                                            |               |                                    |                       |  |

|          | <b>RS1</b><br>0                                                                                                                                              | <b>RS0 R</b>                                                                                                                                                                                                                                      | <b>egister Bank</b><br>0                                                                                 | Addr<br>0x00–                                                                                                         |                                                                                                                |               |                                    |                       |  |

|          |                                                                                                                                                              |                                                                                                                                                                                                                                                   | -                                                                                                        |                                                                                                                       | 0x07                                                                                                           |               |                                    |                       |  |

|          | 0                                                                                                                                                            | 0                                                                                                                                                                                                                                                 | 0                                                                                                        | 0x00-                                                                                                                 | 0x07<br>0x0F                                                                                                   |               |                                    |                       |  |

|          | 0                                                                                                                                                            | 0 1                                                                                                                                                                                                                                               | 0                                                                                                        | 0x00-<br>0x08-                                                                                                        | 0x07<br>0x0F<br>0x17                                                                                           |               |                                    |                       |  |

|          | 0<br>0<br>1                                                                                                                                                  | 0<br>1<br>0                                                                                                                                                                                                                                       | 0<br>1<br>2                                                                                              | 0x00-<br>0x08-<br>0x10-                                                                                               | 0x07<br>0x0F<br>0x17                                                                                           |               |                                    |                       |  |

| Bit2:    | 0<br>0<br>1<br>1<br>0V: Overflo                                                                                                                              | 0<br>1<br>0<br>1<br>2<br>w Flag.                                                                                                                                                                                                                  | 0<br>1<br>2<br>3                                                                                         | 0x00-<br>0x08-<br>0x10-<br>0x18-                                                                                      | 0x07<br>0x0F<br>0x17<br>0x1F                                                                                   |               |                                    |                       |  |

| Bit2:    | 0<br>0<br>1<br>1<br>OV: Overflo<br>This bit is s                                                                                                             | 0<br>1<br>0<br>1<br>2<br>2<br>2<br>3<br>2<br>3<br>2<br>3<br>3<br>2<br>3<br>3<br>2<br>3<br>3<br>3<br>3<br>3<br>3                                                                                                                                   | 0<br>1<br>2<br>3<br>er the followin                                                                      | 0x00-<br>0x08-<br>0x10-<br>0x18-<br>g circumst                                                                        | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:                                                                         |               |                                    |                       |  |

| Bit2:    | 0<br>0<br>1<br>1<br>OV: Overflo<br>This bit is s<br>• An AD                                                                                                  | 0<br>1<br>0<br>1<br>bw Flag.<br>to 1 unde<br>D, ADDC, o                                                                                                                                                                                           | 0<br>1<br>2<br>3<br>er the followin<br>r SUBB instru                                                     | 0x00–<br>0x08–<br>0x10–<br>0x18–<br>og circumst                                                                       | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:<br>ses a sign-o                                                         |               |                                    |                       |  |

| Bit2:    | 0<br>0<br>1<br>1<br>OV: Overflo<br>This bit is s<br>• An AD<br>• A MUL                                                                                       | 0<br>1<br>0<br>1<br>Dw Flag.<br>D, ADDC, o<br>instruction                                                                                                                                                                                         | 0<br>1<br>2<br>3<br>er the followin<br>r SUBB instru<br>results in an                                    | 0x00-<br>0x08-<br>0x10-<br>0x18-<br>g circumst<br>uction caus<br>overflow (r                                          | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:<br>ses a sign-c<br>esult is gre                                         |               |                                    |                       |  |

| Bit2:    | 0<br>0<br>1<br>1<br>OV: Overflo<br>This bit is s<br>• An AD<br>• A MUL<br>• A DIV                                                                            | 0<br>1<br>0<br>1<br>ow Flag.<br>et to 1 unde<br>D, ADDC, o<br>instruction<br>instruction                                                                                                                                                          | 0<br>1<br>2<br>3<br>er the followin<br>r SUBB instru<br>results in an<br>causes a divid                  | 0x00-<br>0x08-<br>0x10-<br>0x18-<br>g circumst<br>uction caus<br>overflow (r<br>de-by-zero                            | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:<br>ses a sign-c<br>result is gre<br>condition.                          | eater than 28 | 55).                               |                       |  |

| Bit2:    | 0<br>0<br>1<br>1<br>OV: Overflo<br>This bit is s<br>• An AD<br>• A MUL<br>• A DIV<br>The OV bit                                                              | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                              | 0<br>1<br>2<br>3<br>er the followin<br>r SUBB instru<br>results in an                                    | 0x00-<br>0x08-<br>0x10-<br>0x18-<br>g circumst<br>uction caus<br>overflow (r<br>de-by-zero                            | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:<br>ses a sign-c<br>result is gre<br>condition.                          | eater than 28 | 55).                               | in all                |  |

| -        | 0<br>0<br>1<br>1<br>0V: Overflo<br>This bit is s<br>• An AD<br>• A MUL<br>• A DIV<br>The OV bit<br>other cases                                               | 0<br>1<br>0<br>1<br>Dow Flag.<br>Det to 1 under<br>D, ADDC, or<br>instruction of<br>instruction of<br>is cleared to<br>s.                                                                                                                         | 0<br>1<br>2<br>3<br>er the followin<br>r SUBB instru<br>results in an<br>causes a divid                  | 0x00-<br>0x08-<br>0x10-<br>0x18-<br>g circumst<br>uction caus<br>overflow (r<br>de-by-zero                            | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:<br>ses a sign-c<br>result is gre<br>condition.                          | eater than 28 | 55).                               | in all                |  |

| -        | 0<br>0<br>1<br>1<br>0V: Overflo<br>This bit is s<br>• An AD<br>• A MUL<br>• A DIV<br>The OV bit<br>other cases<br>F1: User Fl                                | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                              | 0<br>1<br>2<br>3<br>er the followin<br>r SUBB instru<br>results in an<br>causes a divid<br>o 0 by the AD | 0x00-<br>0x08-<br>0x10-<br>0x18-<br>eg circumst<br>uction caus<br>overflow (r<br>de-by-zero<br>D, ADDC,               | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:<br>ances:<br>ess a sign-o<br>esult is gre<br>condition.<br>SUBB, MU     | eater than 25 | 55).<br>instructions               | in all                |  |

| Bit1:    | 0<br>0<br>1<br>1<br>0V: Overflo<br>This bit is s<br>• An AD<br>• A MUL<br>• A DIV<br>The OV bit<br>other cases<br>F1: User FI<br>This is a bit               | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>2<br>3<br>er the followin<br>r SUBB instru<br>results in an<br>causes a divid                  | 0x00-<br>0x08-<br>0x10-<br>0x18-<br>eg circumst<br>uction caus<br>overflow (r<br>de-by-zero<br>D, ADDC,               | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:<br>ances:<br>ess a sign-o<br>esult is gre<br>condition.<br>SUBB, MU     | eater than 25 | 55).<br>instructions               | in all                |  |

| -        | 0<br>0<br>1<br>1<br>0V: Overflo<br>This bit is s<br>• An AD<br>• A MUL<br>• A DIV<br>The OV bit<br>other cases<br>F1: User FI<br>This is a bir<br>PARITY: Pa | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                    | 0<br>1<br>2<br>3<br>er the followin<br>r SUBB instru<br>results in an<br>causes a divid<br>o 0 by the AD | 0x00-<br>0x08-<br>0x10-<br>0x18-<br>g circumst<br>uction caus<br>overflow (r<br>de-by-zero<br>D, ADDC,<br>urpose flag | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:<br>ees a sign-c<br>esult is gre<br>condition.<br>SUBB, MU<br>for use un | eater than 25 | 55).<br>instructions<br>e control. |                       |  |

| Bit1:    | 0<br>0<br>1<br>1<br>0V: Overflo<br>This bit is s<br>• An AD<br>• A MUL<br>• A DIV<br>The OV bit<br>other cases<br>F1: User FI<br>This is a bir<br>PARITY: Pa | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                    | 0<br>1<br>2<br>3<br>er the followin<br>r SUBB instru<br>results in an<br>causes a divid<br>o 0 by the AD | 0x00-<br>0x08-<br>0x10-<br>0x18-<br>g circumst<br>uction caus<br>overflow (r<br>de-by-zero<br>D, ADDC,<br>urpose flag | 0x07<br>0x0F<br>0x17<br>0x1F<br>ances:<br>ees a sign-c<br>esult is gre<br>condition.<br>SUBB, MU<br>for use un | eater than 25 | 55).<br>instructions<br>e control. |                       |  |

| R/W   | R/W                                                                                                                      | R/W           | R/W           | R/W           | R/W            | R/W         | R/W         | Reset Value  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|----------------|-------------|-------------|--------------|--|--|

| -     | PCP2                                                                                                                     | PCP1          | PCP0          | PPCA0         | PWADC0         | PSMB0       | PSPI0       | 00000000     |  |  |

| Bit7  | Bit6                                                                                                                     | Bit5          | Bit4          | Bit3          | Bit2           | Bit1        | Bit0        |              |  |  |

|       |                                                                                                                          |               |               |               |                |             | SFR Address |              |  |  |

|       |                                                                                                                          |               |               |               |                |             | SFR Page    | e: All Pages |  |  |

| Bit7: | Reserved.                                                                                                                |               |               |               |                |             |             |              |  |  |

| Bit6: | PCP2: Com                                                                                                                | oarator2 (C   | P2) Interrur  | ot Priority C | Control        |             |             |              |  |  |

|       | This bit sets                                                                                                            |               |               |               |                |             |             |              |  |  |

|       | 0: CP2 inter                                                                                                             |               |               | •             |                |             |             |              |  |  |

|       | 1: CP2 inter                                                                                                             | •             |               |               |                |             |             |              |  |  |

| Bit5: | PCP1: Com                                                                                                                | parator1 (C   | P1) Interrup  | ot Priority C | ontrol.        |             |             |              |  |  |

|       | This bit sets                                                                                                            |               |               |               |                |             |             |              |  |  |

|       | 0: CP1 inter                                                                                                             |               |               |               |                |             |             |              |  |  |

|       | 1: CP1 inter                                                                                                             | •             | • • •         |               |                |             |             |              |  |  |

| Bit4: | PCP0: Com                                                                                                                |               |               |               | control.       |             |             |              |  |  |

|       | This bit sets the priority of the CP0 interrupt.                                                                         |               |               |               |                |             |             |              |  |  |

|       | 0: CP0 interrupt set to low priority level.<br>1: CP0 interrupt set to high priority level.                              |               |               |               |                |             |             |              |  |  |

|       |                                                                                                                          | •             | • • •         |               |                |             | 1           |              |  |  |

| Bit3: |                                                                                                                          | •             |               |               | ) Interrupt Pr | iority Cont | rol.        |              |  |  |

|       | This bit sets<br>0: PCA0 inte                                                                                            |               |               |               |                |             |             |              |  |  |

|       | 1: PCA0 inte                                                                                                             | •             |               |               |                |             |             |              |  |  |

| Bit2: |                                                                                                                          | •             | • •           |               | ot Priority Co | ntrol       |             |              |  |  |

| DILZ. | This bit sets                                                                                                            |               |               |               |                | muor.       |             |              |  |  |

|       | 0: ADC0 Wir                                                                                                              |               |               |               |                |             |             |              |  |  |

|       | 1: ADC0 Wir                                                                                                              |               |               |               |                |             |             |              |  |  |

| Bit1: |                                                                                                                          |               | •             | • • •         |                | ority Contr | ol.         |              |  |  |

|       | PSMB0: System Management Bus (SMBus0) Interrupt Priority Control.<br>This bit sets the priority of the SMBus0 interrupt. |               |               |               |                |             |             |              |  |  |

|       | 0: SMBus interrupt set to low priority level.                                                                            |               |               |               |                |             |             |              |  |  |

|       | 1: SMBus in                                                                                                              | terrupt set f | to high prior | rity level.   |                |             |             |              |  |  |

| Bit0: | PSPI0: Seria                                                                                                             | al Periphera  | al Interface  | (SPI0) Inter  | rrupt Priority | Control.    |             |              |  |  |

|       | This bit sets                                                                                                            |               |               | •             |                |             |             |              |  |  |

|       | 0: SPI0 inter                                                                                                            | •             |               |               |                |             |             |              |  |  |

|       | 1: SPI0 inter                                                                                                            | rupt set to   | high priority | level.        |                |             |             |              |  |  |

|       |                                                                                                                          |               |               |               |                |             |             |              |  |  |

|       |                                                                                                                          |               |               |               |                |             |             |              |  |  |

|       |                                                                                                                          |               |               |               |                |             |             |              |  |  |

#### SFR Definition 12.15. EIP1: Extended Interrupt Priority 1

#### 13.7.1. Enable/Reset WDT

The watchdog timer is both enabled and reset by writing 0xA5 to the WDTCN register. The user's application software should include periodic writes of 0xA5 to WDTCN as needed to prevent a watchdog timer overflow. The WDT is enabled and reset as a result of any system reset.

#### 13.7.2. Disable WDT

Writing 0xDE followed by 0xAD to the WDTCN register disables the WDT. The following code segment illustrates disabling the WDT:

```

CLR EA ; disable all interrupts

MOV WDTCN,#0DEh ; disable software watchdog timer

MOV WDTCN,#0ADh

SETB EA ; re-enable interrupts

```

The writes of 0xDE and 0xAD must occur within 4 clock cycles of each other, or the disable operation is ignored. Interrupts should be disabled during this procedure to avoid delay between the two writes.

#### 13.7.3. Disable WDT Lockout

Writing 0xFF to WDTCN locks out the disable feature. Once locked out, the disable operation is ignored until the next system reset. Writing 0xFF does not enable or reset the watchdog timer. Applications always intending to use the watchdog should write 0xFF to WDTCN in the initialization code.

#### 13.7.4. Setting WDT Interval

WDTCN.[2:0] control the watchdog timeout interval. The interval is given by the following equation:

$4^{3 + WDTCN[2-0]} \times T_{sysclk}$ ; where  $T_{sysclk}$  is the system clock period.

For a 3 MHz system clock, this provides an interval range of 0.021 ms to 349.5 ms. WDTCN.7 must be logic 0 when setting this interval. Reading WDTCN returns the programmed interval. WDTCN.[2:0] reads 111b after a system reset.

### 14. Oscillators

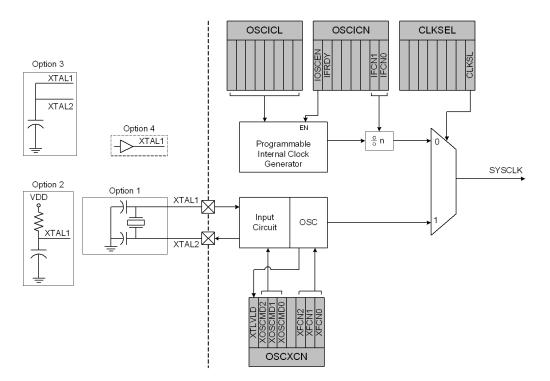

Figure 14.1. Oscillator Diagram

#### 14.1. Programmable Internal Oscillator

All C8051F04x devices include a programmable internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be programmed via the OSCICL register as defined by SFR Definition 14.1. OSCICL is factory calibrated to obtain a 24.5 MHz frequency.

Electrical specifications for the precision internal oscillator are given in Table 14.1 on page 175. The programmed internal oscillator frequency must not exceed 25 MHz. The system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN.

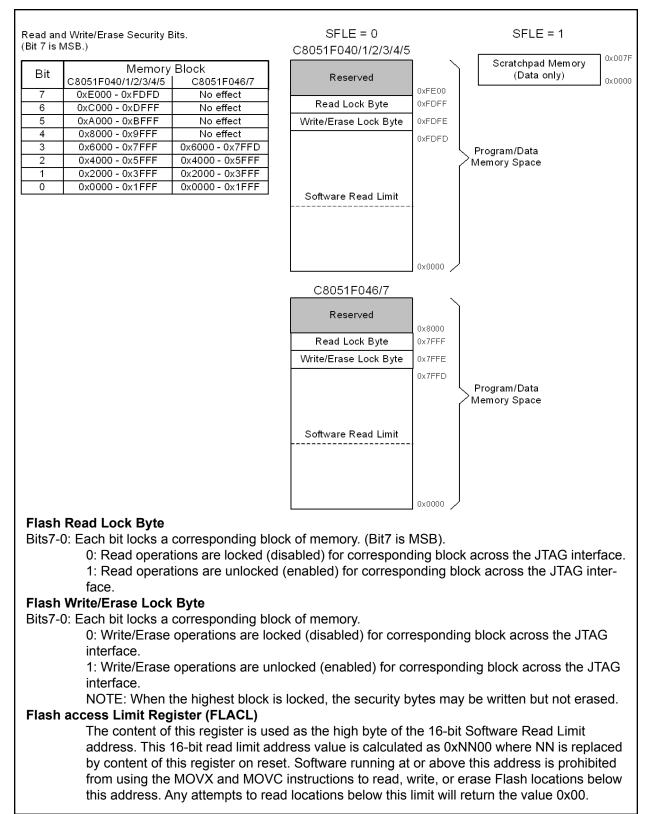

#### Figure 15.1. Flash Program Memory Map and Security Bytes

| R/W      | R/W                     | R/W         | R/W        | R/W       | R/W  | R/W  | R/W                     | Reset Value |

|----------|-------------------------|-------------|------------|-----------|------|------|-------------------------|-------------|

| EAS1     | EAS0                    | ERW3        | EWR2       | EWR1      | EWR0 | EAH1 | EAH0                    | 11111111    |

| Bit7     | Bit6                    | Bit5        | Bit4       | Bit3      | Bit2 | Bit1 | Bit0                    | _           |

|          |                         |             |            |           |      |      | SFR Address<br>SFR Page |             |

| Bits7-6: | EAS1-0: EM              | IF Address  | Setup Time | e Bits.   |      |      |                         |             |

|          | 00: Address             | setup time  | = 0 SYSCL  | K cycles. |      |      |                         |             |

|          | 01: Address             | setup time  | = 1 SYSCL  | K cycle.  |      |      |                         |             |

|          | 10: Address             |             |            |           |      |      |                         |             |

|          | 11: Address             | •           |            |           |      |      |                         |             |

| Bits5-2: | EWR3-0: EN              | -           |            |           |      |      |                         |             |

|          | 0000: /WR a             | •           |            |           |      |      |                         |             |

|          | 0001: /WR a             | •           |            |           |      |      |                         |             |

|          | 0010: /WR a             | •           |            |           |      |      |                         |             |

|          | 0011: /WR a             | •           |            |           |      |      |                         |             |

|          | 0100: /WR a             | •           |            |           |      |      |                         |             |

|          | 0101: /WR a 0110: /WR a | •           |            |           |      |      |                         |             |

|          | 0110: /WR a             | •           |            |           |      |      |                         |             |

|          | 1000: /WR a             | •           |            |           |      |      |                         |             |

|          | 1000: /WR a             | •           |            |           |      |      |                         |             |

|          | 1010: /WR a             | •           |            |           |      |      |                         |             |

|          | 1011: /WR a             | •           |            |           |      |      |                         |             |

|          | 1100: /WR a             | •           |            |           |      |      |                         |             |

|          | 1101: /WR a             | •           |            |           |      |      |                         |             |

|          | 1110: /WR a             | •           |            |           |      |      |                         |             |

|          | 1111: /WR a             |             |            |           |      |      |                         |             |

| Bits1-0: | EAH1-0: EM              | IIF Address | Hold Time  | Bits.     | -    |      |                         |             |

|          | 00: Address             | hold time = | 0 SYSCLK   | cycles.   |      |      |                         |             |

|          | 01: Address             | hold time = | 1 SYSCLK   | Ccycle.   |      |      |                         |             |

|          | 10: Address             |             |            |           |      |      |                         |             |

|          | 11: Address             | hold time = | 3 SYSCLK   | cycles.   |      |      |                         |             |

|          |                         |             |            |           |      |      |                         |             |

|          |                         |             |            |           |      |      |                         |             |

#### SFR Definition 16.3. EMI0TC: External Memory Timing Control

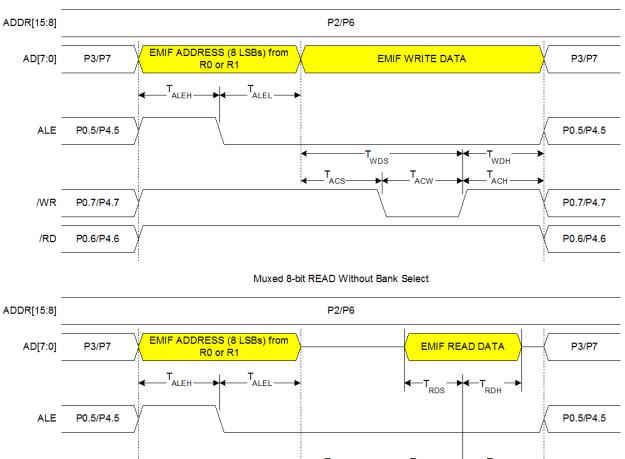

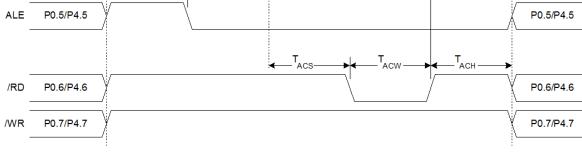

#### 16.6.2.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = '001' or '011'.

Muxed 8-bit WRITE Without Bank Select

#### Figure 16.8. Multiplexed 8-bit MOVX without Bank Select Timing

a digital input by setting P3MDOUT.7 to a logic 0, which selects open-drain output mode, and P3.7 to a logic 1, which disables the low-side output driver.

If the Port pin has been assigned to a digital peripheral by the Crossbar and that pin functions as an input (for example RX0, the UART0 receive pin), then the output drivers on that pin are automatically disabled.

#### 17.1.4. Weak Pullups

By default, each Port pin has an internal weak pullup device enabled which provides a resistive connection (about 100 k $\Omega$ ) between the pin and V<sub>DD</sub>. The weak pullup devices can be globally disabled by writing a logic 1 to the Weak Pullup Disable bit, (WEAKPUD, XBR2.7). The weak pullup is automatically deactivated on any pin that is driving a logic 0; that is, an output pin will not contend with its own pullup device. The weak pullup device can also be explicitly disabled on Ports 1, 2, and 3 pin by configuring the pin as an Analog Input, as described below.

#### 17.1.5. Configuring Port 1, 2, and 3 Pins as Analog Inputs

The pins on Port 1 can serve as analog inputs to the ADC2 analog MUX (C8051F040/1/2/3 only), the pins on Port 2 can serve as analog inputs to the Comparators, and the pins on Port 3 can serve as inputs to ADC0. A Port pin is configured as an Analog Input by writing a logic 0 to the associated bit in the PnMDIN registers. All Port pins default to a Digital Input mode. Configuring a Port pin as an analog input:

- Disables the digital input path from the pin. This prevents additional power supply current from being drawn when the voltage at the pin is near V<sub>DD</sub> / 2. A read of the Port Data bit will return a logic 0 regardless of the voltage at the Port pin.