# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 64                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 8x8b, 13x10b; D/A 2x10b, 2x12b                                |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 100-TQFP                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f042-gqr   |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### List of Figures

| 1. | System Overview                                                                          |     |

|----|------------------------------------------------------------------------------------------|-----|

|    | Figure 1.1. C8051F040/2 Block Diagram                                                    | 21  |

|    | Figure 1.2. C8051F041/3 Block Diagram                                                    | 22  |

|    | Figure 1.3. C8051F044/6 Block Diagram                                                    | 23  |

|    | Figure 1.4. C8051F045/7 Block Diagram                                                    | 24  |

|    | Figure 1.5. Comparison of Peak MCU Execution Speeds                                      | 25  |

|    | Figure 1.6. On-Board Clock and Reset                                                     | 26  |

|    | Figure 1.7. On-Chip Memory Map                                                           | 27  |

|    | Figure 1.8. Development/In-System Debug Diagram                                          | 28  |

|    | Figure 1.9. Digital Crossbar Diagram                                                     | 29  |

|    | Figure 1.10. PCA Block Diagram                                                           | 30  |

|    | Figure 1.11. CAN Controller Diagram                                                      | 31  |

|    | Figure 1.12. 10/12-Bit ADC Block Diagram                                                 | 32  |

|    | Figure 1.13. 8-Bit ADC Diagram                                                           | 33  |

|    | Figure 1.14. Comparator and DAC Diagram                                                  | 34  |

|    | Absolute Maximum Ratings                                                                 |     |

|    | Global DC Electrical Characteristic                                                      |     |

| 4. | Pinout and Package Definitions                                                           |     |

|    | Figure 4.1. TQFP-100 Pinout Diagram                                                      |     |

|    | Figure 4.2. TQFP-100 Package Drawing                                                     |     |

|    | Figure 4.3. TQFP-64 Pinout Diagram                                                       |     |

|    | Figure 4.4. TQFP-64 Package Drawing                                                      | 46  |

| 5. | 12-Bit ADC (ADC0, C8051F040/1 Only)                                                      |     |

|    | Figure 5.1. 12-Bit ADC0 Functional Block Diagram                                         |     |

|    | Figure 5.2. Analog Input Diagram                                                         |     |

|    | Figure 5.3. High Voltage Difference Amplifier Functional Diagram                         |     |

|    | Figure 5.4. 12-Bit ADC Track and Conversion Example Timing                               |     |

|    | Figure 5.5. ADC0 Equivalent Input Circuits                                               |     |

|    | Figure 5.6. Temperature Sensor Transfer Function                                         |     |

|    | Figure 5.7. ADC0 Data Word Example                                                       | 61  |

|    | Figure 5.8. 12-Bit ADC0 Window Interrupt Example:                                        |     |

|    | Right Justified Single-Ended Data                                                        | 63  |

|    | Figure 5.9. 12-Bit ADC0 Window Interrupt Example:                                        |     |

|    | Right Justified Differential Data                                                        | 64  |

|    | Figure 5.10. 12-Bit ADC0 Window Interrupt Example:                                       |     |

|    | Left Justified Single-Ended Data                                                         |     |

|    | Figure 5.11. 12-Bit ADC0 Window Interrupt Example: Left Justified Differential Dat<br>66 | a.  |

| 6. | 10-Bit ADC (ADC0, C8051F042/3/4/5/6/7 Only)                                              | • • |

|    | Figure 6.1. 10-Bit ADC0 Functional Block Diagram                                         |     |

|    | Figure 6.2. Analog Input Diagram                                                         |     |

|    | Figure 6.3. High Voltage Difference Amplifier Functional Diagram                         |     |

|    | Figure 6.4. 10-Bit ADC Track and Conversion Example Timing                               | 77  |

|     | Figure 6.5. ADC0 Equivalent Input Circuits                                        | . 78     |

|-----|-----------------------------------------------------------------------------------|----------|

|     | Figure 6.6. Temperature Sensor Transfer Function                                  |          |

|     | Figure 6.7. ADC0 Data Word Example                                                | . 83     |

|     | Figure 6.8. 10-Bit ADC0 Window Interrupt Example:                                 |          |

|     | Right Justified Single-Ended Data                                                 | 85       |

|     | Figure 6.9. 10-Bit ADC0 Window Interrupt Example:                                 |          |

|     | Right Justified Differential Data                                                 | 86       |

|     | Figure 6.10. 10-Bit ADC0 Window Interrupt Example:                                |          |

|     | Left Justified Single-Ended Data                                                  | 87       |

|     | Figure 6.11. 10-Bit ADC0 Window Interrupt Example: Left Justified Differential Da |          |

|     | 88                                                                                |          |

| 7   | 8-Bit ADC (ADC2, C8051F040/1/2/3 Only)                                            |          |

| ••  | Figure 7.1. ADC2 Functional Block Diagram                                         | 91       |

|     | Figure 7.2. ADC2 Track and Conversion Example Timing                              |          |

|     | Figure 7.3. ADC2 Equivalent Input Circuit                                         |          |

|     | Figure 7.4. ADC2 Data Word Example                                                |          |

|     | Figure 7.5. ADC Window Compare Examples, Single-Ended Mode                        |          |

|     | Figure 7.6. ADC Window Compare Examples, Differential Mode                        |          |

| 8.  | DACs, 12-Bit Voltage Mode (C8051F040/1/2/3 Only)                                  | 102      |

| 0.  | Figure 8.1. DAC Functional Block Diagram                                          | 105      |

| 9.  | Voltage Reference (C8051F040/2/4/6)                                               |          |

| ••• | Figure 9.1. Voltage Reference Functional Block Diagram                            | 113      |

| 10  | Voltage Reference (C8051F041/3/5/7)                                               | -        |

|     | Figure 10.1. Voltage Reference Functional Block Diagram                           | 117      |

| 11. | .Comparators                                                                      |          |

|     | Figure 11.1. Comparator Functional Block Diagram                                  | 121      |

|     | Figure 11.2. Comparator Hysteresis Plot                                           |          |

| 12  | CIP-51 Microcontroller                                                            |          |

|     | Figure 12.1. CIP-51 Block Diagram                                                 | 127      |

|     | Figure 12.2. Memory Map                                                           |          |

|     | Figure 12.3. SFR Page Stack                                                       |          |

|     | Figure 12.4. SFR Page Stack While Using SFR Page 0x0F To Access Port 5            | 137      |

|     | Figure 12.5. SFR Page Stack After ADC2 Window Comparator Interrupt Occurs.        |          |

|     | Figure 12.6. SFR Page Stack Upon PCA Interrupt Occurring During an ADC2 ISR       | <b>R</b> |

|     | 139                                                                               |          |

|     | Figure 12.7. SFR Page Stack Upon Return From PCA Interrupt                        | 140      |

|     | Figure 12.8. SFR Page Stack Upon Return From ADC2 Window Interrupt                | 141      |

| 13  | Reset Sources                                                                     |          |

|     | Figure 13.1. Reset Sources                                                        |          |

|     | Figure 13.2. Reset Timing                                                         | 166      |

| 14  | Oscillators                                                                       |          |

|     | Figure 14.1. Oscillator Diagram                                                   |          |

|     | Figure 14.2. 32.768 kHz External Crystal Example                                  | 177      |

| 15  | Flash Memory                                                                      |          |

|     | Figure 15.1. Flash Program Memory Map and Security Bytes                          | 181      |

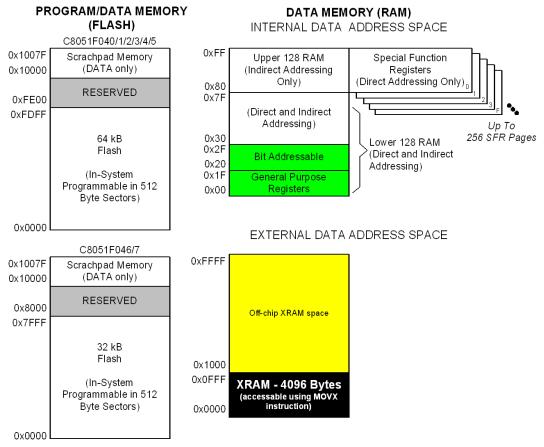

### 1.2. On-Chip Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The CIP-51 SFR address space contains up to 256 *SFR Pages*. In this way, the CIP-51 MCU can accommodate the many SFRs required to control and configure the various peripherals featured on the device. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

The CIP-51 in the C8051F04x MCUs additionally has an on-chip 4 kB RAM block and an external memory interface (EMIF) for accessing off-chip data memory or memory-mapped peripherals. The on-chip 4 byte block can be addressed over the entire 64 kB external data memory address range (overlapping 4 kB boundaries). External data memory address space can be mapped to on-chip memory only, off-chip memory only, or a combination of the two (addresses up to 4 kB directed to on-chip, above 4 kB directed to EMIF). The EMIF is also configurable for multiplexed or non-multiplexed address/data lines.

The MCU's program memory consists of 64 kB (C8051F040/1/2/3/4/5) or 32 kB (C8051F046/7) of Flash. This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. The 512 bytes from addresses 0xFE00 to 0xFFFF are reserved for the 64 kB devices. There is also a single 128 byte sector at address 0x10000 to 0x1007F, which may be useful as a small table for software constants. See Figure 1.7 for the MCU system memory map.

Figure 1.7. On-Chip Memory Map

#### P6.2/A10m/A2 P6.3/A11m/A3 P6.4/A12m/A4 P6.0/A8m/A0 P6.1/A9m/A1 DAC1 P4.0 P4.1 P4.2 P4.3 P4.4 P4.5/ALE P5.0/A8 P5.1/A9 P5.2/A10 P5.3/A11 P5.4/A12 P5.5/A13 P5.6/A14 P5.7/A15 P4.6/RD P4.7/WR DGND DAC0 100 8 86 88 8 8 5 8 8 22 8 8 2 88 8 ₹ 8 2 2 88 2 1 2 75 P6.5/A13m/A5 TMS 1 TCK 2 74 P6.6/A14m/A6 3 TDI 73 P6.7/A15m/A7 4 72 P7.0/AD0/D0 TDO 5 71 P7.1/AD1/D1 /RST CANRX 6 70 P7.2/AD2/D2 7 69 P7.3/AD3/D3 CANTX AV+ 8 68 P7.4/AD4/D4 AGND 9 67 P7.5/AD5/D5 AGND 10 66 P7.6/AD6/D6 AV+ 11 65 P7.7/AD7/D7 VREF 12 64 VDD C8051F040/2/4/6 AGND 13 63 DGND AV+ 14 62 P0.0 61 P0.1 VREFD 15 60 P0.2 VREF0 16 VREF2 17 59 P0.3 58 P0.4 AIN0.0 18 57 P0.5/ALE AIN0.1 19 56 P0.6/RD AIN0.2 20 AIN0.3 21 55 P0.7/WR HVCAP 22 54 P3.0/AD0/D0 HVREF 23 53 P3.1/AD1/D1 52 P3.2/AD2/D2 HVAIN+ 24 HVAIN- 25 51 P3.3/AD3/D3 [<del>4</del>] 26 27 2 P1.6/AIN2.6/A14 [ P1.5/AIN2.5/A13 ] P1.1/AIN2.1/A9 [ P1.0/AIN2.0/A8 [ P2.7/A15m/A7 P2.6/A14m/A6 P2.5/A13m/A5 P2.4/A13m/A4 P2.4/A12m/A4 P2.3/A11m/A3 DQ DGND P2.0/A8m/A0 | P3.7/AD7/D7 | P3.6/AD6/D6 | P3.5/AD5/D5 | P3.4/AD4/D4 | XTAL1 XTAL2 MONEN P1.4/AIN2.4/A12 P1.2/AIN2.2/A10 P2.2/A10m/A2 P1.7/AIN2.7/A15 P1.3/AIN2.3/A11 P2.1/A9m/A1

Figure 4.1. TQFP-100 Pinout Diagram

### C8051F040/1/2/3/4/5/6/7

|        |      |                        |        |                        | Δ      | MX0AD3-             | 0    |                    |       |                |

|--------|------|------------------------|--------|------------------------|--------|---------------------|------|--------------------|-------|----------------|

|        |      | 0000                   | 0001   | 0010                   | 0011   | 0100                | 0101 | 0110               | 0111  | 1xxx           |

|        | 0000 | AIN0.0                 | AIN0.1 | AIN0.2                 | AIN0.3 | HVDA                | AGND | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0001 | +(AIN0.0)<br>-(AIN0.1) |        | AIN0.2                 | AIN0.3 | HVDA                | AGND | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0010 | AIN0.0                 | AIN0.1 | +(AIN0.2)<br>-(AIN0.3) |        | HVDA                | AGND | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0011 | +(AIN0.0)<br>-(AIN0.1) |        | +(AIN0.2)<br>-(AIN0.3) |        | HVDA                | AGND | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0100 | AIN0.0                 | AIN0.1 | AIN0.2                 | AIN0.3 | +(HVDA)<br>-(HVREF) |      | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0101 | +(AIN0.0)<br>-(AIN0.1) |        | AIN0.2                 | AIN0.3 | +(HVDA)<br>-(HVREF) |      | P3EVEN             | P3ODD | TEMP<br>SENSOR |

| 3-0    | 0110 | AIN0.0                 | AIN0.1 | +(AIN0.2)<br>-(AIN0.3) |        | +(HVDA)<br>-(HVREF) |      | P3EVEN             | P3ODD | TEMP<br>SENSOR |

| Bits   | 0111 | +(AIN0.0)<br>-(AIN0.1) |        | +(AIN0.2)<br>-(AIN0.3) |        | +(HVDA)<br>-(HVREF) |      | P3EVEN             | P3ODD | TEMP<br>SENSOR |

| AMX0CF | 1000 | AIN0.0                 | AIN0.1 | AIN0.2                 | AIN0.3 | HVDA                | AGND | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

| AM     | 1001 | +(AIN0.0)<br>-(AIN0.1) |        | AIN0.2                 | AIN0.3 | HVDA                | AGND | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1010 | AIN0.0                 | AIN0.1 | +(AIN0.2)<br>-(AIN0.3) |        | HVDA                | AGND | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1011 | +(AIN0.0)<br>-(AIN0.1) |        | +(AIN0.2)<br>-(AIN0.3) |        | HVDA                | AGND | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1100 | AIN0.0                 | AIN0.1 | AIN0.2                 | AIN0.3 | +(HVDA)<br>-(HVREF) |      | +P3EVEN<br>-P3ODD) |       | TEMP<br>SENSOR |

|        | 1101 | +(AIN0.0)<br>-(AIN0.1) |        | AIN0.2                 | AIN0.3 | +(HVDA)<br>-(HVREF) |      | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1110 | AIN0.0                 | AIN0.1 | +(AIN0.2)<br>-(AIN0.3) |        | +(HVDA)<br>-(HVREF) |      | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1111 | +(AIN0.0)<br>-(AIN0.1) |        | +(AIN0.2)<br>-(AIN0.3) |        | +(HVDA)<br>-(HVREF) |      | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

### Table 5.1. AMUX Selection Chart (AMX0AD3–0 and AMX0CF3–0 bits)

Note: "P3EVEN" denotes even numbered and "P3ODD" odd numbered Port 3 pins selected in the AMX0PRT register.

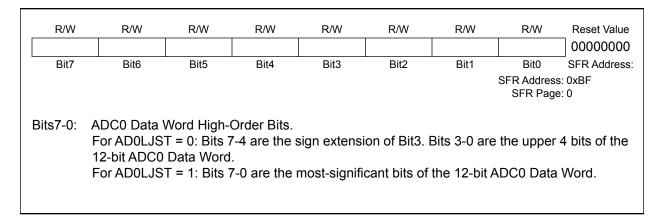

### SFR Definition 5.7. ADC0H: ADC0 Data Word MSB

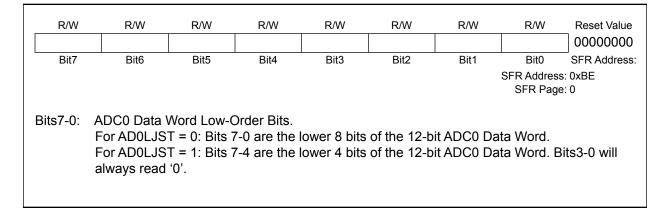

### SFR Definition 5.8. ADC0L: ADC0 Data Word LSB

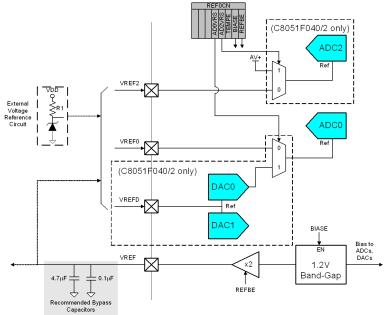

### 9. Voltage Reference (C8051F040/2/4/6)

The voltage reference circuit offers full flexibility in operating the ADC and DAC modules. Three voltage reference input pins allow each ADC and the two DACs (C8051F040/2 only) to reference an external voltage reference or the on-chip voltage reference output. ADC0 may also reference the DAC0 output internally, and ADC2 may reference the analog power supply voltage, via the VREF multiplexers shown in Figure 9.1.

The internal voltage reference circuit consists of a 1.2 V, temperature stable bandgap voltage reference generator and a gain-of-two output buffer amplifier. The internal reference may be routed via the VREF pin to external system components or to the voltage reference input pins shown in Figure 9.1. Bypass capacitors of 0.1  $\mu$ F and 4.7  $\mu$ F are recommended from the VREF pin to AGND, as shown in Figure 9.1. See Table 9.1 for voltage reference specifications.

The Reference Control Register, REF0CN (defined in SFR Definition 9.1) enables/disables the internal reference generator and selects the reference inputs for ADC0 and ADC2. The BIASE bit in REF0CN enables the on-board reference generator while the REFBE bit enables the gain-of-two buffer amplifier which drives the VREF pin. When disabled, the supply current drawn by the bandgap and buffer amplifier falls to less than 1  $\mu$ A (typical) and the output of the buffer amplifier enters a high impedance state. If the internal bandgap is used as the reference voltage generator, BIASE and REFBE must both be set to logic 1. If the internal reference is not used, REFBE may be set to logic 0. Note that the BIASE bit must be set to logic 1 if either DAC or ADC is used, regardless of the voltage reference used. If neither the ADC nor the DAC are being used, both of these bits can be set to logic 0 to conserve power. Bits AD0VRS and AD2VRS select the ADC0 and ADC2 voltage reference sources, respectively. The electrical specifications for the Voltage Reference are given in Table 9.1.

The temperature sensor connects to the highest order input of the ADC0 input multiplexer (see Section "5.1. Analog Multiplexer and PGA" on page 47 for C8051F040 devices, or Section "6.1. Analog Multiplexer and PGA" on page 69 for C8051F042/4/6 devices). The TEMPE bit within REF0CN enables and disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any A/D measurements performed on the sensor while disabled result in meaningless data.

Figure 9.1. Voltage Reference Functional Block Diagram

| SFR Definition 12.13. EIE1: Extended I | Interrupt Enable 1 |

|----------------------------------------|--------------------|

|----------------------------------------|--------------------|

| R/W   | R/W                           | R/W         | R/W          | R/W          | R/W         | R/W      | R/W         | Reset Value  |

|-------|-------------------------------|-------------|--------------|--------------|-------------|----------|-------------|--------------|

|       | CP2IE                         | CP1IE       | CP0IE        | EPCA0        | EWADC0      | ESMB0    | ESPI0       | 0000000      |

| Bit7  | Bit6                          | Bit5        | Bit4         | Bit3         | Bit2        | Bit1     | Bit0        |              |

|       |                               |             |              |              |             |          | SFR Address |              |

|       |                               |             |              |              |             |          | SFR Page    | e: All Pages |

| Bit7: | Reserved. R                   | ead = 0b V  | Vrite = don' | t care       |             |          |             |              |

| Bit6: | CP2IE: Enal                   |             |              |              |             |          |             |              |

|       | This bit sets                 |             |              |              |             |          |             |              |

|       | 0: Disable C                  |             | •            |              |             |          |             |              |

|       | 1: Enable inf                 | errupt requ | ests genera  | ated by the  | CP2IF flag. |          |             |              |

| Bit6: | CP1IE: Enal                   |             |              |              |             |          |             |              |

|       | This bit sets                 |             | •            | 1 interrupt. |             |          |             |              |

|       | 0: Disable C                  |             |              |              |             |          |             |              |

| Dilo  | 1: Enable inf                 |             |              |              | CP1IF flag. |          |             |              |

| Bit6: | CP0IE: Enal                   |             |              |              |             |          |             |              |

|       | This bit sets<br>0: Disable C |             |              | o interrupt. |             |          |             |              |

|       | 1: Enable inf                 |             |              | ated by the  |             |          |             |              |

| Bit3: | EPCA0: Ena                    |             |              |              |             | rrunt    |             |              |

| Dito. | This bit sets                 |             |              |              |             | inupt.   |             |              |

|       | 0: Disable al                 |             |              |              |             |          |             |              |

|       | 1: Enable int                 |             | •            | ated by PC   | ٩0.         |          |             |              |

| Bit2: | EWADC0: E                     |             |              |              |             |          |             |              |

|       | This bit sets                 | the maskin  | g of ADC0    | Window Co    | mparison in | terrupt. |             |              |

|       | 0: Disable A                  |             |              |              |             |          |             |              |

|       | 1: Enable Int                 |             |              |              |             |          | ns.         |              |

| Bit1: | ESMB0: Ena                    |             |              |              |             | rrupt.   |             |              |

|       | This bit sets                 |             | •            | Bus interru  | pt.         |          |             |              |

|       | 0: Disable al                 |             |              |              |             |          |             |              |

| Bit0: | 1: Enable inf<br>ESPI0: Enab  |             |              |              |             |          |             |              |

| DILU. | This bit sets                 |             | •            | •            | io) menupi. |          |             |              |

|       | 0: Disable al                 |             | •            | iteriupi.    |             |          |             |              |

|       | 1: Enable Int                 |             |              | ated by the  | SPI0 flag   |          |             |              |

|       |                               |             | este genere  |              | er is nag.  |          |             |              |

|       |                               |             |              |              |             |          |             |              |

|       |                               |             |              |              |             |          |             |              |

| R/W   | R/W                                                                                                                      | R/W           | R/W           | R/W           | R/W            | R/W         | R/W         | Reset Value  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|----------------|-------------|-------------|--------------|--|--|--|

| -     | PCP2                                                                                                                     | PCP1          | PCP0          | PPCA0         | PWADC0         | PSMB0       | PSPI0       | 00000000     |  |  |  |

| Bit7  | Bit6                                                                                                                     | Bit5          | Bit4          | Bit3          | Bit2           | Bit1        | Bit0        |              |  |  |  |

|       |                                                                                                                          |               |               |               |                |             | SFR Address |              |  |  |  |

|       |                                                                                                                          |               |               |               |                |             | SFR Page    | e: All Pages |  |  |  |

| Bit7: | Reserved.                                                                                                                |               |               |               |                |             |             |              |  |  |  |

| Bit6: | PCP2: Com                                                                                                                | oarator2 (C   | P2) Interrur  | ot Priority C | Control        |             |             |              |  |  |  |

|       | This bit sets                                                                                                            |               |               |               |                |             |             |              |  |  |  |

|       | 0: CP2 inter                                                                                                             |               |               | •             |                |             |             |              |  |  |  |

|       | 1: CP2 inter                                                                                                             | •             |               |               |                |             |             |              |  |  |  |

| Bit5: | PCP1: Com                                                                                                                | parator1 (C   | P1) Interrup  | ot Priority C | ontrol.        |             |             |              |  |  |  |

|       | This bit sets                                                                                                            |               |               |               |                |             |             |              |  |  |  |

|       | 0: CP1 inter                                                                                                             |               |               |               |                |             |             |              |  |  |  |

|       | 1: CP1 inter                                                                                                             | •             | • • •         |               |                |             |             |              |  |  |  |

| Bit4: | PCP0: Com                                                                                                                |               |               |               | control.       |             |             |              |  |  |  |

|       | This bit sets                                                                                                            |               |               | •             |                |             |             |              |  |  |  |

|       | 0: CP0 inter                                                                                                             |               |               |               |                |             |             |              |  |  |  |

|       | 1: CP0 inter                                                                                                             | •             | • • •         |               |                |             | 1           |              |  |  |  |

| Bit3: |                                                                                                                          | •             |               |               | ) Interrupt Pr | iority Cont | rol.        |              |  |  |  |

|       | This bit sets<br>0: PCA0 inte                                                                                            |               |               | •             |                |             |             |              |  |  |  |

|       | 1: PCA0 inte                                                                                                             | •             |               |               |                |             |             |              |  |  |  |

| Bit2: |                                                                                                                          | •             | • •           |               | ot Priority Co | ntrol       |             |              |  |  |  |

| DILZ. | This bit sets                                                                                                            |               |               |               |                | muor.       |             |              |  |  |  |

|       | 0: ADC0 Wir                                                                                                              |               |               |               |                |             |             |              |  |  |  |

|       | 1: ADC0 Wir                                                                                                              |               |               |               |                |             |             |              |  |  |  |

| Bit1: |                                                                                                                          |               | •             | • • •         |                | ority Contr | ol.         |              |  |  |  |

|       | PSMB0: System Management Bus (SMBus0) Interrupt Priority Control.<br>This bit sets the priority of the SMBus0 interrupt. |               |               |               |                |             |             |              |  |  |  |

|       | 0: SMBus interrupt set to low priority level.                                                                            |               |               |               |                |             |             |              |  |  |  |

|       | 1: SMBus in                                                                                                              | terrupt set f | to high prior | rity level.   |                |             |             |              |  |  |  |

| Bit0: | PSPI0: Seria                                                                                                             | al Periphera  | al Interface  | (SPI0) Inter  | rrupt Priority | Control.    |             |              |  |  |  |

|       | This bit sets                                                                                                            |               |               | •             |                |             |             |              |  |  |  |

|       | 0: SPI0 inter                                                                                                            | •             |               |               |                |             |             |              |  |  |  |

|       | 1: SPI0 inter                                                                                                            | rupt set to   | high priority | level.        |                |             |             |              |  |  |  |

|       |                                                                                                                          |               |               |               |                |             |             |              |  |  |  |

|       |                                                                                                                          |               |               |               |                |             |             |              |  |  |  |

|       |                                                                                                                          |               |               |               |                |             |             |              |  |  |  |

### SFR Definition 12.15. EIP1: Extended Interrupt Priority 1

### 14. Oscillators

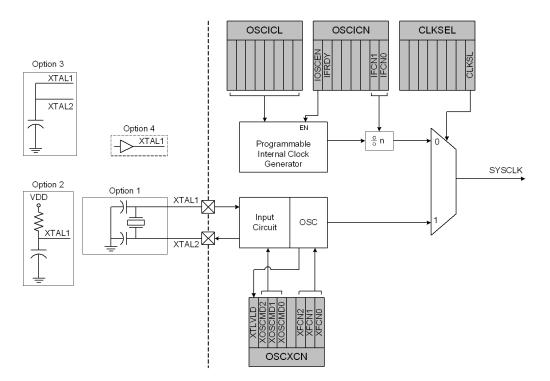

Figure 14.1. Oscillator Diagram

### 14.1. Programmable Internal Oscillator

All C8051F04x devices include a programmable internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be programmed via the OSCICL register as defined by SFR Definition 14.1. OSCICL is factory calibrated to obtain a 24.5 MHz frequency.

Electrical specifications for the precision internal oscillator are given in Table 14.1 on page 175. The programmed internal oscillator frequency must not exceed 25 MHz. The system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN.

### 14.5. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 14.1, Option 2. The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23( 10<sup>3</sup> ) / RC = 1.23 ( 10<sup>3</sup> ) / [ 246 x 50 ] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 14.4, the required XFCN setting is 010b.

### 14.6. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 14.1, Option 3. The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the desired frequency of oscillation and find the capacitor to be used from the equations below. Assume  $V_{DD} = 3.0 \text{ V}$  and f = 50 kHz:

$f = KF / (C \times V_{DD}) = KF / (C \times 3) = 0.050 MHz$

If a frequency of roughly 50 kHz is desired, select the K Factor from the table in SFR Definition 14.4 as KF = 7.7:

0.050 MHz = 7.7 / (C x 3)

C x 3 = 7.7 / 0.050 = 154, so C = 154 / 3 pF = 51.3 pF

Therefore, the XFCN value to use in this example is 010b.

The lock bits can always be read and cleared to logic 0 regardless of the security setting applied to the block containing the security bytes. This allows additional blocks to be protected after the block containing the security bytes has been locked. Important Note: The only means of removing a lock once set is to erase the entire program memory space by performing a JTAG erase operation (i.e., cannot be done in user firmware). Addressing either security byte while performing a JTAG erase operation will automatically initiate erasure of the entire program memory space (except for the reserved area). This erasure can only be performed via JTAG. If a non-security byte in the 0xFBFF-0xFDFF (C8051F040/1/2/3/4/5) or 0x7DFF-0x7FFF (C8051F046/7) page is addressed during the JTAG erasure, only that page (including the security bytes) will be erased.

The Flash Access Limit security feature (see Figure 15.1) protects proprietary program code and data from being read by software running on the C8051F04x. This feature provides support for OEMs that wish to program the MCU with proprietary value-added firmware before distribution. The value-added firmware can be protected while allowing additional code to be programmed in remaining program memory space later.

The Software Read Limit (SRL) is a 16-bit address that establishes two logical partitions in the program memory space. The first is an upper partition consisting of all the program memory locations at or above the SRL address, and the second is a lower partition consisting of all the program memory locations starting at 0x0000 up to (but excluding) the SRL address. Software in the upper partition can execute code in the lower partition, but is prohibited from reading locations in the lower partition using the MOVC instruction. (Executing a MOVC instruction from the upper partition with a source address in the lower partition will always return a data value of 0x00.) Software running in the lower partition can access locations in both the upper and lower partition without restriction.

The Value-added firmware should be placed in the lower partition. On reset, control is passed to the valueadded firmware via the reset vector. Once the value-added firmware completes its initial execution, it branches to a predetermined location in the upper partition. If entry points are published, software running in the upper partition may execute program code in the lower partition, but it cannot read the contents of the lower partition. Parameters may be passed to the program code running in the lower partition either through the typical method of placing them on the stack or in registers before the call or by placing them in prescribed memory locations in the upper partition.

The SRL address is specified using the contents of the Flash Access Register. The 16-bit SRL address is calculated as 0xNN00, where NN is the contents of the SRL Security Register. Thus, the SRL can be located on 256-byte boundaries anywhere in program memory space. However, the 512-byte erase sector size essentially requires that a 512 boundary be used. The contents of a non-initialized SRL security byte is 0x00, thereby setting the SRL address to 0x0000 and allowing read access to all locations in program memory space by default.

| PSN 970        |                                          |        |        | Pi                                        | )<br>4                                   |

|----------------|------------------------------------------|--------|--------|-------------------------------------------|------------------------------------------|

| MIN UKA<br>FXO | 0                                        | 3      |        |                                           |                                          |

| RX0            | w.                                       | ۲      |        |                                           |                                          |

| SCK            | 1                                        |        | ø      |                                           |                                          |

| MISO           |                                          | ۲      |        | ۲                                         |                                          |

| MOSI           |                                          | v      | \$     |                                           |                                          |

| NSS            |                                          |        |        |                                           | -                                        |

| SDA            | \$                                       |        | \$     |                                           |                                          |

| SCL            |                                          | ۲      | -      |                                           |                                          |

| TX1            | \$                                       |        | @      |                                           |                                          |

| RX1            |                                          | ۲      |        | 49                                        |                                          |

| CEX0           | \$                                       |        | \$     |                                           | \$                                       |

| CEX1           |                                          | ۹      | -      | 49                                        |                                          |

| CEX2           |                                          |        | \$     |                                           |                                          |

| CEX3           |                                          |        |        | ۲                                         |                                          |

| CEX4           |                                          |        |        |                                           |                                          |

| CEX5           |                                          |        |        |                                           |                                          |

| ECI            | en e |        |        |                                           | , B                                      |

| CP0            | \$                                       |        | ø      | 0                                         |                                          |

| CP1            | \$                                       | 8      | \$     |                                           | 0                                        |

| CP2            | Ø                                        | @      | ø      | ø                                         | ()<br>()                                 |

| TO             | \$                                       | \$     |        | 1000000<br>100000000000000000000000000000 |                                          |

| /INTO          | \$                                       | \$     | \$     | \$                                        | ۲                                        |

| T1             | ann an  | ø      | \$     | ¢                                         | en e |

| /INT1          | annan<br>B                               | \$     |        | \$                                        | ø                                        |

| T2             | -                                        | ۲      | ۲      | \$                                        | ۲                                        |

| T2EX           | ø                                        | \$     | \$     | \$                                        | ti th                                    |

| Т3             | ۲                                        | \$     | Ø      | 1                                         | ¢,                                       |

| тзех           | ۲                                        | ۲      | ۲      | ۲                                         | ۲                                        |

| T4             | ø                                        | ۲      | ø      | 8                                         | ø                                        |

| T4EX           | Ø                                        | ۲      | ø      | Ø                                         | en e |

| SYSCLK         | ۲                                        | ۲      | ۲      | ۲                                         | ۲                                        |

| CNVSTRO        | Ø                                        | ۲      | ¢      | ø                                         | (B)                                      |

| CNVSTR2        | \$                                       | \$     |        | \$                                        |                                          |

|                |                                          |        |        |                                           |                                          |

|                |                                          |        |        |                                           |                                          |

|                |                                          |        |        |                                           |                                          |

|                |                                          |        |        |                                           |                                          |

|                | innnnn:                                  | tiinnn | inesne | dimme.                                    | anana;                                   |

Figure 17.6. Crossbar Example: (EMIFLE = 1; EMIF in Multiplexed Mode; P1MDIN = 0xE3; XBR0 = 0x05; XBR1 = 0x14; XBR2 = 0x42)

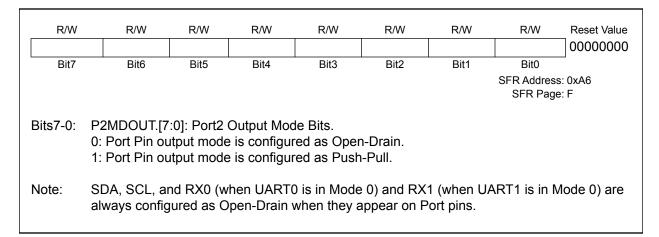

### SFR Definition 17.12. P2MDOUT: Port2 Output Mode

### SFR Definition 17.13. P3: Port3 Data

| R/W      | R/W                                                                                                                                                                                                                                                                          | R/W  | R/W  | R/W  | R/W  | R/W       | R/W                     | Reset Value             |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-----------|-------------------------|-------------------------|--|--|--|--|--|

| P3.7     | P3.6                                                                                                                                                                                                                                                                         | P3.5 | P3.4 | P3.3 | P3.2 | P3.1      | P3.0                    | 11111111                |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                         | Bit5 | Bit4 | Bit3 | Bit2 | Bit2 Bit1 |                         | Bit<br>Addressable      |  |  |  |  |  |

|          |                                                                                                                                                                                                                                                                              |      |      |      |      |           | SFR Address<br>SFR Page | s: 0xB0<br>e: All Pages |  |  |  |  |  |

| Bits7-0: |                                                                                                                                                                                                                                                                              |      |      |      |      |           |                         |                         |  |  |  |  |  |

| Note:    | P3.[7:0] can be driven by the External Data Memory Interface (as AD[7:0] in Multiplexed mode, or as D[7:0] in Non-multiplexed mode). See Section "16. External Data Memory Interface and On-Chip XRAM" on page 187 for more information about the External Memory Interface. |      |      |      |      |           |                         |                         |  |  |  |  |  |

| SFR Definition 19.1 | . SMB0CN: SMBus0 Control |

|---------------------|--------------------------|

|---------------------|--------------------------|

| R     | R/W                                                                                                                                                                                | R/W                                                                   | R/W                                                        | R/W                                      | R/W                                        | R/W                          | R/W                           | Reset Value  |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------|--------------------------------------------|------------------------------|-------------------------------|--------------|--|--|--|--|--|--|

| BUSY  | ENSMB                                                                                                                                                                              | STA                                                                   | STO                                                        | SI                                       | AA                                         | FTE                          | TOE                           | 00000000     |  |  |  |  |  |  |

| Bit7  | Bit6                                                                                                                                                                               | Bit5                                                                  | Bit4                                                       | Bit3                                     | Bit2                                       | Bit1                         | Bit0<br>SFR Addres<br>SFR Pag |              |  |  |  |  |  |  |

| Bit7: | BUSY: Busy Status Flag.<br>0: SMBus0 is free<br>1: SMBus0 is busy                                                                                                                  |                                                                       |                                                            |                                          |                                            |                              |                               |              |  |  |  |  |  |  |

| Bit6: | <ol> <li>SMBus0 is busy</li> <li>ENSMB: SMBus Enable.</li> <li>This bit enables/disables the SMBus serial interface.</li> <li>SMBus0 disabled.</li> <li>SMBus0 enabled.</li> </ol> |                                                                       |                                                            |                                          |                                            |                              |                               |              |  |  |  |  |  |  |

| Bit5: | STA: SMBus<br>0: No START<br>1: When ope<br>bus is not fre<br>more bytes h                                                                                                         | Start Flag.<br>condition<br>rating as a<br>e, the STA<br>ave been t   | is transmitte<br>master, a S<br>RT is transr<br>ransmitted | START cond<br>nitted after               | a STOP is ı                                | received.) If                | STA is set                    | after one or |  |  |  |  |  |  |

| Bit4: | START cond<br>STO: SMBus<br>0: No STOP<br>1: Setting ST<br>tion is receive<br>dition is trans<br>causes SMB                                                                        | Stop Flag<br>condition is<br>O to logic<br>ed, hardwa<br>mitted follo | s transmitte<br>1 causes a<br>ire clears S<br>owed by a S  | STOP conc<br>TO to logic<br>START conc   | 0. If both S<br>dition. In sla             | TA and ST<br>ave mode, s     | O are set, a                  | a STOP con-  |  |  |  |  |  |  |

| Bit3: | SI: SMBus S<br>This bit is set<br>0xF8 does no<br>the CPU to v<br>cleared by ha                                                                                                    | erial Interru<br>by hardwa<br>ot cause Sl<br>ector to the             | upt Flag.<br>are when on<br>I to be set.)<br>e SMBus inf   | e of 27 pos<br>When the S<br>errupt serv | sible SMBu<br>SI interrupt<br>ice routine. | us0 states is<br>is enabled, | setting this                  | bit causes   |  |  |  |  |  |  |

| Bit2: | AA: SMBus A<br>This bit define<br>line.<br>0: A "not ack                                                                                                                           | Assert Ackr<br>es the type<br>nowledge"                               | owledge Fl<br>of acknowl<br>(high level                    | ag.<br>edge returr<br>on SDA) is         | ied during t<br>returned du                | uring the ac                 | knowledge                     | cycle.       |  |  |  |  |  |  |

| Bit1: | 1: An "acknow<br>FTE: SMBus<br>0: No timeour<br>1: Timeout w                                                                                                                       | Free Time<br>t when SC                                                | r Enable Bi<br>L is high                                   | t                                        |                                            | -                            |                               | cie.         |  |  |  |  |  |  |

| Bit0: | TOE: SMBus<br>0: No timeou<br>1: Timeout w                                                                                                                                         | Timeout E<br>t when SC                                                | inable Bit<br>L is low.                                    |                                          |                                            |                              |                               |              |  |  |  |  |  |  |

| 11.0592 MHZ OSCIIIATOR       |                      |                                |              |                                                 |                  |                                     |  |  |  |  |  |  |

|------------------------------|----------------------|--------------------------------|--------------|-------------------------------------------------|------------------|-------------------------------------|--|--|--|--|--|--|

|                              |                      | Freque                         | ncy: 11.0592 | MHz                                             |                  |                                     |  |  |  |  |  |  |

| Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Source       | SCA1-SCA0<br>(pre-scale<br>select) <sup>*</sup> | T1M <sup>*</sup> | Timer 1<br>Reload<br>Value<br>(hex) |  |  |  |  |  |  |

| 230400                       | 0.00%                | 48                             | SYSCLK       | XX                                              | 1                | 0xE8                                |  |  |  |  |  |  |

| 115200                       | 0.00%                | 96                             | SYSCLK       | XX                                              | 1                | 0xD0                                |  |  |  |  |  |  |

| 57600                        | 0.00%                | 192                            | SYSCLK       | XX                                              | 1                | 0xA0                                |  |  |  |  |  |  |

| 28800                        | 0.00%                | 384                            | SYSCLK       | XX                                              | 1                | 0x40                                |  |  |  |  |  |  |

| 14400                        | 0.00%                | 768                            | SYSCLK / 12  | 00                                              | 0                | 0xE0                                |  |  |  |  |  |  |

| 9600                         | 0.00%                | 1152                           | SYSCLK / 12  | 00                                              | 0                | 0xD0                                |  |  |  |  |  |  |

| 2400                         | 0.00%                | 4608                           | SYSCLK / 12  | 00                                              | 0                | 0x40                                |  |  |  |  |  |  |

| 1200                         | 0.00%                | 9216                           | SYSCLK / 48  | 10                                              | 0                | 0xA0                                |  |  |  |  |  |  |

| 230400                       | 0.00%                | 48                             | EXTCLK / 8   | 11                                              | 0                | 0xFD                                |  |  |  |  |  |  |

| 115200                       | 0.00%                | 96                             | EXTCLK / 8   | 11                                              | 0                | 0xFA                                |  |  |  |  |  |  |

| 57600                        | 0.00%                | 192                            | EXTCLK / 8   | 11                                              | 0                | 0xF4                                |  |  |  |  |  |  |

| 28800                        | 0.00%                | 384                            | EXTCLK / 8   | 11                                              | 0                | 0xE8                                |  |  |  |  |  |  |

| 14400                        | 0.00%                | 768                            | EXTCLK / 8   | 11                                              | 0                | 0xD0                                |  |  |  |  |  |  |

| 9600                         | 0.00%                | 1152                           | EXTCLK / 8   | 11                                              | 0                | 0xB8                                |  |  |  |  |  |  |

| _                            | X = Don't care       | 2                              |              |                                                 |                  |                                     |  |  |  |  |  |  |

# Table 22.5. Timer Settings for Standard Baud Rates Using an External11.0592 MHz Oscillator

X = Don't care

\*Note: SCA1-SCA0 and T1M bit definitions can be found in Section 23.1.

### SFR Definition 23.9. TMRnCF: Timer n Configuration

|         |                                                                                                                                                          | _            | R/W<br>TnM1   | R/W<br>TnM0   | R/W<br>TOGn  | R/W<br>TnOE | R/W<br>DCEN | Reset Value |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|---------------|--------------|-------------|-------------|-------------|--|--|--|--|--|--|

| Bit7    | Bit6                                                                                                                                                     | Bit5         | Bit4          | Bit3          | Bit2         | Bit1        | Bit0        | Bit         |  |  |  |  |  |  |

|         |                                                                                                                                                          |              |               |               | DILL         | Diti        | Dito        | Addressable |  |  |  |  |  |  |

|         | ess: TMR2CF:0xC<br>age TMR2CF: pag                                                                                                                       | -            |               |               |              |             |             |             |  |  |  |  |  |  |

| Bit7-5: | Reserved.                                                                                                                                                |              |               |               |              |             |             |             |  |  |  |  |  |  |

| Bit4-3: | TnM1 and Tr                                                                                                                                              | nM0: Timer   | Clock Mode    | e Select Bit  | S.           |             |             |             |  |  |  |  |  |  |

|         | Bits used to select the Timer clock source. The sources can be the System Clock                                                                          |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | (SYSCLK), SYSCLK divided by 2 or 12, or an external clock signal routed to Tn (port pin)                                                                 |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | divided by 8.                                                                                                                                            |              | rce is select | ed as follov  | /S:          |             |             |             |  |  |  |  |  |  |

|         | 00: SYSCLK                                                                                                                                               |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | 01: SYSCLK                                                                                                                                               |              | (10)          |               |              |             |             |             |  |  |  |  |  |  |

|         | 10: EXTERNAL CLOCK/8                                                                                                                                     |              |               |               |              |             |             |             |  |  |  |  |  |  |

| Bit2:   | 11: SYSCLK/                                                                                                                                              |              | ato hit       |               |              |             |             |             |  |  |  |  |  |  |

| DILZ.   | TOGn: Toggle output state bit.<br>When timer is used to toggle a port pin, this bit can be used to read the state of the output, o                       |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | can be written to in order to force the state of the output.                                                                                             |              |               |               |              |             |             |             |  |  |  |  |  |  |

| Bit1:   | TnOE: Timer output enable bit.                                                                                                                           |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | This bit enables the timer to output a 50% duty cycle output to the timer's assigned external                                                            |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | port pin.                                                                                                                                                |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | <u>NOTE</u> : A timer is configured for Square Wave Output as follows:                                                                                   |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | CP/RLn=0                                                                                                                                                 |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | C/Tn = 0                                                                                                                                                 |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | TnOE = 1                                                                                                                                                 |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | Load RCAPnH:RCAPnL (See Section "Equation 23.1. Square Wave Frequency" on                                                                                |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | page 300).<br>Configure Port Pin for output (See Section "17, Port Input/Output" on page 202)                                                            |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | Configure Port Pin for output (See Section "17. Port Input/Output" on page 203).<br>0: Output of toggle mode not available at Timers' assigned port pin. |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | 1: Output of toggle mode available at Timers' assigned port pin.                                                                                         |              |               |               |              |             |             |             |  |  |  |  |  |  |

| Bit0:   | DCEN: Decre                                                                                                                                              |              |               |               |              |             |             |             |  |  |  |  |  |  |

|         | This bit enab                                                                                                                                            | les the time | er to count ι | up or down    | as determin  | ed by the s | tate of TnE | EX.         |  |  |  |  |  |  |

|         | 0: Timer will o                                                                                                                                          | count up, re | egardless of  | f the state c | f TnEX.      |             |             |             |  |  |  |  |  |  |

|         | 1: Timer will o                                                                                                                                          | •            |               | •             | e state of T | nEX as foll | ows:        |             |  |  |  |  |  |  |

|         |                                                                                                                                                          |              | timer count   |               |              |             |             |             |  |  |  |  |  |  |

|         | if Tnl                                                                                                                                                   | ∟X = 1, the  | timer count   | ts UP.        |              |             |             |             |  |  |  |  |  |  |

|         |                                                                                                                                                          |              |               |               |              |             |             |             |  |  |  |  |  |  |

### SFR Definition 23.10. RCAPnL: Timer n Capture Register Low Byte

| R/W          | R/W         | R/W          | R/W           | R/W          | R/W  | R/W  | R/W  | Reset Value                |

|--------------|-------------|--------------|---------------|--------------|------|------|------|----------------------------|

| Bit7         | Bit6        | Bit5         | Bit4          | Bit3         | Bit2 | Bit1 | Bit0 |                            |

| SFR Address: | RCAP2L: 0xC | A; RCAP3L: 0 | xCA; RCAP4L   | : 0xCA       |      |      |      |                            |

| SFR Page:    | RCAP2L: pag | e 0; RCAP3L: | page 1; RCAF  | P4L: page 2  |      |      |      |                            |

| m            |             | register ca  | ptures the lo | ow byte of T |      |      |      | d in capture<br>the reload |

#### SFR Definition 23.11. RCAPnH: Timer n Capture Register High Byte

| R/V      | / R/W         | R/W              | R/W            | R/W          | R/W          | R/W         | R/W          | Reset Value  |

|----------|---------------|------------------|----------------|--------------|--------------|-------------|--------------|--------------|

|          |               |                  |                |              |              |             |              | 00000000     |

| Bit      | Bit6          | Bit5             | Bit4           | Bit3         | Bit2         | Bit1        | Bit0         |              |

| SFR Ad   | dress: RCAP2H | : 0xCB; RCAP3H:  | 0xCB; RCAP4    | IH: 0xCB     |              |             |              |              |

| SFR      | Page: RCAP2H  | : page 0; RCAP3H | I: page 1; RCA | P4H: page 2  |              |             |              |              |

|          |               |                  |                |              |              |             |              |              |

| Bits 7-0 | ): RCAPnH     | : Timer n Capt   | ure Registe    | r High Byte. |              |             |              |              |

|          | The RCA       | PnH register c   | aptures the    | high byte of | f Timer n wl | nen Timer r | n is confiqu | ired in cap- |

|          |               | e. When Timer    | •              | • •          |              |             | •            |              |

|          | reload va     |                  | ge             |              |              |             |              |              |

|          |               |                  |                |              |              |             |              |              |

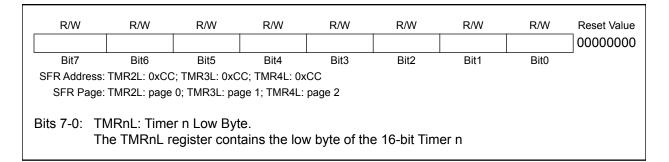

### SFR Definition 23.12. TMRnL: Timer n Low Byte

### 24.2. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

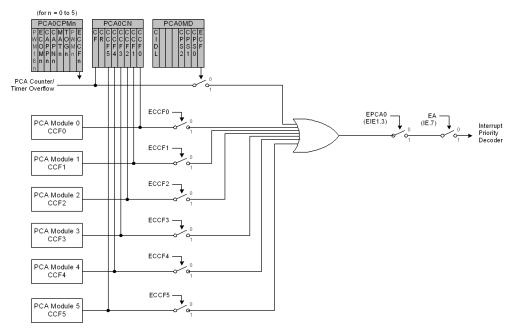

Table 24.2 summarizes the bit settings in the PCA0CPMn registers used to select the PCA0 capture/compare module's operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note: PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit (IE.7) and the EPCA0 bit (EIE1.3) to logic 1. See Figure 24.3 for details on the PCA interrupt configuration.

| PWM16 | ECOM | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                                |

|-------|------|------|------|-----|-----|-----|------|-----------------------------------------------|

| Х     | Х    | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge on<br>CEXn |

| Х     | Х    | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on<br>CEXn |

| Х     | Х    | 1    | 1    | 0   | 0   | 0   | Х    | Capture triggered by transition on CEXn       |

| Х     | 1    | 0    | 0    | 1   | 0   | 0   | Х    | Software Timer                                |

| Х     | 1    | 0    | 0    | 1   | 1   | 0   | Х    | High-Speed Output                             |

| Х     | 1    | 0    | 0    | 0   | 1   | 1   | Х    | Frequency Output                              |

| 0     | 1    | 0    | 0    | 0   | 0   | 1   | 0    | 8-Bit Pulse Width Modulator                   |

| 1     | 1    | 0    | 0    | 0   | 0   | 1   | 0    | 16-Bit Pulse Width Modulator                  |

#### Table 24.2. PCA0CPM Register Settings for PCA Capture/Compare Modules

X = Don't Care

### Figure 24.3. PCA Interrupt Block Diagram

### 24.3. Register Descriptions for PCA0

Following are detailed descriptions of the special function registers related to the operation of PCA0.

| R/W   | R/W                                                                                                                                                                                    | R/W                                                                                           | R/W                                                                                   | R/W                                                    | R/W                                                            | R/W                                         | R/W                                       | Reset Valu               |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------|-------------------------------------------|--------------------------|--|--|--|--|--|