# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                          |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 64                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 8x8b, 13x10b; D/A 2x10b, 2x12b                                |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 100-TQFP                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f042r      |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| N                   | Pin Nu     | Imbers                | Туре          | Description                                                                                                                                                                                                        |  |  |  |  |

|---------------------|------------|-----------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name                | F040/2/4/6 | F040/2/4/6 F041/3/5/7 |               | Description                                                                                                                                                                                                        |  |  |  |  |

| P1.0/AIN2.0/A8      | 36         | 29                    | A In<br>D I/O | ADC1 Input Channel 0 (See ADC1 Specification for com-<br>plete description).<br>Bit 8 External Memory Address bus (Non-multiplexed<br>mode)<br>Port 1.0<br>See Port Input/Output section for complete description. |  |  |  |  |

| P1.1/AIN2.1/A9      | 35         | 28                    | A In<br>D I/O | Port 1.1. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P1.2/AIN2.2/<br>A10 | 34         | 27                    | A In<br>D I/O | Port 1.2. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P1.3/AIN2.3/<br>A11 | 33         | 26                    | A In<br>D I/O | Port 1.3. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P1.4/AIN2.4/<br>A12 | 32         | 23                    | A In<br>D I/O | Port 1.4. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P1.5/AIN2.5/<br>A13 | 31         | 22                    | A In<br>D I/O | Port 1.5. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P1.6/AIN2.6/<br>A14 | 30         | 21                    | A In<br>D I/O | Port 1.6. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P1.7/AIN2.7/<br>A15 | 29         | 20                    | A In<br>D I/O | Port 1.7. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P2.0/A8m/A0         | 46         | 37                    | D I/O         | Bit 8 External Memory Address bus (Multiplexed mode)<br>Bit 0 External Memory Address bus (Non-multiplexed<br>mode) Port 2.0<br>See Port Input/Output section for complete description.                            |  |  |  |  |

| P2.1/A9m/A1         | 45         | 36                    | D I/O         | Port 2.1. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P2.2/A10m/A2        | 44         | 35                    | D I/O         | Port 2.2. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P2.3/A11m/A3        | 43         | 34                    | D I/O         | Port 2.3. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P2.4/A12m/A4        | 42         | 33                    | D I/O         | Port 2.4. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P2.5/A13m/A5        | 41         | 32                    | D I/O         | Port 2.5. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P2.6/A14m/A6        | 40         | 31                    | D I/O         | Port 2.6. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

| P2.7/A15m/A7        | 39         | 30                    | D I/O         | Port 2.7. See Port Input/Output section for complete description.                                                                                                                                                  |  |  |  |  |

Table 4.1. Pin Definitions (Continued)

#### P6.2/A10m/A2 P6.3/A11m/A3 P6.4/A12m/A4 P6.0/A8m/A0 P6.1/A9m/A1 DAC1 P4.0 P4.1 P4.2 P4.3 P4.4 P4.5/ALE P5.0/A8 P5.1/A9 P5.2/A10 P5.3/A11 P5.4/A12 P5.5/A13 P5.6/A14 P5.7/A15 P4.6/RD P4.7/WR DGND DAC0 100 8 86 88 8 8 5 8 8 22 8 8 2 88 8 ₹ 8 2 2 88 2 1 2 75 P6.5/A13m/A5 TMS 1 TCK 2 74 P6.6/A14m/A6 3 TDI 73 P6.7/A15m/A7 4 72 P7.0/AD0/D0 TDO 5 71 P7.1/AD1/D1 /RST CANRX 6 70 P7.2/AD2/D2 7 69 P7.3/AD3/D3 CANTX AV+ 8 68 P7.4/AD4/D4 AGND 9 67 P7.5/AD5/D5 AGND 10 66 P7.6/AD6/D6 AV+ 11 65 P7.7/AD7/D7 VREF 12 64 VDD C8051F040/2/4/6 AGND 13 63 DGND AV+ 14 62 P0.0 61 P0.1 VREFD 15 60 P0.2 VREF0 16 VREF2 17 59 P0.3 58 P0.4 AIN0.0 18 57 P0.5/ALE AIN0.1 19 56 P0.6/RD AIN0.2 20 AIN0.3 21 55 P0.7/WR HVCAP 22 54 P3.0/AD0/D0 HVREF 23 53 P3.1/AD1/D1 52 P3.2/AD2/D2 HVAIN+ 24 HVAIN- 25 51 P3.3/AD3/D3 [<del>4</del>] 26 27 2 P1.6/AIN2.6/A14 [ P1.5/AIN2.5/A13 ] P1.1/AIN2.1/A9 [ P1.0/AIN2.0/A8 [ P2.7/A15m/A7 P2.6/A14m/A6 P2.5/A13m/A5 P2.4/A13m/A4 P2.4/A12m/A4 P2.3/A11m/A3 DQ DGND P2.0/A8m/A0 | P3.7/AD7/D7 | P3.6/AD6/D6 | P3.5/AD5/D5 | P3.4/AD4/D4 | XTAL1 XTAL2 MONEN P1.4/AIN2.4/A12 P1.2/AIN2.2/A10 P2.2/A10m/A2 P1.7/AIN2.7/A15 P1.3/AIN2.3/A11 P2.1/A9m/A1

Figure 4.1. TQFP-100 Pinout Diagram

# C8051F040/1/2/3/4/5/6/7

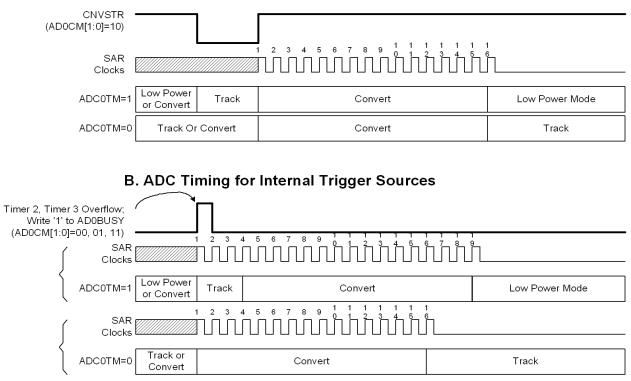

#### A. ADC Timing for External Trigger Source

## Figure 5.4. 12-Bit ADC Track and Conversion Example Timing

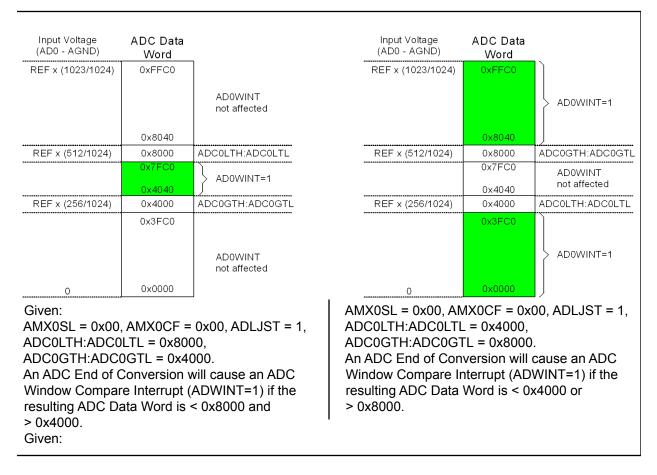

#### Figure 6.10. 10-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data

## Table 8.1. DAC Electrical Characteristics

$V_{DD}$  = 3.0 V, AV+ = 3.0 V,  $V_{REF}$  = 2.40 V (REFBE = 0), No Output Load unless otherwise specified.

| Parameter                                       | Conditions                                                        | Min | Тур              | Max           | Units  |

|-------------------------------------------------|-------------------------------------------------------------------|-----|------------------|---------------|--------|

| Static Performance                              |                                                                   |     |                  |               |        |

| Resolution                                      |                                                                   |     | 12               |               | bits   |

| Integral Nonlinearity                           |                                                                   |     | ±2               | —             | LSB    |

| Differential Nonlinearity                       |                                                                   |     |                  | ±1            | LSB    |

| Output Noise                                    | No Output Filter<br>100 kHz Output Filter<br>10 kHz Output Filter |     | 250<br>128<br>41 | _<br>_<br>_   | µVrms  |

| Offset Error                                    | Data Word = 0x014                                                 | _   | ±3               | ±30           | mV     |

| Offset Tempco                                   |                                                                   | —   | 6                | —             | ppm/°C |

| Full-Scale Error                                |                                                                   | —   | ±20              | ±60           | mV     |

| Full-Scale Error Tempco                         |                                                                   | —   | 10               | —             | ppm/°C |

| V <sub>DD</sub> Power Supply Rejection<br>Ratio |                                                                   | -   | -60              | —             | dB     |

| Output Impedance in Shutdown<br>Mode            | DACnEN = 0                                                        | -   | 100              | —             | kΩ     |

| Output Sink Current                             |                                                                   | —   | 300              | —             | μA     |

| Output Short-Circuit Current                    | Data Word = 0xFFF                                                 | —   | 15               | —             | mA     |

| Dynamic Performance                             |                                                                   | •   | 1                |               |        |

| Voltage Output Slew Rate                        | Load = 40 pF                                                      | _   | 0.44             | —             | V/µs   |

| Output Settling Time to 1/2 LSB                 | Load = 40 pF, Output swing from<br>code 0xFFF to 0x014            | -   | 10               | —             | μs     |

| Output Voltage Swing                            |                                                                   | 0   | —                | VREF<br>– LSB | V      |

| Startup Time                                    |                                                                   | —   | 10               | —             | μs     |

| Analog Outputs                                  |                                                                   | 1   |                  |               |        |

| Load Regulation                                 | $I_L = 0.01 \text{ mA to } 0.3 \text{ mA at code}$<br>0xFFF       | _   | 60               | -             | ppm    |

| Power Consumption (each DA                      | C)                                                                |     |                  |               |        |

| Power Supply Current (AV+<br>supplied to DAC)   | Data Word = 0x7FF                                                 | -   | 110              | 400           | μA     |

| R/W      | R/W                          | R/W         | R/W          | R/W           | R/W          | R/W           | R/W                     | Reset Value       |

|----------|------------------------------|-------------|--------------|---------------|--------------|---------------|-------------------------|-------------------|

| -        | -                            | -           | AD0VRS       | AD2VRS        | TEMPE        | BIASE         | REFBE                   | 00000000          |

| Bit7     | Bit6                         | Bit5        | Bit4         | Bit3          | Bit2         | Bit1          | Bit0                    |                   |

|          |                              |             |              |               |              |               | SFR Address<br>SFR Page |                   |

| Bits7-5: | UNUSED. R                    | ead = 000b  | ; Write = do | on't care.    |              |               |                         |                   |

| Bit4:    | AD0VRS: AD                   | OC0 Voltage | e Reference  | e Select      |              |               |                         |                   |

|          | 0: ADC0 volt                 |             |              |               |              |               |                         |                   |

|          | 1: ADC0 volt                 |             |              |               |              |               |                         |                   |

| Bit3:    | AD2VRS: AD                   | •           |              | •             | 051F040/2    | only).        |                         |                   |

|          | 0: ADC2 volt                 | •           |              | •             |              |               |                         |                   |

| D:+0-    | 1: ADC2 volt                 | •           |              |               |              |               |                         |                   |

| Bit2:    | TEMPE: Ten<br>0: Internal Te | •           |              |               |              |               |                         |                   |

|          | 1: Internal Te               | •           |              |               |              |               |                         |                   |

| Bit1:    | BIASE: ADC                   | •           |              |               | Must be '1'  | if using AD   | C or DAC).              |                   |

|          | 0: Internal Bi               |             |              |               |              |               |                         |                   |

|          | 1: Internal Bi               | ias Genera  | tor On.      |               |              |               |                         |                   |

| Bit0:    | REFBE: Inte                  | rnal Refere | ence Buffer  | Enable Bit.   |              |               |                         |                   |

|          | 0: Internal R                | eference B  | uffer Off.   |               |              |               |                         |                   |

|          | 1: Internal R                | eference B  | uffer On. In | ternal voltag | je reference | e is driven o | on the VRE              | <sup>=</sup> pin. |

### SFR Definition 9.1. REF0CN: Reference Control

### Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register                  | Register Address |           | Description                      | Page No. |

|---------------------------|------------------|-----------|----------------------------------|----------|

| SPI0CFG                   | 0x9A             | 0         | SPI Configuration                | page 261 |

| SPI0CKR                   | 0x9D             | 0         | SPI Clock Rate Control           | page 263 |

| SPIOCN                    | 0xF8             | 0         | SPI Control                      | page 262 |

| SPI0DAT                   | 0x9B             | 0         | SPI Data                         | page 264 |

| SSTA0                     | 0x91             | 0         | UART0 Status and Clock Selection | page 275 |

| TCON                      | 0x88             | 0         | Timer/Counter Control            | page 293 |

| TH0                       | 0x8C             | 0         | Timer/Counter 0 High             | page 296 |

| TH1                       | 0x8D             | 0         | Timer/Counter 1 High             | page 296 |

| TL0                       | 0x8A             | 0         | Timer/Counter 0 Low              | page 295 |

| TL1                       | 0x8B             | 0         | Timer/Counter 1 Low              | page 296 |

| TMOD                      | 0x89             | 0         | Timer/Counter Mode               | page 294 |

| TMR2CF                    | 0xC9             | 0         | Timer/Counter 2 Configuration    | page 302 |

| TMR2CN                    | 0xC8             | 0         | Timer/Counter 2 Control          | page 301 |

| TMR2H                     | 0xCD             | 0         | Timer/Counter 2 High             | page 304 |

| TMR2L                     | 0xCC             | 0         | Timer/Counter 2 Low              | page 303 |

| TMR3CF                    | 0xC9             | 1         | Timer/Counter 3 Configuration    | page 302 |

| TMR3CN                    | 0xC8             | 1         | Timer 3 Control                  | page 301 |

| TMR3H                     | 0xCD             | 1         | Timer/Counter 3 High             | page 304 |

| TMR3L                     | 0xCC             | 1         | Timer/Counter 3 Low              | page 303 |

| TMR4CF                    | 0xC9             | 2         | Timer/Counter 4 Configuration    | page 302 |

| TMR4CN                    | 0xC8             | 2         | Timer/Counter 4 Control          | page 301 |

| TMR4H                     | 0xCD             | 2         | Timer/Counter 4 High             | page 304 |

| TMR4L                     | 0xCC             | 2         | Timer/Counter 4 Low              | page 303 |

| WDTCN                     | 0xFF             | All Pages | Watchdog Timer Control           | page 169 |

| XBR0                      | 0xE1             | F         | Port I/O Crossbar Control 0      | page 212 |

| XBR1                      | 0xE2             | F         | Port I/O Crossbar Control 1      | page 213 |

| XBR2                      | 0xE3             | F         | Port I/O Crossbar Control 2      | page 214 |

| XBR3                      | 0xE4             | F         | Port I/O Crossbar Control 3      | page 215 |

| 0x97, 0xA2,<br>0xCE, 0xDF | 0xB3, 0xB4,      |           | Reserved                         |          |

Notes:

1. Refers to a register in the C8051F040 only.

2. Refers to a register in the C8051F041 only.

3. Refers to a register in C8051F040/1/2/3 only.

4. Refers to a register in the C8051F040/2/4/6 only.

5. Refers to a register in the C8051F041/3/5/7 only.

lup and/or decoupling of the /RST pin to avoid erroneous noise-induced resets. The MCU will remain in reset until at least 12 clock cycles after the active-low /RST signal is removed. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

#### **13.4. Missing Clock Detector Reset**

The Missing Clock Detector is essentially a one-shot circuit that is triggered by the MCU system clock. If the system clock goes away for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a Missing Clock Detector reset, the MCDRSF flag (RSTSRC.2) will be set, signifying the MCD as the reset source; otherwise, this bit reads '0'. The state of the /RST pin is unaffected by this reset. Setting the MCDRSF bit, RSTSRC.2 (see Section "14. Oscillators" on page 173) enables the Missing Clock Detector.

#### 13.5. Comparator0 Reset

Comparator0 can be configured as a reset input by writing a '1' to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled using CPT0CN.7 (see Section "11. Comparators" on page 121) prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (CP0+ pin) is less than the inverting input voltage (CP0- pin), the MCU is put into the reset state. After a Comparator0 Reset, the CORSEF flag (RSTSRC.5) will read '1' signifying Comparator0 as the reset source; otherwise, this bit reads '0'. The state of the /RST pin is unaffected by this reset.

#### 13.6. External CNVSTR0 Pin Reset

The external CNVSTR0 signal can be configured as a reset input by writing a '1' to the CNVRSEF flag (RSTSRC.6). The CNVSTR0 signal can appear on any of the P0, P1, P2 or P3 I/O pins as described in Section "**17.1. Ports 0 through 3 and the Priority Crossbar Decoder**" on page **204**. Note that the Crossbar must be configured for the CNVSTR0 signal to be routed to the appropriate Port I/O. The Crossbar should be configured and enabled before the CNVRSEF is set. When configured as a reset, CNVSTR0 is active-low and level sensitive. After a CNVSTR0 reset, the CNVRSEF flag (RSTSRC.6) will read '1' signifying CNVSTR0 as the reset source; otherwise, this bit reads '0'. The state of the /RST pin is unaffected by this reset.

### 13.7. Watchdog Timer Reset

The MCU includes a programmable Watchdog Timer (WDT) running off the system clock. A WDT overflow will force the MCU into the reset state. To prevent the reset, the WDT must be restarted by application software before overflow. If the system experiences a software or hardware malfunction preventing the software from restarting the WDT, the WDT will overflow and cause a reset. This should prevent the system from running out of control.

Following a reset the WDT is automatically enabled and running with the default maximum time interval. If desired the WDT can be disabled by system software or locked on to prevent accidental disabling. Once locked, the WDT cannot be disabled until the next system reset. The state of the /RST pin is unaffected by this reset.

The WDT consists of a 21-bit timer running from the programmed system clock. The timer measures the period between specific writes to its control register. If this period exceeds the programmed limit, a WDT reset is generated. The WDT can be enabled and disabled as needed in software, or can be permanently enabled if desired. Watchdog features are controlled via the Watchdog Timer Control Register (WDTCN) shown in SFR Definition 13.1.

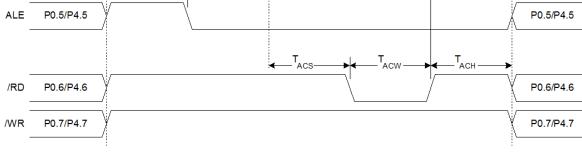

#### 16.4. Multiplexed and Non-multiplexed Selection

The External Memory Interface is capable of acting in a Multiplexed mode or a Non-multiplexed mode, depending on the state of the EMD2 (EMI0CF.4) bit.

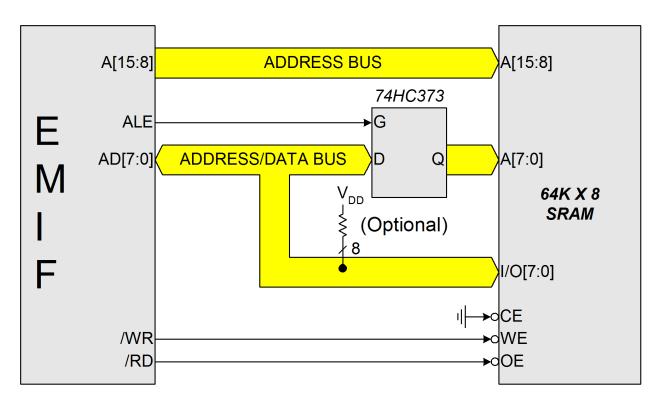

#### 16.4.1. Multiplexed Configuration

In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 16.1.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the 'Q' outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time /RD or /WR is asserted.

Figure 16.1. Multiplexed Configuration Example

# C8051F040/1/2/3/4/5/6/7

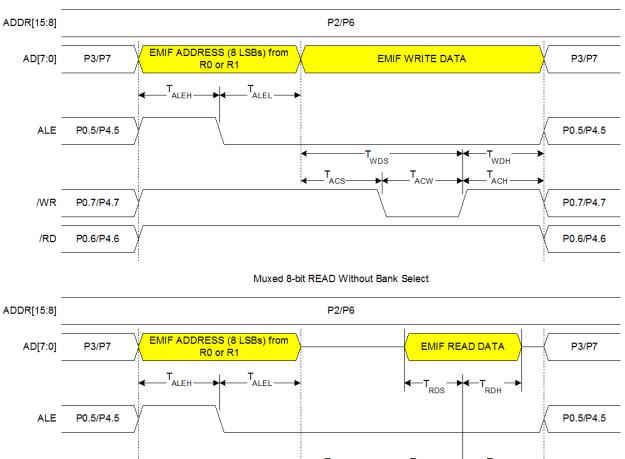

#### 16.6.2.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = '001' or '011'.

Muxed 8-bit WRITE Without Bank Select

#### 18.2.3. Message Handler Registers

The Message Handler Registers are *read only* registers. Their flags can be read via the indexed access method with CAN0ADR, CAN0DATH, and CAN0DATL. The message handler registers provide interrupt, error, transmit/receive requests, and new data information.

Please refer to the Bosch CAN User's Guide for information on the function and use of the Message Handler Registers.

#### 18.2.4. CIP-51 MCU Special Function Registers

C8051F04x family peripherals are modified, monitored, and controlled using Special Function Registers (SFR's). Only three of the CAN Controller's registers may be accessed directly with SFR's. However, all CAN Controller registers can be accessed indirectly using three CIP-51 MCU SFR's: the CAN Data Registers (CAN0DATH and CAN0DATL) and CAN Address Register (CAN0ADR).

#### 18.2.5. Using CAN0ADR, CAN0DATH, and CANDATL to Access CAN Registers

Each CAN Controller Register has an index number (see Table 18.2). The CAN register address space is 128 words (256 bytes). A CAN register is accessed via the CAN Data Registers (CAN0DATH and CAN0-DATL) when a CAN register's index number is placed into the CAN Address Register (CAN0ADR). For example, if the Bit Timing Register is to be configured with a new value, CAN0ADR is loaded with 0x03. The low byte of the desired value is accessed using CAN0DATL and the high byte of the bit timing register is accessed using CAN0DATL is bit addressable for convenience. To load the value 0x2304 into the Bit Timing Register:

CANOADR = 0x03; // Load Bit Timing Register's index (Table 18.1) CANODATH = 0x23; // Move the upper byte into data reg high byte CANODATL = 0x04; // Move the lower byte into data reg low byte

<u>Note:</u> CAN0CN, CAN0STA, and CAN0TST may be accessed either by using the index method, or by direct access with the CIP-51 MCU SFR's. CAN0CN is located at SFR location 0xF8/SFR page 1 (SFR Definition 18.3), CAN0TST at 0xDB/SFR page 1 (SFR Definition 18.4), and CAN0STA at 0xC0/SFR page 1 (SFR Definition 18.5).

#### 18.2.6. CAN0ADR Autoincrement Feature

For ease of programming message objects, CAN0ADR features autoincrementing for the index ranges 0x08 to 0x12 (Interface Registers 1) and 0x20 to 0x2A (Interface Registers 2). When the CAN0ADR register has an index in these ranges, the CAN0ADR will autoincrement by 1 to point to the next CAN register 16-bit word upon a read/write of <u>CAN0DATL</u>. This speeds programming of the frequently-accessed interface registers when configuring message objects.

<u>NOTE:</u> Table 18.2 below supersedes Figure 5 in Section 3, "Programmer's Model" of the Bosch CAN User's Guide.

### SFR Definition 18.1. CAN0DATL: CAN Data Access Register Low Byte

| R/W  | R/W                                                                                | R/W                                                     | R/W                                                        | R/W                                                       | R/W                                                     | R/W                | R/W                                   | Reset Value |

|------|------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------|--------------------|---------------------------------------|-------------|

| Bit7 | Bit6                                                                               | Bit5                                                    | Bit4                                                       | Bit3                                                      | Bit2                                                    | Bit1               | Bit0                                  |             |

|      |                                                                                    |                                                         |                                                            |                                                           | _                                                       |                    | SFR Addres<br>SFR Pag                 |             |

|      | CAN0DATL:<br>The CAN0D/<br>CAN Registe<br>The CAN0AI<br>Register. The<br>CAN0DAT R | AT Register<br>ers pointed<br>DR Registe<br>e desired C | rs are used<br>to with the i<br>r is used to<br>AN Registe | to read/writ<br>ndex numb<br>point the [C<br>r's index nu | e register va<br>er in the CA<br>AN0DATH:<br>mber is mo | N0ADR R<br>CAN0DAT | egister.<br>L] to a desi<br>AN0ADR. 1 | red CAN     |

# SFR Definition 18.2. CAN0ADR: CAN Address Index

| R/W     | R/W                                                                                                                                         | R/W                                                                                                   | R/W                                                                                 | R/W                                                                                        | R/W                                                                 | R/W                                                                                | R/W                                              | Reset Value        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------|--------------------|

| Bit7    | Bit6                                                                                                                                        | Bit5                                                                                                  | Bit4                                                                                | Bit3                                                                                       | Bit2                                                                | Bit1                                                                               | Bit0                                             |                    |

|         |                                                                                                                                             |                                                                                                       |                                                                                     |                                                                                            |                                                                     |                                                                                    | SFR Addres<br>SFR Pag                            |                    |

| Bit7-0: | CAN0ADR: 0<br>The CAN0Al<br>Register. The<br>CAN0DAT R<br><u>Note</u> : When<br>this register<br>"18.2.6. CAI<br>All CAN reg<br>User's Guid | DR Registe<br>e desired C<br>legister can<br>the value o<br>will autoinc<br>NOADR Aut<br>isters' fund | r is used to<br>AN Registe<br>then read/o<br>f CAN0ADF<br>rement by 1<br>toincremer | point the [C<br>pr's index nu<br>write to and<br>R is 0x08-0x<br>upon a wri<br>ht Feature" | mber is mo<br>from the C.<br>12 and 0x2<br>te to CAN0<br>on page 23 | oved into CA<br>AN Registe<br>20-0x2A (IF <sup>-</sup><br>DATL. See<br><b>32</b> . | AN0ADR. 1<br>r.<br>1 and IF2 r<br><b>Section</b> | Гhe<br>registers), |

#### 20.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will wait until the byte is transferred before loading it with the transmit buffer's contents.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 20.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and does not get mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 20.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

#### 20.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

Note: All of the following interrupt bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- 2. The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- 3. The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

## SFR Definition 20.3. SPI0CKR: SPI0 Clock Rate

| R/W              | R/W                                                                                                 | R/W                                                             | R/W                                                         | R/W                         | R/W                      | R/W                         | R/W                     | Reset Value |

|------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------|-----------------------------|--------------------------|-----------------------------|-------------------------|-------------|

| SCR7             | SCR6                                                                                                | SCR5                                                            | SCR4                                                        | SCR3                        | SCR2                     | SCR1                        | SCR0                    |             |

| Bit7             | Bit6                                                                                                | Bit5                                                            | Bit4                                                        | Bit3                        | Bit2                     | Bit1                        | Bit0                    |             |

| Biti             | Бію                                                                                                 | Dito                                                            | DIL                                                         | Dito                        | DILZ                     | Ditt                        | SFR Address<br>SFR Page |             |

| ר<br>f<br>c<br>a | SCR7-SCR0<br>These bits d<br>for master m<br>clock, and is<br>and SPIOCK<br>$s_{SCK} = \frac{1}{2}$ | etermine th<br>ode operat<br>given in th<br><i>R</i> is the 8-b | e frequency<br>ion. The SC<br>e following o<br>it value hel | K clock free<br>equation, w | quency is a<br>here SYSC | divided ver<br>LK is the sy | sion of the             | system      |

| -                | or 0 <= SPI                                                                                         |                                                                 |                                                             | = 0x04,                     |                          |                             |                         |             |

| ;                | $f_{SCK} = \frac{2}{2}$ $f_{SCK} = 20$                                                              | $\frac{2000000}{\times (4+1)}$ $0kHz$                           |                                                             |                             |                          |                             |                         |             |

|                  |                                                                                                     |                                                                 |                                                             |                             |                          |                             |                         |             |

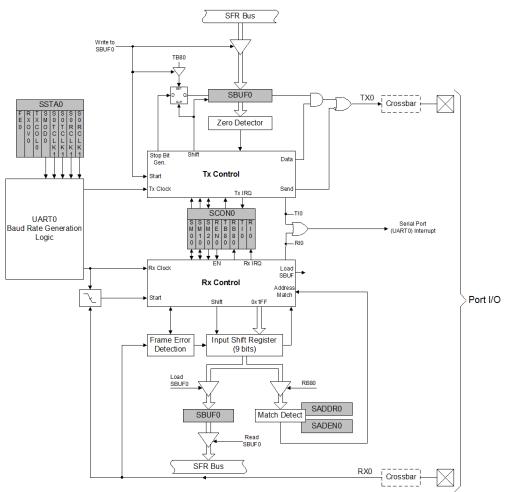

# 21. UART0

UART0 is an enhanced serial port with frame error detection and address recognition hardware. UART0 may operate in full-duplex asynchronous or half-duplex synchronous modes, and mutiproccessor communication is fully supported. Receive data is buffered in a holding register, allowing UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte. A Receive Overrun bit indicates when new received data is latched into the receive buffer before the previously received byte has been read.

UART0 is accessed via its associated SFRs, Serial Control (SCON0) and Serial Data Buffer (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Reading SCON0 accesses the Receive register and writing SCON0 accesses the Transmit register.

UART0 may be operated in polled or interrupt mode. UART0 has two sources of interrupts: a Transmit Interrupt flag, TI0 (SCON0.1) set when transmission of a data byte is complete, and a Receive Interrupt flag, RI0 (SCON0.0) set when reception of a data byte is complete. UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine; they must be cleared manually by software. This allows software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

Figure 21.1. UART0 Block Diagram

#### 21.1.4. Mode 3: 9-Bit UART, Variable Baud Rate

Mode 3 uses the Mode 2 transmission protocol with the Mode 1 baud rate generation. Mode 3 operation transmits 11 bits: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The baud rate is derived from Timer 1 or Timer 2, 3, or 4 overflows, as defined by Equation 21.1 and Equation 21.3. Multiprocessor communications and hardware address recognition are supported, as described in **Section 21.2**.

#### 21.2. Multiprocessor Communications

Modes 2 and 3 support multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit and the built-in UART0 address recognition hardware. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0. UART0 will recognize as "valid" (i.e., capable of causing an interrupt) **two** types of addresses: (1) a *masked* address and (2) a *broadcast* address **at any given time**. Both are described below.

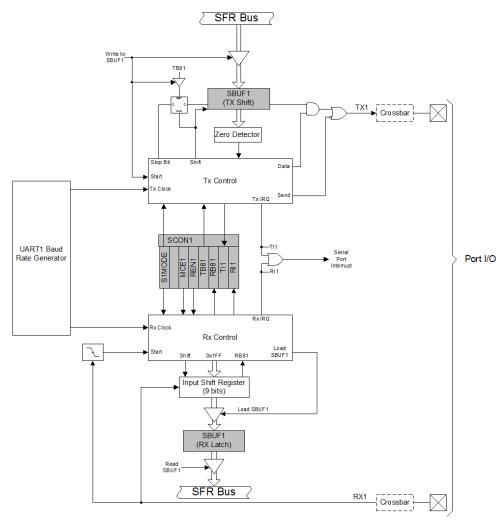

# 22. UART1

UART1 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in **Section "22.1. Enhanced Baud Rate Generation" on page 278**). Received data buffering allows UART1 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART1 has two associated SFRs: Serial Control Register 1 (SCON1) and Serial Data Buffer 1 (SBUF1). The single SBUF1 location provides access to both transmit and receive registers. Reading SBUF1 accesses the buffered Receive register; writing SBUF1 accesses the Transmit register.

With UART1 interrupts enabled, an interrupt is generated each time a transmit is completed (TI1 is set in SCON1), or a data byte has been received (RI1 is set in SCON1). The UART1 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART1 interrupt (transmit complete or receive complete).

# C8051F040/1/2/3/4/5/6/7

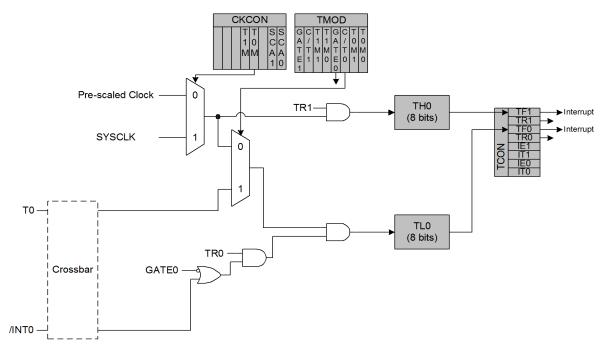

#### 23.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/ timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 23.3. T0 Mode 3 Block Diagram

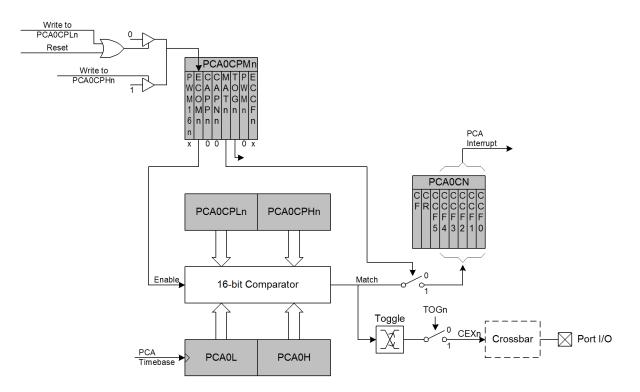

#### 24.2.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode.

**Important Note About Capture/Compare Registers:** When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 24.6. PCA High-Speed Output Mode Diagram