Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 32                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 8x8b, 13x10b; D/A 2x10b, 2x12b                                |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

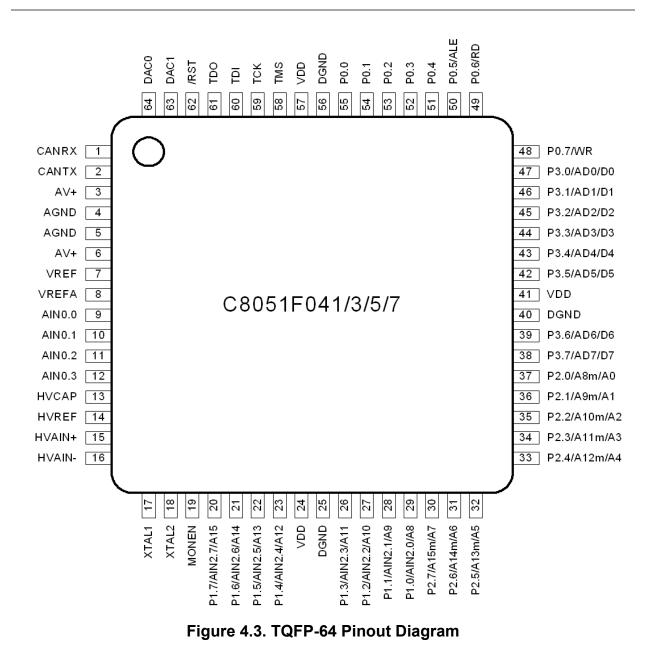

| Package / Case             | 64-TQFP                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f043-gqr   |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F040/1/2/3/4/5/6/7

NOTES:

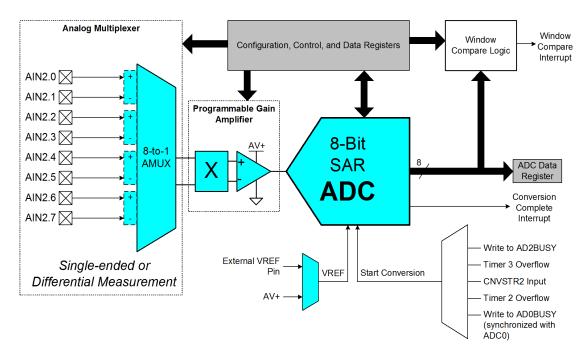

# 1.9. 8-Bit Analog to Digital Converter (C8051F040/1/2/3 Only)

The C8051F040/1/2/3 devices have an on-board 8-bit SAR ADC (ADC2) with an 8-channel input multiplexer and programmable gain amplifier. This ADC features a 500 ksps maximum throughput and true 8-bit performance with an INL of ±1LSB. Eight input pins are available for measurement and can be programmed as single-ended or differential inputs. The ADC is under full control of the CIP-51 microcontroller via the Special Function Registers. The ADC2 voltage reference is selected between the analog power supply (AV+) and an external VREF pin. On C8051F040/2 devices, ADC2 has its own dedicated VREF2 input pin; on C8051F041/3 devices, ADC2 shares the VREFA input pin with the 12/10-bit ADC0. User software may put ADC2 into shutdown mode to save power.

A programmable gain amplifier follows the analog multiplexer. The gain stage can be especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large dc offset (in differential mode, a DAC could be used to provide the dc offset). The PGA gain can be set in software to 0.5, 1, 2, or 4.

A flexible conversion scheduling system allows ADC2 conversions to be initiated by software commands, timer overflows, or an external input signal. ADC2 conversions may also be synchronized with ADC0 software-commanded conversions. Conversion completions are indicated by a status bit and an interrupt (if enabled), and the resulting 8-bit data word is latched into an SFR upon completion.

Figure 1.13. 8-Bit ADC Diagram

# C8051F040/1/2/3/4/5/6/7

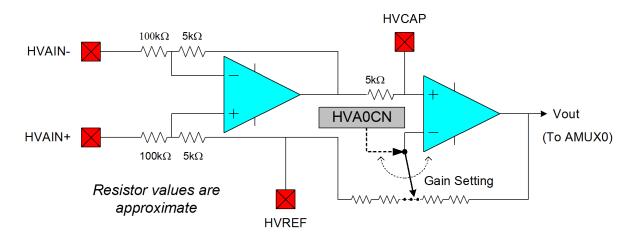

# 5.2. High-Voltage Difference Amplifier

The High Voltage Difference Amplifier (HVDA) can be used to measure high differential voltages up to 60 V peak-to-peak, reject high common-mode voltages up to ±60 V, and condition the signal voltage range to be suitable for input to ADC0. The input signal to the HVDA may be below AGND to –60 volts, and as high as +60 volts, making the device suitable for both single and dual supply applications. The HVDA provides a common-mode signal for the ADC via the High Voltage Reference Input (HVREF), allowing measurement of signals outside the specified ADC input range using on-chip circuitry. The HVDA has a gain of 0.05 V/V to 14 V/V. The first stage 20:1 difference amplifier has a gain of 0.05 V/V when the output amplifier is used as a unity gain buffer. When the output amplifier is set to a gain of 280 (selected using the HVGAIN bits in the High Voltage Control Register), an overall gain of 14 can be attained.

The HVDA uses four available external pins: +HVAIN, –HVAIN, HVCAP, and HVREF. HVAIN+ and HVAINserve as the differential inputs to the HVDA. HVREF should be used to provide a common mode reference for input to ADC0, and to prevent the output of the HVDA circuit from saturating. The output from the HVDA circuit as calculated by Equation 5.1 must remain within the "Output Voltage Range" specification listed in Table 5.3. The ideal value for HVREF in most applications is equal to 1/2 the supply voltage for the device. When the ADC is configured for differential measurement, the HVREF signal is applied to the AINinput of the ADC, thereby removing HVREF from the measurement. HVCAP facilitates the use of a capacitor for noise filtering in conjunction with R7 (see Figure 5.3 for R7 and other approximate resistor values). Alternatively, the HVCAP could also be used to access amplification of the first stage of the HVDA at an external pin. (See Table 5.3 on page 68 for electrical specifications of the HVDA.)

$$V_{OUT} = [(HVAIN+) - (HVAIN-)] \cdot Gain + HVREF$$

**Note:** The output voltage of the HVDA is selected as an input to the AIN+ input of ADC0 via its analog multiplexer (AMUX0). HVDA output voltages outside the ADC's input range will result in saturation of the ADC input. Allow for adequate settle/tracking time for proper voltage measurements.

Equation 5.1. Calculating HVDA Output Voltage to AIN+

# Figure 5.3. High Voltage Difference Amplifier Functional Diagram

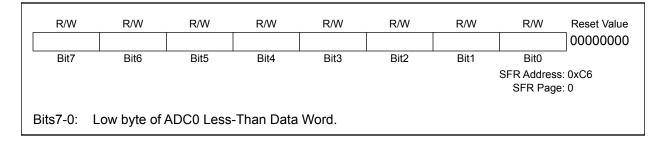

## SFR Definition 5.12. ADC0LTL: ADC0 Less-Than Data Low Byte

| Input Voltage<br>(AD0 - AGND)                                                                                                                        | ADC Data<br>Word                                                      |                                                   | Input Voltage<br>(AD0 - AGND)                                                                                                                                | ADC Data<br>Word                                                    |                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------|

| REF x (4095/4096)                                                                                                                                    | 0x0FFF                                                                |                                                   | REF x (4095/4096)                                                                                                                                            | 0x0FFF                                                              |                                                 |

|                                                                                                                                                      |                                                                       | AD0WINT<br>not affected                           |                                                                                                                                                              |                                                                     | AD0WINT=1                                       |

|                                                                                                                                                      | 0x0201                                                                |                                                   |                                                                                                                                                              | 0x0201                                                              |                                                 |

| REF x (512/4096)                                                                                                                                     | 0x0200                                                                | ADC0LTH:ADC0LTL                                   | REF x (512/4096)                                                                                                                                             | 0x0200                                                              | ADC0GTH:ADC0GTL                                 |

|                                                                                                                                                      | 0x01FF                                                                | AD0WINT=1                                         |                                                                                                                                                              | 0x01FF                                                              | ADOWINT                                         |

|                                                                                                                                                      | 0x0101                                                                | ADOWINT-T                                         |                                                                                                                                                              | 0x0101                                                              | not affected                                    |

| REF x (256/4096)                                                                                                                                     | 0x0100                                                                | ADC0GTH:ADC0GTL                                   | REF x (256/4096)                                                                                                                                             | 0x0100                                                              | ADC0LTH:ADC0LTL                                 |

|                                                                                                                                                      | 0x00FF                                                                | AD0WINT<br>not affected                           |                                                                                                                                                              | 0x00FF                                                              | > ADOWINT=1                                     |

| 0                                                                                                                                                    | 0x0000                                                                |                                                   | 0                                                                                                                                                            | 0x0000                                                              | J                                               |

| Given:<br>AMX0SL = 0x00<br>AD0LJST = '0',<br>ADC0LTH:ADC0<br>ADC0GTH:ADC<br>An ADC0 End of<br>ADC0 Window 0<br>= '1') if the resul<br>< 0x0200 and > | DLTL = 0x02<br>0GTL = 0x0<br>Conversion<br>Compare Int<br>ting ADC0 [ | 00,<br>100.<br>n will cause an<br>errupt (AD0WINT | Given:<br>AMX0SL = 0x00,<br>AD0LJST = '0',<br>ADC0LTH:ADC0I<br>ADC0GTH:ADC0I<br>An ADC0 End of<br>ADC0 Window C<br>= '1') if the resulti<br>> 0x0200 or < 0x | _TL = 0x010<br>GTL = 0x02<br>Conversion<br>ompare Inte<br>ng ADC0 D | 00,<br>200.<br>will cause an<br>errupt (AD0WINT |

#### Figure 5.8. 12-Bit ADC0 Window Interrupt Example: Right Justified Single-Ended Data

| R/W      | R/W                              | R/W        | R/W           | R/W           | R/W          | R/W           | R/W                     | Reset Value |

|----------|----------------------------------|------------|---------------|---------------|--------------|---------------|-------------------------|-------------|

| -        | -                                | -          | AD0VRS        | AD1VRS        | TEMPE        | BIASE         | REFBE                   | 00000000    |

| Bit7     | Bit6                             | Bit5       | Bit4          | Bit3          | Bit2         | Bit1          | Bit0                    | -           |

|          |                                  |            |               |               |              |               | SFR Address<br>SFR Page |             |

| Bits7-5: | UNUSED. R                        | ead = 000k | o: Write = do | on't care.    |              |               |                         |             |

| Bit4:    | AD0VRS: AD                       |            |               |               |              |               |                         |             |

|          | 0: ADC0 volt                     | age refere | nce from VF   | REFA pin.     |              |               |                         |             |

|          | 1: ADC0 volt                     | age refere | nce from DA   | AC0 output (  | C8051F04     | 1/3 only).    |                         |             |

| Bit3:    | AD2VRS: AD                       | •          |               | •             | 051F041/3    | only).        |                         |             |

|          | 0: ADC2 volt                     | -          |               | •             |              |               |                         |             |

| DIIO     | 1: ADC2 volt                     | •          |               |               |              |               |                         |             |

| Bit2:    | TEMPE: Tem                       | •          |               |               |              |               |                         |             |

|          | 0: Internal Te<br>1: Internal Te | •          |               |               |              |               |                         |             |

| Bit1:    | BIASE: ADC                       | •          |               |               | 'Must ha '1' | if using AD   | (C  or  DAC)            |             |

| Ditt.    | 0: Internal Bi                   |            |               |               |              |               | 0 01 DAO).              |             |

|          | 1: Internal Bi                   |            |               |               |              |               |                         |             |

| Bit0:    | REFBE: Inte                      |            |               | Enable Bit.   |              |               |                         |             |

|          | 0: Internal R                    | eference B | uffer Off.    |               |              |               |                         |             |

|          | 1: Internal R                    | oforonoo D | uffor On Int  | tornal valtas | faranaa      | , in driven a |                         |             |

### SFR Definition 10.1. REF0CN: Reference Control

#### Table 14.1. Internal Oscillator Electrical Characteristics

-40 to +85 °C unless otherwise specified.

| Parameter                                           | Conditions   | Min | Тур  | Max | Units |

|-----------------------------------------------------|--------------|-----|------|-----|-------|

| Calibrated Internal Oscillator<br>Frequency         |              | 24  | 24.5 | 25  | MHz   |

| Internal Oscillator Supply Current (from $V_{DD}$ ) | OSCICN.7 = 1 | _   | 450  | _   | μA    |

| External Clock Frequency                            |              | 0   | —    | 30  | MHz   |

| T <sub>XCH</sub> (External Clock High Time)         |              | 15  |      | _   | ns    |

| T <sub>XCL</sub> (External Clock Low Time)          |              | 15  |      | _   | ns    |

#### 14.2. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/ resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 14.1. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 and/or XTAL1 pin(s) as shown in Option 2, 3, or 4 of Figure 14.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 14.4).

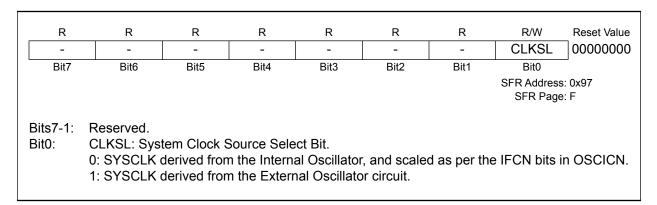

### 14.3. System Clock Selection

The CLKSL bit in register CLKSEL selects which oscillator is used as the system clock. CLKSL must be set to '1' for the system clock to run from the external oscillator; however the external oscillator may still clock peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal and external oscillator, so long as the selected oscillator is enabled and has settled. The internal oscillator requires little start-up time and may be enabled and selected as the system clock in the same write to OSCICN. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use as the system clock. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external oscillator is settled. To avoid reading a false XTLVLD in crystal mode, software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD. RC and C modes typically require no startup time.

# SFR Definition 14.3. CLKSEL: Oscillator Clock Selection

| Parameter           | Description                    | Min                     | Мах                      | Units |

|---------------------|--------------------------------|-------------------------|--------------------------|-------|

| T <sub>SYSCLK</sub> | System Clock Period            | 40                      |                          | ns    |

| T <sub>ACS</sub>    | Address/Control Setup Time     | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ACW</sub>    | Address/Control Pulse Width    | 1 x T <sub>SYSCLK</sub> | 16 x T <sub>SYSCLK</sub> | ns    |

| T <sub>ACH</sub>    | Address/Control Hold Time      | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEH</sub>   | Address Latch Enable High Time | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEL</sub>   | Address Latch Enable Low Time  | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>WDS</sub>    | Write Data Setup Time          | 1 x T <sub>SYSCLK</sub> | 19 x T <sub>SYSCLK</sub> | ns    |

| T <sub>WDH</sub>    | Write Data Hold Time           | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>RDS</sub>    | Read Data Setup Time           | 20                      |                          | ns    |

| T <sub>RDH</sub>    | Read Data Hold Time            | 0                       |                          | ns    |

Table 16.1. AC Parameters for External Memory Interface

# 17. Port Input/Output

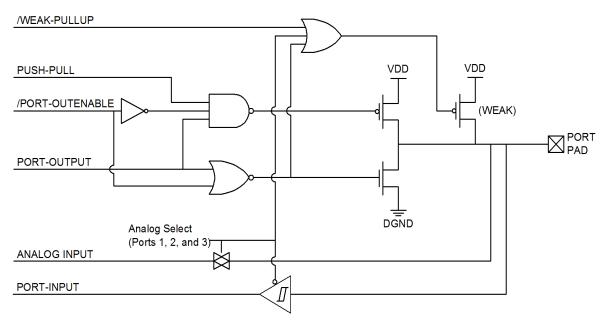

The C8051F04x family of devices are fully integrated mixed-signal System on a Chip MCUs with 64 digital I/O pins (C8051F040/2/4/6) or 32 digital I/O pins (C8051F041/3/5/7), organized as 8-bit Ports. All ports are both bit- and byte-addressable through their corresponding Port Data registers. All Port pins are 5 V-tolerant, and all support configurable Open-Drain or Push-Pull output modes and weak pullups. A block diagram of the Port I/O cell is shown in Figure 17.1. Complete Electrical Specifications for the Port I/O pins are given in Table 17.1.

Figure 17.1. Port I/O Cell Block Diagram

### Table 17.1. Port I/O DC Electrical Characteristics

$V_{DD}$  = 2.7 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                | Conditions                                        | Min                   | Тур                   | Мах                   | Units |

|--------------------------|---------------------------------------------------|-----------------------|-----------------------|-----------------------|-------|

| Output High Voltage      | I <sub>OH</sub> = –3 mA, Port I/O Push-Pull       | V <sub>DD</sub> – 0.7 | _                     |                       |       |

| (V <sub>OH</sub> )       | I <sub>OH</sub> = –10 μA, Port I/O Push-Pull      | V <sub>DD</sub> – 0.1 |                       | _                     | V     |

| (VOH)                    | I <sub>OH</sub> = –10 mA, Port I/O Push-Pull      | —                     | V <sub>DD</sub> – 0.8 |                       |       |

|                          | I <sub>OL</sub> = 8.5 mA                          | _                     | _                     | 0.6                   |       |

| Output Low Voltage       | I <sub>OL</sub> = 10 μA                           | _                     | —                     | 0.1                   | V     |

| (V <sub>OL</sub> )       | I <sub>OL</sub> = 25 mA                           | _                     | 1.0                   | _                     |       |

| Input High Voltage (VIH) |                                                   | 0.7 x V <sub>DD</sub> | —                     | —                     |       |

| Input Low Voltage (VIL)  |                                                   | —                     | —                     | 0.3 x V <sub>DD</sub> |       |

|                          | DGND < Port Pin < V <sub>DD</sub> , Pin Tri-state | —                     | —                     | —                     |       |

| Input Leakage Current    | Weak Pullup Off                                   | _                     | —                     | ± 1                   | μA    |

|                          | Weak Pullup On                                    |                       | 10                    |                       |       |

| Input Capacitance        |                                                   |                       | 5                     |                       | pF    |

# C8051F040/1/2/3/4/5/6/7

## SFR Definition 17.6. P0MDOUT: Port0 Output Mode

| R/W      | R/W                                                                                                                                                                                           | R/W  | R/W  | R/W  | R/W  | R/W  | R/W          | Reset Value |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|--------------|-------------|--|--|--|

|          |                                                                                                                                                                                               |      |      |      |      |      |              | 00000000    |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                          | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0         |             |  |  |  |

|          |                                                                                                                                                                                               |      |      |      |      |      | SFR Address  | s: 0xA4     |  |  |  |

|          |                                                                                                                                                                                               |      |      |      |      |      | SFR Page     | e: F        |  |  |  |

| Bits7-0: | <ul> <li>its7-0: P0MDOUT.[7:0]: Port0 Output Mode Bits.</li> <li>0: Port Pin output mode is configured as Open-Drain.</li> <li>1: Port Pin output mode is configured as Push-Pull.</li> </ul> |      |      |      |      |      |              |             |  |  |  |

| Note:    | SDA, SCL, ar<br>always config                                                                                                                                                                 | •    |      |      | ,    | •    | ART1 is in M | lode 0) are |  |  |  |

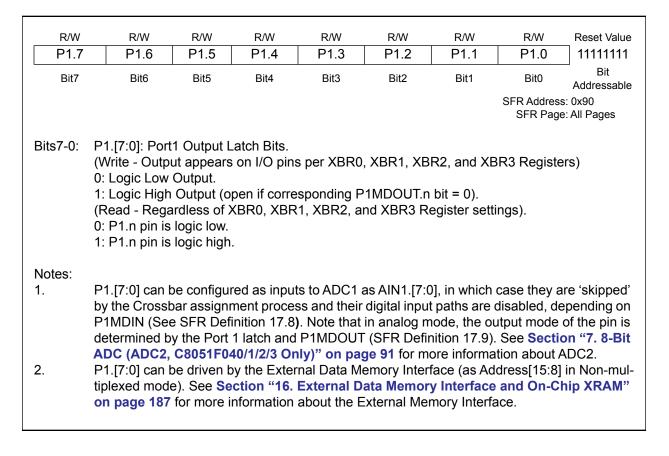

# SFR Definition 17.7. P1: Port1 Data

| R/W      | R/W                                                                                                                                                                              | R/W                                                                                                            | R/W                                                                              | R/W                       | R/W         | R/W          | R/W                     | Reset Value        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------|-------------|--------------|-------------------------|--------------------|

| P4.7     | P4.6                                                                                                                                                                             | P4.5                                                                                                           | P4.4                                                                             | P4.3                      | P4.2        | P4.1         | P4.0                    | 11111111           |

| Bit7     | Bit6                                                                                                                                                                             | Bit5                                                                                                           | Bit4                                                                             | Bit3                      | Bit2        | Bit1         | Bit0                    | Bit<br>Addressable |

|          |                                                                                                                                                                                  |                                                                                                                |                                                                                  |                           |             |              | SFR Address<br>SFR Page |                    |

| Bits7-0: | P4.[7:0]: Port<br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>17.17.<br>Read - Retur<br>0: P4.n pin is<br>1: P4.n pin is<br>Note: P4.7 (/<br>Interface. Se<br>page 187 for | ut appears<br>Output.<br>Output (C<br>ns states o<br>logic low.<br>logic high<br>WR), P4.6<br>e <b>Section</b> | on I/O pins<br>Open-Drain i<br>of I/O pins.<br>(/RD), and<br><b>"16. Exter</b> i | f correspon<br>P4.5 (ALE) | can be driv | ven by the E | External Dat            | a Memory           |

# SFR Definition 17.16. P4: Port4 Data

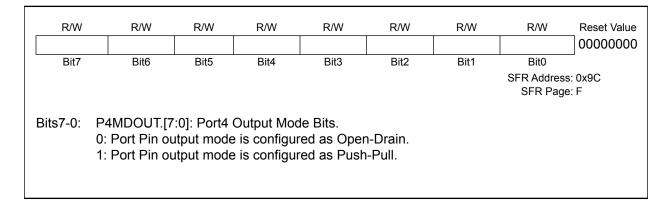

### SFR Definition 17.17. P4MDOUT: Port4 Output Mode

#### 18.1.1. CAN Controller Timing

The CAN controller's system clock ( $f_{sys}$ ) is derived from the CIP-51 system clock (SYSCLK). Note that an external oscillator (such as a quartz crystal) is typically required due to the high accuracy requirements for CAN communication. Refer to Section "4.10.4 Oscillator Tolerance Range" in the Bosch CAN User's Guide for further information regarding this topic.

#### 18.1.2. Example Timing Calculation for 1 Mbit/Sec Communication

This example shows how to configure the CAN contoller timing parameters for a 1 Mbit/Sec bit rate. Table 18.1 shows timing-related system parameters needed for the calculation.

| Parameter                                          | Value       | Description                                                                                                                |

|----------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------|

| CIP-51 system clock (SYSCLK)                       | 22.1184 MHz | External oscillator in 'Crystal Oscillator Mode'. A<br>22.1184 MHz quartz crystal is connected between<br>XTAL1 and XTAL2. |

| CAN Controller system clock<br>(f <sub>sys</sub> ) | 22.1184 MHz | Derived from SYSCLK.                                                                                                       |

| CAN clock period (t <sub>sys</sub> )               | 45.211 ns   | Derived from 1/f <sub>sys</sub> .                                                                                          |

| CAN time quantum (t <sub>q</sub> )                 | 45.211 ns   | Derived from t <sub>sys</sub> x BRP <sup>1,2</sup>                                                                         |

| CAN bus length                                     | 10 m        | 5 ns/m signal delay between CAN nodes.                                                                                     |

| Propagation delay time <sup>3</sup>                | 400 ns      | 2 x (transceiver loop delay + bus line delay)                                                                              |

# Table 18.1. Background System Information

Notes:

1. The CAN time quantum (t<sub>q</sub>) is the smallest unit of time recognized by the CAN contoller. Bit timing parameters are often specified in integer multiples of the time quantum.

2. The Baud Rate Prescaler (BRP) is defined as the value of the BRP Extension Register plus 1. The BRP Extension Register has a reset value of 0x0000; the Baud Rate Prescaler has a reset value of 1.

3. Based on an ISO-11898 compliant transceiver. CAN does not specify a physical layer.

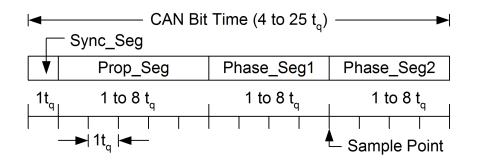

Each bit transmitted on a CAN network has 4 segments (Sync\_Seg, Prop\_Seg, Phase\_Seg1, and Phase\_Seg2), as shown in Figure 18.3. The sum of these segments determines the CAN bit time (1/bit rate). In this example, the desired bit rate is 1 Mbit/sec; therefore, the desired bit time is 1000 ns.

Figure 18.3. Four Segments of a CAN Bit Time

| Mode               | Status<br>Code                                   | SMBus State                                   | Typical Action                                                                                                                   |  |  |

|--------------------|--------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ъъ                 | 0x08                                             | START condition transmitted.                  | Load SMB0DAT with Slave Address +<br>R/W. Clear STA.                                                                             |  |  |

| MT<br>MR           | 0x10                                             | Repeated START condition transmitted.         | Load SMB0DAT with Slave Address +<br>R/W. Clear STA.                                                                             |  |  |

|                    | 0x18                                             | Slave Address + W transmitted. ACK received.  | Load SMB0DAT with data to be transmit-<br>ted.                                                                                   |  |  |

| mitter             | 0x20                                             | Slave Address + W transmitted. NACK received. | Acknowledge poll to retry. Set STO + STA.                                                                                        |  |  |

| Master Transmitter | 0x28                                             | Data byte transmitted. ACK received.          | <ol> <li>Load SMB0DAT with next byte, OR</li> <li>Set STO, OR</li> <li>Clear STO then set STA for repeated<br/>START.</li> </ol> |  |  |

| Mas                | 0x30                                             | Data byte transmitted. NACK received.         | 1) Retry transfer OR<br>2) Set STO.                                                                                              |  |  |

|                    | 0x38                                             | Arbitration Lost.                             | Save current data.                                                                                                               |  |  |

| eiver              | 0x40 Slave Address + R transmitted. ACK received |                                               | If only receiving one byte, clear AA (send NACK after received byte). Wait for received data.                                    |  |  |

| r Rec              | 0x48                                             | Slave Address + R transmitted. NACK received. | Acknowledge poll to retry. Set STO + STA.                                                                                        |  |  |

| Master Receiver    | 0x50                                             | Data byte received. ACK transmitted.          | Read SMB0DAT. Wait for next byte. If next byte is last byte, clear AA.                                                           |  |  |

|                    | 0x58                                             | Data byte received. NACK transmitted.         | Set STO.                                                                                                                         |  |  |

# Table 19.1. SMB0STA Status Codes and States

| Mode              | Status<br>Code                                                                                     | SMBus State                                                                                                | Typical Action                                                                    |  |  |

|-------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|

|                   | 0x60                                                                                               | Own slave address + W received. ACK trans-<br>mitted.                                                      | Wait for data.                                                                    |  |  |

|                   | 0x68                                                                                               | Arbitration lost in sending SLA + R/W as mas-<br>ter. Own address + W received. ACK transmit-<br>ted.      | Save current data for retry when bus is free. Wait for data.                      |  |  |

| <u> </u>          | 0x70                                                                                               | General call address received. ACK transmit-<br>ted.                                                       | Wait for data.                                                                    |  |  |

| Slave Receiver    | 0x78                                                                                               | Arbitration lost in sending SLA + R/W as mas-<br>ter. General call address received. ACK trans-<br>mitted. | Save current data for retry when bus is free.                                     |  |  |

| Slave             | 0x80     Data byte received. ACK transmitted.       0x88     Data byte received. NACK transmitted. |                                                                                                            | Read SMB0DAT. Wait for next byte or STOP.                                         |  |  |

| 0,                |                                                                                                    |                                                                                                            | Set STO to reset SMBus.                                                           |  |  |

|                   | 0x90                                                                                               | Data byte received after general call address.<br>ACK transmitted.                                         | Read SMB0DAT. Wait for next byte or STOP.                                         |  |  |

|                   | 0x98                                                                                               | Data byte received after general call address.<br>NACK transmitted.                                        | Set STO to reset SMBus.                                                           |  |  |

|                   | 0xA0                                                                                               | STOP or repeated START received.                                                                           | No action necessary.                                                              |  |  |

| _                 | 0xA8                                                                                               | Own address + R received. ACK transmitted.                                                                 | Load SMB0DAT with data to transmit.                                               |  |  |

| Slave Transmitter | 0xB0                                                                                               | Arbitration lost in transmitting SLA + R/W as<br>master. Own address + R received. ACK<br>transmitted.     | Save current data for retry when bus is free. Load SMB0DAT with data to transmit. |  |  |

| Tra               | 0xB8                                                                                               | Data byte transmitted. ACK received.                                                                       | Load SMB0DAT with data to transmit.                                               |  |  |

| ave               | 0xC0                                                                                               | Data byte transmitted. NACK received.                                                                      | Wait for STOP.                                                                    |  |  |

| S                 | 0xC8                                                                                               | Last data byte transmitted (AA=0). ACK received.                                                           | Set STO to reset SMBus.                                                           |  |  |

| Slave             | 0xD0                                                                                               | SCL Clock High Timer per SMB0CR timed out                                                                  | Set STO to reset SMBus.                                                           |  |  |

| _                 | 0x00                                                                                               | Bus Error (illegal START or STOP)                                                                          | Set STO to reset SMBus.                                                           |  |  |

| A                 | 0xF8                                                                                               | Idle                                                                                                       | State does not set SI.                                                            |  |  |

Table 19.1. SMB0STA Status Codes and States (Continued)

| R/W       | R/W                                                                                                                   | R/W                                                                                   | R/W                                                                                     | R/W                                                           | R/W                                           | R                            | R/W                         | Reset Value        |

|-----------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------|------------------------------|-----------------------------|--------------------|

| SPIF      | WCOL                                                                                                                  | MODF                                                                                  | RXOVRN                                                                                  | NSSMD1                                                        | NSSMD0                                        | TXBMT                        | SPIEN                       | 00000110           |

| Bit7      | Bit6                                                                                                                  | Bit5                                                                                  | Bit4                                                                                    | Bit3                                                          | Bit2                                          | Bit1                         | Bit0                        | Bit<br>Addressable |

|           |                                                                                                                       |                                                                                       |                                                                                         |                                                               |                                               |                              | SFR Address<br>SFR Page     | : 0xF8             |

| Bit 7:    | SPIF: SPI0 I<br>This bit is se<br>setting this b<br>automatically                                                     | t to logic 1<br>bit causes th                                                         | by hardwar<br>ne CPU to v                                                               | ector to the                                                  | SPI0 interr                                   | upt service                  |                             |                    |

| Bit 6:    | WCOL: Write<br>This bit is se<br>the SPI0 dat<br>cleared by se                                                        | e Collision<br>t to logic 1<br>a register v                                           | Flag.<br>by hardwar                                                                     | e (and gene                                                   | erates a SPI                                  | 0 interrupt)                 |                             |                    |

| Bit 5:    | MODF: Mod<br>This bit is se<br>collision is de<br>matically cle                                                       | e Fault Flag<br>t to logic 1<br>etected (NS                                           | by hardwar<br>SS is low, M                                                              | STEN = 1,                                                     | and NSSME                                     | D[1:0] = 01)                 |                             |                    |

| Bit 4:    | RXOVRN: R<br>This bit is se<br>buffer still ho<br>is shifted into<br>must be clear                                    | eceive Ove<br>t to logic 1<br>olds unread<br>o the SPI0<br>ared by soft               | errun Flag (S<br>by hardwar<br>data from a<br>shift registe<br>ware.                    | Slave Mode<br>e (and gene<br>a previous ti<br>r. This bit is  | only).<br>erates a SPI<br>ransfer and         | 0 interrupt)<br>the last bit | of the curre                | nt transfer        |

| Bits 3-2: | NSSMD1-NS<br>Selects betw<br>(See Section<br>Slave Mode<br>00: 3-Wire S<br>01: 4-Wire S<br>1x: 4-Wire S<br>assume the | veen the fol<br>n "20.2. SF<br>Operation<br>lave or 3-w<br>lave or Mul<br>ingle-Maste | lowing NSS<br>PIO Master M<br>" on page<br>tire Master I<br>Iti-Master M<br>er Mode. NS | operation (<br>Mode Opera<br>259).<br>Mode. NSS<br>ode (Defau | ation" on pa<br>signal is no<br>lt). NSS is a | t routed to<br>Ilways an ir  | a port pin.<br>put to the c | levice.            |

| Bit 1:    | TXBMT: Tran<br>This bit will b<br>data in the tr<br>indicating that                                                   | be set to log<br>ansmit buff<br>at it is safe                                         | gic 0 when r<br>er is transfe                                                           | erred to the                                                  | SPI shift reg                                 | gister, this b               |                             |                    |

| Bit 0:    | SPIEN: SPIC<br>This bit enab<br>0: SPI disab<br>1: SPI enabl                                                          | oles/disable<br>led.                                                                  | es the SPI.                                                                             |                                                               |                                               |                              |                             |                    |

# SFR Definition 20.2. SPI0CN: SPI0 Control

#### 22.2. Operational Modes

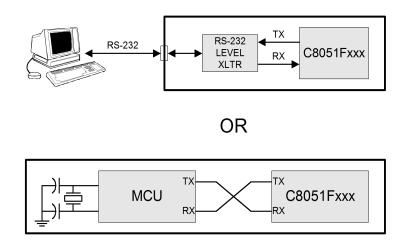

UART1 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S1MODE bit (SCON1.7). Typical UART connection options are shown below.

Figure 22.3. UART Interconnect Diagram

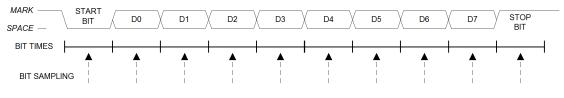

#### 22.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX1 pin and received at the RX1 pin. On receive, the eight data bits are stored in SBUF1 and the stop bit goes into RB81 (SCON1.2).

Data transmission begins when software writes a data byte to the SBUF1 register. The TI1 Transmit Interrupt Flag (SCON1.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN1 Receive Enable bit (SCON1.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF1 receive register if the following conditions are met: RI1 must be logic 0, and if MCE1 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF1 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF1, the stop bit is stored in RB81 and the RI1 flag is set. If these conditions are not met, SBUF1 and RB81 will not be loaded and the RI1 flag will not be set. An interrupt will occur if enabled when either TI1 or RI1 is set.

Figure 22.4. 8-Bit UART Timing Diagram

| R/W    | R/W                                                                                                                                                                                                                                                                                                                                                                                | R/W                        | R/W                          | R/W                    | R/W                                          | R/W          | R/W                   | Reset Value        |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|------------------------|----------------------------------------------|--------------|-----------------------|--------------------|--|--|--|

| S1MODE | Ξ -                                                                                                                                                                                                                                                                                                                                                                                | MCE1                       | REN1                         | TB81                   | RB81                                         | TI1          | RI1                   | 0100000            |  |  |  |

| Bit7   | Bit6                                                                                                                                                                                                                                                                                                                                                                               | Bit5                       | Bit4                         | Bit3                   | Bit2                                         | Bit1         | Bit0                  | Bit<br>Addressable |  |  |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                    |                            |                              |                        |                                              |              | SFR Addres<br>SFR Pag |                    |  |  |  |

| Bit7:  | S1MODE: S<br>This bit sele<br>0: Mode 0: 8<br>1: Mode 1: 9                                                                                                                                                                                                                                                                                                                         | ects the UAF<br>8-bit UART | RT1 Operati<br>with Variable | on Mode.<br>e Baud Rat |                                              |              |                       |                    |  |  |  |

| Bit6:  | UNUSED. F                                                                                                                                                                                                                                                                                                                                                                          |                            |                              |                        |                                              |              |                       |                    |  |  |  |

| Bit5:  | MCE1: Multiprocessor Communication Enable.                                                                                                                                                                                                                                                                                                                                         |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | The function of this bit is dependent on the Serial Port 0 Operation Mode.                                                                                                                                                                                                                                                                                                         |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | Mode 0: Checks for valid stop bit.                                                                                                                                                                                                                                                                                                                                                 |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | 0: Logic level of stop bit is ignored.                                                                                                                                                                                                                                                                                                                                             |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | 1: RI1 will only be activated if stop bit is logic level 1.<br>Mode 1: Multiprocessor Communications Enable.                                                                                                                                                                                                                                                                       |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | 0: Logic level of ninth bit is ignored.                                                                                                                                                                                                                                                                                                                                            |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | 1: RI1 is set and an interrupt is generated only when the ninth bit is logic 1.                                                                                                                                                                                                                                                                                                    |                            |                              |                        |                                              |              |                       |                    |  |  |  |

| Bit4:  | REN1: Receive Enable.                                                                                                                                                                                                                                                                                                                                                              |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | This bit enables/disables the UART receiver.                                                                                                                                                                                                                                                                                                                                       |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | 0: UART1 reception disabled.                                                                                                                                                                                                                                                                                                                                                       |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | 1: UART1 re                                                                                                                                                                                                                                                                                                                                                                        | •                          |                              |                        |                                              |              |                       |                    |  |  |  |

| Bit3:  | TB81: Ninth Transmission Bit.                                                                                                                                                                                                                                                                                                                                                      |                            |                              |                        |                                              |              |                       |                    |  |  |  |

|        | The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode. It                                                                                                                                                                                                                                                                                  |                            |                              |                        |                                              |              |                       |                    |  |  |  |

| D'10   | is not used in 8-bit UART Mode. Set or cleared by software as required.                                                                                                                                                                                                                                                                                                            |                            |                              |                        |                                              |              |                       |                    |  |  |  |

| Bit2:  | RB81: Ninth                                                                                                                                                                                                                                                                                                                                                                        |                            |                              |                        |                                              | :            |                       |                    |  |  |  |

|        | RB81 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9th data bit in Mode 1.                                                                                                                                                                                                                                                                      |                            |                              |                        |                                              |              |                       |                    |  |  |  |

| Bit1:  |                                                                                                                                                                                                                                                                                                                                                                                    |                            |                              |                        |                                              |              |                       |                    |  |  |  |

| Dit i. | TI1: Transmit Interrupt Flag.<br>Set by hardware when a byte of data has been transmitted by UART1 (after the 8th bit in 8-<br>bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the UART1<br>interrupt is enabled, setting this bit causes the CPU to vector to the UART1 interrupt service<br>routine. This bit must be cleared manually by software. |                            |                              |                        |                                              |              |                       |                    |  |  |  |

| Bit0:  | RI1: Receiv                                                                                                                                                                                                                                                                                                                                                                        | •                          | •                            |                        |                                              |              |                       |                    |  |  |  |

|        |                                                                                                                                                                                                                                                                                                                                                                                    | g time). Whe               | n the UAR1                   | 1 interrupt            | s been recei<br>is enabled,<br>routine. This | setting this | bit to '1' c          | auses the          |  |  |  |

# SFR Definition 22.1. SCON1: Serial Port 1 Control

| Oscillator                   |                       |                                |                       |                                                 |      |                                     |  |  |  |

|------------------------------|-----------------------|--------------------------------|-----------------------|-------------------------------------------------|------|-------------------------------------|--|--|--|

|                              | Frequency: 18.432 MHz |                                |                       |                                                 |      |                                     |  |  |  |

| Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error  | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select) <sup>*</sup> | T1M* | Timer 1<br>Reload<br>Value<br>(hex) |  |  |  |

| 230400                       | 0.00%                 | 80                             | SYSCLK                | XX                                              | 1    | 0xD8                                |  |  |  |

| 115200                       | 0.00%                 | 160                            | SYSCLK                | XX                                              | 1    | 0xB0                                |  |  |  |

| 57600                        | 0.00%                 | 320                            | SYSCLK                | XX                                              | 1    | 0x60                                |  |  |  |

| 28800                        | 0.00%                 | 640                            | SYSCLK / 4            | 01                                              | 0    | 0xB0                                |  |  |  |

| 14400                        | 0.00%                 | 1280                           | SYSCLK/4              | 01                                              | 0    | 0x60                                |  |  |  |

| 9600                         | 0.00%                 | 1920                           | SYSCLK / 12           | 00                                              | 0    | 0xB0                                |  |  |  |

| 2400                         | 0.00%                 | 7680                           | SYSCLK / 48           | 10                                              | 0    | 0xB0                                |  |  |  |

| 1200                         | 0.00%                 | 15360                          | SYSCLK / 48           | 10                                              | 0    | 0x60                                |  |  |  |

| 230400                       | 0.00%                 | 80                             | EXTCLK / 8            | 11                                              | 0    | 0xFB                                |  |  |  |

| 115200                       | 0.00%                 | 160                            | EXTCLK / 8            | 11                                              | 0    | 0xF6                                |  |  |  |

| 57600                        | 0.00%                 | 320                            | EXTCLK / 8            | 11                                              | 0    | 0xEC                                |  |  |  |

| 28800                        | 0.00%                 | 640                            | EXTCLK / 8            | 11                                              | 0    | 0xD8                                |  |  |  |

| 14400                        | 0.00%                 | 1280                           | EXTCLK / 8            | 11                                              | 0    | 0xB0                                |  |  |  |

| 9600                         | 0.00%                 | 1920                           | EXTCLK / 8            | 11                                              | 0    | 0x88                                |  |  |  |

| X = Dop't care               |                       |                                |                       |                                                 |      |                                     |  |  |  |

#### Table 22.4. Timer Settings for Standard Baud Rates Using an External 18.432 MHz Oscillator

X = Don't care

\*Note: SCA1-SCA0 and T1M bit definitions can be found in Section 23.1.

| Oscillator                       |                      |                                |                       |                                                 |                  |                                  |  |  |  |

|----------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|--|

| Frequency: 3.6864 MHz            |                      |                                |                       |                                                 |                  |                                  |  |  |  |

| <br>Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select) <sup>*</sup> | T1M <sup>*</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |  |

| 230400                           | 0.00%                | 16                             | SYSCLK                | XX                                              | 1                | 0xF8                             |  |  |  |

| 115200                           | 0.00%                | 32                             | SYSCLK                | XX                                              | 1                | 0xF0                             |  |  |  |

| 57600                            | 0.00%                | 64                             | SYSCLK                | XX                                              | 1                | 0xE0                             |  |  |  |

| 28800                            | 0.00%                | 128                            | SYSCLK                | XX                                              | 1                | 0xC0                             |  |  |  |

| 14400                            | 0.00%                | 256                            | SYSCLK                | XX                                              | 1                | 0x80                             |  |  |  |

| 9600                             | 0.00%                | 384                            | SYSCLK                | XX                                              | 1                | 0x40                             |  |  |  |

| 2400                             | 0.00%                | 1536                           | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |  |  |  |

| 1200                             | 0.00%                | 3072                           | SYSCLK / 12           | 00                                              | 0                | 0x80                             |  |  |  |

| 230400                           | 0.00%                | 16                             | EXTCLK/8              | 11                                              | 0                | 0xFF                             |  |  |  |

| 115200                           | 0.00%                | 32                             | EXTCLK / 8            | 11                                              | 0                | 0xFE                             |  |  |  |

| 57600                            | 0.00%                | 64                             | EXTCLK / 8            | 11                                              | 0                | 0xFC                             |  |  |  |

| 28800                            | 0.00%                | 128                            | EXTCLK / 8            | 11                                              | 0                | 0xF8                             |  |  |  |

| 14400                            | 0.00%                | 256                            | EXTCLK / 8            | 11                                              | 0                | 0xF0                             |  |  |  |

| 9600                             | 0.00%                | 384                            | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |  |  |  |

|                                  | V - Don't cor        |                                |                       |                                                 |                  |                                  |  |  |  |

# Table 22.6. Timer Settings for Standard Baud Rates Using an External 3.6864 MHzOscillator

X = Don't care

\*Note: SCA1-SCA0 and T1M bit definitions can be found in Section 23.1.

Rev. 1.6

# **DOCUMENT CHANGE LIST**

#### **Revision 1.5 to Revision 1.6**

Updated Port Input/Output Chapter (17.1.5): P2.0 and P2.1 are not skipped when configured to Analog Input mode.

#### **Revision 1.4 to Revision 1.5**

- High Voltage Difference Amplifier Electrical Characteristics Tables: Corrected Common Mode Rejection Ratio MIN and TYP specifications.

- Flash Memory Chapter: Corrected text reference to "C8051F12x and C8051F13x"; Changed to "C8051F04x".

- 10 and 12-bit ADC0 Track and Conversion Example Timing Figures: Corrected bit name text from "AD0STM" to "AD0CM".

- ADC0 Chapters (10 and 12-bit): Updated analog multiplexer figure to represent correct connection of HVREF to AIN- in differential HVDA configuration.

- ADC0 Chapters (10 and 12-bit): Updated HVDA section text to clarify usage of HVREF pin.

- ADC0 Chapters (10 and 12-bit): Added differential HVDA options to AMUX Selection Chart Table.

- Product Selection Guide Table: Added RoHS-compliant ordering information.

- Global DC Electrical Characteristics Table: Corrected units for "Analog Supply Current with Analog Subsystems Inactive" to "µA".

- Pin Definitions Table: Corrected HVAIN- pin description to "High Voltage Difference Amplifier Negative Signal Input."

- Interrupt Summary Table: Added "SFRPAGE" column and SFRPAGE value for each interrupt source.

- Interrupt Summary Table: Corrected "T4CON" to "TMR4CN".

- Interrupt Summary Table: Corrected "T2CON" to "TMR2CN".

- Interrupt Summary Table: Corrected "ADWINT" to "AD0WINT".

- SFR Memory Map Table: Corrected SFR Page for ADC2CN from page 1 to page 2.

- Oscillators Chapter: Corrected steps for enabling external crystal oscillator.

- PCA0CPHn SFR Definition: Corrected SFR address of PCA0CPH1 from "0xFD" to "0xFE".