Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                          |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 32                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 8x8b, 13x10b; D/A 2x10b, 2x12b                                |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 64-TQFP                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f043r      |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

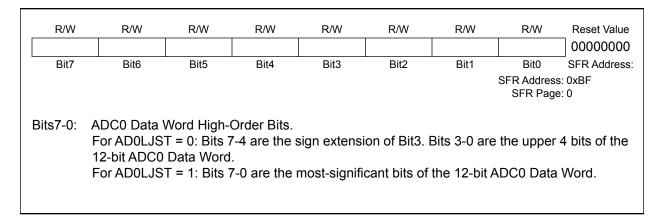

# SFR Definition 5.7. ADC0H: ADC0 Data Word MSB

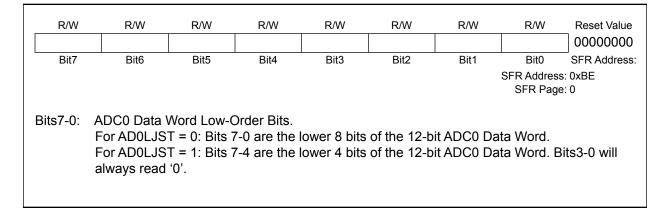

# SFR Definition 5.8. ADC0L: ADC0 Data Word LSB

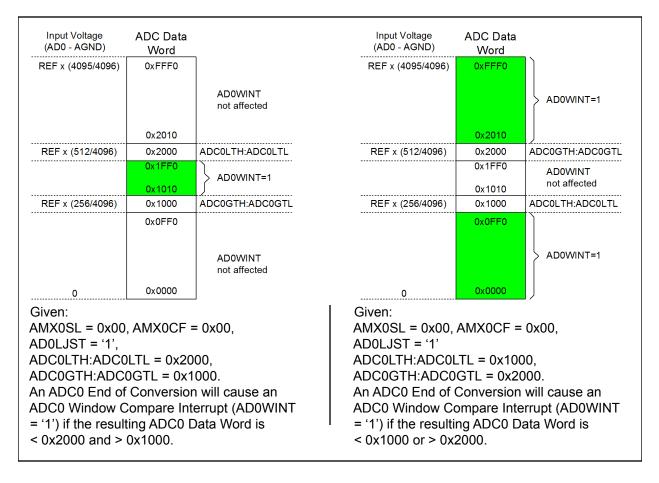

### Figure 5.10. 12-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data

### 6.1.1. Analog Input Configuration

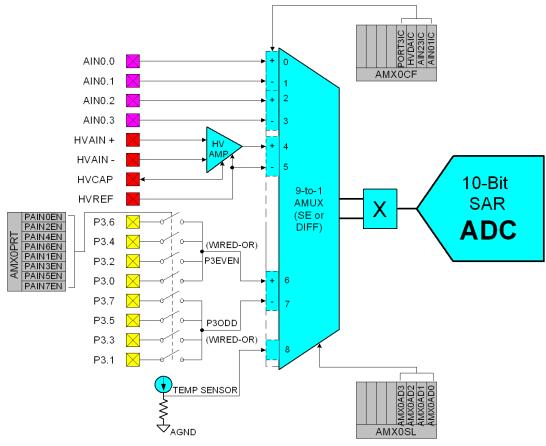

The analog multiplexer routes signals from external analog input pins, Port 3 I/O pins (programmed to be analog inputs), a High Voltage Difference Amplifier, and an on-chip temperature sensor as shown in Figure 6.2.

Figure 6.2. Analog Input Diagram

Analog signals may be input from four external analog input pins (AIN0.0 through AIN0.3) as differential or single-ended measurements. Additionally, Port 3 I/O Port Pins may be configured to input analog signals. Port 3 pins configured as analog inputs are selected using the Port Pin Selection register (AMX0PRT). Any number of Port 3 pins may be selected simultaneously as inputs to the AMUX. Even numbered Port 3 pins and odd numbered Port 3 pins are routed to separate AMUX inputs. (**Note:** Even port pins and odd port pins that are simultaneously selected will be shorted together as "wired-OR".) In this way, differential measurements may be made when using the Port 3 pins (voltage difference between selected even and odd Port 3 pins) as shown in Figure 6.2.

The High-Voltage Difference Amplifier (HVDA) will accept analog input signals and reject up to 60 volts common-mode for differential measurement of up to the reference voltage to the ADC (0 to VREF volts). The output of the HVDA can be selected as an input to the ADC using the AMUX as any other channel is selected for measurement.

# 7. 8-Bit ADC (ADC2, C8051F040/1/2/3 Only)

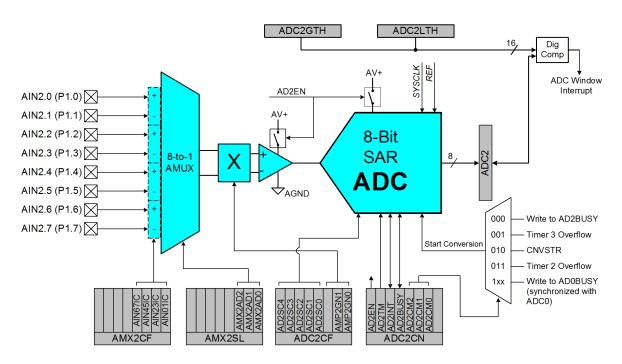

The ADC2 subsystem for the C8051F040/1/2/3 consists of an 8-channel, configurable analog multiplexer, a programmable gain amplifier, and a 500 ksps, 8-bit successive-approximation-register ADC with integrated track-and-hold (see block diagram in Figure 7.1). The AMUX2, PGA2, and Data Conversion Modes, are all configurable under software control via the Special Function Registers shown in Figure 7.1. The ADC2 subsystem (8-bit ADC, track-and-hold and PGA) is enabled only when the AD2EN bit in the ADC2 Control register (ADC2CN) is set to logic 1. The ADC2 subsystem is in low power shutdown when this bit is logic 0. The voltage reference used by ADC2 is selected as described in Section "9. Voltage Reference (C8051F040/2/4/6)" on page 113 for C8051F040/2 devices, or Section "10. Voltage Reference (C8051F041/3/5/7)" on page 117 for C8051F041/3 devices.

Figure 7.1. ADC2 Functional Block Diagram

## 7.1. Analog Multiplexer and PGA

Eight ADC2 channels are available for measurement, as selected by the AMX2SL register (see SFR Definition 7.2). The PGA amplifies the ADC2 output signal by an amount determined by the states of the AMP2GN2-0 bits in the ADC2 Configuration register, ADC2CF (SFR Definition 7.1). The PGA can be software-programmed for gains of 0.5, 1, 2, or 4. Gain defaults to 0.5 on reset.

**Important Note**: AIN2 pins also function as Port 1 I/O pins, and must be configured as analog inputs when used as ADC2 inputs. To configure an AIN2 pin for analog input, set to '0' the corresponding bit in register P1MDIN. Port 1 pins selected as analog inputs are skipped by the Digital I/O Crossbar. See **Section "17.1.5. Configuring Port 1, 2, and 3 Pins as Analog Inputs" on page 207** for more information on configuring the AIN2 pins.

and a RET pops two record bits, also.) The stack record circuitry can also detect an overflow or underflow on the 32-bit shift register, and can notify the debug software even with the MCU running at speed.

#### 12.2.6. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFR's). The SFR's provide control and data exchange with the CIP-51's resources and peripherals. The CIP-51 duplicates the SFR's found in a typical 8051 implementation as well as implementing additional SFR's used to configure and access the sub-systems unique to the MCU. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 12.2 lists the SFR's implemented in the CIP-51 System Controller.

The SFR registers are accessed whenever the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFR's with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, P1, SCON, IE, etc.) are bit-addressable as well as byte-addressable. All other SFR's are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the datasheet, as indicated in Table 12.3, for a detailed description of each register.

#### 12.2.6.1. SFR Paging

The CIP-51 features *SFR paging*, allowing the device to map many SFR's into the 0x80 to 0xFF memory address space. The SFR memory space has 256 *pages*. In this way, each memory location from 0x80 to 0xFF can access up to 256 SFR's. The C8051F04x family of devices utilizes five SFR pages: 0, 1, 2, 3, and F. SFR pages are selected using the Special Function Register Page Selection register, SFRPAGE (see SFR Definition 12.2). The procedure for reading and writing an SFR is as follows:

- 1. Select the appropriate SFR page number using the SFRPAGE register.

- 2. Use direct accessing mode to read or write the special function register (MOV instruction).

#### 12.2.6.2. Interrupts and SFR Paging

When an interrupt occurs, the SFR Page Register will automatically switch to the SFR page containing the flag bit that caused the interrupt. The automatic SFR Page switch function conveniently removes the burden of switching SFR pages from the interrupt service routine. Upon execution of the RETI instruction, the SFR page is automatically restored to the SFR Page in use prior to the interrupt. This is accomplished via a three-byte *SFR Page Stack*. The top byte of the stack is SFRPAGE, the current SFR Page. The second byte of the SFR Page Stack is SFRNEXT. The third, or bottom byte of the SFR Page Stack is SFRLAST. On interrupt, the current SFRPAGE value is pushed to the SFR Page containing the flag bit associated with the interrupt. On a return from interrupt, the SFR Page Stack is popped resulting in the value of SFRNEXT returning to the SFRPAGE register, thereby restoring the SFR page context without software intervention. The value in SFRLAST (0x00 if there is no SFR Page value in the bottom of the stack) of the stack is placed in SFRNEXT register. If desired, the values stored in SFRNEXT and SFRLAST may be modified during an interrupt, enabling the CPU to return to a different SFR Page upon execution of the RETI instruction (on interrupt exit). Modifying registers in the SFR Page Stack does not cause a push or pop of the stack. Only interrupt calls and returns will cause push/pop operations on the SFR Page Stack.

| Interrupt Source          | Interrupt<br>Vector | Priority<br>Order | Pending Flag                   | Bit addressable? | Cleared by HW? | SFRPAGE (SFRPGEN = 1) | Enable<br>Flag     | Priority<br>Control |

|---------------------------|---------------------|-------------------|--------------------------------|------------------|----------------|-----------------------|--------------------|---------------------|

| Comparator 1              | 0x005B              | 11                | CP1FIF/CP1RIF<br>(CPT1CN.4/.5) |                  |                | 2                     | CP1IE<br>(EIE1.5)  | PCP1<br>(EIP1.5)    |

| Comparator 2              | 0x0063              | 12                | CP2FIF/CP2RIF<br>(CPT2CN.4/.5) |                  |                | 3                     | CP2IE<br>(EIE1.6)  | PCP2<br>(EIP1.6)    |

| Timer 3                   | 0x0073              | 14                | TF3 (TMR3CN.7)                 |                  |                | 1                     | ET3<br>(EIE2.0)    | PT3<br>(EIP2.0)     |

| ADC0 End of<br>Conversion | 0x007B              | 15                | ADC0INT<br>(ADC0CN.5)          | Y                |                | 0                     | EADC0<br>(EIE2.1)  | PADC0<br>(EIP2.1)   |

| Timer 4                   | 0x0083              | 16                | TF4 (TMR4CN.7)                 |                  |                | 2                     | ET4<br>(EIE2.2)    | PT4<br>(EIP2.2)     |

| ADC2 Window<br>Comparator | 0x0093              | 17                | AD2WINT<br>(ADC2CN.0)          |                  |                | 2                     | EWADC2<br>(EIE2.3) | PWADC2<br>(EIP2.3)  |

| ADC2 End of<br>Conversion | 0x008B              | 18                | ADC2INT<br>(ADC1CN.5)          |                  |                | 2                     | EADC1<br>(EIE2.4)  | PADC1<br>(EIP2.4)   |

| CAN Interrupt             | 0x009B              | 19                | CAN0CN.7                       |                  | Y              | 1                     | ECAN0<br>(EIE2.5)  | PCAN0<br>(EIP2.5)   |

| UART1                     | 0x00A3              | 20                | RI1 (SCON1.0)<br>TI1 (SCON1.1) |                  |                | 1                     | ES1<br>(EIE2.6)    | PS1<br>(EIP2.6)     |

Table 12.4. Interrupt Summary (Continued)

### 12.17. Power Management Modes

The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the external peripherals and internal clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the internal oscillator is stopped. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power. SFR Definition 12.18 describes the Power Control Register (PCON) used to control the CIP-51's power management modes.

Although the CIP-51 has Idle and Stop modes built in (as with any standard 8051 architecture), power management of the entire MCU is better accomplished by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and put into low power mode. Digital peripherals, such as timers or serial buses, draw little power whenever they are not in use. Turning off the oscillator saves even more power, but requires a reset to restart the MCU.

#### 12.17.1.Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt or /RST is asserted. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the WDT will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to **Section 13.7** for more information on the use and configuration of the WDT.

**Note:** Any instruction that sets the IDLE bit should be immediately followed by an instruction that has 2 or more opcode bytes. For example:

```

// in 'C':

PCON |= 0x01;  // set IDLE bit

PCON = PCON;  // ... followed by a 3-cycle dummy instruction

; in assembly:

ORL PCON, #01h ; set IDLE bit

MOV PCON, PCON ; ... followed by a 3-cycle dummy instruction

```

If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from IDLE mode when a future interrupt occurs.

#### 12.17.2.Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes. In Stop mode, the CPU and internal oscillators are stopped, effectively shutting down all digital peripherals. Each analog peripheral must be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to sleep for longer than the MCD timeout of 100  $\mu$ s.

| R/V              | /              | R/W                                      | R/W  | R/W                       | R/W         | R/W  | R/W  | R/W                     | Reset Value             |  |  |

|------------------|----------------|------------------------------------------|------|---------------------------|-------------|------|------|-------------------------|-------------------------|--|--|

|                  |                | —                                        | _    | —                         |             | —    | STOP | IDLE                    | 0000000                 |  |  |

| Bit              | 7              | Bit6                                     | Bit5 | Bit4                      | Bit3        | Bit2 | Bit1 | Bit0                    |                         |  |  |

|                  |                |                                          |      |                           |             |      |      | SFR Address<br>SFR Page | s: 0x87<br>e: All Pages |  |  |

| Bits7-3<br>Bit1: |                |                                          |      |                           |             |      |      |                         |                         |  |  |

| Bit0:            | Wi<br>0:<br>1: | riting a '1'<br>No effect.<br>CIP-51 foi |      | ill place the e mode. (SI | CIP-51 into |      |      |                         |                         |  |  |

### SFR Definition 12.18. PCON: Power Control

| R                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                                                                                                                                                                                                | R/W                                                                           | R                                | R/W                    | R/W    | R/W                   | Reset Value       |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------|------------------------|--------|-----------------------|-------------------|--|--|--|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                    | XOSCMD0                                                                       | -                                | XFCN2                  | XFCN1  | XFCN0                 | 00000000          |  |  |  |

| Bit7              | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit5                                                                                                                                                                                               | Bit4                                                                          | Bit3                             | Bit2                   | Bit1   | Bit0                  |                   |  |  |  |

| Diti              | Ыю                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ыю                                                                                                                                                                                                 |                                                                               | Dito                             |                        | Ditt   | SFR Addres<br>SFR Pag |                   |  |  |  |

| Bit7:             | ( <b>Read or</b><br>0: Crysta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | KTLVLD: Crystal Oscillator Valid Flag.<br><b>Read only when XOSCMD = 11x.</b> )<br>D: Crystal Oscillator is unused or not yet stable.<br>I: Crystal Oscillator is running and stable.              |                                                                               |                                  |                        |        |                       |                   |  |  |  |

| Bits6-4:          | 00x: Exte<br>010: Exte<br>011: Exte<br>XTAL1 pi<br>10x: RC/0<br>110: Crys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 02-0: External O<br>ernal Oscillator c<br>ernal CMOS Cloo<br>ernal CMOS Cloo<br>n).<br>C Oscillator Moc<br>stal Oscillator Moc                                                                     | rcuit off.<br>ck Mode (Ext<br>ck Mode with<br>le with divide<br>ode.          | ernal CN<br>divide b<br>by 2 sta | y 2 stage (E<br>ge.    |        |                       | nput on           |  |  |  |

| Bit3:<br>Bits2-0: | RESERV<br>XFCN2-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ED. Read = 0, V<br>External Oscill<br>see table below                                                                                                                                              | Vrite = don't c<br>ator Frequen                                               | are.                             | -                      |        |                       |                   |  |  |  |

|                   | XFCN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Crystal (XOSC                                                                                                                                                                                      | CMD = 11x)                                                                    | RC ()                            | (OSCMD =               | 10x) ( | C (XOSCM              | D = 10x)          |  |  |  |

|                   | 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | f ≤ 32 l                                                                                                                                                                                           | (Hz                                                                           |                                  | $f \le 25 \text{ kHz}$ |        | K Factor = 0.87       |                   |  |  |  |

|                   | 001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32 kHz < f ≤                                                                                                                                                                                       | 84 kHz                                                                        | 25 k                             | $Hz < f \le 50$        | kHz    | K Factor = 2.6        |                   |  |  |  |

|                   | 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84 kHz < f ≤                                                                                                                                                                                       | 225 kHz                                                                       | 50 kł                            | $z < f \le 100$        | kHz    | K Factor = 7.7        |                   |  |  |  |

|                   | 011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 225 kHz < f <                                                                                                                                                                                      | ≤590 kHz                                                                      | 100 k                            | $Hz < f \le 200$       | ) kHz  | K Factor              | · = 22            |  |  |  |

|                   | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 590 kHz < f <                                                                                                                                                                                      | 1.5 MHz                                                                       | 200 k                            | $Hz < f \le 400$       | ) kHz  | K Factor              | <sup>·</sup> = 65 |  |  |  |

|                   | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.5 MHz < f                                                                                                                                                                                        | ≤4 MHz                                                                        | 400 k                            | $Hz < f \le 800$       | ) kHz  | K Factor              | = 180             |  |  |  |

|                   | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4 MHz < f ≤                                                                                                                                                                                        | 10 MHz                                                                        | 800 k                            | $Hz < f \le 1.6$       | MHz    | K Factor              | = 664             |  |  |  |

|                   | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10 MHz < f <                                                                                                                                                                                       | 30 MHz                                                                        | 1.6 M                            | $Hz < f \le 3.2$       | MHz    | K Factor =            | = 1590            |  |  |  |

| RC MOD            | Choose Ch | Circuit from Figu<br>(FCN value to m<br>from Figure 14.1<br>(FCN value to m<br>(I0 <sup>3</sup> ) / (R x C), wh<br>ency of oscillation<br>citor value in pF<br>p resistor value<br>om Figure 14.1, | atch crystal f<br>, Option 2; X<br>latch frequen<br>here<br>h in MHz<br>in kΩ | requenc<br>OSCMD<br>cy range     | y.<br>= 10x)<br>::     | x)     |                       |                   |  |  |  |

|                   | Choose k<br>f = KF / (<br>f = freque<br>C = capa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | K Factor (KF) for $C \times V_{DD}$ , where ency of oscillatio citor value on X wer Supply on N                                                                                                    | the oscillatio<br>n in MHz<br>FAL1, XTAL2                                     | n freque                         | ncy desired            | :      |                       |                   |  |  |  |

| R/W                | R/W          | R/W           | R/W           | R/W           | R/W            | R/W            | R/W           | _ Reset Value |

|--------------------|--------------|---------------|---------------|---------------|----------------|----------------|---------------|---------------|

| -                  | -            | PRTSEL        | EMD2          | EMD1          | EMD0           | EALE1          | EALE0         | 00000011      |

| Bit7               | Bit6         | Bit5          | Bit4          | Bit3          | Bit2           | Bit1           | Bit0          | _             |

|                    |              |               |               |               |                |                | SFR Address   |               |

|                    |              |               |               |               |                |                | SFR Page:     | 0             |

| Bits7-6:           | Unused, Re   | ad - 00h 14   | /rito - don't | 0010          |                |                |               |               |

| Bit5:              | PRTSEL: EI   |               |               | care.         |                |                |               |               |

| DILO.              | 0: EMIF acti |               |               |               |                |                |               |               |

|                    | 1: EMIF acti |               |               |               |                |                |               |               |

| Bit4:              | EMD2: EMI    |               |               | <b>`</b> †    |                |                |               |               |

| DI( <del>1</del> . | 0: EMIF ope  | •             |               |               | mode           |                |               |               |

|                    | 1: EMIF ope  |               | •             |               |                | ress and da    | ata nins)     |               |

| Bits3-2:           | EMD1-0: EN   |               |               | •             | pulato ada     |                |               |               |

| 51100 2.           | These bits c | •             | •             |               | xternal Mer    | morv Interfa   | ace.          |               |

|                    | 00: Internal |               |               |               |                |                |               | lias to on-   |

|                    |              | nory space.   |               |               | , <b>,</b> , . |                |               |               |

|                    | 01: Split Mo |               |               | : Accesses    | below the 4    | 1k boundarv    | v are directe | ed on-chip.   |

|                    |              | s above the   |               |               |                |                |               |               |

|                    |              | current cont  |               |               |                |                |               |               |

|                    | Note tha     | t in order to | access off-   | -chip space   | EMI0CN n       | nust be set    | to a page th  | nat is not    |

|                    | containe     | d in the on-  | chip addres   | s space.      |                |                |               |               |

|                    | 10: Split Mo | de with Ban   | k Select: A   | ccesses bel   | ow the 4k b    | oundary ar     | e directed o  | on-chip.      |

|                    | Accesse      | s above the   | 4k bounda     | ry are direc  | ted off-chip   | . 8-bit off-ch | nip MOVX c    | perations     |

|                    | use the o    | contents of   | EMI0CN to     | determine t   | he high-byt    | e of the ad    | dress.        |               |

|                    | 11: External | Only: MOV     | X accesses    | s off-chip XF | RAM only. C    | Dn-chip XRA    | AM is not vi  | sible to the  |

|                    | CPU.         |               |               |               |                |                |               |               |

| Bits1-0:           | EALE1-0: AI  |               |               | · ·           |                |                | = 1).         |               |

|                    | 00: ALE high |               | •             |               |                |                |               |               |

|                    | 01: ALE high |               | •             |               |                |                |               |               |

|                    | 10: ALE high |               | •             |               |                |                |               |               |

|                    | 11: ALE high | i and ALE Id  | ow pulse wi   | atn = 4 SYS   | OLK CYCLES     | 5.             |               |               |

# SFR Definition 16.2. EMI0CF: External Memory Configuration

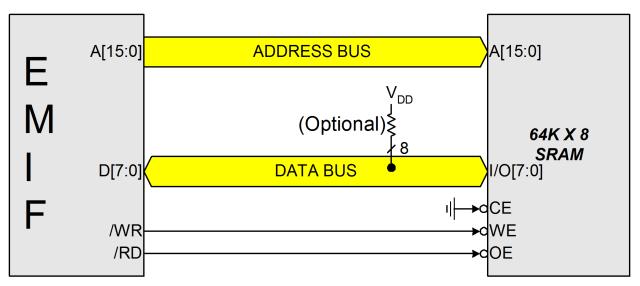

### 16.4.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Nonmultiplexed Configuration is shown in Figure 16.2. See **Section "16.6.1. Non-multiplexed Mode" on page 196** for more information about Non-multiplexed operation.

Figure 16.2. Non-multiplexed Configuration Example

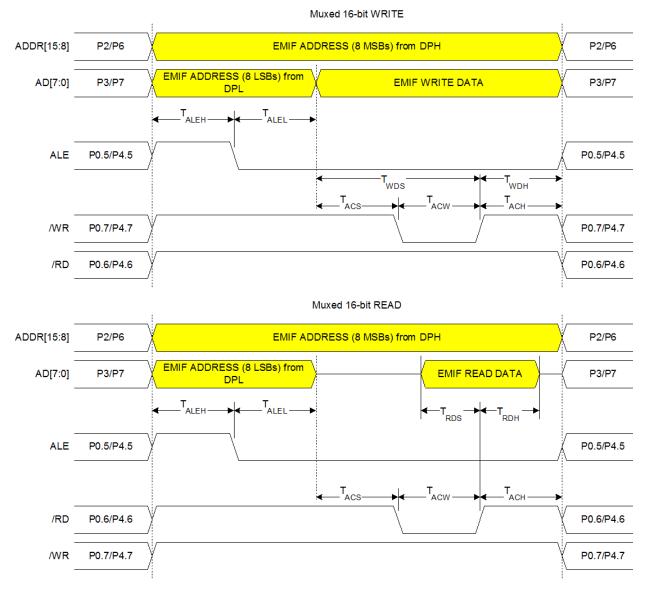

### 16.6.2. Multiplexed Mode

#### 16.6.2.1.16-bit MOVX: EMI0CF[4:2] = '001', '010', or '011'.

Figure 16.7. Multiplexed 16-bit MOVX Timing

| Parameter           | Description                    | Min                     | Мах                      | Units |

|---------------------|--------------------------------|-------------------------|--------------------------|-------|

| T <sub>SYSCLK</sub> | System Clock Period            | 40                      |                          | ns    |

| T <sub>ACS</sub>    | Address/Control Setup Time     | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ACW</sub>    | Address/Control Pulse Width    | 1 x T <sub>SYSCLK</sub> | 16 x T <sub>SYSCLK</sub> | ns    |

| T <sub>ACH</sub>    | Address/Control Hold Time      | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEH</sub>   | Address Latch Enable High Time | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEL</sub>   | Address Latch Enable Low Time  | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>WDS</sub>    | Write Data Setup Time          | 1 x T <sub>SYSCLK</sub> | 19 x T <sub>SYSCLK</sub> | ns    |

| T <sub>WDH</sub>    | Write Data Hold Time           | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>RDS</sub>    | Read Data Setup Time           | 20                      |                          | ns    |

| T <sub>RDH</sub>    | Read Data Hold Time            | 0                       |                          | ns    |

Table 16.1. AC Parameters for External Memory Interface

a digital input by setting P3MDOUT.7 to a logic 0, which selects open-drain output mode, and P3.7 to a logic 1, which disables the low-side output driver.

If the Port pin has been assigned to a digital peripheral by the Crossbar and that pin functions as an input (for example RX0, the UART0 receive pin), then the output drivers on that pin are automatically disabled.

#### 17.1.4. Weak Pullups

By default, each Port pin has an internal weak pullup device enabled which provides a resistive connection (about 100 k $\Omega$ ) between the pin and V<sub>DD</sub>. The weak pullup devices can be globally disabled by writing a logic 1 to the Weak Pullup Disable bit, (WEAKPUD, XBR2.7). The weak pullup is automatically deactivated on any pin that is driving a logic 0; that is, an output pin will not contend with its own pullup device. The weak pullup device can also be explicitly disabled on Ports 1, 2, and 3 pin by configuring the pin as an Analog Input, as described below.

#### 17.1.5. Configuring Port 1, 2, and 3 Pins as Analog Inputs

The pins on Port 1 can serve as analog inputs to the ADC2 analog MUX (C8051F040/1/2/3 only), the pins on Port 2 can serve as analog inputs to the Comparators, and the pins on Port 3 can serve as inputs to ADC0. A Port pin is configured as an Analog Input by writing a logic 0 to the associated bit in the PnMDIN registers. All Port pins default to a Digital Input mode. Configuring a Port pin as an analog input:

- Disables the digital input path from the pin. This prevents additional power supply current from being drawn when the voltage at the pin is near V<sub>DD</sub> / 2. A read of the Port Data bit will return a logic 0 regardless of the voltage at the Port pin.

- 2. Disables the weak pullup device on the pin.

- 3. Causes the Crossbar to "skip over" the pin when allocating Port pins for digital peripherals, except for P2.0-P2.1.

Note that the output drivers on a pin configured as an Analog Input are not explicitly disabled. Therefore, the associated PnMDOUT bits of pins configured as Analog Inputs should explicitly be set to logic 0 (Open-Drain output mode), and the associated Port Data bits should be set to logic 1 (high-impedance). Also note that it is not required to configure a Port pin as an Analog Input in order to use it as an input to the ADC's or Comparators; however, it is strongly recommended. See the analog peripheral's corresponding section in this datasheet for further information.

# SFR Definition 18.1. CAN0DATL: CAN Data Access Register Low Byte

| R/W  | R/W                                                                                | R/W                                                     | R/W                                                        | R/W                                                       | R/W                                                     | R/W                | R/W                                   | Reset Value |

|------|------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------|--------------------|---------------------------------------|-------------|

| Bit7 | Bit6                                                                               | Bit5                                                    | Bit4                                                       | Bit3                                                      | Bit2                                                    | Bit1               | Bit0                                  |             |

|      |                                                                                    |                                                         |                                                            |                                                           | _                                                       |                    | SFR Addres<br>SFR Pag                 |             |

|      | CAN0DATL:<br>The CAN0D/<br>CAN Registe<br>The CAN0AI<br>Register. The<br>CAN0DAT R | AT Register<br>ers pointed<br>DR Registe<br>e desired C | rs are used<br>to with the i<br>r is used to<br>AN Registe | to read/writ<br>ndex numb<br>point the [C<br>r's index nu | e register va<br>er in the CA<br>AN0DATH:<br>mber is mo | N0ADR R<br>CAN0DAT | egister.<br>L] to a desi<br>AN0ADR. 1 | red CAN     |

# SFR Definition 18.2. CAN0ADR: CAN Address Index

| R/W     | R/W                                                                                                                                         | R/W                                                                                                   | R/W                                                                                 | R/W                                                                                        | R/W                                                                 | R/W                                                                                | R/W                                              | Reset Value        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------|--------------------|

| Bit7    | Bit6                                                                                                                                        | Bit5                                                                                                  | Bit4                                                                                | Bit3                                                                                       | Bit2                                                                | Bit1                                                                               | Bit0                                             |                    |

|         |                                                                                                                                             |                                                                                                       |                                                                                     |                                                                                            |                                                                     |                                                                                    | SFR Addres<br>SFR Pag                            |                    |

| Bit7-0: | CAN0ADR: 0<br>The CAN0Al<br>Register. The<br>CAN0DAT R<br><u>Note</u> : When<br>this register<br>"18.2.6. CAI<br>All CAN reg<br>User's Guid | DR Registe<br>e desired C<br>legister can<br>the value o<br>will autoinc<br>NOADR Aut<br>isters' fund | r is used to<br>AN Registe<br>then read/o<br>f CAN0ADF<br>rement by 1<br>toincremer | point the [C<br>pr's index nu<br>write to and<br>R is 0x08-0x<br>upon a wri<br>ht Feature" | mber is mo<br>from the C.<br>12 and 0x2<br>te to CAN0<br>on page 23 | oved into CA<br>AN Registe<br>20-0x2A (IF <sup>-</sup><br>DATL. See<br><b>32</b> . | AN0ADR. 1<br>r.<br>1 and IF2 r<br><b>Section</b> | Гhe<br>registers), |

| Mode               | Status<br>Code | SMBus State                                   | Typical Action                                                                                                                   |

|--------------------|----------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Ъъ                 | 0x08           | START condition transmitted.                  | Load SMB0DAT with Slave Address +<br>R/W. Clear STA.                                                                             |

| MT                 | 0x10           | Repeated START condition transmitted.         | Load SMB0DAT with Slave Address +<br>R/W. Clear STA.                                                                             |

|                    | 0x18           | Slave Address + W transmitted. ACK received.  | Load SMB0DAT with data to be transmit-<br>ted.                                                                                   |

| mitter             | 0x20           | Slave Address + W transmitted. NACK received. | Acknowledge poll to retry. Set STO + STA.                                                                                        |

| Master Transmitter | 0x28           | Data byte transmitted. ACK received.          | <ol> <li>Load SMB0DAT with next byte, OR</li> <li>Set STO, OR</li> <li>Clear STO then set STA for repeated<br/>START.</li> </ol> |