# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 64                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 13x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 100-TQFP                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f044-gq    |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### List of Registers

| SFR | Definition 5 | 5.1. AMX0CF: AMUX0 Configuration                       | 19 |

|-----|--------------|--------------------------------------------------------|----|

|     |              | 5.2. AMX0SL: AMUX0 Channel Select                      |    |

| SFR | Definition 5 | 5.3. AMX0PRT: Port 3 Pin Selection                     | 51 |

| SFR | Definition 5 | 5.4. HVA0CN: High Voltage Difference Amplifier Control | 53 |

|     |              | 5.5. ADC0CF: ADC0 Configuration Register               |    |

|     |              | 5.6. ADC0CN: ADC0 Control                              |    |

| SFR | Definition 5 | 5.7. ADC0H: ADC0 Data Word MSB                         | 60 |

| SFR | Definition 5 | 5.8. ADC0L: ADC0 Data Word LSB                         | 60 |

| SFR | Definition 5 | 5.9. ADC0GTH: ADC0 Greater-Than Data High Byte         | 62 |

|     |              | 5.10. ADC0GTL: ADC0 Greater-Than Data Low Byte         |    |

| SFR | Definition 5 | 5.11. ADC0LTH: ADC0 Less-Than Data High Byte           | 62 |

|     |              | 5.12. ADC0LTL: ADC0 Less-Than Data Low Byte            |    |

|     |              | 6.1. AMX0CF: AMUX0 Configuration                       |    |

| SFR | Definition 6 | 6.2. AMX0SL: AMUX0 Channel Select                      | 71 |

|     |              | 6.3. AMX0PRT: Port 3 Pin Selection                     |    |

| SFR | Definition 6 | 6.4. HVA0CN: High Voltage Difference Amplifier Control | 75 |

| SFR | Definition 6 | S.5. ADC0CF: ADC0 Configuration       8                | 30 |

|     |              | δ.6. ADC0CN: ADC0 Control 8                            |    |

|     |              | 6.7. ADC0H: ADC0 Data Word MSB                         |    |

|     |              | S.8. ADC0L: ADC0 Data Word LSB       8                 |    |

|     |              | S.9. ADC0GTH: ADC0 Greater-Than Data High Byte       6 |    |

|     |              | 6.10. ADC0GTL: ADC0 Greater-Than Data Low Byte         |    |

|     |              | 6.11. ADC0LTH: ADC0 Less-Than Data High Byte           |    |

|     |              | 6.12. ADC0LTL: ADC0 Less-Than Data Low Byte            |    |

|     |              | 7.1. AMX2CF: AMUX2 Configuration                       |    |

|     |              | 7.2. AMX2SL: AMUX2 Channel Select                      |    |

|     |              | 7.3. ADC2CF: ADC2 Configuration                        |    |

|     |              | 7.4. ADC2CN: ADC2 Control                              |    |

|     |              | 7.5. ADC2: ADC2 Data Word                              |    |

|     |              | 7.6. ADC2GT: ADC2 Greater-Than Data                    |    |

|     |              | 7.7. ADC2LT: ADC2 Less-Than Data                       |    |

| SFR | Definition 8 | 3.1. DAC0H: DAC0 High Byte                             | )7 |

|     |              | 3.2. DAC0L: DAC0 Low Byte                              |    |

| SFR | Definition 8 | 3.3. DAC0CN: DAC0 Control                              | )8 |

| SFR | Definition 8 | 3.4. DAC1H: DAC1 High Byte                             | )9 |

|     |              | 3.5. DAC1L: DAC1 Low Byte                              |    |

|     |              | 3.6. DAC1CN: DAC1 Control1                             |    |

|     |              | 0.1. REF0CN: Reference Control1                        |    |

|     |              | 10.1. REF0CN: Reference Control1                       |    |

| SFR | Definition 1 | 11.1. CPTnCN: Comparator 0, 1, and 2 Control           | 24 |

|     |              | 11.2. CPTnMD: Comparator Mode Selection                |    |

|     |              | 12.1. SFR Page Control Register: SFRPGCN               |    |

| SFR | Definition 1 | 12.2. SFR Page Register: SFRPAGE                       | 12 |

| Ordering Part Number | MIPS (Peak) | Flash Memory | RAM  | External Memory Interface | SMBus/I <sup>2</sup> C and SPI | CAN          | UARTS | Timers (16-bit) | Programmable Counter Array | Digital Port I/O's | 12-bit 100ksps ADC | 10-bit 100ksps ADC | 8-bit 500 ksps ADC Inputs | High Voltage Diff Amp | Voltage Reference | Temperature Sensor | DAC Resolution (bits) | DAC Outputs | Analog Comparators | Lead-free (RoHS Compliant) | Package |

|----------------------|-------------|--------------|------|---------------------------|--------------------------------|--------------|-------|-----------------|----------------------------|--------------------|--------------------|--------------------|---------------------------|-----------------------|-------------------|--------------------|-----------------------|-------------|--------------------|----------------------------|---------|

| C8051F040            | 25          | 64 kB        | 4352 | ✓                         | $\checkmark$                   | ~            | 2     | 5               | ✓                          | 64                 | $\checkmark$       | -                  | 8                         | $\checkmark$          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | -                          | 100TQFP |

| C8051F040-GQ         | 25          | 64 kB        | 4352 | $\checkmark$              | $\checkmark$                   | ✓            | 2     | 5               | $\checkmark$               | 64                 | $\checkmark$       | -                  | 8                         | $\checkmark$          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | $\checkmark$               | 100TQFP |

| C8051F041            | 25          | 64 kB        | 4352 | $\checkmark$              | $\checkmark$                   | ~            | 2     | 5               | $\checkmark$               | 32                 | $\checkmark$       | -                  | 8                         | $\checkmark$          | $\checkmark$      | ~                  | 12                    | 2           | 3                  | -                          | 64TQFP  |

| C8051F041-GQ         | 25          | 64 kB        | 4352 | ✓                         | $\checkmark$                   | ~            | 2     | 5               | ✓                          | 32                 | $\checkmark$       | -                  | 8                         | $\checkmark$          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | $\checkmark$               | 64TQFP  |

| C8051F042            | 25          | 64 kB        | 4352 | $\checkmark$              | $\checkmark$                   | ✓            | 2     | 5               | $\checkmark$               | 64                 | -                  | $\checkmark$       | 8                         | $\checkmark$          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | -                          | 100TQFP |

| C8051F042-GQ         | 25          | 64 kB        | 4352 | $\checkmark$              | $\checkmark$                   | ~            | 2     | 5               | $\checkmark$               | 64                 | -                  | $\checkmark$       | 8                         | $\checkmark$          | $\checkmark$      | ~                  | 12                    | 2           | 3                  | $\checkmark$               | 100TQFP |

| C8051F043            | 25          | 64 kB        | 4352 | ✓                         | $\checkmark$                   | ~            | 2     | 5               | ✓                          | 32                 | -                  | $\checkmark$       | 8                         | $\checkmark$          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | -                          | 64TQFP  |

| C8051F043-GQ         | 25          | 64 kB        | 4352 | $\checkmark$              | $\checkmark$                   | $\checkmark$ | 2     | 5               | $\checkmark$               | 32                 | -                  | $\checkmark$       | 8                         | $\checkmark$          | $\checkmark$      | $\checkmark$       | 12                    | 2           | 3                  | $\checkmark$               | 64TQFP  |

| C8051F044            | 25          | 64 kB        | 4352 | $\checkmark$              | $\checkmark$                   | $\checkmark$ | 2     | 5               | $\checkmark$               | 64                 | -                  | $\checkmark$       |                           | $\checkmark$          | $\checkmark$      | $\checkmark$       |                       |             | 3                  | -                          | 100TQFP |

| C8051F044-GQ         | 25          | 64 kB        | 4352 | $\checkmark$              | $\checkmark$                   | $\checkmark$ | 2     | 5               | $\checkmark$               | 64                 | -                  | $\checkmark$       |                           | $\checkmark$          | $\checkmark$      | $\checkmark$       |                       |             | 3                  | $\checkmark$               | 100TQFP |

| C8051F045            | 25          | 64 kB        | 4352 | $\checkmark$              | $\checkmark$                   | $\checkmark$ | 2     | 5               | $\checkmark$               | 32                 | -                  | $\checkmark$       |                           | $\checkmark$          | $\checkmark$      | $\checkmark$       |                       |             | 3                  | I                          | 64TQFP  |

| C8051F045-GQ         | 25          | 64 kB        | 4352 | $\checkmark$              | $\checkmark$                   | $\checkmark$ | 2     | 5               | $\checkmark$               | 32                 | -                  | $\checkmark$       |                           | $\checkmark$          | $\checkmark$      | $\checkmark$       |                       |             | 3                  | $\checkmark$               | 64TQFP  |

| C8051F046            | 25          | 32 kB        | 4352 | $\checkmark$              | $\checkmark$                   | ✓            | 2     | 5               | $\checkmark$               | 64                 | -                  | $\checkmark$       |                           | $\checkmark$          | $\checkmark$      | $\checkmark$       |                       |             | 3                  | -                          | 100TQFP |

| C8051F046-GQ         | 25          | 32 kB        | 4352 | $\checkmark$              | $\checkmark$                   | ✓            | 2     | 5               | $\checkmark$               | 64                 | -                  | $\checkmark$       |                           | $\checkmark$          | $\checkmark$      | $\checkmark$       |                       |             | 3                  | $\checkmark$               | 100TQFP |

| C8051F047            | 25          | 32 kB        | 4352 | $\checkmark$              | $\checkmark$                   | $\checkmark$ | 2     | 5               | $\checkmark$               | 32                 | -                  | $\checkmark$       |                           | $\checkmark$          | $\checkmark$      | $\checkmark$       |                       |             | 3                  | -                          | 64TQFP  |

| C8051F047-GQ         | 25          | 32 kB        | 4352 | $\checkmark$              | $\checkmark$                   | $\checkmark$ | 2     | 5               | $\checkmark$               | 32                 | -                  | $\checkmark$       |                           | $\checkmark$          | $\checkmark$      | $\checkmark$       |                       |             | 3                  | $\checkmark$               | 64TQFP  |

Table 1.1. Product Selection Guide

#### P6.2/A10m/A2 P6.3/A11m/A3 P6.4/A12m/A4 P6.0/A8m/A0 P6.1/A9m/A1 DAC1 P4.0 P4.1 P4.2 P4.3 P4.4 P4.5/ALE P5.0/A8 P5.1/A9 P5.2/A10 P5.3/A11 P5.4/A12 P5.5/A13 P5.6/A14 P5.7/A15 P4.6/RD P4.7/WR DGND DAC0 100 8 86 88 8 8 5 8 8 22 8 8 2 88 8 ₹ 8 2 2 88 2 1 2 75 P6.5/A13m/A5 TMS 1 TCK 2 74 P6.6/A14m/A6 3 TDI 73 P6.7/A15m/A7 4 72 P7.0/AD0/D0 TDO 5 71 P7.1/AD1/D1 /RST CANRX 6 70 P7.2/AD2/D2 7 69 P7.3/AD3/D3 CANTX AV+ 8 68 P7.4/AD4/D4 AGND 9 67 P7.5/AD5/D5 AGND 10 66 P7.6/AD6/D6 AV+ 11 65 P7.7/AD7/D7 VREF 12 64 VDD C8051F040/2/4/6 AGND 13 63 DGND AV+ 14 62 P0.0 61 P0.1 VREFD 15 60 P0.2 VREF0 16 VREF2 17 59 P0.3 58 P0.4 AIN0.0 18 57 P0.5/ALE AIN0.1 19 56 P0.6/RD AIN0.2 20 AIN0.3 21 55 P0.7/WR HVCAP 22 54 P3.0/AD0/D0 HVREF 23 53 P3.1/AD1/D1 52 P3.2/AD2/D2 HVAIN+ 24 HVAIN- 25 51 P3.3/AD3/D3 [<del>4</del>] 26 27 2 P1.6/AIN2.6/A14 [ P1.5/AIN2.5/A13 ] P1.1/AIN2.1/A9 [ P1.0/AIN2.0/A8 [ P2.7/A15m/A7 P2.6/A14m/A6 P2.5/A13m/A5 P2.4/A13m/A4 P2.4/A12m/A4 P2.3/A11m/A3 DQ DGND P2.0/A8m/A0 | P3.7/AD7/D7 | P3.6/AD6/D6 | P3.5/AD5/D5 | P3.4/AD4/D4 | XTAL1 XTAL2 MONEN P1.4/AIN2.4/A12 P1.2/AIN2.2/A10 P2.2/A10m/A2 P1.7/AIN2.7/A15 P1.3/AIN2.3/A11 P2.1/A9m/A1

Figure 4.1. TQFP-100 Pinout Diagram

## C8051F040/1/2/3/4/5/6/7

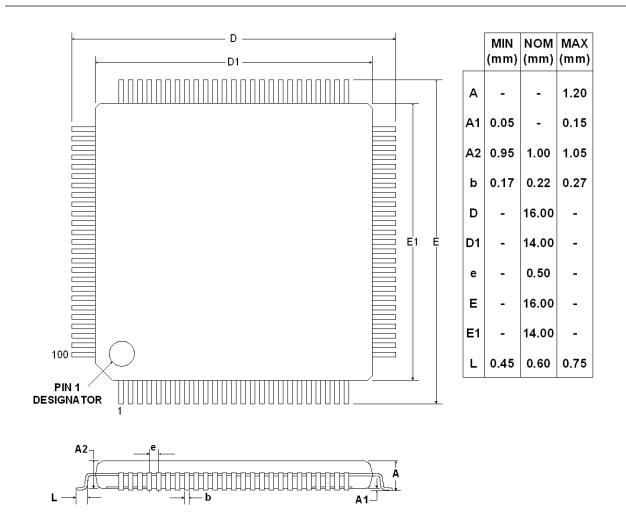

Figure 4.2. TQFP-100 Package Drawing

#### 7.3.2. Window Detector in Differential Mode

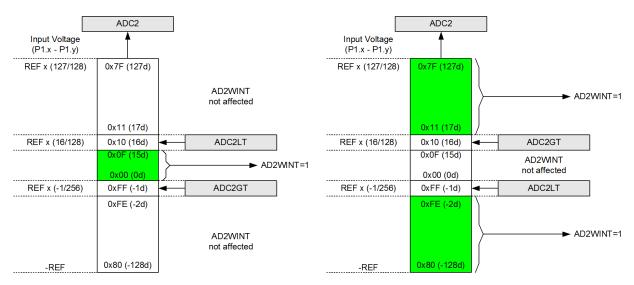

Figure 7.6 shows two example window comparisons for differential mode, with ADC2LT = 0x10 (+16d) and ADC2GT = 0xFF (-1d). Notice that in Differential mode, the codes vary from -VREF to VREF x (127/128) and are represented as 8-bit 2s complement signed integers. In the left example, an AD2WINT interrupt will be generated if the ADC2 conversion word (ADC2L) is within the range defined by ADC2GT and ADC2LT (if 0xFF (-1d) < ADC2 < 0x0F (16d)). In the right example, an AD2WINT interrupt will be generated if ADC2 is outside of the range defined by ADC2GT and ADC2LT (if ADC2 < 0xFF (-1d) or ADC2 > 0x10 (+16d)).

Figure 7.6. ADC Window Compare Examples, Differential Mode

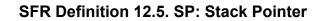

#### 12.2.7. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic 1. Future product versions may use these bits to implement new features, in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

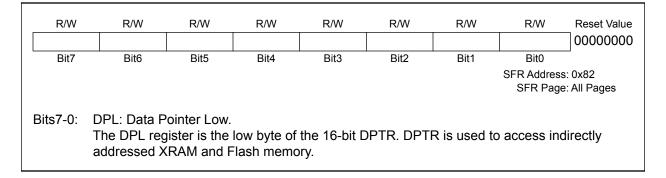

SFR Definition 12.6. DPL: Data Pointer Low Byte

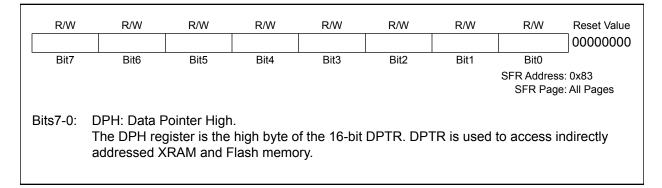

#### SFR Definition 12.7. DPH: Data Pointer High Byte

#### SFR Definition 12.9. ACC: Accumulator

| R/W<br>ACC.7 | R/W<br>ACC.6                | R/W<br>ACC.5 | R/W<br>ACC.4 | R/W<br>ACC.3 | R/W<br>ACC.2 | R/W<br>ACC.1 | R/W<br>ACC.0            | Reset Value             |

|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|-------------------------|-------------------------|

| Bit7         | Bit6                        | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0                    | Bit<br>Addressable      |

|              |                             |              |              |              |              |              | SFR Address<br>SFR Page | s: 0xE0<br>e: All Pages |

|              | ACC: Accum<br>This register |              | mulator for  | arithmetic o | operations.  |              |                         |                         |

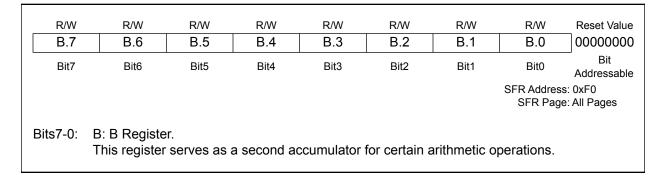

#### SFR Definition 12.10. B: B Register

| Interrupt Source          | Interrupt<br>Vector | Priority<br>Order | Pending Flag                   | Bit addressable? | Cleared by HW? | SFRPAGE (SFRPGEN = 1) | Enable<br>Flag     | Priority<br>Control |

|---------------------------|---------------------|-------------------|--------------------------------|------------------|----------------|-----------------------|--------------------|---------------------|

| Comparator 1              | 0x005B              | 11                | CP1FIF/CP1RIF<br>(CPT1CN.4/.5) |                  |                | 2                     | CP1IE<br>(EIE1.5)  | PCP1<br>(EIP1.5)    |

| Comparator 2              | 0x0063              | 12                | CP2FIF/CP2RIF<br>(CPT2CN.4/.5) |                  |                | 3                     | CP2IE<br>(EIE1.6)  | PCP2<br>(EIP1.6)    |

| Timer 3                   | 0x0073              | 14                | TF3 (TMR3CN.7)                 |                  |                | 1                     | ET3<br>(EIE2.0)    | PT3<br>(EIP2.0)     |

| ADC0 End of<br>Conversion | 0x007B              | 15                | ADC0INT<br>(ADC0CN.5)          | Y                |                | 0                     | EADC0<br>(EIE2.1)  | PADC0<br>(EIP2.1)   |

| Timer 4                   | 0x0083              | 16                | TF4 (TMR4CN.7)                 |                  |                | 2                     | ET4<br>(EIE2.2)    | PT4<br>(EIP2.2)     |

| ADC2 Window<br>Comparator | 0x0093              | 17                | AD2WINT<br>(ADC2CN.0)          |                  |                | 2                     | EWADC2<br>(EIE2.3) | PWADC2<br>(EIP2.3)  |

| ADC2 End of<br>Conversion | 0x008B              | 18                | ADC2INT<br>(ADC1CN.5)          |                  |                | 2                     | EADC1<br>(EIE2.4)  | PADC1<br>(EIP2.4)   |

| CAN Interrupt             | 0x009B              | 19                | CAN0CN.7                       |                  | Y              | 1                     | ECAN0<br>(EIE2.5)  | PCAN0<br>(EIP2.5)   |

| UART1                     | 0x00A3              | 20                | RI1 (SCON1.0)<br>TI1 (SCON1.1) |                  |                | 1                     | ES1<br>(EIE2.6)    | PS1<br>(EIP2.6)     |

Table 12.4. Interrupt Summary (Continued)

| SFR Definition 12 | .11. IE: Int | errupt Enable |

|-------------------|--------------|---------------|

|-------------------|--------------|---------------|

| R/W   | R/W                          | R/W           | R/W          | R/W           | R/W               | R/W          | R/W                   | Reset Value  |

|-------|------------------------------|---------------|--------------|---------------|-------------------|--------------|-----------------------|--------------|

| EA    | IEGF0                        | ET2           | ES0          | ET1           | EX1               | ET0          | EX0                   | 0000000      |

| Bit7  | Bit6                         | Bit5          | Bit1         | Bit0          | Bit<br>Addressabl |              |                       |              |

|       |                              |               |              |               |                   |              | SFR Addres<br>SFR Pag |              |

| Bit7: | EA: Enable A                 | All Interrupt | s.           |               |                   |              |                       |              |

|       | This bit globa               | ally enable   | s/disables a | ll interrupts | . It override     | s the indivi | dual interru          | pt mask set- |

|       | tings.                       |               |              |               |                   |              |                       |              |

|       | 0: Disable all               |               |              |               |                   |              |                       |              |

| 5.10  | 1: Enable ea                 |               |              | to its indivi | dual mask s       | setting.     |                       |              |

| Bit6: | IEGF0: Gene                  |               | •            |               | <b>.</b>          | hand         |                       |              |

| Bit5: | This is a gen                |               |              | se under so   | onware con        | Irol.        |                       |              |

| םווט. | ET2: Enable<br>This bit sets |               | •            | or 2 intorru  | unt               |              |                       |              |

|       | 0: Disable Ti                |               | •            |               | ipi.              |              |                       |              |

|       | 1: Enable int                |               | •            | ited hy the   | TF2 flag          |              |                       |              |

| Bit4: | ES0: Enable                  |               | •            |               | n 2 nag.          |              |                       |              |

|       | This bit sets                |               | •            | RT0 interru   | ıpt.              |              |                       |              |

|       | 0: Disable U/                |               | •            |               | F -               |              |                       |              |

|       | 1: Enable UA                 |               | •            |               |                   |              |                       |              |

| Bit3: | ET1: Enable                  | Timer 1 In    | terrupt.     |               |                   |              |                       |              |

|       | This bit sets                |               |              | er 1 interru  | ıpt.              |              |                       |              |

|       | 0: Disable all               |               |              |               |                   |              |                       |              |

|       | 1: Enable inter              |               |              | ited by the   | TF1 flag.         |              |                       |              |

| Bit2: | EX1: Enable                  |               | •            |               |                   |              |                       |              |

|       | This bit sets                |               | •            | al interrupt  | 1.                |              |                       |              |

|       | 0: Disable ex                |               | •            | مالا برما ام  |                   |              |                       |              |

| Bit1: | 1: Enable inter              |               | •            | ited by the   | /INTT pin.        |              |                       |              |

| DILI. | ET0: Enable<br>This bit sets |               | •            | or 0 intorru  | unt               |              |                       |              |

|       | 0: Disable all               |               | •            |               | ipt.              |              |                       |              |

|       | 1: Enable int                |               |              | ited by the   | TE0 flag          |              |                       |              |

| Bit0: | EX0: Enable                  |               | •            |               | n o nag.          |              |                       |              |

|       | This bit sets                |               |              | l interrupt   | 0.                |              |                       |              |

|       | 0: Disable ex                |               |              |               | -                 |              |                       |              |

|       |                              |               |              |               |                   |              |                       |              |

#### SFR Definition 13.1. WDTCN: Watchdog Timer Control

| R/W      | R/W                                                         | R/W                               | R/W           | R/W         | R/W           | R/W         | R/W                   | Reset Value             |

|----------|-------------------------------------------------------------|-----------------------------------|---------------|-------------|---------------|-------------|-----------------------|-------------------------|

|          |                                                             |                                   |               |             |               |             |                       | xxxxx111                |

| Bit7     | Bit6                                                        | Bit5                              | Bit4          | Bit3        | Bit2          | Bit1        | Bit0                  |                         |

|          |                                                             |                                   |               |             |               |             | SFR Addres<br>SFR Pag | s: 0xFF<br>e: All Pages |

| Bits7-0: | WDT Contro<br>Writing 0xA5<br>Writing 0xDE<br>Writing 0xFF  | both enab<br>followed v           | vithin 4 syst | em clocks b |               | ables the V | NDT.                  |                         |

| Bit4:    | Watchdog St<br>Reading the<br>0: WDT is ina<br>1: WDT is ac | atus Bit (w<br>WDTCN.[4<br>active | hen Read)     |             | hdog Timer    | Status.     |                       |                         |

| Bits2-0: | Watchdog Ti<br>The WDTCN<br>WDTCN.7 m                       | .[2:0] bits s                     | et the Watc   | hdog Timeo  | out Interval. | When writ   | ing these b           | its,                    |

#### 16.4. Multiplexed and Non-multiplexed Selection

The External Memory Interface is capable of acting in a Multiplexed mode or a Non-multiplexed mode, depending on the state of the EMD2 (EMI0CF.4) bit.

#### 16.4.1. Multiplexed Configuration

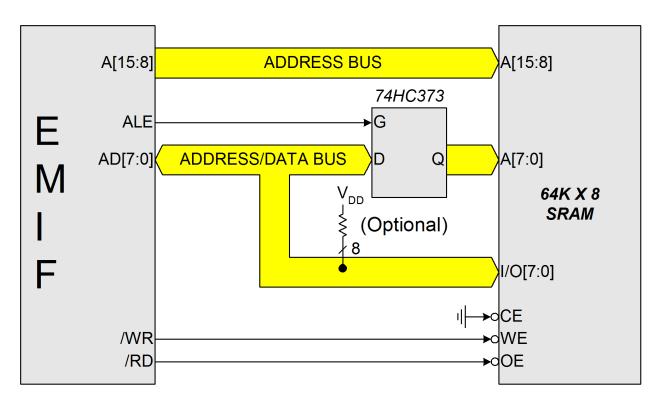

In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 16.1.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the 'Q' outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time /RD or /WR is asserted.

Figure 16.1. Multiplexed Configuration Example

|         |   |   |   | F | 20 |     |     |    |           |             |               | P            | 21           |            |      |                 | T           |        |       | F    | 2            |       |                |               |          |             |       | Р               | 3             |          |                |        | Crossbar Register Bits |

|---------|---|---|---|---|----|-----|-----|----|-----------|-------------|---------------|--------------|--------------|------------|------|-----------------|-------------|--------|-------|------|--------------|-------|----------------|---------------|----------|-------------|-------|-----------------|---------------|----------|----------------|--------|------------------------|

| PIN I/O | 0 | 1 | 2 | 3 | 4  | 5   | 6   | 7  | 0         | 1           | 2             | 3            | 4            | 5          | 6    | 7               | 0           | 1      | 2     | 3    | 4            | 5     | 6              | 7             | 0        | 1           | 2     | 3               | 4             | 5        | 6              | 7      | Crossbar Register Dits |

| ТХ0     | • |   |   |   |    |     |     |    |           |             |               |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | UART0EN: XBR0.2        |

| RX0     |   | ٠ |   |   |    |     |     |    |           |             |               |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | UARTUEN. ABRU.2        |

| SCK     | • |   | ٠ |   |    |     |     |    |           |             |               |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        |                        |

| MISO    |   | ٠ |   | ٠ |    |     |     |    |           |             |               |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | SPI0EN: XBR0.1         |

| MOSI    |   |   | ٠ |   | ٠  |     |     |    |           |             |               |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | SPIUEN: ABRU.I         |

| NSS     |   |   |   | ٠ |    | ٠   |     | NS | SS is     | s no        | ot as         | sig          | ned          | to         | a po | ort p           | oin '       | whe    | en tl | he S | PI i         | is pl | lace           | d ir          | 1 3-V    | wire        | e m   | ode             |               |          |                |        |                        |

| SDA     | • |   | ٠ | ٠ | ٠  | ٠   | ٠   |    |           |             |               |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | SMB0EN: XBR0.0         |

| SCL     |   | ٠ |   | ٠ | ٠  | ٠   | ٠   | ٠  |           |             |               |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | SWIDDEN. ABRU.U        |

| TX1     | • |   | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | ٠         |             |               |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | UART1EN: XBR2.2        |

| RX1     |   | ٠ |   | ٠ | ٠  | ٠   | ٠   | ٠  | •         | ٠           |               |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | UARTIEN: ABRZ.Z        |

| CEX0    | • |   | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | •         | •           | ٠             |              |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        |                        |

| CEX1    |   | • |   | ٠ | ٠  | ٠   | ٠   | ٠  | •         | •           | ٠             | ٠            |              |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        |                        |

| CEX2    |   |   | ٠ |   | ٠  | ٠   | ٠   | •  | •         | •           | ٠             | ٠            | ٠            |            |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        |                        |

| CEX3    |   |   |   | ٠ |    | ٠   | •   | •  | •         | •           | •             | •            | •            | •          |      |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | PCA0ME: XBR0.[5:3]     |

| CEX4    |   |   |   |   | ٠  |     | •   | •  | •         | •           | •             | •            | •            | •          | •    |                 |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        |                        |

| CEX5    |   |   |   |   |    | ٠   |     | •  | •         | •           | •             | •            | •            | ٠          | ٠    | •               |             |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        |                        |

| ECI     | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | ٠         | •           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           |        |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | ECI0E: XBR0.6          |

| CP0     | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | ٠         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      |       |      |              |       |                |               |          |             |       |                 |               |          |                |        | CP0E: XBR0.7           |

| CP1     | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | ٠         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     |      |              |       |                |               |          |             |       |                 |               |          |                |        | CP1E: XBR1.0           |

| CP2     | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | ٠         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    |              |       |                |               |          |             |       |                 |               |          |                |        | CP2E: XBR3.3           |

| т0      | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | ٠         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            |       |                |               |          |             |       |                 |               |          |                |        | T0E: XBR1.1            |

| /INT0   | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | •         | •           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     |                |               |          |             |       |                 |               |          |                |        | INT0E: XBR1.2          |

| T1      | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | ٠         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              |               |          |             |       |                 |               |          |                |        | T1E: XBR1.3            |

| /INT1   | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | •         | •           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              | ٠             |          |             |       |                 |               |          |                |        | INT1E: XBR1.4          |

| T2      | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | •         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              | ٠             | ٠        |             |       |                 |               |          |                |        | T2E: XBR1.5            |

| T2EX    | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | •         | •           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              | ٠             | •        | •           |       |                 |               |          |                |        | T2EXE: XBR1.6          |

| Т3      | • | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | •  | •         | •           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              | •             | •        | •           | •     |                 |               |          |                |        | T3E: XBR3.0            |

| T3EX    | • | • | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | ٠         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              | •             | •        | ٠           | ٠     | •               |               |          |                |        | T3EXE: XBR3.1          |

| T4      | ٠ | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | ٠         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              | ٠             | •        | ٠           | ٠     | ٠               | ٠             |          |                |        | T4E: XBR2.3            |

| T4EX    | • | • | ٠ | ٠ | ٠  | ٠   | ٠   | •  | •         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              | ٠             | •        | •           | •     | ٠               | •             | •        |                |        | T4EXE: XBR2.4          |

| /SYSCLK | ٠ | ٠ | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | •         | ٠           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              | ٠             | •        | ٠           | ٠     | ٠               | ٠             | •        | •              |        | SYSCKE: XBR1.7         |

| CNVSTR0 | • | • | ٠ | ٠ | ٠  | ٠   | ٠   | ٠  | •         | •           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | ٠     | ٠    | ٠            | ٠     | ٠              | •             | •        | ٠           | •     | •               | •             | •        | •              | •      | CNVSTE0: XBR2.0        |

| CNVSTR2 | • | • | • | ٠ | ٠  | ٠   | •   | •  | •         | •           | ٠             | ٠            | ٠            | ٠          | ٠    | ٠               | ٠           | ٠      | •     | •    | ٠            | ٠     | •              | •             | ٠        | ٠           | •     | ٠               | •             | •        | •              | •      | CNVSTE2: XBR3.2        |

|         |   |   |   |   |    | ALE | /RD | MR | AIN1.0/A8 | E AIN1.1/A9 | ation 1.2/A10 | Z AIN1.3/A11 | a AIN1.4/A12 | an 1.5/A13 |      | 표<br>AIN1.7/A15 | ₹<br>A8m/A0 | pam/A1 |       |      | a<br>412m/A4 |       | р<br>2 А14т/Аб | 다<br>머A15m/A7 | Z AD0/D0 | axii AD1/D1 | DZ/D2 | EQ/EQA<br>ta/No | u-d<br>AD4/D4 | a AD5/D5 | 90/90V<br>Data | AD7/D7 |                        |

#### Figure 17.3. Priority Crossbar Decode Table (EMIFLE = 0; P1MDIN = 0xFF)

#### 17.1.1. Crossbar Pin Assignment and Allocation

The Crossbar assigns Port pins to a peripheral if the corresponding enable bits of the peripheral are set to a logic 1 in the Crossbar configuration registers XBR0, XBR1, XBR2, and XBR3, shown in SFR Definition 17.1, SFR Definition 17.2, SFR Definition 17.3, and SFR Definition 17.4. For example, if the UART0EN bit (XBR0.2) is set to a logic 1, the TX0 and RX0 pins will be mapped to P0.0 and P0.1 respectively. Because UART0 has the highest priority, its pins will always be mapped to P0.0 and P0.1 when UART0EN is set to a logic 1. If a digital peripheral's enable bits are not set to a logic 1, then its ports are not accessible at the Port pins of the device. Also note that the Crossbar assigns pins to all associated functions when a serial communication peripheral is selected (i.e. SMBus, SPI, UART). It would be impossible, for example, to assign TX0 to a Port pin without assigning RX0 as well. Each combination of enabled peripherals results in a unique device pinout.

All Port pins on Ports 0 through 3 that are not allocated by the Crossbar can be accessed as General-Purpose I/O (GPIO) pins by reading and writing the associated Port Data registers (See SFR Definition 17.5,

| CAN Register<br>Index | Register Name          | Reset<br>Value | Notes                                                                             |

|-----------------------|------------------------|----------------|-----------------------------------------------------------------------------------|

| 0x00                  | CAN Control Register   | 0x0001         | Accessible in CIP-51 SFR Map                                                      |

| 0x01                  | Status Register        | 0x0000         | Accessible in CIP-51 SFR Map                                                      |

| 0x02                  | Error Register         | 0x0000         | Read Only                                                                         |

| 0x03                  | Bit Timing Register    | 0x2301         | Write Enabled by CCE Bit in CAN0CN                                                |

| 0x04                  | Interrupt Register     | 0x0000         | Read Only                                                                         |

| 0x05                  | Test Register          | 0x0000         | Bit 7 (RX) is determined by CAN bus                                               |

| 0x06                  | BRP Extension Register | 0x0000         | Write Enabled by TEST bit in CAN0CN                                               |

| 0x08                  | IF1 Command Request    | 0x0001         | CAN0ADR autoincrements in IF1 index space<br>(0x08 - 0x12) upon write to CAN0DATL |

| 0x09                  | IF1 Command Mask       | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0A                  | IF1 Mask 1             | 0xFFFF         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0B                  | IF1 Mask 2             | 0xFFFF         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0C                  | IF1 Arbitration 1      | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0D                  | IF1 Arbitration 2      | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0E                  | IF1 Message Control    | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0F                  | IF1 Data A1            | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x10                  | IF1 Data A2            | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x11                  | IF1 Data B1            | 0x0000         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x12                  | IF1 Data B2            | 0x0000         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x20                  | IF2 Command Request    | 0x0001         | CAN0ADR autoincrements in IF2 index space<br>(0x20 - 0x2A) upon write to CAN0DATL |

| 0x21                  | IF2 Command Mask       | 0x0000         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x22                  | IF2 Mask 1             | 0xFFFF         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x23                  | IF2 Mask 2             | 0xFFFF         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x24                  | 0x24 IF2 Arbitration 1 |                | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x25                  | IF2 Arbitration 2      | 0x0000         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

Table 18.2. CAN Register Index and Reset Values

### 20. Enhanced Serial Peripheral Interface (SPI0)

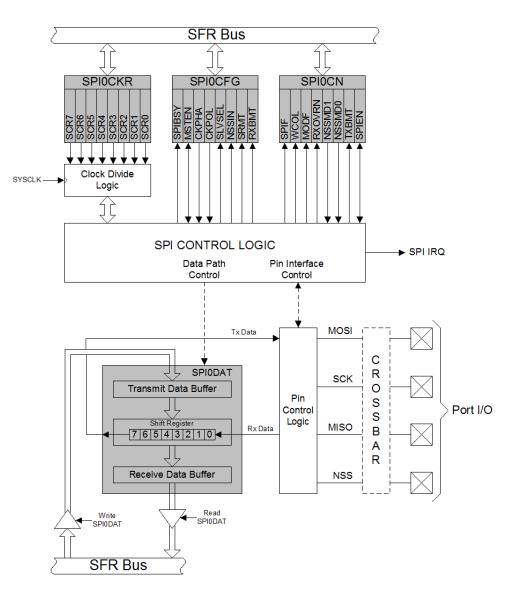

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

| R/W      | R/W                                                                                                                                                                             | R/W                              | R/W          | R/W         | R/W          | R/W            | R/W             | Reset Value      |  |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------|-------------|--------------|----------------|-----------------|------------------|--|--|--|--|--|--|

| SM00     | SM10                                                                                                                                                                            | SM20                             | REN0         | TB80        | RB80         | TI0            | RI0             | 0000000          |  |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                            | Bit5                             | Bit4         | Bit3        | Bit2         | Bit1           | Bit0            |                  |  |  |  |  |  |  |

|          |                                                                                                                                                                                 |                                  |              |             |              |                | SFR Addres      | ss: 0x98         |  |  |  |  |  |  |

|          |                                                                                                                                                                                 |                                  |              |             |              |                | SFR Pag         | ge: 0            |  |  |  |  |  |  |

|          |                                                                                                                                                                                 |                                  |              |             |              |                |                 |                  |  |  |  |  |  |  |

| Bits7-6: |                                                                                                                                                                                 | 0: Serial Po                     | rt Operatio  | n Mode:     |              |                |                 |                  |  |  |  |  |  |  |

|          | Write:                                                                                                                                                                          |                                  |              |             |              |                | <i>c</i>        |                  |  |  |  |  |  |  |

|          | When writte                                                                                                                                                                     | en, these bit                    | s select the | e Serial Po | ort Operatio | n Mode as      | follows:        |                  |  |  |  |  |  |  |

|          | SM00                                                                                                                                                                            | SM10                             |              | Мо          | do           |                | -               |                  |  |  |  |  |  |  |

|          |                                                                                                                                                                                 |                                  | Mod          |             |              |                | _               |                  |  |  |  |  |  |  |

|          | 0                                                                                                                                                                               | 0                                |              | -           | nronous Mo   |                |                 |                  |  |  |  |  |  |  |

|          | 0                                                                                                                                                                               | 1                                |              |             | Variable B   |                | _               |                  |  |  |  |  |  |  |

|          | 1                                                                                                                                                                               | 0                                |              |             | T, Fixed Ba  |                | _               |                  |  |  |  |  |  |  |

|          | 1                                                                                                                                                                               | 1                                | Mode 3: 9    | -Bit UAR I, | Variable B   | aud Rate       |                 |                  |  |  |  |  |  |  |

|          |                                                                                                                                                                                 | h:tt.                            |              |             |              | مام 4 مع ما    |                 |                  |  |  |  |  |  |  |

|          |                                                                                                                                                                                 | ese bits retu                    |              |             |              | s defined a    | bove.           |                  |  |  |  |  |  |  |

| Bit5:    |                                                                                                                                                                                 | tiprocessor (<br>n of this bit i |              |             |              | Operation I    | Mode            |                  |  |  |  |  |  |  |

|          | Mode 0: No                                                                                                                                                                      |                                  | is depende   |             |              | Speration      | NOUE.           |                  |  |  |  |  |  |  |

|          |                                                                                                                                                                                 |                                  | lid stop bit |             |              |                |                 |                  |  |  |  |  |  |  |

|          | Mode 1: Checks for valid stop bit.<br>0: Logic level of stop bit is ignored.                                                                                                    |                                  |              |             |              |                |                 |                  |  |  |  |  |  |  |

|          | 1: RIO will only be activated if stop bit is logic level 1.                                                                                                                     |                                  |              |             |              |                |                 |                  |  |  |  |  |  |  |

|          | Mode 2 and 3: Multiprocessor Communications Enable.                                                                                                                             |                                  |              |             |              |                |                 |                  |  |  |  |  |  |  |

|          | 0: Logic level of ninth bit is ignored.                                                                                                                                         |                                  |              |             |              |                |                 |                  |  |  |  |  |  |  |

|          |                                                                                                                                                                                 |                                  |              |             | erated only  | when the r     | ninth bit is lo | gic 1 and the    |  |  |  |  |  |  |

|          |                                                                                                                                                                                 | received add                     |              |             |              |                |                 |                  |  |  |  |  |  |  |

| Bit4:    | REN0: Rec                                                                                                                                                                       | eive Enable                      |              |             |              |                |                 |                  |  |  |  |  |  |  |

|          | This bit ena                                                                                                                                                                    | ables/disable                    | es the UAR   | T0 receive  | er.          |                |                 |                  |  |  |  |  |  |  |

|          | 0: UART0 r                                                                                                                                                                      | eception dis                     | sabled.      |             |              |                |                 |                  |  |  |  |  |  |  |

|          | 1: UART0 r                                                                                                                                                                      | eception en                      | abled.       |             |              |                |                 |                  |  |  |  |  |  |  |

| Bit3:    |                                                                                                                                                                                 | n Transmiss                      |              |             |              |                |                 |                  |  |  |  |  |  |  |

|          | •                                                                                                                                                                               |                                  |              | •           |              |                |                 | s 2 and 3. It is |  |  |  |  |  |  |

|          |                                                                                                                                                                                 | Modes 0 ar                       |              | or cleared  | by software  | e as require   | ed.             |                  |  |  |  |  |  |  |

| Bit2:    |                                                                                                                                                                                 | h Receive B                      |              |             |              |                |                 |                  |  |  |  |  |  |  |

|          |                                                                                                                                                                                 | -                                | -            |             |              |                |                 | n Mode 1, if     |  |  |  |  |  |  |

|          |                                                                                                                                                                                 | gic 0, RB80                      | is assigned  | the logic l | evel of the  | received s     | top bit. RB8    | is not used i    |  |  |  |  |  |  |

| <b></b>  | Mode 0.                                                                                                                                                                         | - 14 1 - 4 4                     | <b>-</b> 1   |             |              |                |                 |                  |  |  |  |  |  |  |

| Bit1:    |                                                                                                                                                                                 | nit Interrupt                    |              |             |              | 44 a d b 1 1 A |                 | • • Oth hit in   |  |  |  |  |  |  |

|          | •                                                                                                                                                                               | ware when                        | •            |             |              | •              | •               |                  |  |  |  |  |  |  |

|          |                                                                                                                                                                                 | at the begin                     |              |             |              |                |                 |                  |  |  |  |  |  |  |

|          |                                                                                                                                                                                 | etting this bit                  |              |             |              | UARTUI         | iterrupt serv   | nce routine.     |  |  |  |  |  |  |

| Bit0:    |                                                                                                                                                                                 | st be cleare<br>/e Interrupt     | •            | by SUIWA    | IC.          |                |                 |                  |  |  |  |  |  |  |

| 510.     |                                                                                                                                                                                 |                                  |              | ata hae ha  | en receive   |                | n (as solort    | ed by the        |  |  |  |  |  |  |

|          | Set by hardware when a byte of data has been received by UART0 (as selected by the SM20 bit). When the UART0 interrupt is enabled, setting this bit causes the CPU to vector to |                                  |              |             |              |                |                 |                  |  |  |  |  |  |  |

|          | •                                                                                                                                                                               |                                  | •            |             |              | •              | •               | •                |  |  |  |  |  |  |

#### SFR Definition 21.1. SCON0: UART0 Control

| R/W    | R/W                                                                                                           | R/W                                          | R/W                                          | R/W                      | R/W                                          | R/W          | R/W                   | Reset Value                                     |  |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------|----------------------------------------------|--------------|-----------------------|-------------------------------------------------|--|--|--|--|

| S1MODE | Ξ -                                                                                                           | MCE1                                         | REN1                                         | TB81                     | RB81                                         | TI1          | RI1                   | 0100000                                         |  |  |  |  |

| Bit7   | Bit6                                                                                                          | Bit5                                         | Bit4                                         | Bit3                     | Bit2                                         | Bit1         | Bit0                  | Bit<br>Addressable                              |  |  |  |  |

|        |                                                                                                               |                                              |                                              |                          |                                              |              | SFR Addres<br>SFR Pag | ess: 0x98                                       |  |  |  |  |

| Bit7:  | S1MODE: S<br>This bit sele<br>0: Mode 0: 8<br>1: Mode 1: 9                                                    | ects the UAF<br>8-bit UART                   | RT1 Operati<br>with Variable                 | on Mode.<br>e Baud Rat   |                                              |              |                       |                                                 |  |  |  |  |

| Bit6:  | UNUSED. F                                                                                                     |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

| Bit5:  | MCE1: Mult                                                                                                    | •                                            |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | The function of this bit is dependent on the Serial Port 0 Operation Mode.                                    |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | Mode 0: Checks for valid stop bit.                                                                            |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | 0: Logic level of stop bit is ignored.                                                                        |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | 1: RI1 will only be activated if stop bit is logic level 1.<br>Mode 1: Multiprocessor Communications Enable.  |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | 0: Logic level of ninth bit is ignored.                                                                       |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | 1: RI1 is set and an interrupt is generated only when the ninth bit is logic 1.                               |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

| Bit4:  | REN1: Receive Enable.                                                                                         |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | This bit enables/disables the UART receiver.                                                                  |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | 0: UART1 reception disabled.                                                                                  |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | 1: UART1 reception enabled.                                                                                   |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

| Bit3:  | TB81: Ninth Transmission Bit.                                                                                 |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

|        | The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode. If             |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

| D'10   | is not used in 8-bit UART Mode. Set or cleared by software as required.<br>RB81: Ninth Receive Bit.           |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

| Bit2:  |                                                                                                               |                                              |                                              |                          |                                              | :            |                       |                                                 |  |  |  |  |

|        | RB81 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9th data bit in Mode 1. |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

| Bit1:  | TI1: Transm                                                                                                   |                                              |                                              |                          |                                              |              |                       |                                                 |  |  |  |  |

| Dit i. | Set by hard<br>bit UART M                                                                                     | ware when a<br>ode, or at th<br>enabled, set | a byte of da<br>e beginning<br>ting this bit | of the STC<br>causes the | OP bit in 9-bi<br>CPU to vec                 | t UART Mo    | ode). Wher            | e 8th bit in 8-<br>1 the UART1<br>rrupt service |  |  |  |  |

| Bit0:  | RI1: Receiv                                                                                                   | •                                            | •                                            |                          |                                              |              |                       |                                                 |  |  |  |  |

|        |                                                                                                               | g time). Whe                                 | n the UAR1                                   | 1 interrupt              | s been recei<br>is enabled,<br>routine. This | setting this | bit to '1' c          | auses the                                       |  |  |  |  |

#### SFR Definition 22.1. SCON1: Serial Port 1 Control

| R/W   | R/W                                                                                   | R/W                                                  | R/W                                    | R/W                         | R/W           | R/W          | R/W                   | Reset Valu        |

|-------|---------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|-----------------------------|---------------|--------------|-----------------------|-------------------|

| TF1   | TR1                                                                                   | TF0                                                  | TR0                                    | IE1                         | IT1           | IE0          | IT0                   | 0000000           |

| Bit7  | Bit6                                                                                  | Bit5                                                 | Bit4                                   | Bit3                        | Bit2          | Bit1         | Bit0                  | Bit<br>Addressabl |

|       |                                                                                       |                                                      |                                        |                             |               |              | SFR Addres<br>SFR Pag |                   |

| it7:  | TF1: Timer 1<br>Set by hardw<br>matically clea<br>0: No Timer<br>1: Timer 1 ha        | vare when<br>ared when<br>1 overflow (               | Timer 1 ove<br>the CPU ve<br>detected. |                             |               |              |                       |                   |

| it6:  | TR1: Timer 1<br>0: Timer 1 di<br>1: Timer 1 er                                        | Run Conti Run Conti                                  |                                        |                             |               |              |                       |                   |