Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 32                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 13x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 64-TQFP                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f045-gqr   |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. System Overview

The C8051F04x family of devices are fully integrated mixed-signal System-on-a-Chip MCUs with 64 digital I/O pins (C8051F040/2/4/6) or 32 digital I/O pins (C8051F041/3/5/7), and an integrated CAN 2.0B controller. Highlighted features are listed below; refer to Table 1.1 for specific product feature selection.

- High-Speed pipelined 8051-compatible CIP-51 microcontroller core (up to 25 MIPS)

- Controller Area Network (CAN 2.0B) Controller with 32 message objects, each with its own indentifier mask.

- In-system, full-speed, non-intrusive debug interface (on-chip)

- True 12-bit (C8051F040/1) or 10-bit (C8051F042/3/4/5/6/7) 100 ksps 8-channel ADC with PGA and analog multiplexer

- High Voltage Difference Amplifier input to the 12/10-bit ADC (60 V Peak-to-Peak) with programmable gain.

- True 8-bit 500 ksps 8-channel ADC with PGA and analog multiplexer (C8051F040/1/2/3)

- Two 12-bit DACs with programmable update scheduling (C8051F040/1/2/3)

- 64 kB (C8051F040/1/2/3/4/5) or 32 kB (C8051F046/7) of in-system programmable Flash memory

- 4352 (4096 + 256) bytes of on-chip RAM

- External Data Memory Interface with 64 kB address space

- SPI, SMBus/I<sup>2</sup>C, and (2) UART serial interfaces implemented in hardware

- Five general purpose 16-bit Timers

- Programmable Counter/Timer Array with six capture/compare modules

- On-chip Watchdog Timer, V<sub>DD</sub> Monitor, and Temperature Sensor

With on-chip  $V_{DD}$  monitor, Watchdog Timer, and clock oscillator, the C8051F04x family of devices are truly stand-alone System-on-a-Chip solutions. All analog and digital peripherals are enabled/disabled and configured by user firmware. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware.

On-board JTAG debug circuitry allows non-intrusive (uses no on-chip resources), full speed, in-circuit programming and debugging using the production MCU installed in the final application. This debug system supports inspection and modification of memory and registers, setting breakpoints, watchpoints, single stepping, Run, and Halt commands. All analog and digital peripherals are fully functional while debugging using JTAG.

Each MCU is specified for 2.7 V to 3.6 V operation over the industrial temperature range (-45 to +85  $^{\circ}$ C). The Port I/Os, /RST, and JTAG pins are tolerant for input signals up to 5 V. The C8051F040/2/4/6 are available in a 100-pin TQFP and the C8051F041/3/5/7 are available in a 64-pin TQFP.

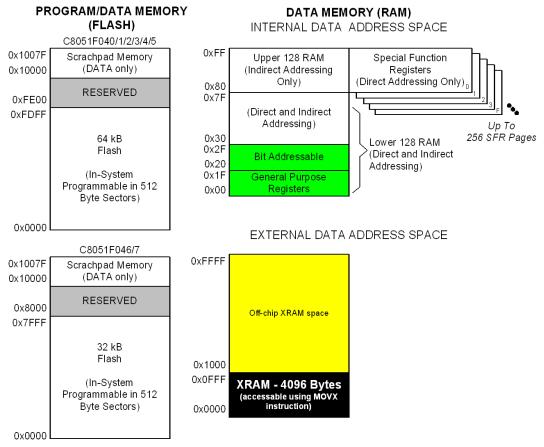

# 1.2. On-Chip Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The CIP-51 SFR address space contains up to 256 *SFR Pages*. In this way, the CIP-51 MCU can accommodate the many SFRs required to control and configure the various peripherals featured on the device. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

The CIP-51 in the C8051F04x MCUs additionally has an on-chip 4 kB RAM block and an external memory interface (EMIF) for accessing off-chip data memory or memory-mapped peripherals. The on-chip 4 byte block can be addressed over the entire 64 kB external data memory address range (overlapping 4 kB boundaries). External data memory address space can be mapped to on-chip memory only, off-chip memory only, or a combination of the two (addresses up to 4 kB directed to on-chip, above 4 kB directed to EMIF). The EMIF is also configurable for multiplexed or non-multiplexed address/data lines.

The MCU's program memory consists of 64 kB (C8051F040/1/2/3/4/5) or 32 kB (C8051F046/7) of Flash. This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. The 512 bytes from addresses 0xFE00 to 0xFFFF are reserved for the 64 kB devices. There is also a single 128 byte sector at address 0x10000 to 0x1007F, which may be useful as a small table for software constants. See Figure 1.7 for the MCU system memory map.

Figure 1.7. On-Chip Memory Map

| Neme     | Pin Nu     | Imbers     | Tune  | Description                                                                                                                            |  |  |

|----------|------------|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name     | F040/2/4/6 | F041/3/5/7 | Туре  | Description                                                                                                                            |  |  |

| AIN0.1   | 19         | 10         | A In  | ADC0 Input Channel 1 (See ADC0 Specification for complete description).                                                                |  |  |

| AIN0.2   | 20         | 11         | A In  | ADC0 Input Channel 2 (See ADC0 Specification for complete description).                                                                |  |  |

| AIN0.3   | 21         | 12         | A In  | ADC0 Input Channel 3 (See ADC0 Specification for complete description).                                                                |  |  |

| HVCAP    | 22         | 13         | A I/O | High Voltage Difference Amplifier Capacitor.                                                                                           |  |  |

| HVREF    | 23         | 14         | A In  | High Voltage Difference Amplifier Bias Reference.                                                                                      |  |  |

| HVAIN+   | 24         | 15         | A In  | High Voltage Difference Amplifier Positive Signal Input.                                                                               |  |  |

| HVAIN-   | 25         | 16         | A In  | High Voltage Difference Amplifier Negative Signal Input.                                                                               |  |  |

| CANTX    | 7          | 2          | D Out | Controller Area Network Transmit Output.                                                                                               |  |  |

| CANRX    | 6          | 1          | D In  | Controller Area Network Receive Input.                                                                                                 |  |  |

| DAC0     | 100        | 64         | A Out | Digital to Analog Converter 0 Voltage Output. (See DAC Specification for complete description). (C8051F040/1/2/3 only)                 |  |  |

| DAC1     | 99         | 63         | A Out | Digital to Analog Converter 1 Voltage Output. (See DAC Specification for complete description). (C8051F040/1/2/3 only)                 |  |  |

| P0.0     | 62         | 55         | D I/O | Port 0.0. See Port Input/Output section for complete description.                                                                      |  |  |

| P0.1     | 61         | 54         | D I/O | Port 0.1. See Port Input/Output section for complete description.                                                                      |  |  |

| P0.2     | 60         | 53         | D I/O | Port 0.2. See Port Input/Output section for complete description.                                                                      |  |  |

| P0.3     | 59         | 52         | D I/O | Port 0.3. See Port Input/Output section for complete description.                                                                      |  |  |

| P0.4     | 58         | 51         | D I/O | Port 0.4. See Port Input/Output section for complete description.                                                                      |  |  |

| P0.5/ALE | 57         | 50         | D I/O | ALE Strobe for External Memory Address bus (multi-<br>plexed mode) Port 0.5<br>See Port Input/Output section for complete description. |  |  |

| P0.6/RD  | 56         | 49         | D I/O | /RD Strobe for External Memory Address bus<br>Port 0.6<br>See Port Input/Output section for complete description.                      |  |  |

| P0.7/WR  | 55         | 48         | D I/O | /WR Strobe for External Memory Address bus<br>Port 0.7<br>See Port Input/Output section for complete description.                      |  |  |

Table 4.1. Pin Definitions (Continued)

#### P6.2/A10m/A2 P6.3/A11m/A3 P6.4/A12m/A4 P6.0/A8m/A0 P6.1/A9m/A1 DAC1 P4.0 P4.1 P4.2 P4.3 P4.4 P4.5/ALE P5.0/A8 P5.1/A9 P5.2/A10 P5.3/A11 P5.4/A12 P5.5/A13 P5.6/A14 P5.7/A15 P4.6/RD P4.7/WR DGND DAC0 100 8 86 88 8 8 5 8 8 22 8 8 2 88 8 ₹ 8 2 2 88 2 1 2 75 P6.5/A13m/A5 TMS 1 TCK 2 74 P6.6/A14m/A6 3 TDI 73 P6.7/A15m/A7 4 72 P7.0/AD0/D0 TDO 5 71 P7.1/AD1/D1 /RST CANRX 6 70 P7.2/AD2/D2 7 69 P7.3/AD3/D3 CANTX AV+ 8 68 P7.4/AD4/D4 AGND 9 67 P7.5/AD5/D5 AGND 10 66 P7.6/AD6/D6 AV+ 11 65 P7.7/AD7/D7 VREF 12 64 VDD C8051F040/2/4/6 AGND 13 63 DGND AV+ 14 62 P0.0 61 P0.1 VREFD 15 60 P0.2 VREF0 16 VREF2 17 59 P0.3 58 P0.4 AIN0.0 18 57 P0.5/ALE AIN0.1 19 56 P0.6/RD AIN0.2 20 AIN0.3 21 55 P0.7/WR HVCAP 22 54 P3.0/AD0/D0 HVREF 23 53 P3.1/AD1/D1 52 P3.2/AD2/D2 HVAIN+ 24 HVAIN- 25 51 P3.3/AD3/D3 [<del>4</del>] 26 27 2 P1.6/AIN2.6/A14 [ P1.5/AIN2.5/A13 ] P1.1/AIN2.1/A9 [ P1.0/AIN2.0/A8 [ P2.7/A15m/A7 P2.6/A14m/A6 P2.5/A13m/A5 P2.4/A13m/A4 P2.4/A12m/A4 P2.3/A11m/A3 DQ DGND P2.0/A8m/A0 | P3.7/AD7/D7 | P3.6/AD6/D6 | P3.5/AD5/D5 | P3.4/AD4/D4 | XTAL1 XTAL2 MONEN P1.4/AIN2.4/A12 P1.2/AIN2.2/A10 P2.2/A10m/A2 P1.7/AIN2.7/A15 P1.3/AIN2.3/A11 P2.1/A9m/A1

Figure 4.1. TQFP-100 Pinout Diagram

# C8051F040/1/2/3/4/5/6/7

#### 5.1.1. Analog Input Configuration

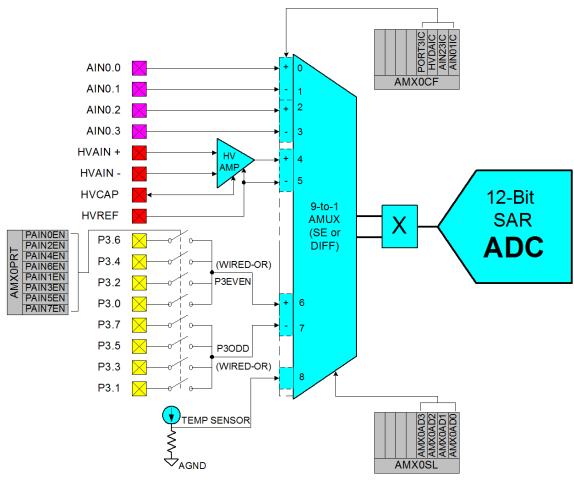

The analog multiplexer routes signals from external analog input pins, Port 3 I/O pins (See Section "17.1.5. Configuring Port 1, 2, and 3 Pins as Analog Inputs" on page 207), a High Voltage Difference Amplifier, and an on-chip temperature sensor as shown in Figure 5.2.

Figure 5.2. Analog Input Diagram

Analog signals may be input from four external analog input pins (AIN0.0 through AIN0.3) as differential or single-ended measurements. Additionally, Port 3 I/O Port Pins may be configured to input analog signals. Port 3 pins configured as analog inputs are selected using the Port Pin Selection register (AMX0PRT). Any number of Port 3 pins may be selected simultaneously as inputs to the AMUX. Even numbered Port 3 pins and odd numbered Port 3 pins are routed to separate AMUX inputs. (**Note:** Even port pins and odd port pins that are simultaneously selected will be shorted together as "wired-OR".) In this way, differential measurements may be made when using the Port 3 pins (voltage difference between selected even and odd Port 3 pins) as shown in Figure 5.2.

The High Voltage Difference Amplifier (HVDA) will accept analog input signals and reject up to 60 volts common-mode for differential measurement of up to the reference voltage to the ADC (0 to VREF volts). The output of the HVDA can be selected as an input to the ADC using the AMUX as any other channel is selected for input. (See Section "5.2. High-Voltage Difference Amplifier" on page 52).

# Table 7.2. ADC2 Electrical Characteristics

$V_{DD}$  = 3.0 V, AV+ = 3.0 V,  $V_{REF2}$  = 2.40 V (REFBE = 0), PGA2 = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                      | Conditions                         | Min      | Тур       | Max   | Units  |

|------------------------------------------------|------------------------------------|----------|-----------|-------|--------|

| DC Accuracy                                    |                                    |          |           |       |        |

| Resolution                                     |                                    |          | 8         |       | bits   |

| Integral Nonlinearity                          |                                    | —        | —         | ±1    | LSB    |

| Differential Nonlinearity                      | Guaranteed Monotonic               | _        | —         | ±1    | LSB    |

| Offset Error                                   |                                    | —        | 0.5±0.3   | —     | LSB    |

| Full Scale Error                               | Differential mode                  | —        | -1±0.2    | —     | LSB    |

| Dynamic Performance (10 kHz s                  | sine-wave input, 0 to 1 dB below   | w Full S | cale, 500 | ksps) |        |

| Signal-to-Noise Plus Distortion                |                                    | 45       | 47        | —     | dB     |

| Total Harmonic Distortion                      | Up to the 5 <sup>th</sup> harmonic | —        | -51       | —     | dB     |

| Spurious-Free Dynamic Range                    |                                    | _        | 52        | —     | dB     |

| Conversion Rate                                | 1                                  |          | 1         |       |        |

| SAR Conversion Clock<br>Frequency              |                                    | _        | _         | 6     | MHz    |

| Conversion Time in SAR Clocks                  |                                    | 8        |           | _     | clocks |

| Track/Hold Acquisition Time                    |                                    | 300      |           |       | ns     |

| Throughput Rate                                |                                    | —        | —         | 500   | ksps   |

| Analog Inputs                                  | 1                                  |          | 1         |       |        |

| Input Voltage Range                            | Single-ended                       | 0        | —         | VREF  | V      |

| Common Mode Range                              |                                    | 0        | —         | AV+   | V      |

| Input Capacitance                              |                                    | _        | 5         | —     | pF     |

| Power Specifications                           | 1                                  |          | 1         |       |        |

| Power Supply Current<br>(AV+ supplied to ADC2) | Operating Mode, 500 ksps           | _        | 420       | 900   | μA     |

| Power Supply Rejection                         |                                    | —        | ±0.3      | —     | mV/V   |

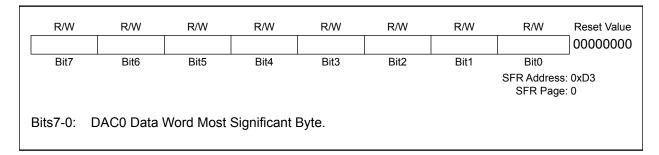

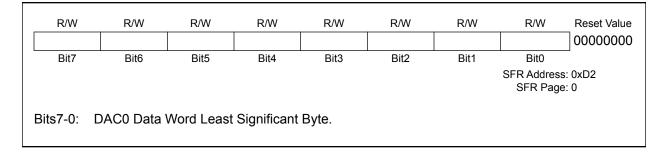

# 8.1. DAC Output Scheduling

Each DAC features a flexible output update mechanism which allows for seamless full-scale changes and supports jitter-free updates for waveform generation. The following examples are written in terms of DAC0, but DAC1 operation is identical.

#### 8.1.1. Update Output On-Demand

In its default mode (DAC0CN.[4:3] = '00') the DAC0 output is updated "on-demand" on a write to the highbyte of the DAC0 data register (DAC0H). It is important to note that writes to DAC0L are held, and have no effect on the DAC0 output until a write to DAC0H takes place. If writing a full 12-bit word to the DAC data registers, the 12-bit data word is written to the low byte (DAC0L) and high byte (DAC0H) data registers. Data is latched into DAC0 after a write to the corresponding DAC0H register, **so the write sequence should be DAC0L followed by DAC0H** if the full 12-bit resolution is required. The DAC can be used in 8bit mode by initializing DAC0L to the desired value (typically 0x00), and writing data to only DAC0H (also see **Section 8.2** for information on formatting the 12-bit DAC data word within the 16-bit SFR space).

#### 8.1.2. Update Output Based on Timer Overflow

Similar to the ADC operation, in which an ADC conversion can be initiated by a timer overflow independently of the processor, the DAC outputs can use a Timer overflow to schedule an output update event. This feature is useful in systems where the DAC is used to generate a waveform of a defined sampling rate by eliminating the effects of variable interrupt latency and instruction execution on the timing of the DAC output. When the DACOMD bits (DACOCN.[4:3]) are set to '01', '10', or '11', writes to both DAC data registers (DACOL and DACOH) are held until an associated Timer overflow event (Timer 3, Timer 4, or Timer 2, respectively) occurs, at which time the DACOH:DACOL contents are copied to the DAC input latches allowing the DAC output to change to the new value.

# 8.2. DAC Output Scaling/Justification

In some instances, input data should be shifted prior to a DAC0 write operation to properly justify data within the DAC input registers. This action would typically require one or more load and shift operations, adding software overhead and slowing DAC throughput. To alleviate this problem, the data-formatting feature provides a means for the user to program the orientation of the DAC0 data word within data registers DAC0H and DAC0L. The three DAC0DF bits (DAC0CN.[2:0]) allow the user to specify one of five data word orientations as shown in the DAC0CN register definition.

DAC1 is functionally the same as DAC0 described above. The electrical specifications for both DAC0 and DAC1 are given in Table 8.1.

# SFR Definition 8.1. DAC0H: DAC0 High Byte

# SFR Definition 8.2. DAC0L: DAC0 Low Byte

| Mnemonic          | Bytes                                      | Clock<br>Cycles |     |

|-------------------|--------------------------------------------|-----------------|-----|

| MOV direct, #data | Move immediate to direct byte              | 3               | 3   |

| MOV @Ri, A        | Move A to indirect RAM                     | 1               | 2   |

| MOV @Ri, direct   | Move direct byte to indirect RAM           | 2               | 2   |

| MOV @Ri, #data    | Move immediate to indirect RAM             | 2               | 2   |

| MOV DPTR, #data16 | Load DPTR with 16-bit constant             | 3               | 3   |

| MOVC A, @A+DPTR   | Move code byte relative DPTR to A          | 1               | 3   |

| MOVC A, @A+PC     | Move code byte relative PC to A            | 1               | 3   |

| MOVX A, @Ri       | Move external data (8-bit address) to A    | 1               | 3   |

| MOVX @Ri, A       | Move A to external data (8-bit address)    | 1               | 3   |

| MOVX A, @DPTR     | Move external data (16-bit address) to A   | 1               | 3   |

| MOVX @DPTR, A     | Move A to external data (16-bit address)   | 1               | 3   |

| PUSH direct       | Push direct byte onto stack                | 2               | 2   |

| POP direct        | Pop direct byte from stack                 | 2               | 2   |

| XCH A, Rn         | Exchange Register with A                   | 1               | 1   |

| XCH A, direct     | Exchange direct byte with A                | 2               | 2   |

| XCH A, @Ri        | Exchange indirect RAM with A               | 1               | 2   |

| XCHD A, @Ri       | Exchange low nibble of indirect RAM with A | 1               | 2   |

|                   | Boolean Manipulation                       |                 | 1   |

| CLR C             | Clear Carry                                | 1               | 1   |

| CLR bit           | Clear direct bit                           | 2               | 2   |

| SETB C            | Set Carry                                  | 1               | 1   |

| SETB bit          | Set direct bit                             | 2               | 2   |

| CPL C             | Complement Carry                           | 1               | 1   |

| CPL bit           | Complement direct bit                      | 2               | 2   |

| ANL C, bit        | AND direct bit to Carry                    | 2               | 2   |

| ANL C, /bit       | AND complement of direct bit to Carry      | 2               | 2   |

| ORL C, bit        | OR direct bit to carry                     | 2               | 2   |

| ORL C, /bit       | OR complement of direct bit to Carry       | 2               | 2   |

| MOV C, bit        | Move direct bit to Carry                   | 2               | 2   |

| MOV bit, C        | Move Carry to direct bit                   | 2               | 2   |

| JC rel            | Jump if Carry is set                       | 2               | 2/3 |

| JNC rel           | Jump if Carry is not set                   | 2               | 2/3 |

| JB bit, rel       | Jump if direct bit is set                  | 3               | 3/4 |

| JNB bit, rel      | Jump if direct bit is not set              | 3               | 3/4 |

| JBC bit, rel      | Jump if direct bit is set and clear bit    | 3               | 3/4 |

| ,                 | Program Branching                          |                 |     |

| ACALL addr11      | Absolute subroutine call                   | 2               | 3   |

| LCALL addr16      | Long subroutine call                       | 3               | 4   |

| RET               | Return from subroutine                     | 1               | 5   |

| RETI              | Return from interrupt                      | 1               | 5   |

| AJMP addr11       | Absolute jump                              | 2               | 3   |

| LJMP addr16       | Long jump                                  | 3               | 4   |

| SJMP rel          | Short jump (relative address)              | 2               | 3   |

| JMP @A+DPTR       | Jump indirect relative to DPTR             | 1               | 3   |

| JZ rel            | Jump if A equals zero                      | 2               | 2/3 |

# Table 12.1. CIP-51 Instruction Set Summary (Continued)

# Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register | Address | SFR Page  | Description                            | Page No.                                      |

|----------|---------|-----------|----------------------------------------|-----------------------------------------------|

| PCA0CPH4 | 0xEE    | 0         | PCA Capture 4 High                     | page 318                                      |

| PCA0CPH5 | 0xE2    | 0         | PCA Capture 5 High                     | page 318                                      |

| PCA0CPL0 | 0xFB    | 0         | PCA Capture 0 Low                      | page 318                                      |

| PCA0CPL1 | 0xFD    | 0         | PCA Capture 1 Low                      | page 318                                      |

| PCA0CPL2 | 0xE9    | 0         | PCA Capture 2 Low                      | page 318                                      |

| PCA0CPL3 | 0xEB    | 0         | PCA Capture 3 Low                      | page 318                                      |

| PCA0CPL4 | 0xED    | 0         | PCA Capture 4 Low                      | page 318                                      |

| PCA0CPL5 | 0xE1    | 0         | PCA Capture 5 Low                      | page 318                                      |

| PCA0CPM0 | 0xDA    | 0         | PCA Module 0 Mode Register             | page 316                                      |

| PCA0CPM1 | 0xDB    | 0         | PCA Module 1 Mode Register             | page 316                                      |

| PCA0CPM2 | 0xDC    | 0         | PCA Module 2 Mode Register             | page 316                                      |

| PCA0CPM3 | 0xDD    | 0         | PCA Module 3 Mode Register             | page 316                                      |

| PCA0CPM4 | 0xDE    | 0         | PCA Module 4 Mode Register             | page 316                                      |

| PCA0CPM5 | 0xDF    | 0         | PCA Module 5 Mode Register             | page 316                                      |

| PCA0H    | 0xFA    | 0         | PCA Counter High                       | page 317                                      |

| PCA0L    | 0xF9    | 0         | PCA Counter Low                        | page 317                                      |

| PCA0MD   | 0xD9    | 0         | PCA Mode                               | page 315                                      |

| PCON     | 0x87    | All Pages | Power Control                          | page 164                                      |

| PSCTL    | 0x8F    | 0         | Program Store R/W Control              | page 185                                      |

| PSW      | 0xD0    | All Pages | Program Status Word                    | page 151                                      |

| RCAP2H   | 0xCB    | 0         | Timer/Counter 2 Capture/Reload High    | page 303                                      |

| RCAP2L   | 0xCA    | 0         | Timer/Counter 2 Capture/Reload Low     | page 303                                      |

| RCAP3H   | 0xCB    | 1         | Timer/Counter 3 Capture/Reload High    | page 303                                      |

| RCAP3L   | 0xCA    | 1         | Timer/Counter 3 Capture/Reload Low     | page 303                                      |

| RCAP4H   | 0xCB    | 2         | Timer/Counter 4 Capture/Reload High    | page 303                                      |

| RCAP4L   | 0xCA    | 2         | Timer/Counter 4 Capture/Reload Low     | page 303                                      |

| REF0CN   | 0xD1    | 0         | Programmable Voltage Reference Control | page 114 <sup>4</sup> , page 118 <sup>5</sup> |

| RSTSRC   | 0xEF    | 0         | Reset Source Register                  | page 170                                      |

| SADDR0   | 0xA9    | 0         | UART 0 Slave Address                   | page 276                                      |

| SADEN0   | 0xB9    | 0         | UART 0 Slave Address Enable            | page 276                                      |

| SBUF0    | 0x99    | 0         | UART 0 Data Buffer                     | page 276                                      |

| SBUF1    | 0x99    | 1         | UART 1 Data Buffer                     | page 283                                      |

| SCON0    | 0x98    | 0         | UART 0 Control                         | page 274                                      |

| SCON1    | 0x98    | 1         | UART 1 Control                         | page 282                                      |

| SFRPAGE  | 0x84    | All Pages | SFR Page Register                      | page 142                                      |

| SFRPGCN  | 0x96    | F         | SFR Page Control Register              | page 142                                      |

| SFRNEXT  | 0x85    | All Pages | SFR Next Page Stack Access Register    | page 143                                      |

| SFRLAST  | 0x86    | All Pages | SFR Last Page Stack Access Register    | page 143                                      |

| SMB0ADR  | 0xC3    | 0         | SMBus Slave Address                    | page 250                                      |

| SMB0CN   | 0xC0    | 0         | SMBus Control                          | page 247                                      |

| SMB0CR   | 0xCF    | 0         | SMBus Clock Rate                       | page 248                                      |

| SMB0DAT  | 0xC2    | 0         | SMBus Data                             | page 249                                      |

| SMB0STA  | 0xC1    | 0         | SMBus Status                           | page 251                                      |

| SP       | 0x81    | All Pages | Stack Pointer                          | page 150                                      |

148

#### 12.3. Interrupt Handler

The CIP-51 includes an extended interrupt system supporting a total of 20 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interruptpending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE-EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

**Note:** Any instruction that clears the EA bit should be immediately followed by an instruction that has two or more opcode bytes. For example:

// in 'C': EA = 0; // clear EA bit EA = 0; // ... followed by another 2-byte opcode ; in assembly: CLR EA ; clear EA bit CLR EA ; ... followed by another 2-byte opcode

If an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears the EA bit), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. However, a read of the EA bit will return a '0' inside the interrupt service routine. When the "CLR EA" opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### 12.3.1. MCU Interrupt Sources and Vectors

The MCUs support 20 interrupt sources. Software can simulate an interrupt event by setting any interruptpending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 12.4. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

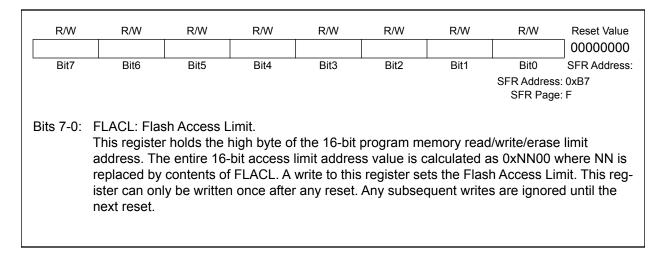

# SFR Definition 15.1. FLACL: Flash Access Limit

# SFR Definition 15.2. FLSCL: Flash Memory Control

|   | R/W             | R/W                                                                                                                                                                                                                                                                                                                               | R/W      | R/W      | R/W      | R/W      | R/W      | R/W                       | Reset Value  |

|---|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|---------------------------|--------------|

|   | FOSE            | FRAE                                                                                                                                                                                                                                                                                                                              | Reserved | Reserved | Reserved | Reserved | Reserved | FLWE                      | 10000000     |

|   | Bit7            | Bit6                                                                                                                                                                                                                                                                                                                              | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0                      | SFR Address: |

|   |                 |                                                                                                                                                                                                                                                                                                                                   |          |          |          |          |          | SFR Address:<br>SFR Page: |              |

| В |                 | FOSE: Flash One-Shot Timer Enable<br>This is the timer that turns off the sense amps after a Flash read.<br>0: Flash One-Shot Timer disabled.<br>1: Flash One-Shot Timer enabled (recommended setting).                                                                                                                           |          |          |          |          |          |                           |              |

| В | it6:            | FRAE: Flash Read Always Enable<br>0: Flash reads occur as necessary (recommended setting).                                                                                                                                                                                                                                        |          |          |          |          |          |                           |              |

| _ | its5-1:<br>it0: | <ol> <li>1: Flash reads occur every system clock cycle.</li> <li>RESERVED. Read = 00000b. Must Write 00000b.</li> <li>FLWE: Flash Write/Erase Enable</li> <li>This bit must be set to allow Flash writes/erases from user software.</li> <li>0: Flash writes/erases disabled.</li> <li>1: Flash writes/erases enabled.</li> </ol> |          |          |          |          |          |                           |              |

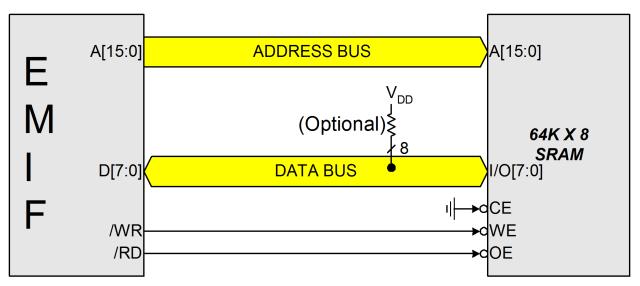

#### 16.4.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Nonmultiplexed Configuration is shown in Figure 16.2. See **Section "16.6.1. Non-multiplexed Mode" on page 196** for more information about Non-multiplexed operation.

Figure 16.2. Non-multiplexed Configuration Example

| Parameter           | Description                    | Min                     | Мах                      | Units |

|---------------------|--------------------------------|-------------------------|--------------------------|-------|

| T <sub>SYSCLK</sub> | System Clock Period            | 40                      |                          | ns    |

| T <sub>ACS</sub>    | Address/Control Setup Time     | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ACW</sub>    | Address/Control Pulse Width    | 1 x T <sub>SYSCLK</sub> | 16 x T <sub>SYSCLK</sub> | ns    |

| T <sub>ACH</sub>    | Address/Control Hold Time      | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEH</sub>   | Address Latch Enable High Time | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>ALEL</sub>   | Address Latch Enable Low Time  | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>WDS</sub>    | Write Data Setup Time          | 1 x T <sub>SYSCLK</sub> | 19 x T <sub>SYSCLK</sub> | ns    |

| T <sub>WDH</sub>    | Write Data Hold Time           | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |

| T <sub>RDS</sub>    | Read Data Setup Time           | 20                      |                          | ns    |

| T <sub>RDH</sub>    | Read Data Hold Time            | 0                       |                          | ns    |

Table 16.1. AC Parameters for External Memory Interface

| R/W      | R/W                                                                                                                                                                                                                                                                                 | R/W  | R/W  | R/W  | R/W  | R/W  | R/W                     | Reset Value        |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|-------------------------|--------------------|

| P7.7     | P7.6                                                                                                                                                                                                                                                                                | P7.5 | P7.4 | P7.3 | P7.2 | P7.1 | P7.0                    | 11111111           |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0                    | Bit<br>Addressable |

|          |                                                                                                                                                                                                                                                                                     |      |      |      |      |      | SFR Address<br>SFR Page |                    |

| Bits7-0: |                                                                                                                                                                                                                                                                                     |      |      |      |      |      |                         |                    |

| Note:    | P7.[7:0] can be driven by the External Data Memory Interface (as AD[7:0] in Multiplexed mode, or as D[7:0] in Non-multiplexed mode). See <b>Section "16. External Data Memory Interface and On-Chip XRAM" on page 187</b> for more information about the External Memory Interface. |      |      |      |      |      |                         |                    |

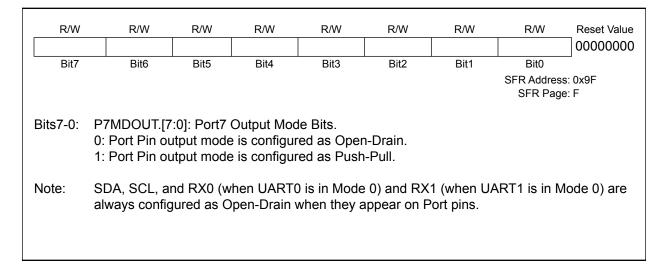

# SFR Definition 17.23. P7MDOUT: Port7 Output Mode

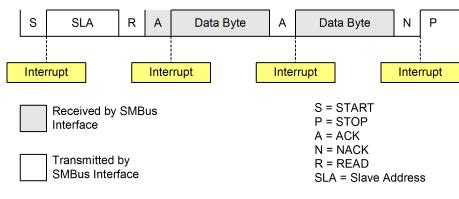

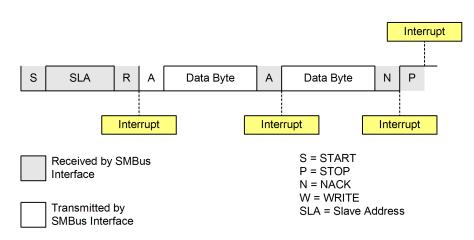

#### 19.3.2. Master Receiver Mode

Serial data is received on SDA while the serial clock is output on SCL. The SMBus0 interface generates a START followed by the first data byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 to indicate a "READ" operation. The SMBus0 interface receives serial data from the slave and generates the clock on SCL. After each byte is received, SMBus0 generates an ACK or NACK depending on the state of the AA bit in register SMB0CN. SMBus0 generates a STOP condition to indicate the end of the serial transfer.

#### Figure 19.5. Typical Master Receiver Sequence

#### **19.3.3. Slave Transmitter Mode**

Serial data is transmitted on SDA while the serial clock is received on SCL. The SMBus0 interface receives a START followed by data byte containing the slave address and direction bit. If the received slave address matches the address held in register SMB0ADR, the SMBus0 interface generates an ACK. SMBus0 will also ACK if the general call address (0x00) is received and the General Call Address Enable bit (SMB0ADR.0) is set to logic 1. In this case the data direction bit (R/W) will be logic 1 to indicate a "READ" operation. The SMBus0 interface receives the clock on SCL and transmits one or more bytes of serial data, waiting for an ACK from the master after each byte. SMBus0 exits slave mode after receiving a STOP condition from the master.

# Figure 19.6. Typical Slave Transmitter Sequence

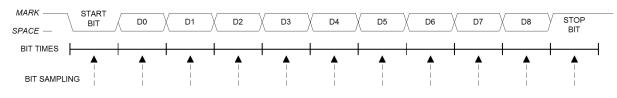

#### 21.1.3. Mode 2: 9-Bit UART, Fixed Baud Rate

Mode 2 provides asynchronous, full-duplex communication using a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. Mode 2 supports multiprocessor communications and hardware address recognition (see Section 21.2). On transmit, the ninth data bit is determined by the value in TB80 (SCON0.3). It can be assigned the value of the parity flag P in the PSW or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if RI0 is logic 0 and one of the following requirements are met:

- SM20 is logic 0

- SM20 is logic 1, the received 9th bit is logic 1, and the received address matches the UART0 address as described in Section 21.2.

If the above conditions are satisfied, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 are set.

The baud rate in Mode 2 is either SYSCLK / 32 or SYSCLK / 64, according to the value of the SMOD0 bit in register SSTA0.

$$BaudRate = 2^{SMOD0} \times \left(\frac{SYSCLK}{64}\right)$$

Equation 21.5. Mode 2 Baud Rate

Figure 21.5. UART0 Modes 2 and 3 Timing Diagram

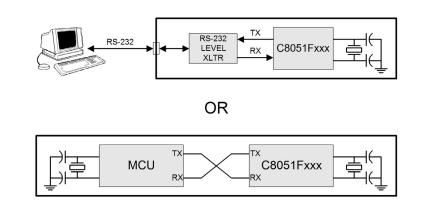

Figure 21.6. UART0 Modes 1, 2, and 3 Interconnect Diagram

# SFR Definition 23.10. RCAPnL: Timer n Capture Register Low Byte

| R/W          | R/W         | R/W          | R/W           | R/W         | R/W  | R/W  | R/W  | Reset Value                |

|--------------|-------------|--------------|---------------|-------------|------|------|------|----------------------------|

| Bit7         | Bit6        | Bit5         | Bit4          | Bit3        | Bit2 | Bit1 | Bit0 |                            |

| SFR Address: | RCAP2L: 0xC | A; RCAP3L: 0 | xCA; RCAP4L   | : 0xCA      |      |      |      |                            |

| SFR Page:    | RCAP2L: pag | e 0; RCAP3L: | page 1; RCAF  | P4L: page 2 |      |      |      |                            |

| m            | ne RCAPnL   | register ca  | ptures the lo |             |      |      |      | d in capture<br>the reload |

#### SFR Definition 23.11. RCAPnH: Timer n Capture Register High Byte

| R/W       | R/W                                                                                                                                                                                  | R/W          | R/W           | R/W          | R/W          | R/W         | R/W          | Reset Value  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|--------------|--------------|-------------|--------------|--------------|

|           |                                                                                                                                                                                      |              |               |              |              |             |              | 00000000     |

| Bit7      | Bit6                                                                                                                                                                                 | Bit5         | Bit4          | Bit3         | Bit2         | Bit1        | Bit0         |              |

| SFR Addr  | ess: RCAP2H: 0x0                                                                                                                                                                     | CB; RCAP3H:  | 0xCB; RCAP4   | H: 0xCB      |              |             |              |              |

| SFR P     | age: RCAP2H: pag                                                                                                                                                                     | je 0; RCAP3H | : page 1; RCA | P4H: page 2  |              |             |              |              |

|           |                                                                                                                                                                                      |              |               |              |              |             |              |              |

| Bits 7-0: | RCAPnH: Tir                                                                                                                                                                          | ner n Captı  | ure Register  | r High Byte. |              |             |              |              |

|           |                                                                                                                                                                                      | •            | •             | • •          | f Timer n wl | nen Timer r | n is confiau | ired in cap- |

|           | The RCAPnH register captures the high byte of Timer n when Timer n is configured in cap-<br>ture mode. When Timer n is configured in auto-reload mode, it holds the high byte of the |              |               |              |              |             |              |              |

|           | reload value.                                                                                                                                                                        |              |               |              |              |             |              |              |

|           |                                                                                                                                                                                      |              |               |              |              |             |              |              |

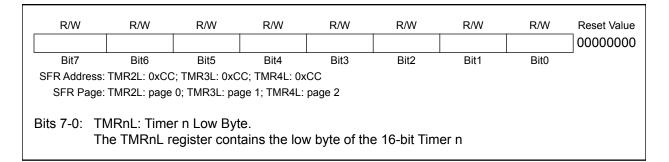

#### SFR Definition 23.12. TMRnL: Timer n Low Byte

#### 24.2.3. High-Speed Output Mode

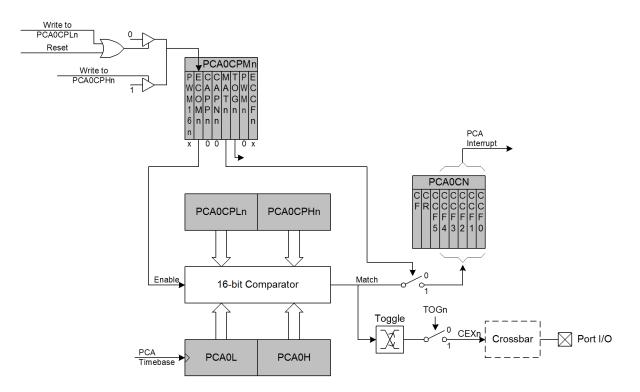

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode.

**Important Note About Capture/Compare Registers:** When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 24.6. PCA High-Speed Output Mode Diagram

# Table 25.1. Boundary Data Register Bit Definitions (Continued)

EXTEST provides access to both capture and update actions, while Sample only performs a capture.

| Bit                 | Action  | Target                      |

|---------------------|---------|-----------------------------|

| 75, 77, 79, 81, 83, | Capture | P4.n input from pin         |

| 85, 87, 89          | Update  | P4.n output to pin          |

| 90, 92, 94, 96, 98, | Capture | P5.n output enable from MCU |

| 100, 102, 104       | Update  | P5.n output enable to pin   |

| 91, 93, 95, 97, 99, | Capture | P5.n input from pin         |

| 101, 103, 105       | Update  | P5.n output to pin          |

| 106, 108, 110, 112, | Capture | P6.n output enable from MCU |

| 114, 116, 118, 120  | Update  | P6.n output enable to pin   |

| 107, 109, 111, 113, | Capture | P6.n input from pin         |

| 115, 117, 119, 121  | Update  | P6.n output to pin          |

| 122, 124, 126, 128, | Capture | P7.n output enable from MCU |

| 130, 132, 134, 136  | Update  | P7.n output enable to pin   |

| 123, 125, 127, 129, | Capture | P7.n input from pin         |

| 131, 133, 135, 137  | Update  | P7.n output to pin          |

#### 25.1.1. EXTEST Instruction

The EXTEST instruction is accessed via the IR. The Boundary DR provides control and observability of all the device pins as well as the Weak Pullup feature. All inputs to on-chip logic are set to logic 1.

#### 25.1.2. SAMPLE Instruction

The SAMPLE instruction is accessed via the IR. The Boundary DR provides observability and presetting of the scan-path latches.

#### 25.1.3. BYPASS Instruction

The BYPASS instruction is accessed via the IR. It provides access to the standard JTAG Bypass data register.

#### 25.1.4. IDCODE Instruction

The IDCODE instruction is accessed via the IR. It provides access to the 32-bit Device ID register.