Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                          |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 32                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 13x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 64-TQFP                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f045       |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 24.7. PCA0CPHn: PCA0 Capture Module High Byte         | . 318 |

|----------------------------------------------------------------------|-------|

| JTAG Register Definition 25.1. IR: JTAG Instruction Register         | . 319 |

| JTAG Register Definition 25.2. DEVICEID: JTAG Device ID Register     | . 322 |

| JTAG Register Definition 25.3. FLASHCON: JTAG Flash Control Register | . 324 |

| JTAG Register Definition 25.4. FLASHDAT: JTAG Flash Data             | . 325 |

| JTAG Register Definition 25.5. FLASHADR: JTAG Flash Address          | . 325 |

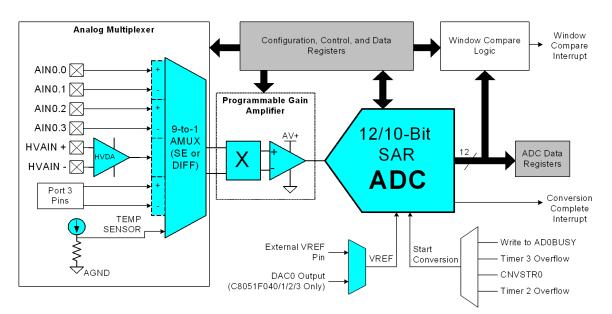

## 1.8. 12/10-Bit Analog to Digital Converter

The C8051F040/1 devices have an on-chip 12-bit SAR ADC (ADC0) with a 9-channel input multiplexer and programmable gain amplifier. With a maximum throughput of 100 ksps, the ADC offers true 12-bit performance with an INL of ±1LSB. C8051F042/3/4/5/6/7 devices include a 10-bit SAR ADC with similar specifications and configuration options. The ADC0 voltage reference is selected between the DAC0 output and an external VREF pin. On C8051F040/2/4/6 devices, ADC0 has its own dedicated VREF0 input pin; on C8051F041/3/5/7 devices, the ADC0 uses the VREFA input pin and, on the C8051F041/3, shares it with the 8-bit ADC2. The on-chip 15 ppm/°C voltage reference may generate the voltage reference for the on-chip ADCs or other system components via the VREF output pin.

The ADC is under full control of the CIP-51 microcontroller via its associated Special Function Registers. One input channel is tied to an internal temperature sensor, while the other eight channels are available externally. Each pair of the eight external input channels can be configured as either two single-ended inputs or a single differential input. The system controller can also put the ADC into shutdown mode to save power.

A programmable gain amplifier follows the analog multiplexer. The gain can be set to 0.5, 1, 2, 4, 8, or 16 and is software programmable. The gain stage can be especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large dc offset (in differential mode, a DAC could be used to provide the dc offset).

Conversions can be started in four ways; a software command, an overflow of Timer 2, an overflow of Timer 3, or an external signal input. This flexibility allows the start of conversion to be triggered by software events, external HW signals, or a periodic timer overflow signal. Conversion completions are indicated by a status bit and an interrupt (if enabled). The resulting 10- or 12-bit data word is latched into two SFRs upon completion of a conversion. The data can be right or left justified in these registers under software control.

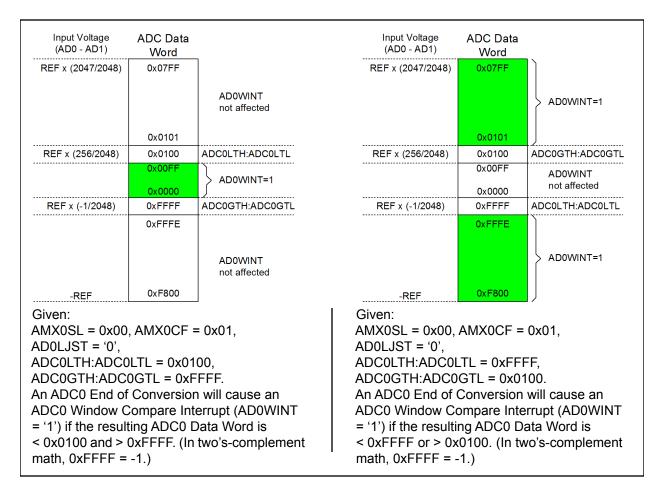

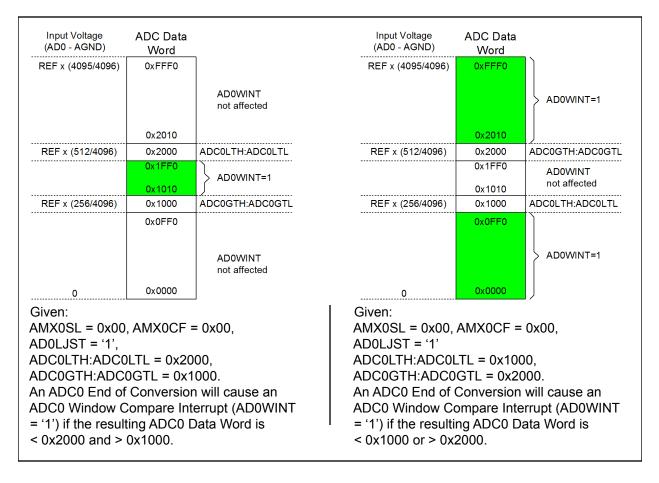

Window Compare registers for the ADC data can be configured to interrupt the controller when ADC data is within or outside of a specified range. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within the specified window.

Figure 1.12. 10/12-Bit ADC Block Diagram

| N                   | Pin Nu     | Pin Numbers |               | Description                                                                                                                                                                                                        |

|---------------------|------------|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                | F040/2/4/6 | F041/3/5/7  | Туре          | Description                                                                                                                                                                                                        |

| P1.0/AIN2.0/A8      | 36         | 29          | A In<br>D I/O | ADC1 Input Channel 0 (See ADC1 Specification for com-<br>plete description).<br>Bit 8 External Memory Address bus (Non-multiplexed<br>mode)<br>Port 1.0<br>See Port Input/Output section for complete description. |

| P1.1/AIN2.1/A9      | 35         | 28          | A In<br>D I/O | Port 1.1. See Port Input/Output section for complete description.                                                                                                                                                  |

| P1.2/AIN2.2/<br>A10 | 34         | 27          | A In<br>D I/O | Port 1.2. See Port Input/Output section for complete description.                                                                                                                                                  |

| P1.3/AIN2.3/<br>A11 | 33         | 26          | A In<br>D I/O | Port 1.3. See Port Input/Output section for complete description.                                                                                                                                                  |

| P1.4/AIN2.4/<br>A12 | 32         | 23          | A In<br>D I/O | Port 1.4. See Port Input/Output section for complete description.                                                                                                                                                  |

| P1.5/AIN2.5/<br>A13 | 31         | 22          | A In<br>D I/O | Port 1.5. See Port Input/Output section for complete description.                                                                                                                                                  |

| P1.6/AIN2.6/<br>A14 | 30         | 21          | A In<br>D I/O | Port 1.6. See Port Input/Output section for complete description.                                                                                                                                                  |

| P1.7/AIN2.7/<br>A15 | 29         | 20          | A In<br>D I/O | Port 1.7. See Port Input/Output section for complete description.                                                                                                                                                  |

| P2.0/A8m/A0         | 46         | 37          | D I/O         | Bit 8 External Memory Address bus (Multiplexed mode)<br>Bit 0 External Memory Address bus (Non-multiplexed<br>mode) Port 2.0<br>See Port Input/Output section for complete description.                            |

| P2.1/A9m/A1         | 45         | 36          | D I/O         | Port 2.1. See Port Input/Output section for complete description.                                                                                                                                                  |

| P2.2/A10m/A2        | 44         | 35          | D I/O         | Port 2.2. See Port Input/Output section for complete description.                                                                                                                                                  |

| P2.3/A11m/A3        | 43         | 34          | D I/O         | Port 2.3. See Port Input/Output section for complete description.                                                                                                                                                  |

| P2.4/A12m/A4        | 42         | 33          | D I/O         | Port 2.4. See Port Input/Output section for complete description.                                                                                                                                                  |

| P2.5/A13m/A5        | 41         | 32          | D I/O         | Port 2.5. See Port Input/Output section for complete description.                                                                                                                                                  |

| P2.6/A14m/A6        | 40         | 31          | D I/O         | Port 2.6. See Port Input/Output section for complete description.                                                                                                                                                  |

| P2.7/A15m/A7        | 39         | 30          | D I/O         | Port 2.7. See Port Input/Output section for complete description.                                                                                                                                                  |

Table 4.1. Pin Definitions (Continued)

## SFR Definition 5.6. ADC0CN: ADC0 Control

| R/W     | R/W               | R/W           | R/W            | R/W          | R/W           | R/W            | R/W           | Reset Valu       |  |  |  |

|---------|-------------------|---------------|----------------|--------------|---------------|----------------|---------------|------------------|--|--|--|

| AD0EN   | AD0TM             | AD0INT        | AD0BUSY        | AD0CM1       | AD0CM0        | AD0WINT        | AD0LJST       |                  |  |  |  |

| Bit7    | Bit6              | Bit5          | Bit4           | Bit3         | Bit2          | Bit1           | Bit0          | Bit<br>Addressab |  |  |  |

|         | SFR Address: 0xE8 |               |                |              |               |                |               |                  |  |  |  |

|         |                   |               |                |              |               |                | SFR Page      | e: 0             |  |  |  |

| Bit7:   | AD0EN: AD         | DC0 Enable    | e Bit.         |              |               |                |               |                  |  |  |  |

|         | 0: ADC0 D         | isabled. AD   | C0 is in low   | -power shu   | tdown.        |                |               |                  |  |  |  |

|         |                   |               | C0 is active   | and ready    | for data con  | versions.      |               |                  |  |  |  |

| Bit6:   | ADOTM: AD         |               |                | ling in cont |               |                | ion io in nu  |                  |  |  |  |

|         |                   |               | y AD0CM1-0     | -            | inuous unie:  | ss a convers   | ion is in pro | ocess            |  |  |  |

| Bit5:   |                   |               | rsion Comp     |              | ot Flag.      |                |               |                  |  |  |  |

|         |                   |               | red by softw   |              |               |                |               |                  |  |  |  |

|         | 0: ADCO ha        | as not com    | oleted a data  | a conversio  | n since the   | last time this | flag was cl   | eared.           |  |  |  |

|         |                   | •             | ed a data co   | nversion.    |               |                |               |                  |  |  |  |

| Bit4:   | AD0BUSY:          | ADC0 Bus      | sy Bit.        |              |               |                |               |                  |  |  |  |

|         | Read:             | onversion i   | s complete (   |              | sion is not c | urrently in pr | oares AD      |                  |  |  |  |

|         |                   |               | g edge of AE   |              |               |                | Ugress. AD    | 01111 15 50      |  |  |  |

|         |                   |               | s in progres   |              |               |                |               |                  |  |  |  |

|         | Write:            |               |                |              |               |                |               |                  |  |  |  |

|         | 0: No Effect      |               |                |              |               |                |               |                  |  |  |  |

|         |                   |               | version if AD  |              |               |                |               |                  |  |  |  |

| Bit3-2: | If AD0CM1-0       |               | art of Convei  | sion wode    | Select.       |                |               |                  |  |  |  |

|         |                   |               | initiated on   | everv write  | of '1' to AD( | BUSY.          |               |                  |  |  |  |

|         |                   |               | initiated on   |              |               |                |               |                  |  |  |  |

|         |                   |               | initiated on   |              |               | CNVSTR0.       |               |                  |  |  |  |

|         |                   |               | initiated on o | overflow of  | Timer 2.      |                |               |                  |  |  |  |

|         | If ADOTM =        |               | h tha write a  |              |               | lasta far 2 C  | ND alaaka f   | allowed by       |  |  |  |

|         | conversion        |               | in the write c | of 1 to ADU  | BOSY and I    | lasts for 3 SA | AR CIOCKS, I  |                  |  |  |  |

|         |                   |               | v the overflo  | w of Timer   | 3 and last fo | or 3 SAR clo   | cks. followe  | ed by con-       |  |  |  |

|         | version.          | 9 010. 100. 0 | ,              |              |               |                |               |                  |  |  |  |

|         | 10: ADC0 t        | racks only    | when CNVS      | TR0 input    | s logic low;  | conversion s   | starts on ris | ing              |  |  |  |

|         | CNVSTR0           |               |                |              |               |                |               |                  |  |  |  |

|         |                   | g started b   | y the overflo  | w of Timer   | 2 and last fo | or 3 SAR clo   | cks, followe  | ed by con-       |  |  |  |

| Bit1:   |                   |               | dow Compa      | ra Interrunt | Flag          |                |               |                  |  |  |  |

| 51(1.   |                   |               | ed by softwa   |              | r iag.        |                |               |                  |  |  |  |

|         |                   |               |                |              | as not occur  | red since this | s flag was la | ast cleared      |  |  |  |

|         |                   |               | nparison Dat   |              |               |                | J             |                  |  |  |  |

| Bit0:   |                   |               | Justify Selec  |              |               |                |               |                  |  |  |  |

|         | 0: Data in A      |               | COL register   | o oro right  | i i i i l     |                |               |                  |  |  |  |

|         |                   |               | COL register   | •            |               |                |               |                  |  |  |  |

### Figure 5.9. 12-Bit ADC0 Window Interrupt Example: Right Justified Differential Data

### Figure 5.10. 12-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data

|        |      |                        |        |                        | A      | MX0AD3-             | 0    |                    |       |                |

|--------|------|------------------------|--------|------------------------|--------|---------------------|------|--------------------|-------|----------------|

|        |      | 0000                   | 0001   | 0010                   | 0011   | 0100                | 0101 | 0110               | 0111  | 1xxx           |

|        | 0000 | AIN0.0                 | AIN0.1 | AIN0.2                 | AIN0.3 | HVDA                | AGND | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0001 | +(AIN0.0)<br>-(AIN0.1) |        | AIN0.2                 | AIN0.3 | HVDA                | AGND | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0010 | AIN0.0                 | AIN0.1 | +(AIN0.2)<br>-(AIN0.3) |        | HVDA                | AGND | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0011 | +(AIN0.0)<br>-(AIN0.1) |        | +(AIN0.2)<br>-(AIN0.3) |        | HVDA                | AGND | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0100 | AIN0.0                 | AIN0.1 | AIN0.2                 | AIN0.3 | +(HVDA)<br>-(HVREF) |      | P3EVEN             | P3ODD | TEMP<br>SENSOR |

|        | 0101 | +(AIN0.0)<br>-(AIN0.1) |        | AIN0.2                 | AIN0.3 | +(HVDA)<br>-(HVREF) |      | P3EVEN             | P3ODD | TEMP<br>SENSOR |

| 3-0    | 0110 | AIN0.0                 | AIN0.1 | +(AIN0.2)<br>-(AIN0.3) |        | +(HVDA)<br>-(HVREF) |      | P3EVEN             | P3ODD | TEMP<br>SENSOR |

| Bits   | 0111 | +(AIN0.0)<br>-(AIN0.1) |        | +(AIN0.2)<br>-(AIN0.3) |        | +(HVDA)<br>-(HVREF) |      | P3EVEN             | P3ODD | TEMP<br>SENSOR |

| AMX0CF | 1000 | AIN0.0                 | AIN0.1 | AIN0.2                 | AIN0.3 | HVDA                | AGND | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

| AM     | 1001 | +(AIN0.0)<br>-(AIN0.1) |        | AIN0.2                 | AIN0.3 | HVDA                | AGND | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1010 | AIN0.0                 | AIN0.1 | +(AIN0.2)<br>-(AIN0.3) |        | HVDA                | AGND | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1011 | +(AIN0.0)<br>-(AIN0.1) |        | +(AIN0.2)<br>-(AIN0.3) |        | HVDA                | AGND | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1100 | AIN0.0                 | AIN0.1 | AIN0.2                 | AIN0.3 | +(HVDA)<br>-(HVREF) |      | +P3EVEN<br>-P3ODD) |       | TEMP<br>SENSOR |

|        | 1101 | +(AIN0.0)<br>-(AIN0.1) |        | AIN0.2                 | AIN0.3 | +(HVDA)<br>-(HVREF) |      | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1110 | AIN0.0                 | AIN0.1 | +(AIN0.2)<br>-(AIN0.3) |        | +(HVDA)<br>-(HVREF) |      | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

|        | 1111 | +(AIN0.0)<br>-(AIN0.1) |        | +(AIN0.2)<br>-(AIN0.3) |        | +(HVDA)<br>-(HVREF) |      | +P3EVEN<br>-P3ODD  |       | TEMP<br>SENSOR |

## Table 6.1. AMUX Selection Chart (AMX0AD3-0 and AMX0CF3-0 bits)

Note: "P3EVEN" denotes even numbered and "P3ODD" odd numbered Port 3 pins selected in the AMX0PRT register.

| Mnemonic Description |                                                     | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 3/4             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/4             |

| NOP                  | No operation                                        | 1     | 1               |

## Table 12.1. CIP-51 Instruction Set Summary (Continued)

Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 64 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

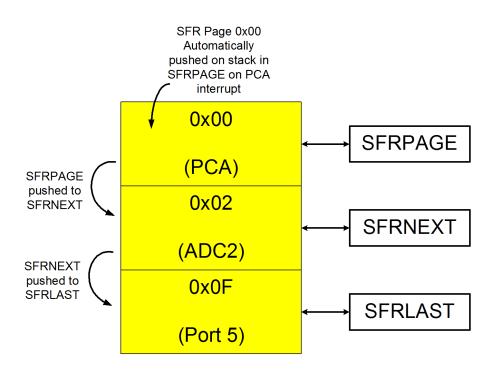

## Figure 12.6. SFR Page Stack Upon PCA Interrupt Occurring During an ADC2 ISR

On exit from the PCA interrupt service routine, the CIP-51 will return to the ADC2 Window Comparator ISR. On execution of the RETI instruction, SFR Page 0x00 used to access the PCA registers will be automatically popped off of the SFR Page Stack, and the contents of the SFRNEXT register will be moved to the SFRPAGE register. Software in the ADC2 ISR can continue to access SFR's as it did prior to the PCA interrupt. Likewise, the contents of SFRLAST are moved to the SFRNEXT register. Recall this was the SFR Page value 0x0F being used to access Port 5 before the ADC2 interrupt occurred. See Figure 12.7 below.

## Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| Register                  | Register Address |           | Description                      | Page No. |

|---------------------------|------------------|-----------|----------------------------------|----------|

| SPI0CFG                   | 0x9A             | 0         | SPI Configuration                | page 261 |

| SPI0CKR                   | 0x9D             | 0         | SPI Clock Rate Control           | page 263 |

| SPIOCN                    | 0xF8             | 0         | SPI Control                      | page 262 |

| SPI0DAT                   | 0x9B             | 0         | SPI Data                         | page 264 |

| SSTA0                     | 0x91             | 0         | UART0 Status and Clock Selection | page 275 |

| TCON                      | 0x88             | 0         | Timer/Counter Control            | page 293 |

| TH0                       | 0x8C             | 0         | Timer/Counter 0 High             | page 296 |

| TH1                       | 0x8D             | 0         | Timer/Counter 1 High             | page 296 |

| TL0                       | 0x8A             | 0         | Timer/Counter 0 Low              | page 295 |

| TL1                       | 0x8B             | 0         | Timer/Counter 1 Low              | page 296 |

| TMOD                      | 0x89             | 0         | Timer/Counter Mode               | page 294 |

| TMR2CF                    | 0xC9             | 0         | Timer/Counter 2 Configuration    | page 302 |

| TMR2CN                    | 0xC8             | 0         | Timer/Counter 2 Control          | page 301 |

| TMR2H                     | 0xCD             | 0         | Timer/Counter 2 High             | page 304 |

| TMR2L                     | 0xCC             | 0         | Timer/Counter 2 Low              | page 303 |

| TMR3CF                    | 0xC9             | 1         | Timer/Counter 3 Configuration    | page 302 |

| TMR3CN                    | 0xC8             | 1         | Timer 3 Control                  | page 301 |

| TMR3H                     | 0xCD             | 1         | Timer/Counter 3 High             | page 304 |

| TMR3L                     | 0xCC             | 1         | Timer/Counter 3 Low              | page 303 |

| TMR4CF                    | 0xC9             | 2         | Timer/Counter 4 Configuration    | page 302 |

| TMR4CN                    | 0xC8             | 2         | Timer/Counter 4 Control          | page 301 |

| TMR4H                     | 0xCD             | 2         | Timer/Counter 4 High             | page 304 |

| TMR4L                     | 0xCC             | 2         | Timer/Counter 4 Low              | page 303 |

| WDTCN                     | 0xFF             | All Pages | Watchdog Timer Control           | page 169 |

| XBR0                      | 0xE1             | F         | Port I/O Crossbar Control 0      | page 212 |

| XBR1                      | 0xE2             | F         | Port I/O Crossbar Control 1      | page 213 |

| XBR2                      | 0xE3             | F         | Port I/O Crossbar Control 2      | page 214 |

| XBR3                      | 0xE4             | F         | Port I/O Crossbar Control 3      | page 215 |

| 0x97, 0xA2,<br>0xCE, 0xDF | 0xB3, 0xB4,      |           | Reserved                         |          |

Notes:

1. Refers to a register in the C8051F040 only.

2. Refers to a register in the C8051F041 only.

3. Refers to a register in C8051F040/1/2/3 only.

4. Refers to a register in the C8051F040/2/4/6 only.

5. Refers to a register in the C8051F041/3/5/7 only.

| SFR Definition 12 | .11. IE: Int | errupt Enable |

|-------------------|--------------|---------------|

|-------------------|--------------|---------------|

| R/W   | R/W                                                                                                                 | R/W           | R/W      | R/W           | R/W         | R/W      | R/W                   | Reset Value       |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------|---------------|----------|---------------|-------------|----------|-----------------------|-------------------|--|--|--|--|

| EA    | IEGF0                                                                                                               | ET2           | ES0      | ET1           | EX1         | ET0      | EX0                   | 0000000           |  |  |  |  |

| Bit7  | Bit6                                                                                                                | Bit5          | Bit4     | Bit3          | Bit2        | Bit1     | Bit0                  | Bit<br>Addressabl |  |  |  |  |

|       |                                                                                                                     |               |          |               |             |          | SFR Addres<br>SFR Pag |                   |  |  |  |  |

| Bit7: | EA: Enable A                                                                                                        | All Interrupt | s.       |               |             |          |                       |                   |  |  |  |  |

|       | This bit globally enables/disables all interrupts. It overrides the individual interrupt mask set-                  |               |          |               |             |          |                       |                   |  |  |  |  |

|       | tings.                                                                                                              |               |          |               |             |          |                       |                   |  |  |  |  |

|       | 0: Disable all                                                                                                      |               |          |               |             |          |                       |                   |  |  |  |  |

| 5.10  | 1: Enable ea                                                                                                        |               |          | to its indivi | dual mask s | setting. |                       |                   |  |  |  |  |

| Bit6: | IEGF0: Gene                                                                                                         |               | •        |               | <b>.</b>    | hand     |                       |                   |  |  |  |  |

| Bit5: | This is a gen                                                                                                       |               |          | se under so   | onware con  | Irol.    |                       |                   |  |  |  |  |

| םווט. | ET2: Enable<br>This bit sets                                                                                        |               | •        | or 2 intorru  | unt         |          |                       |                   |  |  |  |  |

|       | 0: Disable Ti                                                                                                       |               | •        |               | ipi.        |          |                       |                   |  |  |  |  |

|       | 1: Enable int                                                                                                       |               | •        | ited hy the   | TF2 flag    |          |                       |                   |  |  |  |  |

| Bit4: | ES0: Enable                                                                                                         |               | •        |               | n 2 nag.    |          |                       |                   |  |  |  |  |

|       |                                                                                                                     |               | •        | RT0 interru   | ıpt.        |          |                       |                   |  |  |  |  |

|       | This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.                                    |               |          |               |             |          |                       |                   |  |  |  |  |

|       | 1: Enable UA                                                                                                        |               | •        |               |             |          |                       |                   |  |  |  |  |

| Bit3: | ET1: Enable                                                                                                         | Timer 1 In    | terrupt. |               |             |          |                       |                   |  |  |  |  |

|       | This bit sets                                                                                                       |               |          | er 1 interru  | ıpt.        |          |                       |                   |  |  |  |  |

|       | 0: Disable all Timer 1 interrupt.                                                                                   |               |          |               |             |          |                       |                   |  |  |  |  |

|       | 1: Enable inter                                                                                                     |               |          | ited by the   | TF1 flag.   |          |                       |                   |  |  |  |  |

| Bit2: | EX1: Enable                                                                                                         |               | •        |               |             |          |                       |                   |  |  |  |  |

|       | This bit sets                                                                                                       |               | •        | al interrupt  | 1.          |          |                       |                   |  |  |  |  |

|       | <ul><li>0: Disable external interrupt 1.</li><li>1: Enable interrupt requests generated by the /INT1 pin.</li></ul> |               |          |               |             |          |                       |                   |  |  |  |  |

| Bit1: |                                                                                                                     |               | •        | ited by the   | /INTT pin.  |          |                       |                   |  |  |  |  |

| DILI. | ET0: Enable<br>This bit sets                                                                                        |               |          | or 0 intorru  | unt         |          |                       |                   |  |  |  |  |

|       | 0: Disable all                                                                                                      |               | •        |               | ipt.        |          |                       |                   |  |  |  |  |

|       | 1: Enable int                                                                                                       |               |          | ited by the   | TE0 flag    |          |                       |                   |  |  |  |  |

| Bit0: | EX0: Enable                                                                                                         |               | •        |               | n o nag.    |          |                       |                   |  |  |  |  |

|       | This bit sets                                                                                                       |               |          | l interrupt   | 0.          |          |                       |                   |  |  |  |  |

|       | 0: Disable ex                                                                                                       |               |          |               | -           |          |                       |                   |  |  |  |  |

|       |                                                                                                                     |               |          |               |             |          |                       |                   |  |  |  |  |

| R/W      | R/W                             | R/W          | R/W            | R/W            | R/W           | R/W  | R/W                   | Reset Value              |

|----------|---------------------------------|--------------|----------------|----------------|---------------|------|-----------------------|--------------------------|

| -        | -                               | PT2          | PS0            | PT1            | PX1           | PT0  | PX0                   | 1100000                  |

| Bit7     | Bit6                            | Bit5         | Bit4           | Bit3           | Bit2          | Bit1 | Bit0                  | Bit<br>Addressable       |

|          |                                 |              |                |                |               |      | SFR Addres<br>SFR Pag | s: 0xB8<br>je: All Pages |

| Bits7-6: | UNUSED. R                       | ead = 11b,   | Write = don    | l't care.      |               |      |                       |                          |

| Bit5:    | PT2: Timer 2                    | Interrupt F  | Priority Cont  | rol.           |               |      |                       |                          |

|          | This bit sets                   | the priority | of the Time    | r 2 interrup   | t.            |      |                       |                          |

|          | 0: Timer 2 int                  |              |                |                | evel.         |      |                       |                          |

|          | 1: Timer 2 int                  |              | 0 1            |                |               |      |                       |                          |

| Bit4:    | PS0: UART0                      | •            |                |                |               |      |                       |                          |

|          | This bit sets                   |              |                |                |               |      |                       |                          |

|          | 0: UART0 int                    |              |                |                | evel.         |      |                       |                          |

| D:10.    | 1: UART0 int                    |              | • •            |                |               |      |                       |                          |

| Bit3:    | PT1: Timer 1                    |              |                |                |               |      |                       |                          |

|          | This bit sets<br>0: Timer 1 int |              |                | •              |               |      |                       |                          |

|          | 1: Timer 1 inf                  |              |                |                | evel.         |      |                       |                          |

| Bit2:    | PX1: Externa                    | •            | • •            |                |               |      |                       |                          |

|          | This bit sets                   |              |                |                | ot 1 interrup | t    |                       |                          |

|          | 0: External Ir                  |              |                |                |               |      |                       |                          |

|          | 1: External Ir                  |              |                |                |               |      |                       |                          |

| Bit1:    | PT0: Timer 0                    |              |                |                |               |      |                       |                          |

|          | This bit sets                   | the priority | of the Time    | r 0 interrup   | t.            |      |                       |                          |

|          | 0: Timer 0 int                  | terrupt prio | rity set to lo | w priority le  | evel.         |      |                       |                          |

|          | 1: Timer 0 int                  | •            | • •            |                |               |      |                       |                          |

| Bit0:    | PX0: Externa                    |              |                |                |               |      |                       |                          |

|          | This bit sets                   |              |                |                |               | t.   |                       |                          |

|          | 0: External Ir                  |              |                | •              |               |      |                       |                          |

|          | 1: External Ir                  | nterrupt 0 s | et to hiah p   | riority level. |               |      |                       |                          |

## SFR Definition 12.12. IP: Interrupt Priority

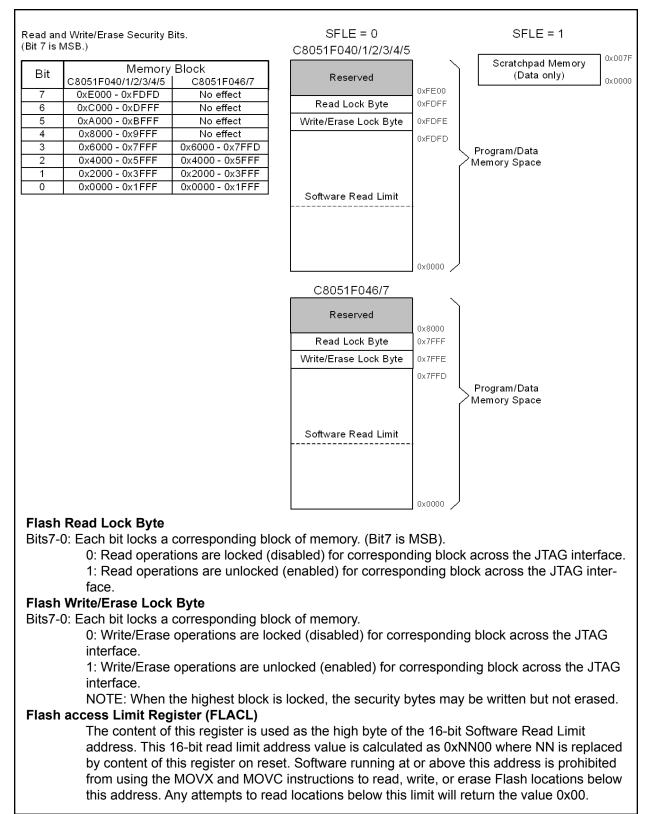

## Figure 15.1. Flash Program Memory Map and Security Bytes

### 18.1.1. CAN Controller Timing

The CAN controller's system clock ( $f_{sys}$ ) is derived from the CIP-51 system clock (SYSCLK). Note that an external oscillator (such as a quartz crystal) is typically required due to the high accuracy requirements for CAN communication. Refer to Section "4.10.4 Oscillator Tolerance Range" in the Bosch CAN User's Guide for further information regarding this topic.

### 18.1.2. Example Timing Calculation for 1 Mbit/Sec Communication

This example shows how to configure the CAN contoller timing parameters for a 1 Mbit/Sec bit rate. Table 18.1 shows timing-related system parameters needed for the calculation.

| Parameter                                          | Value       | Description                                                                                                                |

|----------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------|

| CIP-51 system clock (SYSCLK)                       | 22.1184 MHz | External oscillator in 'Crystal Oscillator Mode'. A<br>22.1184 MHz quartz crystal is connected between<br>XTAL1 and XTAL2. |

| CAN Controller system clock<br>(f <sub>sys</sub> ) | 22.1184 MHz | Derived from SYSCLK.                                                                                                       |

| CAN clock period (t <sub>sys</sub> )               | 45.211 ns   | Derived from 1/f <sub>sys</sub> .                                                                                          |

| CAN time quantum (t <sub>q</sub> )                 | 45.211 ns   | Derived from t <sub>sys</sub> x BRP <sup>1,2</sup>                                                                         |

| CAN bus length                                     | 10 m        | 5 ns/m signal delay between CAN nodes.                                                                                     |

| Propagation delay time <sup>3</sup>                | 400 ns      | 2 x (transceiver loop delay + bus line delay)                                                                              |

## Table 18.1. Background System Information

Notes:

1. The CAN time quantum (t<sub>q</sub>) is the smallest unit of time recognized by the CAN contoller. Bit timing parameters are often specified in integer multiples of the time quantum.

2. The Baud Rate Prescaler (BRP) is defined as the value of the BRP Extension Register plus 1. The BRP Extension Register has a reset value of 0x0000; the Baud Rate Prescaler has a reset value of 1.

3. Based on an ISO-11898 compliant transceiver. CAN does not specify a physical layer.

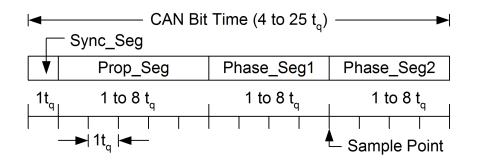

Each bit transmitted on a CAN network has 4 segments (Sync\_Seg, Prop\_Seg, Phase\_Seg1, and Phase\_Seg2), as shown in Figure 18.3. The sum of these segments determines the CAN bit time (1/bit rate). In this example, the desired bit rate is 1 Mbit/sec; therefore, the desired bit time is 1000 ns.

Figure 18.3. Four Segments of a CAN Bit Time

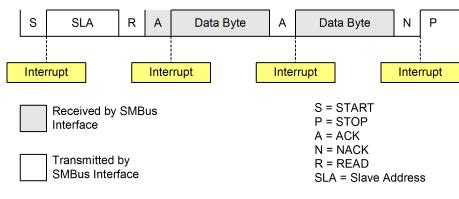

#### 19.3.2. Master Receiver Mode

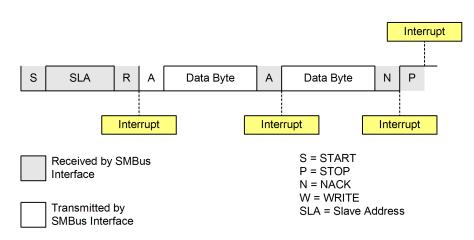

Serial data is received on SDA while the serial clock is output on SCL. The SMBus0 interface generates a START followed by the first data byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 to indicate a "READ" operation. The SMBus0 interface receives serial data from the slave and generates the clock on SCL. After each byte is received, SMBus0 generates an ACK or NACK depending on the state of the AA bit in register SMB0CN. SMBus0 generates a STOP condition to indicate the end of the serial transfer.

### Figure 19.5. Typical Master Receiver Sequence

### **19.3.3. Slave Transmitter Mode**

Serial data is transmitted on SDA while the serial clock is received on SCL. The SMBus0 interface receives a START followed by data byte containing the slave address and direction bit. If the received slave address matches the address held in register SMB0ADR, the SMBus0 interface generates an ACK. SMBus0 will also ACK if the general call address (0x00) is received and the General Call Address Enable bit (SMB0ADR.0) is set to logic 1. In this case the data direction bit (R/W) will be logic 1 to indicate a "READ" operation. The SMBus0 interface receives the clock on SCL and transmits one or more bytes of serial data, waiting for an ACK from the master after each byte. SMBus0 exits slave mode after receiving a STOP condition from the master.

## Figure 19.6. Typical Slave Transmitter Sequence

| R/W                                                                                                                                                                                                                                                                                                          | R/W                                                           | R/W                        | R/W                        | R/W  | R/W         | R/W       | R/W                       | Reset Value |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------|----------------------------|------|-------------|-----------|---------------------------|-------------|--|--|--|

| SLV6                                                                                                                                                                                                                                                                                                         | SLV5                                                          | SLV4                       | SLV3                       | SLV2 | SLV1        | SLV0      | GC                        | 00000000    |  |  |  |

| Bit7                                                                                                                                                                                                                                                                                                         | Bit6                                                          | Bit5                       | Bit4                       | Bit3 | Bit2        | Bit1      | Bit0                      |             |  |  |  |

|                                                                                                                                                                                                                                                                                                              |                                                               |                            |                            |      |             |           | SFR Address:<br>SFR Page: |             |  |  |  |

| Bits7-1: SLV6-SLV0: SMBus0 Slave Address.<br>These bits are loaded with the 7-bit slave address to which SMBus0 will respond when oper-<br>ating as a slave transmitter or slave receiver. SLV6 is the most significant bit of the address<br>and corresponds to the first bit of the address byte received. |                                                               |                            |                            |      |             |           |                           |             |  |  |  |

| Bit0:                                                                                                                                                                                                                                                                                                        | GC: General<br>This bit is us<br>0: General c<br>1: General c | ed to enabl<br>all address | e general c<br>is ignored. |      | (0x00) recc | ognition. |                           |             |  |  |  |

## SFR Definition 19.4. SMB0ADR: SMBus0 Address

#### 19.4.5. Status Register

The SMB0STA Status register holds an 8-bit status code indicating the current state of the SMBus0 interface. There are 28 possible SMBus0 states, each with a corresponding unique status code. The five most significant bits of the status code vary while the three least-significant bits of a valid status code are fixed at zero when SI = '1'. Therefore, all possible status codes are multiples of eight. This facilitates the use of status codes in software as an index used to branch to appropriate service routines (allowing 8 bytes of code to service the state or jump to a more extensive service routine).

For the purposes of user software, the contents of the SMB0STA register is only defined when the SI flag is logic 1. Software should never write to the SMB0STA register; doing so will yield indeterminate results. The 28 SMBus0 states, along with their corresponding status codes, are given in Table 19.1.

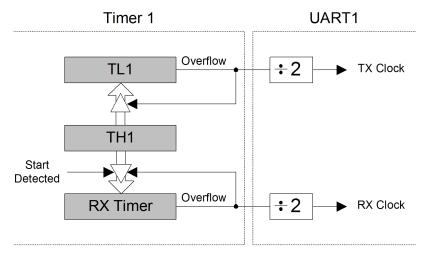

## 22.1. Enhanced Baud Rate Generation

The UART1 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 22.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 22.2. UART1 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "23.1.3. Mode 2: 8-bit Counter/ Timer with Auto-Reload" on page 291). The Timer 1 reload value should be set so that overflows will occur at two times the desired baud rate. Note that Timer 1 may be clocked by one of five sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, or the external oscillator clock / 8. For any given Timer 1 clock source, the UART1 baud rate is determined by Equation 22.1, where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and *TH1* is the high byte of Timer 1 (reload value).

$$UartBaudRate = \frac{T1_{CLK}}{(256 - TH1)} \times \frac{1}{2}$$

Timer 1 clock frequency is selected as described in **Section "23.1. Timer 0 and Timer 1" on page 289**. A quick reference for typical baud rates and system clock frequencies is given in Table 22.1 through Table 22.6. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1 (see Section "23.1. Timer 0 and Timer 1" on page 289 for more details).

| Frequency: 22.1184 MHz       Target<br>Baud Rate<br>(bps)     Baud Rate<br>% Error     Oscillator<br>Divide<br>Factor     Timer Clock<br>Source<br>Factor     SCA1-SCA0<br>(pre-scale<br>select)*     T1N | 1* Timer 1            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Baud Rate<br>(bps)         % Error<br>Factor         Divide<br>Source<br>Factor         Source<br>(pre-scale<br>select)*                                                                                  | Timer 1               |

|                                                                                                                                                                                                           | Reload<br>Value (hex) |

| 230400 0.00% 96 SYSCLK XX 1                                                                                                                                                                               | 0xD0                  |

| 115200 0.00% 192 SYSCLK XX 1                                                                                                                                                                              | 0xA0                  |

| 57600 0.00% 384 SYSCLK XX 1                                                                                                                                                                               | 0x40                  |

| 28800 0.00% 768 SYSCLK / 12 00 0                                                                                                                                                                          | 0xE0                  |

| 14400 0.00% 1536 SYSCLK / 12 00 0                                                                                                                                                                         | 0xC0                  |

| 9600 0.00% 2304 SYSCLK / 12 00 0                                                                                                                                                                          | 0xA0                  |

| 2400 0.00% 9216 SYSCLK / 48 10 0                                                                                                                                                                          | 0xA0                  |

| 1200 0.00% 18432 SYSCLK / 48 10 0                                                                                                                                                                         | 0x40                  |

| 230400 0.00% 96 EXTCLK / 8 11 0                                                                                                                                                                           | 0xFA                  |

| 115200 0.00% 192 EXTCLK / 8 11 0                                                                                                                                                                          | 0xF4                  |

| 57600 0.00% 384 EXTCLK / 8 11 0                                                                                                                                                                           | 0xE8                  |

| 28800 0.00% 768 EXTCLK / 8 11 0                                                                                                                                                                           | 0xD0                  |

| 14400 0.00% 1536 EXTCLK / 8 11 0                                                                                                                                                                          | 0xA0                  |

| 9600 0.00% 2304 EXTCLK / 8 11 0                                                                                                                                                                           | 0x70                  |

# Table 22.3. Timer Settings for Standard Baud Rates Using an External22.1184 MHz Oscillator

X = Don't care

\*Note: SCA1-SCA0 and T1M bit definitions can be found in Section 23.1.

| R/W   | R/W                                                                                                                                                                                                                                                                                                             | R/W                                         | R/W                                    | R/W                         | R/W           | R/W          | R/W                   | Reset Valu        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------|-----------------------------|---------------|--------------|-----------------------|-------------------|

| TF1   | TR1                                                                                                                                                                                                                                                                                                             | TF0                                         | TR0                                    | IE1                         | IT1           | IE0          | IT0                   | 0000000           |

| Bit7  | Bit6                                                                                                                                                                                                                                                                                                            | Bit5                                        | Bit4                                   | Bit3                        | Bit2          | Bit1         | Bit0                  | Bit<br>Addressabl |

|       |                                                                                                                                                                                                                                                                                                                 |                                             |                                        |                             |               |              | SFR Addres<br>SFR Pag |                   |

| it7:  | TF1: Timer 1<br>Set by hardw<br>matically clea<br>0: No Timer<br>1: Timer 1 ha                                                                                                                                                                                                                                  | vare when<br>ared when<br>1 overflow (      | Timer 1 ove<br>the CPU ve<br>detected. |                             |               |              |                       |                   |

| it6:  | TR1: Timer 1<br>0: Timer 1 di<br>1: Timer 1 er                                                                                                                                                                                                                                                                  | Run Conti Run Conti                         |                                        |                             |               |              |                       |                   |

| it5:  | <ul> <li>TF0: Timer 0 Overflow Flag.</li> <li>Set by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.</li> <li>0: No Timer 0 overflow detected.</li> <li>1: Timer 0 has overflowed.</li> </ul> |                                             |                                        |                             |               |              |                       |                   |

| it4:  | TR0: Timer 0 di<br>0: Timer 0 di<br>1: Timer 0 er                                                                                                                                                                                                                                                               | ) Run Conti<br>sabled.                      |                                        |                             |               |              |                       |                   |

| it3:  | IE1: External Interrupt 1.<br>This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be<br>cleared by software but is automatically cleared when the CPU vectors to the External Inter<br>rupt 1 service routine if IT1 = 1. This flag is the inverse of the /INT1 signal.  |                                             |                                        |                             |               |              |                       |                   |

| it2:  | IT1: Interrupt<br>This bit select<br>active-low.<br>0: /INT1 is le                                                                                                                                                                                                                                              | vel triggere                                | the configued, active-lo               | W.                          | nterrupt will | be falling-e | edge sensi            | tive or           |

| iit1: | 1: /INT1 is ed<br>IE0: External<br>This flag is so<br>cleared by so<br>rupt 0 service                                                                                                                                                                                                                           | I Interrupt 0<br>et by hardw<br>oftware but | ).<br>vare when a<br>is automation     | n edge/leve<br>cally cleare | d when the    | CPU vector   | rs to the Ex          |                   |

| itO:  | ITO: Interrupt<br>This bit select<br>active-low.<br>0: /INT0 is le                                                                                                                                                                                                                                              | t 0 Type Se<br>cts whether                  | lect.<br>the configu                   | ired /INT0 i                |               |              | -                     | tive or           |

### 25.2. Flash Programming Commands

The Flash memory can be programmed directly over the JTAG interface using the Flash Control, Flash Data, Flash Address, and Flash Scale registers. These Indirect Data Registers are accessed via the JTAG Instruction Register. Read and write operations on indirect data registers are performed by first setting the appropriate DR address in the IR register. Each read or write is then initiated by writing the appropriate Indirect Operation Code (IndOpCode) to the selected data register. Incoming commands to this register have the following format:

| 19:18     | 17:0      |

|-----------|-----------|

| IndOpCode | WriteData |

IndOpCode: These bit set the operation to perform according to the following table:

| IndOpCode | Operation |

|-----------|-----------|

| 0x        | Poll      |

| 10        | Read      |

| 11        | Write     |

The Poll operation is used to check the Busy bit as described below. Although a Capture-DR is performed, no Update-DR is allowed for the Poll operation. Since updates are disabled, polling can be accomplished by shifting in/out a single bit.

The Read operation initiates a read from the register addressed by the DRAddress. Reads can be initiated by shifting only 2 bits into the indirect register. After the read operation is initiated, polling of the Busy bit must be performed to determine when the operation is complete.

The write operation initiates a write of WriteData to the register addressed by DRAddress. Registers of any width up to 18 bits can be written. If the register to be written contains fewer than 18 bits, the data in Write-Data should be left-justified, i.e. its MSB should occupy bit 17 above. This allows shorter registers to be written in fewer JTAG clock cycles. For example, an 8-bit register could be written by shifting only 10 bits. After a Write is initiated, the Busy bit should be polled to determine when the next operation can be initiated. The contents of the Instruction Register should not be altered while either a read or write operation is busy.

Outgoing data from the indirect Data Register has the following format:

| 19 | 18:1     | 0    |  |

|----|----------|------|--|

| 0  | ReadData | Busy |  |

The Busy bit indicates that the current operation is not complete. It goes high when an operation is initiated and returns low when complete. Read and Write commands are ignored while Busy is high. In fact, if polling for Busy to be low will be followed by another read or write operation, JTAG writes of the next operation can be made while checking for Busy to be low. They will be ignored until Busy is read low, at which time the new operation will initiate. This bit is placed ate bit 0 to allow polling by single-bit shifts. When waiting for a Read to complete and Busy is 0, the following 18 bits can be shifted out to obtain the resulting data. ReadData is always right-justified. This allows registers shorter than 18 bits to be read using a reduced number of shifts. For example, the results from a byte-read requires 9 bit shifts (Busy + 8 bits).