# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Not For New Designs                                               |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | CANbus, EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 64                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 13x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 100-TQFP                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f046-gq    |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

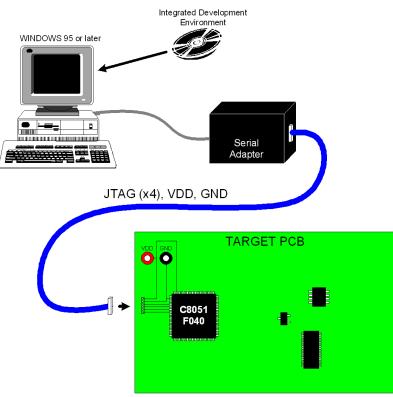

# 1.3. JTAG Debug and Boundary Scan

The C8051F04x family has on-chip JTAG boundary scan and debug circuitry that provides *non-intrusive*, *full speed, in-circuit debugging using the production part installed in the end application*, via the four-pin JTAG interface. The JTAG port is fully compliant to IEEE 1149.1, providing full boundary scan for test and manufacturing purposes.

Silicon Labs' debugging system supports inspection and modification of memory and registers, breakpoints, watchpoints, a stack monitor, and single stepping. No additional target RAM, program memory, timers, or communications channels are required. All the digital and analog peripherals are functional and work correctly while debugging. All the peripherals (except for the ADC and SMBus) are stalled when the MCU is halted, during single stepping, or at a breakpoint in order to keep them synchronized with instruction execution.

The C8051F040DK development kit provides all the hardware and software necessary to develop application code and perform in-circuit debugging with the C8051F04x MCUs. The development kit includes two target boards and a cable to facilitate evaluating a simple CAN communication network. The kit also includes software with a developer's studio and debugger, a target application board with the associated MCU installed, and the required cables and wall-mount power supply. The Serial Adapter takes its power from the application board; it requires roughly 20 mA at 2.7-3.6 V. For applications where there is not sufficient power available from the target system, the provided power supply can be connected directly to the Serial Adapter.

Silicon Labs' debug environment is a vastly superior configuration for developing and debugging embedded applications compared to standard MCU emulators, which use on-board "ICE Chips" and target cables and require the MCU in the application board to be socketed. Silicon Labs' debug environment both increases ease of use and preserves the performance of the precision, on-chip analog peripherals.

Figure 1.8. Development/In-System Debug Diagram

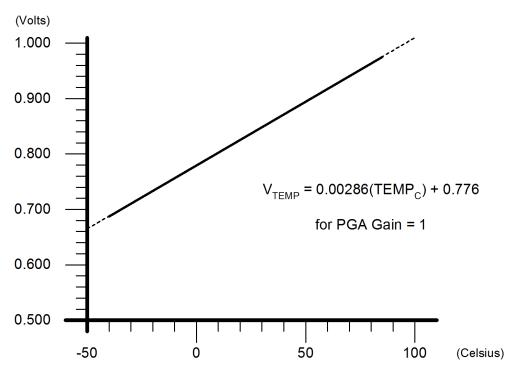

Figure 5.6. Temperature Sensor Transfer Function

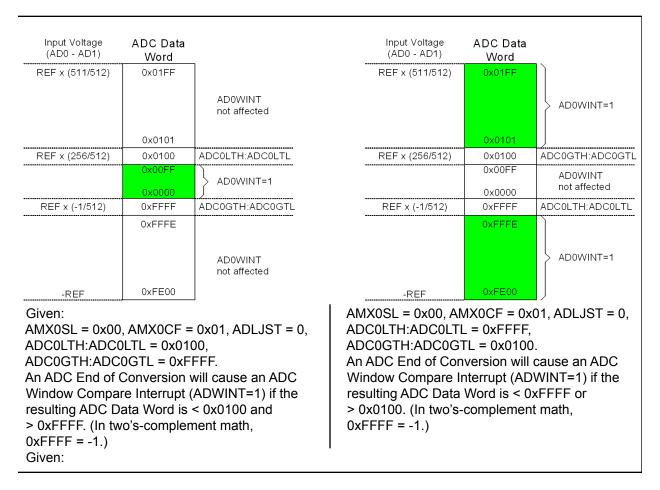

#### Figure 6.9. 10-Bit ADC0 Window Interrupt Example: Right Justified Differential Data

# 7.3. ADC2 Programmable Window Detector

The ADC2 Programmable Window Detector continuously compares the ADC2 output to user-programmed limits, and notifies the system when an out-of-bound condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD2WINT in ADC2CN) can also be used in polled mode. The reference words are loaded into the ADC2 Greater-Than and ADC2 Less-Than registers (ADC2GT and ADC2LT). Notice that the window detector flag can be asserted when the measured data is inside or outside the user-programmed limits, depending on the programming of the ADC2GT and ADC2LT registers.

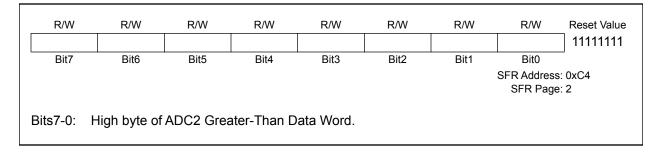

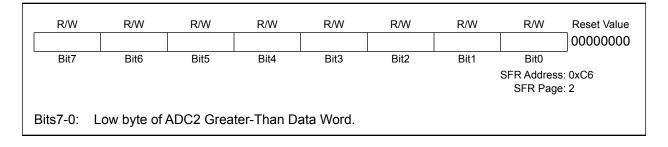

### SFR Definition 7.6. ADC2GT: ADC2 Greater-Than Data

# SFR Definition 7.7. ADC2LT: ADC2 Less-Than Data

#### 7.3.1. Window Detector in Single-Ended Mode

Figure 7.5 shows two example window comparisons for Single-ended mode, with ADC2LT = 0x20 and ADC2GT = 0x10. In Single-ended mode, the codes vary from 0 to VREF x (255/256) and are represented as 8-bit unsigned integers. In the left example, an AD2WINT interrupt will be generated if the ADC2 conversion word (ADC2) is within the range defined by ADC2GT and ADC2LT (if 0x10 < ADC2 < 0x20). In the right example, and AD2WINT interrupt will be generated if ADC2 is outside of the range defined by ADC2GT and ADC2LT (if ADC2 < 0x20). In the right example, and AD2WINT interrupt will be generated if ADC2 is outside of the range defined by ADC2GT and ADC2LT (if ADC2 < 0x10 or ADC2 > 0x20).

| R/W      | F                                       | R      | R           | R/W                             | R/W           | R/W         | R/W         | R/W                     | Reset Value |  |  |

|----------|-----------------------------------------|--------|-------------|---------------------------------|---------------|-------------|-------------|-------------------------|-------------|--|--|

| DAC0EI   | N -                                     |        | -           | DAC0MD1                         | DACOMDO       | DAC0DF2     | DAC0DF1     | DAC0DF0                 | 0000000     |  |  |

| Bit7     | Bi                                      | t6     | Bit5        | Bit4                            | Bit3          | Bit2        | Bit1        | Bit0                    | -           |  |  |

|          |                                         |        |             |                                 |               |             |             | SFR Address<br>SFR Page |             |  |  |

| Bit7:    | DAC0E                                   | EN: DA | C0 Enab     | le Bit.                         |               |             |             |                         |             |  |  |

|          | 0: DAC                                  | 0 Disa | abled. DA   | C0 Output p                     | in is disable | ed; DAC0 is | in low-powe | er shutdown             | mode.       |  |  |

|          | 1: DAC                                  | 0 Ena  | bled. DA    | C0 Output pi                    | in is active; | DAC0 is ope | erational.  |                         |             |  |  |

| Bits6-5: | UNUSED. Read = 00b; Write = don't care. |        |             |                                 |               |             |             |                         |             |  |  |

| Bits4-3: | DAC0MD1-0: DAC0 Mode Bits.              |        |             |                                 |               |             |             |                         |             |  |  |

|          | 00: DA                                  | C outp | out update  | es occur on a                   | a write to D  | AC0H.       |             |                         |             |  |  |

|          | 01: DA                                  | C out  | out update  | es occur on                     | Timer 3 ove   | rflow.      |             |                         |             |  |  |

|          | 10: DA                                  | C out  | out update  | es occur on                     | Timer 4 ove   | rflow.      |             |                         |             |  |  |

|          | 11: DA                                  | C outp | out update  | es occur on <sup>-</sup>        | Timer 2 ove   | rflow.      |             |                         |             |  |  |

| Bits2-0: |                                         |        |             | ata Format E                    |               |             |             |                         |             |  |  |

|          |                                         |        |             |                                 |               |             |             |                         |             |  |  |

|          | 000:                                    | The I  | nost sign   | ificant nibble                  | e of the DAC  | 0 Data Wor  | d is in DAC | 0H[3:0], whi            | le the leas |  |  |

|          |                                         | signi  | ficant byte | e is in DAC0                    | L.            |             |             |                         |             |  |  |

|          |                                         | D      | AC0H        |                                 |               |             | DACO        | L                       |             |  |  |

|          |                                         |        | MSB         |                                 |               |             |             |                         | LSB         |  |  |

|          |                                         |        |             | ·                               |               |             |             | i i                     | •           |  |  |

|          | 001:                                    |        | •           | ificant 5-bits<br>its are in DA |               | 0 Data Word | d is in DAC | 0H[4:0], whi            | le the leas |  |  |

|          |                                         | D      | AC0H        |                                 |               |             | DACO        | L                       |             |  |  |

|          |                                         | MS     | B           |                                 | Ī             |             |             | ]                       | LSB         |  |  |

|          |                                         |        |             |                                 |               |             |             |                         |             |  |  |

|          | 010:                                    |        |             | ificant 6-bits<br>its are in DA |               | 0 Data Word | d is in DAC | 0H[5:0], whi            | le the leas |  |  |

|          |                                         |        | AC0H        |                                 |               | DACOL       |             |                         |             |  |  |

|          | MSI                                     | 3      |             |                                 |               |             |             | LSB                     |             |  |  |

|          |                                         |        |             |                                 |               |             |             |                         |             |  |  |

|          | 011:                                    |        |             | ificant 7-bits<br>its are in DA |               | 0 Data Word | d is in DAC | 0H[6:0], whi            | le the leas |  |  |

|          |                                         |        | AC0H        |                                 |               |             | DACO        | L                       |             |  |  |

| М        | SB                                      |        |             |                                 |               |             |             | SB                      |             |  |  |

|          | ~-                                      |        |             |                                 |               |             |             | -                       |             |  |  |

|          | 1xx:                                    | The I  | most sian   | ificant 8-bits                  | of the DAC    | 0 Data Word | d is in DAC | 0H[7:01. whi            | le the leas |  |  |

|          |                                         |        |             | its are in DA                   |               |             |             | - L - ],                |             |  |  |

|          |                                         |        | AC0H        |                                 |               |             | DACO        | L                       |             |  |  |

| MSB      |                                         |        |             |                                 |               |             | LSB         |                         |             |  |  |

|          |                                         |        |             |                                 |               |             | LOD         |                         |             |  |  |

|          |                                         |        |             |                                 |               |             |             |                         |             |  |  |

|          |                                         |        |             |                                 |               |             |             |                         |             |  |  |

|          |                                         |        |             |                                 |               |             |             |                         |             |  |  |

|          |                                         |        |             |                                 |               |             |             |                         |             |  |  |

| R/W      | R/W                                                                   | R/W                                     | R/W                                          | R/W                                      | R/W                                        | R/W                                      | R/W                                      | Reset Value                        |

|----------|-----------------------------------------------------------------------|-----------------------------------------|----------------------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------|

|          |                                                                       |                                         |                                              |                                          |                                            |                                          |                                          | 0000000                            |

| Bit7     | Bit6                                                                  | Bit5                                    | Bit4                                         | Bit3                                     | Bit2                                       | Bit1                                     | Bit0                                     | -                                  |

|          |                                                                       |                                         |                                              |                                          |                                            |                                          | SFR Address<br>SFR Page                  | :: 0x85<br>:: All Pages            |

| 3its7-0: | SFR page co<br>Stack: SFRF<br>The SFRPAO<br>Page Stack.<br>SFR Page S | AGE is the<br>GE, SFRST<br>Only interre | first entry, S<br>ACK, and S<br>upts and ret | SFRNEXT is<br>FRLAST by<br>turns from in | s the secon<br>rtes may be<br>nterrupt ser | d, and SFR<br>used alter<br>vice routine | LAST is thi<br>the context<br>s push and | rd entry.<br>in the SFF<br>pop the |

|          | Write:<br>Sets the SFF                                                |                                         | tained in the                                | e second by                              | te of the SI                               | R Stack. T                               | his will cau                             | se the                             |

|          | SFRPAGE S                                                             | FR to have                              | this SFR p                                   | age value u                              | pon a retur                                | n from inter                             | rupt.                                    |                                    |

# SFR Definition 12.4. SFR Last Register: SFRLAST

| R/W  | R/W                                                                                                              | R/W                                                        | R/W                                                      | R/W                                                      | R/W                                      | R/W                        | R/W                       | _ Reset Value              |

|------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|------------------------------------------|----------------------------|---------------------------|----------------------------|

|      |                                                                                                                  |                                                            |                                                          |                                                          |                                          |                            |                           | 00000000                   |

| Bit7 | Bit6                                                                                                             | Bit5                                                       | Bit4                                                     | Bit3                                                     | Bit2                                     | Bit1                       | Bit0                      |                            |

|      |                                                                                                                  |                                                            |                                                          |                                                          |                                          |                            | SFR Address               | s: 0x86                    |

|      |                                                                                                                  |                                                            |                                                          |                                                          |                                          |                            | SFR Page                  | e: All Pages               |

|      | Stack: SFRP<br>entry. The SF<br>not cause the<br>routine push<br>Write:<br>Sets the SFF<br>have this SF<br>Read: | FR stack by<br>e stack to 'p<br>and pop th<br>R Page in th | tes may be<br>bush' or 'po<br>e SFR Pagi<br>e last entry | used alter to<br>o'. Only inte<br>e Stack.<br>of the SFR | the context<br>rrupts and<br>Stack. This | in the SFR<br>returns fron | Page Stac<br>n the intern | k, and will<br>upt service |

## Table 12.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved.

| -        |      | SFR Page  | Description                            | Page No.                                      |

|----------|------|-----------|----------------------------------------|-----------------------------------------------|

| PCA0CPH4 | 0xEE | 0         | PCA Capture 4 High                     | page 318                                      |

| PCA0CPH5 | 0xE2 | 0         | PCA Capture 5 High                     | page 318                                      |

| PCA0CPL0 | 0xFB | 0         | PCA Capture 0 Low                      | page 318                                      |

| PCA0CPL1 | 0xFD | 0         | PCA Capture 1 Low                      | page 318                                      |

| PCA0CPL2 | 0xE9 | 0         | PCA Capture 2 Low                      | page 318                                      |

| PCA0CPL3 | 0xEB | 0         | PCA Capture 3 Low                      | page 318                                      |

| PCA0CPL4 | 0xED | 0         | PCA Capture 4 Low                      | page 318                                      |

| PCA0CPL5 | 0xE1 | 0         | PCA Capture 5 Low                      | page 318                                      |

| PCA0CPM0 | 0xDA | 0         | PCA Module 0 Mode Register             | page 316                                      |

| PCA0CPM1 | 0xDB | 0         | PCA Module 1 Mode Register             | page 316                                      |

| PCA0CPM2 | 0xDC | 0         | PCA Module 2 Mode Register             | page 316                                      |

| PCA0CPM3 | 0xDD | 0         | PCA Module 3 Mode Register             | page 316                                      |

| PCA0CPM4 | 0xDE | 0         | PCA Module 4 Mode Register             | page 316                                      |

| PCA0CPM5 | 0xDF | 0         | PCA Module 5 Mode Register             | page 316                                      |

| PCA0H    | 0xFA | 0         | PCA Counter High                       | page 317                                      |

| PCA0L    | 0xF9 | 0         | PCA Counter Low                        | page 317                                      |

| PCA0MD   | 0xD9 | 0         | PCA Mode                               | page 315                                      |

| PCON     | 0x87 | All Pages | Power Control                          | page 164                                      |

| PSCTL    | 0x8F | 0         | Program Store R/W Control              | page 185                                      |

| PSW      | 0xD0 | All Pages | Program Status Word                    | page 151                                      |

| RCAP2H   | 0xCB | 0         | Timer/Counter 2 Capture/Reload High    | page 303                                      |

| RCAP2L   | 0xCA | 0         | Timer/Counter 2 Capture/Reload Low     | page 303                                      |

| RCAP3H   | 0xCB | 1         | Timer/Counter 3 Capture/Reload High    | page 303                                      |

| RCAP3L   | 0xCA | 1         | Timer/Counter 3 Capture/Reload Low     | page 303                                      |

| RCAP4H   | 0xCB | 2         | Timer/Counter 4 Capture/Reload High    | page 303                                      |

| RCAP4L   | 0xCA | 2         | Timer/Counter 4 Capture/Reload Low     | page 303                                      |

| REF0CN   | 0xD1 | 0         | Programmable Voltage Reference Control | page 114 <sup>4</sup> , page 118 <sup>5</sup> |

| RSTSRC   | 0xEF | 0         | Reset Source Register                  | page 170                                      |

| SADDR0   | 0xA9 | 0         | UART 0 Slave Address                   | page 276                                      |

| SADEN0   | 0xB9 | 0         | UART 0 Slave Address Enable            | page 276                                      |

| SBUF0    | 0x99 | 0         | UART 0 Data Buffer                     | page 276                                      |

| SBUF1    | 0x99 | 1         | UART 1 Data Buffer                     | page 283                                      |

| SCON0    | 0x98 | 0         | UART 0 Control                         | page 274                                      |

| SCON1    | 0x98 | 1         | UART 1 Control                         | page 282                                      |

| SFRPAGE  | 0x84 | All Pages | SFR Page Register                      | page 142                                      |

| SFRPGCN  | 0x96 | F         | SFR Page Control Register              | page 142                                      |

| SFRNEXT  | 0x85 | All Pages | SFR Next Page Stack Access Register    | page 143                                      |

| SFRLAST  | 0x86 | All Pages | SFR Last Page Stack Access Register    | page 143                                      |

| SMB0ADR  | 0xC3 | 0         | SMBus Slave Address                    | page 250                                      |

| SMB0CN   | 0xC0 | 0         | SMBus Control                          | page 247                                      |

| SMB0CR   | 0xCF | 0         | SMBus Clock Rate                       | page 248                                      |

| SMB0DAT  | 0xC2 | 0         | SMBus Data                             | page 249                                      |

| SMB0STA  | 0xC1 | 0         | SMBus Status                           | page 251                                      |

| SP       | 0x81 | All Pages | Stack Pointer                          | page 150                                      |

148

| R/W   | R/W                                                                                         | R/W                                              | R/W           | R/W           | R/W            | R/W         | R/W         | Reset Value  |  |  |  |

|-------|---------------------------------------------------------------------------------------------|--------------------------------------------------|---------------|---------------|----------------|-------------|-------------|--------------|--|--|--|

| -     | PCP2                                                                                        | PCP1                                             | PCP0          | PPCA0         | PWADC0         | PSMB0       | PSPI0       | 00000000     |  |  |  |

| Bit7  | Bit6                                                                                        | Bit5                                             | Bit4          | Bit3          | Bit2           | Bit1        | Bit0        |              |  |  |  |

|       |                                                                                             |                                                  |               |               |                |             | SFR Address |              |  |  |  |

|       |                                                                                             |                                                  |               |               |                |             | SFR Page    | e: All Pages |  |  |  |

| Bit7: | Reserved.                                                                                   |                                                  |               |               |                |             |             |              |  |  |  |

| Bit6: | PCP2: Com                                                                                   | oarator2 (C                                      | P2) Interrur  | ot Priority C | Control        |             |             |              |  |  |  |

|       | This bit sets                                                                               |                                                  |               |               |                |             |             |              |  |  |  |

|       | 0: CP2 inter                                                                                |                                                  |               | •             |                |             |             |              |  |  |  |

|       | 1: CP2 inter                                                                                | •                                                |               |               |                |             |             |              |  |  |  |

| Bit5: | PCP1: Com                                                                                   | parator1 (C                                      | P1) Interrup  | ot Priority C | ontrol.        |             |             |              |  |  |  |

|       | This bit sets                                                                               |                                                  |               |               |                |             |             |              |  |  |  |

|       | 0: CP1 inter                                                                                |                                                  |               |               |                |             |             |              |  |  |  |

|       | 1: CP1 inter                                                                                | •                                                | • • •         |               |                |             |             |              |  |  |  |

| Bit4: | PCP0: Com                                                                                   |                                                  |               |               | control.       |             |             |              |  |  |  |

|       |                                                                                             | This bit sets the priority of the CP0 interrupt. |               |               |                |             |             |              |  |  |  |

|       | 0: CP0 interrupt set to low priority level.<br>1: CP0 interrupt set to high priority level. |                                                  |               |               |                |             |             |              |  |  |  |

|       |                                                                                             | •                                                | • • •         |               |                |             | 1           |              |  |  |  |

| Bit3: |                                                                                             | •                                                |               |               | ) Interrupt Pr | iority Cont | rol.        |              |  |  |  |

|       | This bit sets<br>0: PCA0 inte                                                               |                                                  |               | •             |                |             |             |              |  |  |  |

|       | 1: PCA0 inte                                                                                | •                                                |               |               |                |             |             |              |  |  |  |

| Bit2: |                                                                                             | •                                                | • •           |               | ot Priority Co | ntrol       |             |              |  |  |  |

| DILZ. | This bit sets                                                                               |                                                  |               |               |                | muor.       |             |              |  |  |  |

|       | 0: ADC0 Wir                                                                                 |                                                  |               |               |                |             |             |              |  |  |  |

|       | 1: ADC0 Wir                                                                                 |                                                  |               |               |                |             |             |              |  |  |  |

| Bit1: |                                                                                             |                                                  | Interrupt Pri | ority Contr   | ol.            |             |             |              |  |  |  |

|       | This bit sets                                                                               | •                                                |               | ```           |                | ,           |             |              |  |  |  |

|       | 0: SMBus in                                                                                 | terrupt set I                                    | to low priori | ty level.     |                |             |             |              |  |  |  |

|       | 1: SMBus in                                                                                 | terrupt set f                                    | to high prior | rity level.   |                |             |             |              |  |  |  |

| Bit0: | PSPI0: Seria                                                                                | al Periphera                                     | al Interface  | (SPI0) Inter  | rrupt Priority | Control.    |             |              |  |  |  |

|       | This bit sets                                                                               |                                                  |               | •             |                |             |             |              |  |  |  |

|       | 0: SPI0 inter                                                                               | •                                                |               |               |                |             |             |              |  |  |  |

|       | 1: SPI0 inter                                                                               | rupt set to                                      | high priority | level.        |                |             |             |              |  |  |  |

|       |                                                                                             |                                                  |               |               |                |             |             |              |  |  |  |

|       |                                                                                             |                                                  |               |               |                |             |             |              |  |  |  |

|       |                                                                                             |                                                  |               |               |                |             |             |              |  |  |  |

# SFR Definition 12.15. EIP1: Extended Interrupt Priority 1

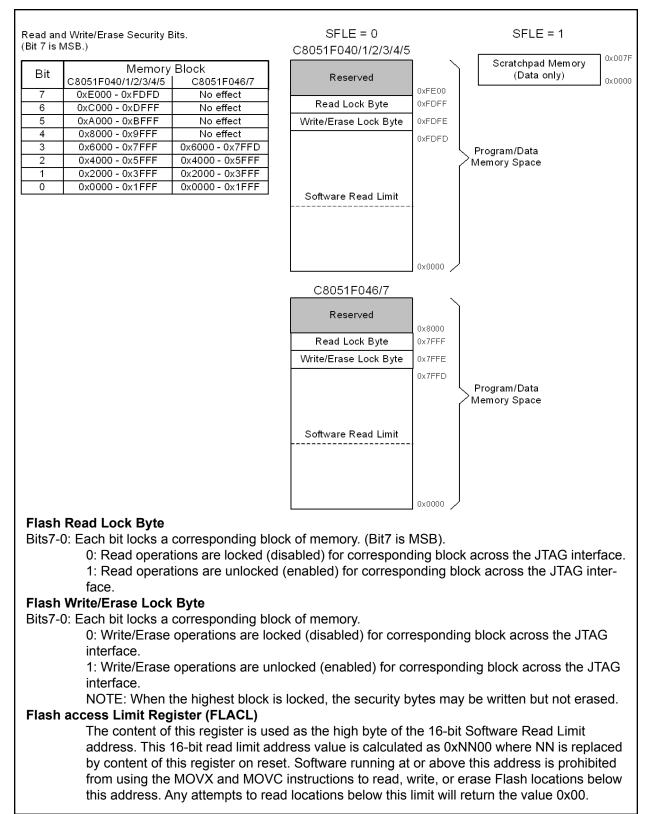

# Figure 15.1. Flash Program Memory Map and Security Bytes

#### 16.5.3. Split Mode with Bank Select

When EMI0CF.[3:2] are set to '10', the XRAM memory map is split into two areas, on-chip space and offchip space.

- Effective addresses below the 4k boundary will access on-chip XRAM space.

- Effective addresses above the 4k boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is onchip or off-chip. The upper 8-bits of the Address Bus A[15:8] are determined by EMI0CN, and the lower 8-bits of the Address Bus A[7:0] are determined by R0 or R1. All 16-bits of the Address Bus A[15:0] are driven in "Bank Select" mode.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is onchip or off-chip, and the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

#### 16.5.4. External Only

When EMI0CF[3:2] are set to '11', all MOVX operations are directed to off-chip space. On-chip XRAM is not visible to the CPU. This mode is useful for accessing off-chip memory located between 0x0000 and the 4k boundary.

- 8-bit MOVX operations ignore the contents of EMI0CN. The upper Address bits A[15:8] are not driven (identical behavior to an off-chip access in "Split Mode without Bank Select" described above). This allows the user to manipulate the upper address bits at will by setting the Port state directly. The lower 8-bits of the effective address A[7:0] are determined by the contents of R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine the effective address A[15:0]. The full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

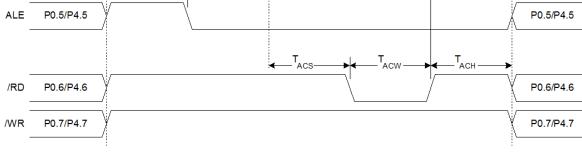

#### 16.6. Timing

The timing parameters of the External Memory Interface can be configured to enable connection to devices having different setup and hold time requirements. The Address Setup time, Address Hold time, / RD and

/WR strobe widths, and in multiplexed mode, the width of the ALE pulse are all programmable in units of SYSCLK periods through EMI0TC, shown in SFR Definition 16.3, and EMI0CF[1:0].

The timing for an off-chip MOVX instruction can be calculated by adding 4 SYSCLK cycles to the timing parameters defined by the EMI0TC register. Assuming non-multiplexed operation, the minimum execution time for an off-chip XRAM operation is 5 SYSCLK cycles (1 SYSCLK for /RD or /WR pulse + 4 SYSCLKs). For multiplexed operations, the Address Latch Enable signal will require a minimum of 2 additional SYSCLK cycles. Therefore, the minimum execution time of an off-chip XRAM operation in multiplexed mode is 7 SYSCLK cycles (2 SYSCLKs for /ALE, 1 for /RD or /WR + 4 SYSCLKs). The programmable setup and hold times default to the maximum delay settings after a reset.

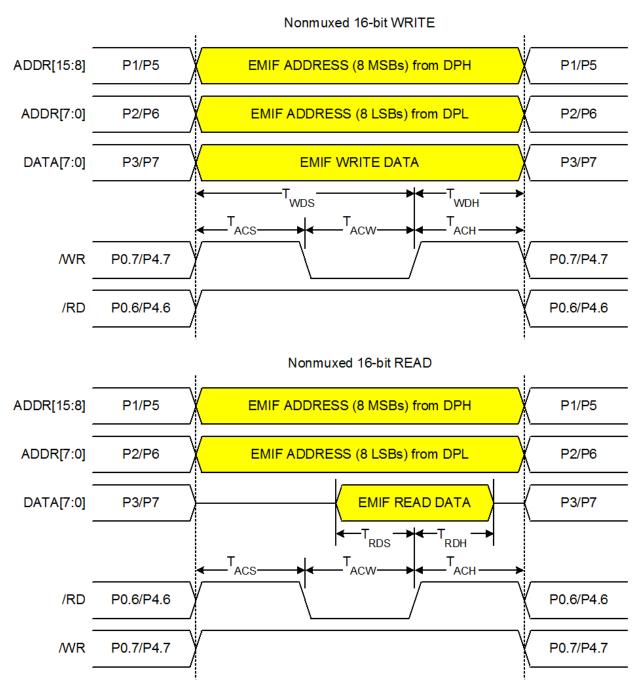

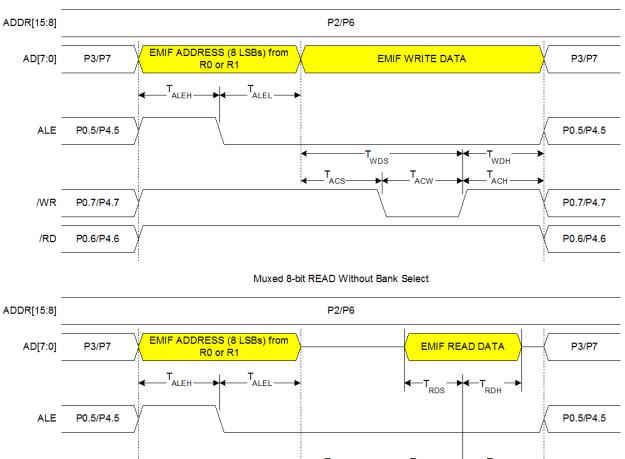

Table 16.1 lists the AC parameters for the External Memory Interface, and Figure 16.4 through Figure 16.9 show the timing diagrams for the different External Memory Interface modes and MOVX operations.

## 16.6.1. Non-multiplexed Mode

16.6.1.1.16-bit MOVX: EMI0CF[4:2] = '101', '110', or '111'.

Figure 16.4. Non-multiplexed 16-bit MOVX Timing

#### 16.6.2.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = '001' or '011'.

Muxed 8-bit WRITE Without Bank Select

# Figure 16.8. Multiplexed 8-bit MOVX without Bank Select Timing

#### 17.1.7. Crossbar Pin Assignment Example

In this example (Figure 17.6), we configure the Crossbar to allocate Port pins for UART0, the SMBus, UART1, /INT0, and /INT1 (8 pins total). Additionally, we configure the External Memory Interface to operate in Multiplexed mode and to appear on the Low ports. Further, we configure P1.2, P1.3, and P1.4 for Analog Input mode so that the voltages at these pins can be measured by ADC2. The configuration steps are as follows:

- 1. XBR0, XBR1, and XBR2 are set such that UART0EN = 1, SMB0EN = 1, INT0E = 1, INT1E = 1, and EMIFLE = 1. Thus: XBR0 = 0x05, XBR1 = 0x14, and XBR2 = 0x02.

- 2. We configure the External Memory Interface to use Multiplexed mode and to appear on the Low ports. PRTSEL = 0, EMD2 = 0.

- 3. We configure the desired Port 1 pins to Analog Input mode by setting P1MDIN to 0xE3 (P1.4, P1.3, and P1.2 are Analog Inputs, so their associated P1MDIN bits are set to logic 0).

- 4. We enable the Crossbar by setting XBARE = 1: XBR2 = 0x42.

- UART0 has the highest priority, so P0.0 is assigned to TX0, and P0.1 is assigned to RX0.

- The SMBus is next in priority order, so P0.2 is assigned to SDA, and P0.3 is assigned to SCL.

- UART1 is next in priority order, so P0.4 is assigned to TX1. Because the External Memory Interface is selected on the lower Ports, EMIFLE = 1, which causes the Crossbar to skip P0.6 (/RD) and P0.7 (/WR). Because the External Memory Interface is configured in Multiplexed mode, the Crossbar will also skip P0.5 (ALE). RX1 is assigned to the next nonskipped pin, which in this case is P1.0.

- /INT0 is next in priority order, so it is assigned to P1.1.

- P1MDIN is set to 0xE3, which configures P1.2, P1.3, and P1.4 as Analog Inputs, causing the Crossbar to skip these pins.

- /INT1 is next in priority order, so it is assigned to the next non-skipped pin, which is P1.5.

- The External Memory Interface will drive Ports 2 and 3 (denoted by red dots in Figure 17.6) during the execution of an off-chip MOVX instruction.

- 5. We set the UART0 TX pin (TX0, P0.0) and UART1 TX pin (TX1, P0.4) outputs to Push-Pull by setting P0MDOUT = 0x11.

- We configure all EMIF-controlled pins to push-pull output mode by setting P0MDOUT |= 0xE0; P2MDOUT = 0xFF; P3MDOUT = 0xFF.

- We explicitly disable the output drivers on the 3 Analog Input pins by setting P1MDOUT = 0x00 (configure outputs to Open-Drain) and P1 = 0xFF (a logic 1 selects the high-impedance state).

#### 18.2.3. Message Handler Registers

The Message Handler Registers are *read only* registers. Their flags can be read via the indexed access method with CAN0ADR, CAN0DATH, and CAN0DATL. The message handler registers provide interrupt, error, transmit/receive requests, and new data information.

Please refer to the Bosch CAN User's Guide for information on the function and use of the Message Handler Registers.

#### 18.2.4. CIP-51 MCU Special Function Registers

C8051F04x family peripherals are modified, monitored, and controlled using Special Function Registers (SFR's). Only three of the CAN Controller's registers may be accessed directly with SFR's. However, all CAN Controller registers can be accessed indirectly using three CIP-51 MCU SFR's: the CAN Data Registers (CAN0DATH and CAN0DATL) and CAN Address Register (CAN0ADR).

#### 18.2.5. Using CAN0ADR, CAN0DATH, and CANDATL to Access CAN Registers

Each CAN Controller Register has an index number (see Table 18.2). The CAN register address space is 128 words (256 bytes). A CAN register is accessed via the CAN Data Registers (CAN0DATH and CAN0-DATL) when a CAN register's index number is placed into the CAN Address Register (CAN0ADR). For example, if the Bit Timing Register is to be configured with a new value, CAN0ADR is loaded with 0x03. The low byte of the desired value is accessed using CAN0DATL and the high byte of the bit timing register is accessed using CAN0DATL is bit addressable for convenience. To load the value 0x2304 into the Bit Timing Register:

CANOADR = 0x03; // Load Bit Timing Register's index (Table 18.1) CANODATH = 0x23; // Move the upper byte into data reg high byte CANODATL = 0x04; // Move the lower byte into data reg low byte

<u>Note:</u> CAN0CN, CAN0STA, and CAN0TST may be accessed either by using the index method, or by direct access with the CIP-51 MCU SFR's. CAN0CN is located at SFR location 0xF8/SFR page 1 (SFR Definition 18.3), CAN0TST at 0xDB/SFR page 1 (SFR Definition 18.4), and CAN0STA at 0xC0/SFR page 1 (SFR Definition 18.5).

#### 18.2.6. CAN0ADR Autoincrement Feature

For ease of programming message objects, CAN0ADR features autoincrementing for the index ranges 0x08 to 0x12 (Interface Registers 1) and 0x20 to 0x2A (Interface Registers 2). When the CAN0ADR register has an index in these ranges, the CAN0ADR will autoincrement by 1 to point to the next CAN register 16-bit word upon a read/write of <u>CAN0DATL</u>. This speeds programming of the frequently-accessed interface registers when configuring message objects.

<u>NOTE:</u> Table 18.2 below supersedes Figure 5 in Section 3, "Programmer's Model" of the Bosch CAN User's Guide.

| CAN Register<br>Index | Register Name          | Reset<br>Value | Notes                                                                             |

|-----------------------|------------------------|----------------|-----------------------------------------------------------------------------------|

| 0x00                  | CAN Control Register   | 0x0001         | Accessible in CIP-51 SFR Map                                                      |

| 0x01                  | Status Register        | 0x0000         | Accessible in CIP-51 SFR Map                                                      |

| 0x02                  | Error Register         | 0x0000         | Read Only                                                                         |

| 0x03                  | Bit Timing Register    | 0x2301         | Write Enabled by CCE Bit in CAN0CN                                                |

| 0x04                  | Interrupt Register     | 0x0000         | Read Only                                                                         |

| 0x05                  | Test Register          | 0x0000         | Bit 7 (RX) is determined by CAN bus                                               |

| 0x06                  | BRP Extension Register | 0x0000         | Write Enabled by TEST bit in CAN0CN                                               |

| 0x08                  | IF1 Command Request    | 0x0001         | CAN0ADR autoincrements in IF1 index space<br>(0x08 - 0x12) upon write to CAN0DATL |

| 0x09                  | IF1 Command Mask       | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0A                  | IF1 Mask 1             | 0xFFFF         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0B                  | IF1 Mask 2             | 0xFFFF         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0C                  | IF1 Arbitration 1      | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0D                  | IF1 Arbitration 2      | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0E                  | IF1 Message Control    | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x0F                  | IF1 Data A1            | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x10                  | IF1 Data A2            | 0x0000         | CAN0ADR autoincrement upon write to<br>CAN0DATL                                   |

| 0x11                  | IF1 Data B1            | 0x0000         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x12                  | IF1 Data B2            | 0x0000         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x20                  | IF2 Command Request    | 0x0001         | CAN0ADR autoincrements in IF2 index space<br>(0x20 - 0x2A) upon write to CAN0DATL |

| 0x21                  | IF2 Command Mask       | 0x0000         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x22                  | IF2 Mask 1             | 0xFFFF         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x23                  | IF2 Mask 2             | 0xFFFF         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x24                  | IF2 Arbitration 1      | 0x0000         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

| 0x25                  | IF2 Arbitration 2      | 0x0000         | CAN0ADR autoincrement upon write to CAN0DATL                                      |

Table 18.2. CAN Register Index and Reset Values

| SFR Definition 19.1 | . SMB0CN: SMBus0 Control |

|---------------------|--------------------------|

|---------------------|--------------------------|

| R     | R/W                                                                                                         | R/W                                                                   | R/W                                                        | R/W                                      | R/W                                        | R/W                          | R/W                           | Reset Value  |

|-------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------|--------------------------------------------|------------------------------|-------------------------------|--------------|

| BUSY  | ENSMB                                                                                                       | STA                                                                   | STO                                                        | SI                                       | AA                                         | FTE                          | TOE                           | 00000000     |

| Bit7  | Bit6                                                                                                        | Bit5                                                                  | Bit4                                                       | Bit3                                     | Bit2                                       | Bit1                         | Bit0<br>SFR Addres<br>SFR Pag |              |

| Bit7: | BUSY: Busy<br>0: SMBus0 is<br>1: SMBus0 is                                                                  | s free                                                                | g.                                                         |                                          |                                            |                              |                               |              |

| Bit6: | ENSMB: SM<br>This bit enab<br>0: SMBus0 d                                                                   | Bus Énable<br>les/disable<br>isabled.                                 |                                                            | is serial inte                           | erface.                                    |                              |                               |              |

| Bit5: | 1: SMBus0 e<br>STA: SMBus<br>0: No START<br>1: When ope<br>bus is not fre<br>more bytes h                   | Start Flag.<br>condition<br>rating as a<br>e, the STA<br>ave been t   | is transmitte<br>master, a S<br>RT is transr<br>ransmitted | START cond<br>nitted after               | a STOP is ı                                | received.) If                | STA is set                    | after one or |

| Bit4: | START cond<br>STO: SMBus<br>0: No STOP<br>1: Setting ST<br>tion is receive<br>dition is trans<br>causes SMB | Stop Flag<br>condition is<br>O to logic<br>ed, hardwa<br>mitted follo | s transmitte<br>1 causes a<br>ire clears S<br>owed by a S  | STOP conc<br>TO to logic<br>START conc   | 0. If both S<br>dition. In sla             | TA and ST<br>ave mode, s     | O are set, a                  | a STOP con-  |

| Bit3: | SI: SMBus S<br>This bit is set<br>0xF8 does no<br>the CPU to v<br>cleared by ha                             | erial Interru<br>by hardwa<br>ot cause Sl<br>ector to the             | upt Flag.<br>are when on<br>I to be set.)<br>e SMBus inf   | e of 27 pos<br>When the S<br>errupt serv | sible SMBu<br>SI interrupt<br>ice routine. | us0 states is<br>is enabled, | setting this                  | bit causes   |

| Bit2: | AA: SMBus A<br>This bit defin-<br>line.<br>0: A "not ack                                                    | Assert Ackr<br>es the type<br>nowledge"                               | owledge Fl<br>of acknowl<br>(high level                    | ag.<br>edge returr<br>on SDA) is         | ied during t<br>returned du                | uring the ac                 | knowledge                     | cycle.       |

| Bit1: | 1: An "acknow<br>FTE: SMBus<br>0: No timeour<br>1: Timeout w                                                | Free Time<br>t when SC                                                | r Enable Bi<br>L is high                                   | t                                        |                                            | -                            |                               | cie.         |

| Bit0: | TOE: SMBus<br>0: No timeou<br>1: Timeout w                                                                  | Timeout E<br>t when SC                                                | inable Bit<br>L is low.                                    |                                          |                                            |                              |                               |              |

## 20.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 20.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and does not get mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 20.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 20.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

## 20.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will wait until the byte is transferred before loading it with the transmit buffer's contents.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 20.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and does not get mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 20.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

#### 20.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

Note: All of the following interrupt bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- 2. The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- 3. The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

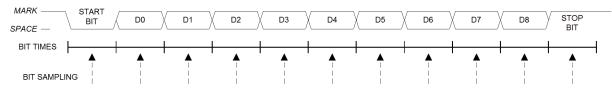

#### 22.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB81 (SCON1.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB81 (SCON1.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF1 register. The TI1 Transmit Interrupt Flag (SCON1.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN1 Receive Enable bit (SCON1.4) is set to '1'. After the stop bit is received, the data byte will be loaded into the SBUF1 receive register if the following conditions are met: (1) RI1 must be logic 0, and (2) if MCE1 is logic 1, the 9th bit must be logic 1 (when MCE1 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF1, the ninth bit is stored in RB81, and the RI1 flag is set to '1'. A UART1 interrupt will occur if enabled when either TI1 or RI1 is set to '1'.

Figure 22.5. 9-Bit UART Timing Diagram

# SFR Definition 23.8. TMRnCN: Timer n Control

| R/W            | R/W                                                                                                                                                 | R/W         | R/W         | R/W            | R/W         | R/W         | R/W         | _ Reset Valu      |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|----------------|-------------|-------------|-------------|-------------------|

| TFn            | EXFn                                                                                                                                                | -           | -           | EXENn          | TRn         | C/Tn        | CP/RLn      | 0000000           |

| Bit7           | Bit6                                                                                                                                                | Bit5        | Bit4        | Bit3           | Bit2        | Bit1        | Bit0        | Bit<br>Addressabl |

| SFR Addre      | ess: TMR2CN:0xC                                                                                                                                     | 8:TMR3CN:0  | xC8:TMR4CN  | 1:0xC8         |             |             |             | Addressabi        |

|                | ige: TMR2CN: pag                                                                                                                                    |             |             |                |             |             |             |                   |

|                |                                                                                                                                                     |             |             |                |             |             |             |                   |

| Bit7:          | TFn: Timer n                                                                                                                                        | Overflow/U  | Inderflow F | lag.           |             |             |             |                   |

|                | Set by hardware when either the Timer overflows from 0xFFFF to 0x0000, underflows from                                                              |             |             |                |             |             |             |                   |

|                | the value placed in RCAPnH:RCAPnL to 0xFFFF (in Auto-reload Mode), or underflows from                                                               |             |             |                |             |             |             |                   |

|                | 0x0000 to 0xFFFF (in Capture Mode). When the Timer interrupt is enabled, setting this bit                                                           |             |             |                |             |             |             |                   |

|                | causes the CPU to vector to the Timer interrupt service routine. This bit is not automatically                                                      |             |             |                |             |             |             |                   |

|                | cleared by ha                                                                                                                                       |             |             | •              | oftware.    |             |             |                   |

| Bit6:          | EXFn: Timer 2                                                                                                                                       |             |             | -              |             |             |             |                   |

|                | Set by hardware when either a capture or reload is caused by a high-to-low transition on the                                                        |             |             |                |             |             |             |                   |

|                | TnEX input pin and EXENn is logic 1. When the Timer interrupt is enabled, setting this bit                                                          |             |             |                |             |             |             |                   |

|                | causes the CPU to vector to the Timer Interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software. |             |             |                |             |             |             |                   |

|                | •                                                                                                                                                   | roware and  | a must be o | cleared by so  | mware.      |             |             |                   |

| Bit5-4:        | Reserved.                                                                                                                                           | r n Evtorna | l Enchlo    |                |             |             |             |                   |

| Bit3:          | EXENn: Timer n External Enable.<br>Enables high-to-low transitions on TnEX to trigger captures, reloads, and control the direc-                     |             |             |                |             |             |             |                   |

|                | tion of the timer/counter (up or down count). If DECEN = 1, TnEX will determine if the time                                                         |             |             |                |             |             |             |                   |

|                | counts up or down when in Auto-reload Mode. If EXENn = 1, ThEX will determine in the time                                                           |             |             |                |             |             |             |                   |

|                | a digital input.                                                                                                                                    |             |             |                |             |             |             |                   |

|                | 0: Transitions on the TnEX pin are ignored.                                                                                                         |             |             |                |             |             |             |                   |

|                | 1: Transitions on the TnEX pin cause capture, reload, or control the direction of timer coun                                                        |             |             |                |             |             |             |                   |

|                | (up or down) as follows:                                                                                                                            |             |             |                |             |             |             |                   |

|                | Capture Mode: '1'-to-'0' Transition on TnEX pin causes RCAPnH:RCAPnL to capture time                                                                |             |             |                |             |             |             |                   |

|                | value.                                                                                                                                              |             |             |                |             |             |             |                   |

|                | Auto-Reload I                                                                                                                                       | Mode:       |             |                |             |             |             |                   |

|                | DCEN = 0: '1'-to-'0' transition causes reload of timer and sets the EXFn Flag.                                                                      |             |             |                |             |             |             |                   |

|                | DCEN = 1: TnEX logic level controls direction of timer (up or down).                                                                                |             |             |                |             |             |             |                   |

| Bit2:<br>Bit1: | TRn: Timer n                                                                                                                                        |             | -           |                |             |             |             |                   |

|                | This bit enables/disables the respective Timer.                                                                                                     |             |             |                |             |             |             |                   |

|                | 0: Timer disat                                                                                                                                      |             | . ,         |                |             |             |             |                   |

|                | 1: Timer enab                                                                                                                                       |             |             | iting.         |             |             |             |                   |

|                | C/Tn: Counter                                                                                                                                       |             |             | ad by alask    | defined by  | TnN11.TnN1  | 0           |                   |

|                | 0: Timer Func<br>(TMRnCF.4:T                                                                                                                        |             |             |                | Jenned by   |             | 0           |                   |

|                | 1: Counter Fu                                                                                                                                       |             |             | onted by high  | to low tra  | neitione on | ovtornal in | out nin           |

| BitO:          | CP/RLn: Capt                                                                                                                                        |             |             | ented by high  |             |             | external in | Jut pin.          |

|                | This bit select                                                                                                                                     |             |             | functions in a | antura ar a | uto-reload  | mode        |                   |

|                |                                                                                                                                                     |             |             | UNCHORS IN C   | adiure or a |             |             |                   |

|                | 0: Timer is in /                                                                                                                                    |             |             |                | apture or a |             |             |                   |