Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | SPI, UART/USART, USI                                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                       |

| Program Memory Size        | 64KB (32K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 2K x 8                                                                   |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega645-16mi |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

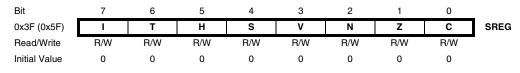

# 7.4 Status Register

The Status Register contains information about the result of the most recently executed arithmetic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the Status Register is updated after all ALU operations, as specified in the Instruction Set Reference. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code.

The Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt. This must be handled by software.

# 7.4.1 SREG – AVR Status Register

The AVR Status Register - SREG - is defined as:

# • Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the Global Interrupt Enable Register is cleared, none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared by the application with the SEI and CLI instructions, as described in the instruction set reference.

# • Bit 6 – T: Bit Copy Storage

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or destination for the operated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the BLD instruction.

# • Bit 5 – H: Half Carry Flag

The Half Carry Flag H indicates a Half Carry in some arithmetic operations. Half Carry Is useful in BCD arithmetic. See the "Instruction Set Description" for detailed information.

# • Bit 4 – S: Sign Bit, S = N $\oplus$ V

The S-bit is always an exclusive or between the Negative Flag N and the Two's Complement Overflow Flag V. See the "Instruction Set Description" for detailed information.

# • Bit 3 – V: Two's Complement Overflow Flag

The Two's Complement Overflow Flag V supports two's complement arithmetics. See the "Instruction Set Description" for detailed information.

# • Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

# • Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the "Instruction Set Description" for detailed information.

Applying an external clock source to TOSC1 can be done if EXTCLK in the ASSR Register is written to logic one. See "Asynchronous Operation of Timer/Counter2" on page 141 for further description on selecting external clock as input instead of a 32kHz crystal.

# 9.9 System Clock Prescaler

The Atmel ATmega325/3250/645/6450 system clock can be divided by setting the "CLKPR – Clock Prescale Register" on page 33. This feature can be used to decrease power consumption when the requirement for processing power is low. This can be used with all clock source options, and it will affect the clock frequency of the CPU and all synchronous peripherals. clk<sub>I/O</sub>, clk<sub>ADC</sub>, clk<sub>CPU</sub>, and clk<sub>FLASH</sub> are divided by a factor as shown in Table 9-11 on page 33.

# 9.9.1 Switching Time

When switching between prescaler settings, the System Clock Prescaler ensures that no glitches occur in the clock system and that no intermediate frequency is higher than neither the clock frequency corresponding to the previous setting, nor the clock frequency corresponding to the new setting.

The ripple counter that implements the prescaler runs at the frequency of the undivided clock, which may be faster than the CPU's clock frequency. Hence, it is not possible to determine the state of the prescaler – even if it were readable, and the exact time it takes to switch from one clock division to another cannot be exactly predicted.

From the time the CLKPS values are written, it takes between T1 + T2 and T1 +  $2^{T2}$  before the new clock frequency is active. In this interval, 2 active clock edges are produced. Here, T1 is the previous clock period, and T2 is the period corresponding to the new prescaler setting.

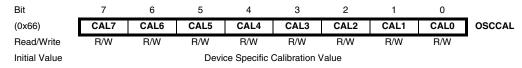

# 9.10 Register Description

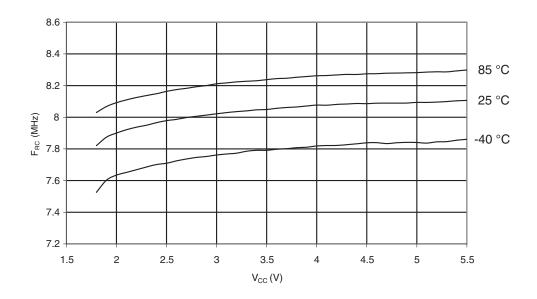

# 9.10.1 OSCCAL – Oscillator Calibration Register

# Bits 7:0 – CAL7:0: Oscillator Calibration Value

The Oscillator Calibration Register is used to trim the Calibrated Internal RC Oscillator to remove process variations from the oscillator frequency. A pre-programmed calibration value is automatically written to this register during chip reset, giving the Factory calibrated frequency as specified in Table 28-2 on page 300. The application software can write this register to change the oscillator frequency. The oscillator can be calibrated to frequencies as specified in Table 28-2 on page 300. Calibration outside that range is not guaranteed.

Note that this oscillator is used to time EEPROM and Flash write accesses, and these write times will be affected accordingly. If the EEPROM or Flash are written, do not calibrate to more than 8.8MHz. Otherwise, the EEPROM or Flash write may fail.

The CAL7 bit determines the range of operation for the oscillator. Setting this bit to 0 gives the lowest frequency range, setting this bit to 1 gives the highest frequency range. The two frequency ranges are overlapping, in other words a setting of OSCCAL = 0x7F gives a higher frequency than OSCCAL = 0x80.

#### • Bit 7:0 – PCINT23:16: Pin Change Enable Mask 23..16

Each PCINT23:16 bit selects whether pin change interrupt is enabled on the corresponding I/O pin. If PCINT23:16 is set and the PCIE2 bit in EIMSK is set, pin change interrupt is enabled on the corresponding I/O pin. If PCINT23:16 is cleared, pin change interrupt on the corresponding I/O pin is disabled.

Note: 1. PCMSK3 and PCMSK2 are only present in ATmega3250/6450.

# 13.2.6 PCMSK1 – Pin Change Mask Register 1

| Bit           | 7       | 6       | 5       | 4       | 3       | 2       | 1      | 0      | _      |

|---------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|

| (0x6C)        | PCINT15 | PCINT14 | PCINT13 | PCINT12 | PCINT11 | PCINT10 | PCINT9 | PCINT8 | PCMSK1 |

| Read/Write    | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     | R/W    | R/W    | •      |

| Initial Value | 0       | 0       | 0       | 0       | 0       | 0       | 0      | 0      |        |

### • Bit 7:0 – PCINT15:8: Pin Change Enable Mask 15..8

Each PCINT15:8-bit selects whether pin change interrupt is enabled on the corresponding I/O pin. If PCINT15:8 is set and the PCIE1 bit in EIMSK is set, pin change interrupt is enabled on the corresponding I/O pin. If PCINT15:8 is cleared, pin change interrupt on the corresponding I/O pin is disabled.

#### 13.2.7 PCMSK0 – Pin Change Mask Register 0

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| (0x6B)        | PCINT7 | PCINT6 | PCINT5 | PCINT4 | PCINT3 | PCINT2 | PCINT1 | PCINT0 | PCMSK0 |

| Read/Write    | R/W    | •      |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |        |

#### • Bit 7:0 – PCINT7:0: Pin Change Enable Mask 7..0

Each PCINT7:0 bit selects whether pin change interrupt is enabled on the corresponding I/O pin. If PCINT7:0 is set and the PCIE0 bit in EIMSK is set, pin change interrupt is enabled on the corresponding I/O pin. If PCINT7:0 is cleared, pin change interrupt on the corresponding I/O pin is disabled.

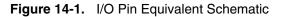

# 14. I/O-Ports

# 14.1 Overview

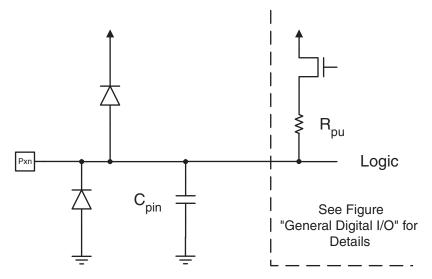

All AVR ports have true Read-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintentionally changing the direction of any other pin with the SBI and CBI instructions. The same applies when changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input). Each output buffer has symmetrical drive characteristics with both high sink and source capability. Port B has a higher pin driver strength than the other ports, but all the pin drivers are strong enough to drive LED displays directly. All port pins have individually selectable pull-up resistors with a supply-voltage invariant resistance. All I/O pins have protection diodes to both  $V_{CC}$  and Ground as indicated in Figure 14-1. Refer to "Electrical Characteristics" on page 297 for a complete list of parameters. If exceeding the pin voltage "Absolute Maximum Ratings", resulting currents can harm the device if not limited accordingly. For segment pins used as general I/O, the same situation can also influence the LCD voltage level.

All registers and bit references in this section are written in general form. A lower case "x" represents the numbering letter for the port, and a lower case "n" represents the bit number. However, when using the register or bit defines in a program, the precise form must be used. For example, PORTB3 for bit no. 3 in Port B, here documented generally as PORTxn. The physical I/O Registers and bit locations are listed in "Register Description" on page 81.

Three I/O memory address locations are allocated for each port, one each for the Data Register – PORTx, Data Direction Register – DDRx, and the Port Input Pins – PINx. The Port Input Pins I/O location is read only, while the Data Register and the Data Direction Register are read/write. However, writing a logic one to a bit in the PINx Register, will result in a toggle in the corresponding bit in the Data Register. In addition, the Pull-up Disable – PUD bit in MCUCR disables the pull-up function for all pins in all ports when set.

Using the I/O port as General Digital I/O is described in "Ports as General Digital I/O" on page 61. Most port pins are multiplexed with alternate functions for the peripheral features on the device. How each alternate function interferes with the port pin is described in "Alternate Port

The OCR0A Register is double buffered when using any of the Pulse Width Modulation (PWM) modes. For the normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR0 Compare Register to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

The OCR0A Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR0A Buffer Register, and if double buffering is disabled the CPU will access the OCR0A directly.

# 15.5.1 Force Output Compare

In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC0A) bit. Forcing compare match will not set the OCF0A Flag or reload/clear the timer, but the OC0A pin will be updated as if a real compare match had occurred (the COM0A1:0 bits settings define whether the OC0A pin is set, cleared or toggled).

# 15.5.2 Compare Match Blocking by TCNT0 Write

All CPU write operations to the TCNT0 Register will block any compare match that occur in the next timer clock cycle, even when the timer is stopped. This feature allows OCR0A to be initialized to the same value as TCNT0 without triggering an interrupt when the Timer/Counter clock is enabled.

# 15.5.3 Using the Output Compare Unit

Since writing TCNT0 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT0 when using the Output Compare unit, independently of whether the Timer/Counter is running or not. If the value written to TCNT0 equals the OCR0A value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT0 value equal to BOTTOM when the counter is counting down.

The setup of the OC0A should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC0A value is to use the Force Output Compare (FOC0A) strobe bits in Normal mode. The OC0A Register keeps its value even when changing between Waveform Generation modes.

Be aware that the COM0A1:0 bits are not double buffered together with the compare value. Changing the COM0A1:0 bits will take effect immediately.

# 15.6 Compare Match Output Unit

The Compare Output mode (COM0A1:0) bits have two functions. The Waveform Generator uses the COM0A1:0 bits for defining the Output Compare (OC0A) state at the next compare match. Also, the COM0A1:0 bits control the OC0A pin output source. Figure 15-4 shows a simplified schematic of the logic affected by the COM0A1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O port control registers (DDR and PORT) that are affected by the COM0A1:0 bits are shown. When referring to the OC0A state, the reference is for the internal OC0A Register, not the OC0A pin. If a System Reset occur, the OC0A Register is reset to "0".

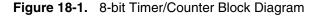

# 18. 8-bit Timer/Counter2 with PWM and Asynchronous Operation

# 18.1 Features

Timer/Counter2 is a general purpose, single compare unit, 8-bit Timer/Counter module. The main features are:

- Single Compare Unit Counter

- Clear Timer on Compare Match (Auto Reload)

- Glitch-free, Phase Correct Pulse Width Modulator (PWM)

- Frequency Generator

- 10-bit Clock Prescaler

- Overflow and Compare Match Interrupt Sources (TOV2 and OCF2A)

- Allows Clocking from External 32kHz Watch Crystal Independent of the I/O Clock

# 18.2 Overview

A simplified block diagram of the 8-bit Timer/Counter is shown in Figure 18-1. For the actual placement of I/O pins, refer to "Pinout ATmega3250/6450" on page 2. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the "Register Description" on page 143.

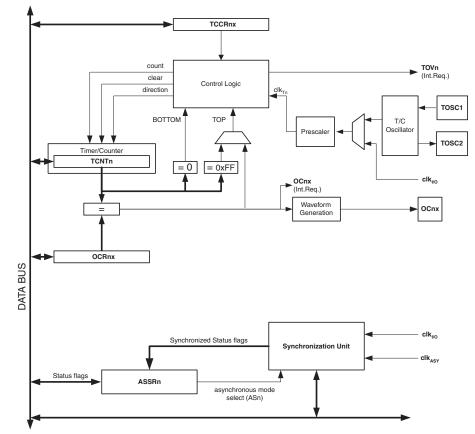

An interrupt can be generated each time the counter value reaches the TOP value by using the OCF2A Flag. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing the TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR2A is lower than the current value of TCNT2, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the compare match can occur.

For generating a waveform output in CTC mode, the OC2A output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to toggle mode (COM2A1:0 = 1). The OC2A value will not be visible on the port pin unless the data direction for the pin is set to output. The waveform generated will have a maximum frequency of  $f_{OC2A} = f_{clk\_l/O}/2$  when OCR2A is set to zero (0x00). The waveform frequency is defined by the following equation:

$$f_{OCnx} = \frac{f_{clk\_l/O}}{2 \cdot N \cdot (1 + OCRnx)}$$

The *N* variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

As for the Normal mode of operation, the TOV2 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x00.

#### 18.7.3 Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (WGM21:0 = 3) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM option by its single-slope operation. The counter counts from BOTTOM to MAX then restarts from BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC2A) is cleared on the compare match between TCNT2 and OCR2A, and set at BOTTOM. In inverting Compare Output mode, the output is set on compare match and cleared at BOTTOM. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct PWM mode that uses dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

In fast PWM mode, the counter is incremented until the counter value matches the MAX value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast

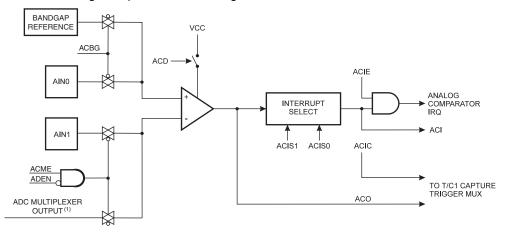

# 22. Analog Comparator

The Analog Comparator compares the input values on the positive pin AIN0 and negative pin AIN1. When the voltage on the positive pin AIN0 is higher than the voltage on the negative pin AIN1, the Analog Comparator output, ACO, is set. The comparator's output can be set to trigger the Timer/Counter1 Input Capture function. In addition, the comparator can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select Interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 22-1.

The Power Reduction ADC bit, PRADC, in "Power Reduction Register" on page 37 must be disabled by writing a logical zero to be able to use the ADC module.

Figure 22-1. Analog Comparator Block Diagram<sup>(2)</sup>

- Notes: 1. See Table 22-1 on page 198.

- 2. Refer to Figure 1-1 on page 2, Figure 1-2 on page 3, and "Alternate Functions of Port E" on page 72 for Analog Comparator pin placement.

# • Bit 7 – ACD: Analog Comparator Disable

When this bit is written logic one, the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. This will reduce power consumption in Active and Idle mode. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

# • Bit 6 – ACBG: Analog Comparator Bandgap Select

When this bit is set, a fixed bandgap reference voltage replaces the positive input to the Analog Comparator. When this bit is cleared, AINO is applied to the positive input of the Analog Comparator. When the bandgap reference is used as input to the analog comparator, it will take a certain time for the voltage to stabilize. If not stabilized, the the first converison may give a wrong value. See "Internal Voltage Reference" on page 44.

# • Bit 5 – ACO: Analog Comparator Output

The output of the Analog Comparator is synchronized and then directly connected to ACO. The synchronization introduces a delay of 1 - 2 clock cycles.

# • Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set by hardware when a comparator output event triggers the interrupt mode defined by ACIS1 and ACIS0. The Analog Comparator interrupt routine is executed if the ACIE bit is set and the I-bit in SREG is set. ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logic one to the flag.

#### • Bit 3 – ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is written logic one and the I-bit in the Status Register is set, the Analog Comparator interrupt is activated. When written logic zero, the interrupt is disabled.

# • Bit 2 – ACIC: Analog Comparator Input Capture Enable

When written logic one, this bit enables the Input Capture function in Timer/Counter1 to be triggered by the Analog Comparator. The comparator output is in this case directly connected to the Input Capture front-end logic, making the comparator utilize the noise canceler and edge select features of the Timer/Counter1 Input Capture interrupt. When written logic zero, no connection between the Analog Comparator and the Input Capture function exists. To make the comparator trigger the Timer/Counter1 Input Capture interrupt, the ICIE1 bit in the Timer Interrupt Mask Register (TIMSK1) must be set.

- Page Write to the RWW section: The NRWW section can be read during the Page Write.

- Page Write to the NRWW section: The CPU is halted during the operation.

#### 26.8.4 Using the SPM Interrupt

If the SPM interrupt is enabled, the SPM interrupt will generate a constant interrupt when the SPMEN bit in SPMCSR is cleared. This means that the interrupt can be used instead of polling the SPMCSR Register in software. When using the SPM interrupt, the Interrupt Vectors should be moved to the BLS section to avoid that an interrupt is accessing the RWW section when it is blocked for reading. How to move the interrupts is described in "Interrupts" on page 49.

#### 26.8.5 Consideration While Updating BLS

Special care must be taken if the user allows the Boot Loader section to be updated by leaving Boot Lock bit11 unprogrammed. An accidental write to the Boot Loader itself can corrupt the entire Boot Loader, and further software updates might be impossible. If it is not necessary to change the Boot Loader software itself, it is recommended to program the Boot Lock bit11 to protect the Boot Loader software from any internal software changes.

#### 26.8.6 Prevent Reading the RWW Section During Self-Programming

During Self-Programming (either Page Erase or Page Write), the RWW section is always blocked for reading. The user software itself must prevent that this section is addressed during the self programming operation. The RWWSB in the SPMCSR will be set as long as the RWW section is busy. During Self-Programming the Interrupt Vector table should be moved to the BLS as described in "Interrupts" on page 49, or the interrupts must be disabled. Before addressing the RWW section after the programming is completed, the user software must clear the RWWSB by writing the RWWSRE. See "Simple Assembly Code Example for a Boot Loader" on page 260 for an example.

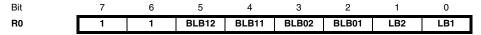

#### 26.8.7 Setting the Boot Loader Lock Bits by SPM

To set the Boot Loader Lock bits and general Lock bits, write the desired data to R0, write "X0001001" to SPMCSR and execute SPM within four clock cycles after writing SPMCSR.

See Table 26-2 and Table 26-3 for how the different settings of the Boot Loader bits affect the Flash access.

If bits 5..0 in R0 are cleared (zero), the corresponding Lock bit will be programmed if an SPM instruction is executed within four cycles after BLBSET and SPMEN are set in SPMCSR. The Z-pointer is don't care during this operation, but for future compatibility it is recommended to load the Z-pointer with 0x0001 (same as used for reading the Lock bits). For future compatibility it is also recommended to set bits 7, and 6 in R0 to "1" when writing the Lock bits. When programming the Lock bits the entire Flash can be read during the operation.

#### 26.8.8 EEPROM Write Prevents Writing to SPMCSR

Note that an EEPROM write operation will block all software programming to Flash. Reading the Fuses and Lock bits from software will also be prevented during the EEPROM write operation. It is recommended that the user checks the status bit (EEWE) in the EECR Register and verifies that the bit is cleared before writing to the SPMCSR Register.

| Fuse High Byte        | Bit No | Description                                       | Default Value                                |

|-----------------------|--------|---------------------------------------------------|----------------------------------------------|

| OCDEN <sup>(4)</sup>  | 7      | Enable OCD                                        | 1 (unprogrammed,<br>OCD disabled)            |

| JTAGEN <sup>(5)</sup> | 6      | Enable JTAG                                       | 0 (programmed, JTAG enabled)                 |

| SPIEN <sup>(1)</sup>  | 5      | Enable Serial Program and Data<br>Downloading     | 0 (programmed, SPI prog. enabled)            |

| WDTON <sup>(3)</sup>  | 4      | Watchdog Timer always on                          | 1 (unprogrammed)                             |

| EESAVE                | 3      | EEPROM memory is preserved through the Chip Erase | 1 (unprogrammed,<br>EEPROM not<br>preserved) |

| BOOTSZ1               | 2      | Select Boot Size (see Table 27-6 for details)     | 0 (programmed) <sup>(2)</sup>                |

| BOOTSZ0               | 1      | Select Boot Size (see Table 27-6 for details)     | 0 (programmed) <sup>(2)</sup>                |

| BOOTRST               | 0      | Select Reset Vector                               | 1 (unprogrammed)                             |

Table 27-4.Fuse High Byte

Note: 1. The SPIEN Fuse is not accessible in serial programming mode.

- 2. The default value of BOOTSZ1..0 results in maximum Boot Size. See Table 26-6 on page 262 for details.

- 3. See "Register Description" on page 47 for details.

- 4. Never ship a product with the OCDEN Fuse programmed regardless of the setting of Lock bits and JTAGEN Fuse. A programmed OCDEN Fuse enables some parts of the clock system to be running in all sleep modes. This may increase the power consumption.

- 5. If the JTAG interface is left unconnected, the JTAGEN fuse should if possible be disabled. This to avoid static current at the TDO pin in the JTAG interface.

#### Table 27-5.Fuse Low Byte

| Fuse Low Byte         | Bit No | Description          | Default Value                   |

|-----------------------|--------|----------------------|---------------------------------|

| CKDIV8 <sup>(4)</sup> | 7      | Divide clock by 8    | 0 (programmed)                  |

| CKOUT <sup>(3)</sup>  | 6      | Clock output         | 1 (unprogrammed)                |

| SUT1                  | 5      | Select start-up time | 1 (unprogrammed) <sup>(1)</sup> |

| SUT0                  | 4      | Select start-up time | 0 (programmed) <sup>(1)</sup>   |

| CKSEL3                | 3      | Select Clock source  | 0 (programmed) <sup>(2)</sup>   |

| CKSEL2                | 2      | Select Clock source  | 0 (programmed) <sup>(2)</sup>   |

| CKSEL1                | 1      | Select Clock source  | 1 (unprogrammed) <sup>(2)</sup> |

| CKSEL0                | 0      | Select Clock source  | 0 (programmed) <sup>(2)</sup>   |

Note: 1. The default value of SUT1..0 results in maximum start-up time for the default clock source. See Table 28-4 on page 301 for details.

- The default setting of CKSEL3..0 results in internal RC Oscillator @ 8 MHz. See Table 9-5 on page 29 for details.

- 3. The CKOUT Fuse allow the system clock to be output on PORTE7. See "Clock Output Buffer" on page 31 for details.

- 4. See "System Clock Prescaler" on page 32 for details.

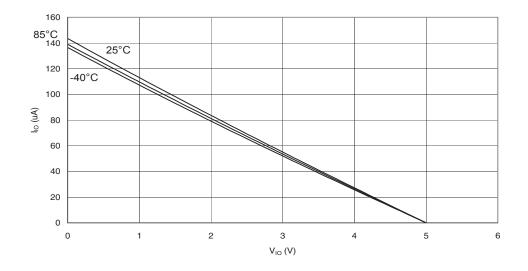

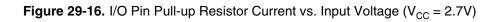

# 29.7 Pin Pull-up

Figure 29-15. I/O Pin Pull-up Resistor Current vs. Input Voltage (V<sub>CC</sub> = 5V)

~ ~

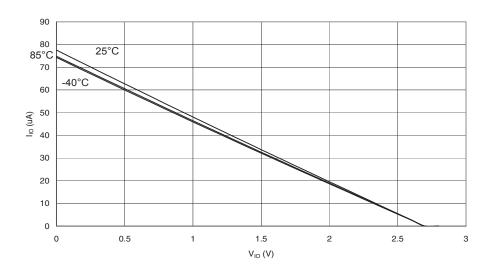

Figure 29-47. Calibrated 8MHz RC Oscillator Frequency vs.  $V_{CC}$

Figure 29-48. Calibrated 8MHz RC Oscillator Frequency vs. Osccal Value

# ATmega325/3250/645/6450

| Address                    | Name             | Bit 7                        | Bit 6      | Bit 5        | Bit 4                 | Bit 3            | Bit 2              | Bit 1            | Bit 0      | Page      |

|----------------------------|------------------|------------------------------|------------|--------------|-----------------------|------------------|--------------------|------------------|------------|-----------|

| (0x84)                     | TCNT1L           |                              |            |              | Timer/Co              | unter1 Low       |                    |                  |            | 127       |

| (0x83)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x82)                     | TCCR1C           | FOC1A                        | FOC1B      | -            | -                     | -                | -                  | -                | -          | 126       |

| (0x81)                     | TCCR1B           | ICNC1                        | ICES1      | -            | WGM13                 | WGM12            | CS12               | CS11             | CS10       | 125       |

| (0x80)                     | TCCR1A           | COM1A1                       | COM1A0     | COM1B1       | COM1B0                | -                | -                  | WGM11            | WGM10      | 123       |

| (0x7F)                     | DIDR1            | -                            | -          | -            | -                     | -                | -                  | AIN1D            | AINOD      | 200       |

| (0x7E)                     | DIDR0            | ADC7D                        | ADC6D      | ADC5D        | ADC4D                 | ADC3D            | ADC2D              | ADC1D            | ADC0D      | 217       |

| (0x7D)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x7C)                     | ADMUX            | REFS1                        | REFS0      | ADLAR        | MUX4                  | MUX3             | MUX2               | MUX1             | MUX0       | 213       |

| (0x7B)                     | ADCSRB           | -                            | ACME       | -            | -                     | -                | ADTS2              | ADTS1            | ADTS0      | 198/217   |

| (0x7A)                     | ADCSRA           | ADEN                         | ADSC       | ADATE        | ADIF                  | ADIE             | ADPS2              | ADPS1            | ADPS0      | 215       |

| (0x79)                     | ADCH             |                              |            |              | ADC Data F            | Register High    |                    |                  |            | 216       |

| (0x78)                     | ADCL             |                              |            |              | ADC Data F            | Register Low     |                    |                  |            | 216       |

| (0x77)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x76)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x75)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x74)                     | Reserved         | -                            |            | -            | -                     | -                | -                  | -                | -          |           |

| . ,                        | PCMSK3           | -                            | PCINT30    | PCINT29      | PCINT28               | PCINT27          | PCINT26            | PCINT25          | PCINT24    | 58        |

| (0x73)                     | Reserved         | _                            | -          | -            | -                     | -                | -                  | -                | -          | 00        |

| (0x72)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x71)                     | TIMSK2           | -                            |            | -            | -                     | -                | -                  | -<br>OCIE2A      | -<br>TOIE2 | 146       |

| (0x70)                     | TIMSK2           |                              |            |              |                       |                  | -<br>OCIE1B        | OCIE2A<br>OCIE1A | TOIE2      |           |

| (0x6F)                     |                  | -                            | -          | ICIE1        | -                     | -                | - OCIETB           |                  | TOIET      | 128       |

| (0x6E)                     | TIMSK0<br>PCMSK2 | -<br>DCINT22                 |            | -<br>DCINT21 | -                     | -<br>PCINT19     |                    | OCIE0A           |            | 99<br>58  |

| (0x6D)                     |                  | PCINT23                      | PCINT22    | PCINT21      | PCINT20               |                  | PCINT18<br>PCINT10 | PCINT17          | PCINT16    | 58        |

| (0x6C)                     | PCMSK1           | PCINT15                      | PCINT14    | PCINT13      | PCINT12               | PCINT11          |                    | PCINT9           | PCINT8     | 59        |

| (0x6B)                     | PCMSK0           | PCINT7                       | PCINT6     | PCINT5       | PCINT4                | PCINT3           | PCINT2             | PCINT1           | PCINT0     | 59        |

| (0x6A)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x69)                     | EICRA            | -                            | -          | -            | -                     | -                | -                  | ISC01            | ISC00      | 56        |

| (0x68)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x67)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x66)                     | OSCCAL           |                              |            |              | Dscillator Calibratio | n Register [CAL7 | 0]                 |                  |            | 32        |

| (0x65)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x64)                     | PRR              | -                            | -          | -            | -                     | PRTIM1           | PRSPI              | PSUSART0         | PRADC      | 40        |

| (0x63)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x62)                     | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| (0x61)                     | CLKPR            | CLKPCE                       | -          | -            | -                     | CLKPS3           | CLKPS2             | CLKPS1           | CLKPS0     | 32        |

| (0x60)                     | WDTCR            | -                            | -          | -            | WDCE                  | WDE              | WDP2               | WDP1             | WDP0       | 47        |

| 0x3F (0x5F)                | SREG             | I                            | Т          | Н            | S                     | V                | Ν                  | Z                | С          | 12        |

| 0x3E (0x5E)                | SPH              |                              |            |              | Stack Po              | inter High       |                    |                  |            | 14        |

| 0x3D (0x5D)                | SPL              |                              |            |              | Stack Po              | inter Low        |                    |                  |            | 14        |

| 0x3C (0x5C)                | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| 0x3B (0x5B)                | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| 0x3A (0x5A)                | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| 0x39 (0x59)                | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| 0x38 (0x58)                | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| 0x38 (0x58)<br>0x37 (0x57) | SPMCSR           | SPMIE                        | RWWSB      | -            | RWWSRE                | BLBSET           | PGWRT              | PGERS            | SPMEN      | 263       |

| 0x37 (0x57)<br>0x36 (0x56) | Reserved         |                              |            |              |                       |                  |                    |                  |            |           |

| 0x36 (0x56)<br>0x35 (0x55) | MCUCR            | JTD                          | -          | -            | PUD                   | -                | -                  | IVSEL            | IVCE       | 53/81/227 |

| 0x35 (0x55)<br>0x34 (0x54) | MCUSR            | -                            | -          | -            | JTRF                  | WDRF             | BORF               | EXTRF            | PORF       | 47        |

| 0x34 (0x54)<br>0x33 (0x53) | SMCR             | -                            | -          | -            | -                     | SM2              | SM1                | SM0              | SE         | 35        |

| ( )                        | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| 0x32 (0x52)                | OCDR             | -<br>IDRD/OCDR7              | -<br>OCDR6 | -<br>OCDR5   | -<br>OCDR4            | -<br>OCDR3       | -<br>OCDR2         | -<br>OCDR1       | -<br>OCDR0 | 223       |

| 0x31 (0x51)                | ACSR             | ACD                          | ACBG       | ACO          | ACI                   | ACIE             | ACIC               | ACIS1            | ACISO      | 198       |

| 0x30 (0x50)                | Reserved         | ACD -                        |            | -            | - ACI                 | -                | ACIC -             |                  |            | 190       |

| 0x2F (0x4F)                |                  | -                            | -          | -            |                       |                  | -                  | -                | -          | 150       |

| 0x2E (0x4E)                | SPDR             |                              | MCO        |              |                       | a Register       |                    |                  | OPIOV      | 156       |

| 0x2D (0x4D)                | SPSR             | SPIF                         | WCOL       | -            | -                     | -                | -                  | -                | SPI2X      | 156       |

| 0x2C (0x4C)                | SPCR             | SPIE                         | SPE        | DORD         | MSTR                  | CPOL             | CPHA               | SPR1             | SPR0       | 154       |

| 0x2B (0x4B)                | GPIOR2           |                              |            |              |                       | se I/O Register  |                    |                  |            | 25        |

| 0x2A (0x4A)                | GPIOR1           | General Purpose I/O Register |            |              |                       |                  |                    | 25               |            |           |

| 0x29 (0x49)                | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

| 0x28 (0x48)                | Reserved         | -                            | -          | -            | -                     | -                | -                  | -                | -          |           |

|                            | OCR0A            |                              |            |              | Timer/Counter0 (      | Dutput Compare A |                    |                  |            | 98        |

| 0x27 (0x47)                | TCNT0            |                              |            |              |                       | Counter0         |                    |                  |            | 98        |

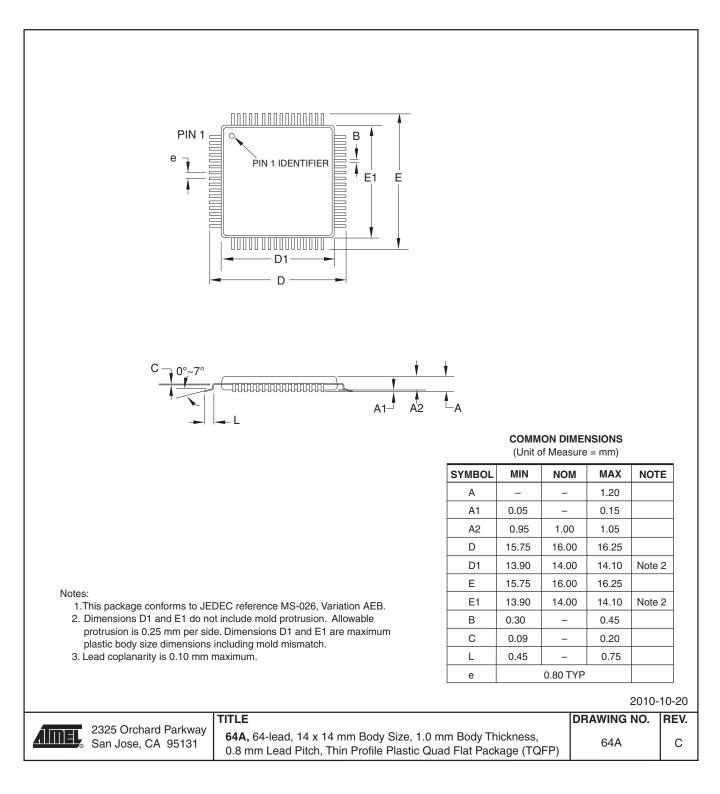

# 33. Packaging Information

33.1 64A

# 34. Errata

# 34.1 Errata ATmega325

The revision letter in this section refers to the revision of the ATmega325 device.

# 34.1.1 ATmega325 Rev. C

• Interrupts may be lost when writing the timer registers in the asynchronous timer

1. Interrupts may be lost when writing the timer registers in the asynchronous timer The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

# **Problem Fix/ Workaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

# 34.1.2 ATmega325 Rev. B

Not sampled.

# 34.1.3 ATmega325 Rev. A

- Interrupts may be lost when writing the timer registers in the asynchronous timer

- 1. Interrupts may be lost when writing the timer registers in the asynchronous timer The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

# **Problem Fix/ Workaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

# 34.2 Errata ATmega3250

The revision letter in this section refers to the revision of the ATmega3250 device.

# 34.2.1 ATmega3250 Rev. C

• Interrupts may be lost when writing the timer registers in the asynchronous timer

1. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

# **Problem Fix/ Workaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

# 34.2.2 ATmega3250 Rev. B

Not sampled.

# 35.11 Rev. 2570D - 05/05

- 1. MLF-package alternative changed to "Quad Flat No-Lead/Micro Lead Frame Package QFN/MLF".

- 2. Added "Pin Change Interrupt Timing" on page 55.

- 3. Updated "Signature Bytes" on page 268.

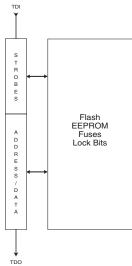

- 4. Updated Table 27-15 on page 282.

- 5. Added Figure 27-12 on page 284.

- 6. Updated Figure 23-9 on page 209 and Figure 27-5 on page 276.

- 7. Updated algorithm "Enter Programming Mode" on page 271.

- 8. Added "Supply Current of I/O modules" on page 311.

- 9. Updated "Ordering Information" on page 343.

# 35.12 Rev. 2570C - 11/04

- 1. "0 8MHz @ 2.7 5.5V; 0 16MHz @ 4.5 5.5V" on page 1 updated.

- 2. Table 9-8 on page 30 updated.

- COM01:0 renamed COM0A1:0 in "8-bit Timer/Counter0 with PWM" on page 85.

- 4. PRR-bit descripton added to "16-bit Timer/Counter1" on page 102, "SPI Serial Peripheral Interface" on page 148, and "USART0" on page 157.

- 5. "Part Number" on page 225 updated.

- 6. "Typical Characteristics" on page 306 updated.

- 7. "DC Characteristics" on page 297 updated.

- 8. "Alternate Functions of Port G" on page 76 updated.

# 35.13 Rev. 2570B - 09/04

1. Updated "Ordering Information" on page 343.

# 35.14 Rev. 2570A - 09/04

1. Initial revision.

# ATmega325/3250/645/6450

|    | 26.9     | Register Description                                       | 263 |

|----|----------|------------------------------------------------------------|-----|

| 27 | Memor    | y Programming                                              | 265 |

|    | 27.1     | Program And Data Memory Lock Bits                          | 265 |

|    | 27.2     | Fuse Bits                                                  | 266 |

|    | 27.3     | Signature Bytes                                            |     |

|    | 27.4     | Calibration Byte                                           |     |

|    | 27.5     | Parallel Programming Parameters, Pin Mapping, and Commands |     |

|    | 27.6     | Parallel Programming                                       | 271 |

|    | 27.7     | Serial Downloading                                         |     |

|    | 27.8     | Programming via the JTAG Interface                         | 284 |

| 28 | Electric | cal Characteristics                                        | 297 |

|    | 28.1     | Absolute Maximum Ratings*                                  | 297 |

|    | 28.2     | DC Characteristics                                         | 297 |

|    | 28.3     | Speed Grades                                               | 299 |

|    | 28.4     | Clock Characteristics                                      |     |

|    | 28.5     | System and Reset Characteristics                           |     |

|    | 28.6     | SPI Timing Characteristics                                 |     |

|    | 28.7     | ADC                                                        |     |

| 29 | Туріса   | I Characteristics                                          | 306 |

|    | 29.1     | Active Supply Current                                      |     |

|    | 29.2     | Idle Supply Current                                        |     |

|    | 29.3     | Supply Current of I/O modules                              | 311 |

|    | 29.4     | Power-down Supply Current                                  | 312 |

|    | 29.5     | Power-save Supply Current                                  | 313 |

|    | 29.6     | Standby Supply Current                                     | 313 |

|    | 29.7     | Pin Pull-up                                                | 314 |

|    | 29.8     | Pin Driver Strength                                        | 317 |

|    | 29.9     | Pin Thresholds and hysteresis                              |     |

|    | 29.10    | BOD Thresholds and Analog Comparator Offset                |     |

|    | 29.11    | Internal Oscillator Speed                                  | 329 |

|    | 29.12    | Current Consumption of Peripheral Units                    |     |

|    | 29.13    | Current Consumption in Reset and Reset Pulsewidth          | 334 |

| 30 | Registe  | er Summary                                                 | 336 |

| 31 | Instruc  | tion Set Summary                                           | 340 |

#### Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1)(408) 441-0311 Fax: (+1)(408) 487-2600 www.atmel.com

#### Atmel Asia Limited Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369

Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 JAPAN Tel: (+81)(3) 3523-3551 Fax: (+81)(3) 3523-7581

#### © 2011 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, AVR<sup>®</sup>, QTouch<sup>®</sup>, QMatrix<sup>®</sup>, AVR Studio<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Windows<sup>®</sup> and others are registered trademarks of Microsoft Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROF-ITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.