#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ic2-rlril |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# SFR Mapping

The Special Function Registers (SFRs) of the AT89C51IC2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP

- I/O port registers: P0, P1, P2, P3, PI2

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- PCA (Programmable Counter Array) registers: CCON, CCAPMx, CL, CH, CCAPxH, CCAPxL (x: 0 to 4)

- Power and clock control registers: PCON

- Hardware Watchdog Timer registers: WDTRST, WDTPRG

- Interrupt system registers: IEN0, IPL0, IPH0, IEN1, IPL1, IPH1

- Keyboard Interface registers: KBE, KBF, KBLS

- SPI registers: SPCON, SPSTR, SPDAT

- 2-wire Interface registers: SSCON, SSCS, SSDAT, SSADR

- BRG (Baud Rate Generator) registers: BRL, BDRCON

- Flash register: FCON

- Clock Prescaler register: CKRL

- 32 kHz Sub Clock Oscillator registers: CKSEL, OSSCON

### Table 2. C51 Core SFRs

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High byte |    |    |    |     |     |    |    |   |

#### Table 3. System Management SFRs

| Mnemonic | Add | Name                        | 7     | 6     | 5          | 4    | 3    | 2      | 1          | 0      |

|----------|-----|-----------------------------|-------|-------|------------|------|------|--------|------------|--------|

| PCON     | 87h | Power Control               | SMOD1 | SMOD0 | -          | -    | GF1  | GF0    | PD         | IDL    |

| AUXR     | 8Eh | Auxiliary Register 0        | -     | -     | M0         |      | XRS1 | XRS0   | EXTRA<br>M | AO     |

| AUXR1    | A2h | Auxiliary Register 1        | -     | -     | ENBOO<br>T | -    | GF3  | 0      | -          | DPS    |

| CKRL     | 97h | Clock Reload Register       | -     | -     | -          | -    | -    | -      | -          | -      |

| CKSEL    | 85h | Clock Selection Register    | -     | -     | -          | -    | -    | -      | -          | CKS    |

| OSCON    | 86h | Oscillator Control Register | -     | -     | -          | -    | -    | SCLKT0 | OscBEn     | OscAEn |

| CKCKON0  | 8Fh | Clock Control Register 0    | TWIX2 | WDTX2 | PCAX2      | SIX2 | T2X2 | T1X2   | T0X2       | X2     |

| CKCKON1  | AFh | Clock Control Register 1    | -     | -     | -          | -    | -    | -      | -          | SPIX2  |

### Table 4. Interrupt SFRs

| Mnemonic | Add | Name                              | 7  | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|----------|-----|-----------------------------------|----|------|------|-----|------|------|------|------|

| IEN0     | A8h | Interrupt Enable Control 0        | EA | EC   | ET2  | ES  | ET1  | EX1  | ET0  | EX0  |

| IEN1     | B1h | Interrupt Enable Control 1        | -  | -    | -    | -   | -    | ESPI | ETWI | KBD  |

| IPH0     | B7h | Interrupt Priority Control High 0 | -  | PPCH | PT2H | PHS | PT1H | PX1H | PT0H | PX0H |

| IPL0     | B8h | Interrupt Priority Control Low 0  | -  | PPCL | PT2L | PLS | PT1L | PX1L | PTOL | PX0L |

| IPH1     | B3h | Interrupt Priority Control High 1 | -  | -    | -    | -   | -    | SPIH | TWIH | KBDH |

| IPL1     | B2h | Interrupt Priority Control Low 1  | -  | -    | -    | -   | -    | SPIL | TWIL | KBDL |

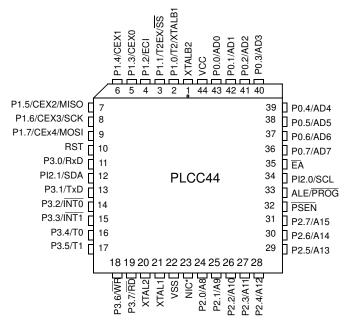

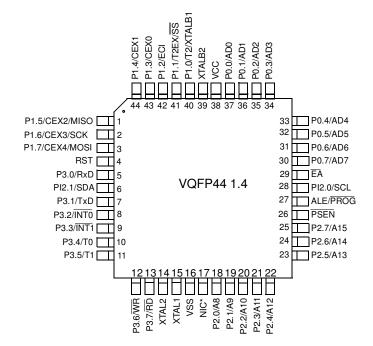

# **Pin Configurations**

#### Figure 2. Pin Configurations

• It is always possible to switch dynamically by software from OscA to OscB, and vice versa by changing CKS bit.

Idle Modes

- IDLE modes are achieved by using any instruction that writes into PCON.0 bit (IDL)

- IDLE modes A and B depend on previous software sequence, prior to writing into PCON.0 bit:

- IDLE MODE A: OscA is running (OscAEn = 1) and selected (CKS = 1)

- IDLE MODE B: OscB is running (OscBEn = 1) and selected (CKS = 0)

- The unused oscillator OscA or OscB can be stopped by software by clearing OscAEn or OscBEn respectively.

- IDLE mode can be canceled either by Reset, or by activation of any enabled interruption

- In both cases, PCON.0 bit (IDL) is cleared by hardware

- Exit from IDLE modes will leave Oscillators control bits (OscEnA, OscEnB, CKS) unchanged.

- Power Down Modes

POWER DOWN modes are achieved by using any instruction that writes into PCON.1 bit (PD)

- POWER DOWN modes A and B depend on previous software sequence, prior to writing into PCON.1 bit:

- Both OscA and OscB will be stopped.

- POWER DOWN mode can be cancelled either by a hardware Reset, an external interruption, or the keyboard interrupt.

- By Reset signal: The CPU will restart according to OSC bit in Hardware Security Bit (HSB) register.

- By INT0 or INT1 interruption, if enabled: (standard behavioral), request on Pads must be driven low enough to ensure correct restart of the oscillator which was selected when entering in Power down.

- By keyboard Interrupt if enabled: a hardware clear of the PCON.1 flag ensure the restart of the oscillator which was selected when entering in Power down.

Table 18. Overview

| PCON.1 | PCON.0 | OscBEn | OscAEn | CKS | Selected Mode                  | Comment                                                     |

|--------|--------|--------|--------|-----|--------------------------------|-------------------------------------------------------------|

| 0      | 0      | 0      | 1      | 1   | NORMAL MODE<br>A, OscB stopped | Default mode after power-up or<br>Warm Reset                |

| 0      | 0      | 1      | 1      | 1   | NORMAL MODE<br>A, OscB running | Default mode after power-up or<br>Warm Reset + OscB running |

| 0      | 0      | 1      | 0      | 0   | NORMAL MODE<br>B, OscA stopped | OscB running and selected                                   |

| 0      | 0      | 1      | 1      | 0   | NORMAL MODE<br>B, OscA running | OscB running and selected +<br>OscA running                 |

| х      | х      | 0      | 0      | х   | INVALID                        | OscA & OscB cannot be stopped at the same time              |

| х      | х      | х      | 0      | 1   | INVALID                        | OscA must not be stopped, as used for CPU and peripherals   |

| х      | х      | 0      | х      | 0   | INVALID                        | OscB must not be stopped as used for CPU and peripherals    |

; Block move using dual data pointers ; Modifies DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added 00A2 AUXR1 EOU 0A2H ; 0000 909000MOV DPTR, #SOURCE ; address of SOURCE 0003 05A2 INC AUXR1 ; switch data pointers 0005 90A000 MOV DPTR, #DEST ; address of DEST 0008 LOOP: 0008 05A2 INC AUXR1 ; switch data pointers 000A E0 MOVX A, @DPTR ; get a byte from SOURCE 000B A3 INC DPTR ; increment SOURCE address 000C 05A2 INC AUXR1 ; switch data pointers 000E FO MOVX @DPTR, A ; write the byte to DEST 000F A3 INC DPTR ; increment DEST address 0010 70F6JNZ LOOP ; check for 0 terminator 0012 05A2 INC AUXR1 ; (optional) restore DPS

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

## Table 25. T2MOD Register

T2MOD - Timer 2 Mode Control Register (C9h)

| 7             | 6               | 5                              | 4                                                                                                                              | 3                                          | 2              | 1             | 0    |  |  |  |  |

|---------------|-----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------|---------------|------|--|--|--|--|

| -             | -               | -                              | -                                                                                                                              | -                                          | -              | T2OE          | DCEN |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                    | Description                                                                                                                    |                                            |                |               |      |  |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value r | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                |                                            |                |               |      |  |  |  |  |

| 6             | -               | <b>Reserved</b><br>The value r | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                |                                            |                |               |      |  |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value r | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                |                                            |                |               |      |  |  |  |  |

| 4             | -               | <b>Reserved</b><br>The value r | ead from this                                                                                                                  | bit is indeterm                            | ninate. Do not | set this bit. |      |  |  |  |  |

| 3             | -               | Reserved<br>The value r        | ead from this                                                                                                                  | bit is indeterm                            | ninate. Do not | set this bit. |      |  |  |  |  |

| 2             | -               | Reserved<br>The value r        | ead from this                                                                                                                  | bit is indeterm                            | ninate. Do not | set this bit. |      |  |  |  |  |

| 1             | T2OE            | Cleared to                     | Timer 2 Output Enable bit<br>Cleared to program P1.0/T2 as clock input or I/O port.<br>Set to program P1.0/T2 as clock output. |                                            |                |               |      |  |  |  |  |

| 0             | DCEN            | Cleared to                     |                                                                                                                                | <b>bit</b><br>2 as up/down<br>up/down coun |                |               |      |  |  |  |  |

Reset Value = XXXX XX00b Not bit addressable

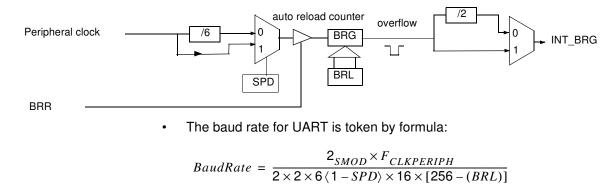

# Internal Baud Rate Generator (BRG)

When the internal Baud Rate Generator is used, the Baud Rates are determined by the BRG overflow depending on the BRL reload value, the value of SPD bit (Speed Mode) in BDRCON register and the value of the SMOD1 bit in PCON register.

#### Figure 21. Internal Baud Rate

$(BRL) = 256 - \frac{2_{SMOD1} \times F_{CLKPERIPH}}{2 \times 2 \times 6_{(1 - SPD)} \times 16 \times BaudRate}$

AIMEL

## **UART Registers**

Table 40.

SADEN Register

SADEN - Slave Address Mask Register for UART (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

#### Table 41. SADDR Register

SADDR - Slave Address Register for UART (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

#### Table 42. SBUF Register

SBUF - Serial Buffer Register for UART (99h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = XXXX XXXXb

#### Table 43. BRL Register

BRL - Baud Rate Reload Register for the internal baud rate generator, UART (9Ah)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

## Table 48. IENO Register

IEN0 - Interrupt Enable Register (A8h)

| 7             | 6               | 5             | 4                                                                                                                                    | 3                                                  | 2     | 1 | 0 |  |  |  |  |

|---------------|-----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------|---|---|--|--|--|--|

| EA            | EC              | ET2           | ET2 ES ET1 EX1 ET0 EX0                                                                                                               |                                                    |       |   |   |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description   | Description                                                                                                                          |                                                    |       |   |   |  |  |  |  |

| 7             | EA              |               | nterrupt bit<br>isable all inter<br>e all interrupts                                                                                 |                                                    |       |   |   |  |  |  |  |

| 6             | EC              |               | CA interrupt enable bit<br>eared to disable.<br>et to enable.                                                                        |                                                    |       |   |   |  |  |  |  |

| 5             | ET2             | Cleared to di | Fimer 2 overflow interrupt Enable bit<br>Cleared to disable timer 2 overflow interrupt.<br>Set to enable timer 2 overflow interrupt. |                                                    |       |   |   |  |  |  |  |

| 4             | ES              |               | Enable bit<br>isable serial p<br>e serial port in                                                                                    |                                                    |       |   |   |  |  |  |  |

| 3             | ET1             | Cleared to di | sable timer 1                                                                                                                        | pt Enable bit<br>overflow inter<br>flow interrupt. | rupt. |   |   |  |  |  |  |

| 2             | EX1             | Cleared to di | errupt 1 Enal<br>isable externa<br>e external inte                                                                                   | al interrupt 1.                                    |       |   |   |  |  |  |  |

| 1             | ET0             | Cleared to di | Timer 0 overflow interrupt Enable bit<br>Cleared to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt. |                                                    |       |   |   |  |  |  |  |

| 0             | EX0             | Cleared to di | errupt 0 Enal<br>isable externa<br>e external inte                                                                                   | al interrupt 0.                                    |       |   |   |  |  |  |  |

Reset Value = 0000 0000b Bit addressable

## Table 49. IPL0 Register

IPL0 - Interrupt Priority Register (B8h)

| 7             | 6               | 5                        | 4                                                                                   | 3    | 2    | 1    | 0    |  |  |

|---------------|-----------------|--------------------------|-------------------------------------------------------------------------------------|------|------|------|------|--|--|

| -             | PPCL            | PT2L                     | PSL                                                                                 | PT1L | PX1L | PTOL | PX0L |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description              |                                                                                     |      |      |      |      |  |  |

| 7             | -               | Reserved<br>The value re | eserved<br>he value read from this bit is indeterminate. Do not set this bit.       |      |      |      |      |  |  |

| 6             | PPCL            |                          | PCA interrupt Priority bit<br>Refer to PPCH for priority level.                     |      |      |      |      |  |  |

| 5             | PT2L            |                          | Timer 2 overflow interrupt Priority bit<br>Refer to PT2H for priority level.        |      |      |      |      |  |  |

| 4             | PSL             |                          | Serial port Priority bit<br>Refer to PSH for priority level.                        |      |      |      |      |  |  |

| 3             | PT1L            |                          | Timer 1 overflow interrupt Priority bit<br>Refer to PT1H for priority level.        |      |      |      |      |  |  |

| 2             | PX1L            |                          | External interrupt 1 Priority bit<br>Refer to PX1H for priority level.              |      |      |      |      |  |  |

| 1             | PTOL            |                          | <b>Fimer 0 overflow interrupt Priority bit</b><br>Refer to PT0H for priority level. |      |      |      |      |  |  |

| 0             | PX0L            |                          | errupt 0 Prio<br>)H for priority                                                    | •    |      |      |      |  |  |

Reset Value = X000 0000b Bit addressable

| Error Conditions       | The following flags in the SPSTA signal SPI error conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode Fault (MODF)      | <ul> <li>Mode Fault error in Master mode SPI indicates that the level on the Slave Select (SS) pin is inconsistent with the actual mode of the device. MODF is set to warn that there may be a multi-master conflict for system control. In this case, the SPI system is affected in the following ways:</li> <li>An SPI receiver/error CPU interrupt request is generated</li> <li>The SPEN bit in SPCON is cleared. This disables the SPI</li> <li>The MSTR bit in SPCON is cleared</li> <li>When SS Disable (SSDIS) bit in the SPCON register is cleared, the MODF flag is set when the SS signal becomes '0'.</li> </ul> |

|                        | However, as stated before, for a system with one Master, if the $\overline{SS}$ pin of the Master device is pulled low, there is no way that another Master attempts to drive the network. In this case, to prevent the MODF flag from being set, software can set the SSDIS bit in the SPCON register and therefore making the $\overline{SS}$ pin as a general-purpose I/O pin.                                                                                                                                                                                                                                            |

|                        | Clearing the MODF bit is accomplished by a read of SPSTA register with MODF bit set, followed by a write to the SPCON register. SPEN Control bit may be restored to its original set state after the MODF bit has been cleared.                                                                                                                                                                                                                                                                                                                                                                                              |

| Write Collision (WCOL) | A Write Collision (WCOL) flag in the SPSTA is set when a write to the SPDAT register is done during a transmit sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                        | WCOL does not cause an interruption, and the transfer continues uninterrupted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | Clearing the WCOL bit is done through a software sequence of an access to SPSTA and an access to SPDAT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Overrun Condition      | An overrun condition occurs when the Master device tries to send several data Bytes<br>and the Slave devise has not cleared the SPIF bit issuing from the previous data Byte<br>transmitted. In this case, the receiver buffer contains the Byte sent after the SPIF bit was<br>last cleared. A read of the SPDAT returns this Byte. All others Bytes are lost.                                                                                                                                                                                                                                                              |

|                        | This condition is not detected by the SPI peripheral.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SS Error Flag (SSERR)  | A Synchronous Serial Slave Error occurs when $\overline{SS}$ goes high before the end of a received data in slave mode. SSERR does not cause in interruption, this bit is cleared by writing 0 to SPEN bit (reset of the SPI state machine).                                                                                                                                                                                                                                                                                                                                                                                 |

| Interrupts             | Two SPI status flags can generate a CPU interrupt requests:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 57. SPI Interrupts

| Flag                    | Request                                               |

|-------------------------|-------------------------------------------------------|

| SPIF (SP data transfer) | SPI Transmitter Interrupt request                     |

| MODF (Mode Fault)       | SPI Receiver/Error Interrupt Request (if SSDIS = '0') |

Serial Peripheral data transfer flag, SPIF: This bit is set by hardware when a transfer has been completed. SPIF bit generates transmitter CPU interrupt requests.

Mode Fault flag, MODF: This bit becomes set to indicate that the level on the SS is inconsistent with the mode of the SPI. MODF with SSDIS reset, generates receiver/error CPU interrupt requests. When SSDIS is set, no MODF interrupt request is generated.

Figure 32 gives a logical view of the above statements.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                            |

|---------------|-----------------|----------------------------------------------------------------------------------------|

| 1             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |

| 0             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit. |

Reset Value = 00X0 XXXXb

Not Bit addressable

*Serial Peripheral DATa Register* (SPDAT) The Serial Peripheral Data Register (Table 60) is a read/write buffer for the receive data register. A write to SPDAT places data directly into the shift register. No transmit buffer is available in this model.

A Read of the SPDAT returns the value located in the receive buffer and not the content of the shift register.

#### Table 60. SPDAT Register

SPDAT - Serial Peripheral Data Register (0C5H)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

Reset Value = Indeterminate

R7:R0: Receive data bits

SPCON, SPSTA and SPDAT registers may be read and written at any time while there is no on-going exchange. However, special care should be taken when writing to them while a transmission is on-going:

- Do not change SPR2, SPR1 and SPR0

- Do not change CPHA and CPOL

- Do not change MSTR

- Clearing SPEN would immediately disable the peripheral

- Writing to the SPDAT will cause an overflow.

## 2-wire Interface (TWI)

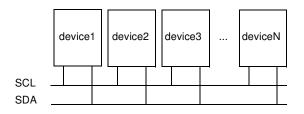

This section describes the 2-wire interface. In the rest of the section SSLC means Twowire. The 2-wire bus is a bi-directional 2-wire serial communication standard. It is designed primarily for simple but efficient integrated circuit (IC) control. The system is comprised of two lines, SCL (Serial Clock) and SDA (Serial Data) that carry information between the ICs connected to them. The serial data transfer is limited to 400Kbit/s in standard mode. Various communication configuration can be designed using this bus. Figure 35 shows a typical 2-wire bus configuration. All the devices connected to the bus can be master and slave.

Figure 35. 2-wire Bus Configuration

| Bit<br>Number | Bit<br>Mnemonic | Description                        |

|---------------|-----------------|------------------------------------|

| 1             | SD1             | Address bit 1 or Data bit 1.       |

| 0             | SD0             | Address bit 0 (R/W) or Data bit 0. |

Table 75. SSCS (094h) read - Synchronous Serial Control and Status Register

| 7   | 6   | 5   | 4   | 3   | 2 | 1 | 0 |

|-----|-----|-----|-----|-----|---|---|---|

| SC4 | SC3 | SC2 | SC1 | SC0 | 0 | 0 | 0 |

#### Table 76. SSCS Register: Read Mode - Reset Value = F8h

| Bit<br>Number | Bit<br>Mnemonic | Description                                    |

|---------------|-----------------|------------------------------------------------|

| 0             | 0               | Always zero                                    |

| 1             | 0               | Always zero                                    |

| 2             | 0               | Always zero                                    |

| 3             | SC0             | Status Code bit 0<br>See Table 68.to Table 72. |

| 4             | SC1             | Status Code bit 1<br>See Table 68.to Table 72. |

| 5             | SC2             | Status Code bit 2<br>See Table 68.to Table 72. |

| 6             | SC3             | Status Code bit 3<br>See Table 68.to Table 72. |

| 7             | SC4             | Status Code bit 4<br>See Table 68.to Table 72. |

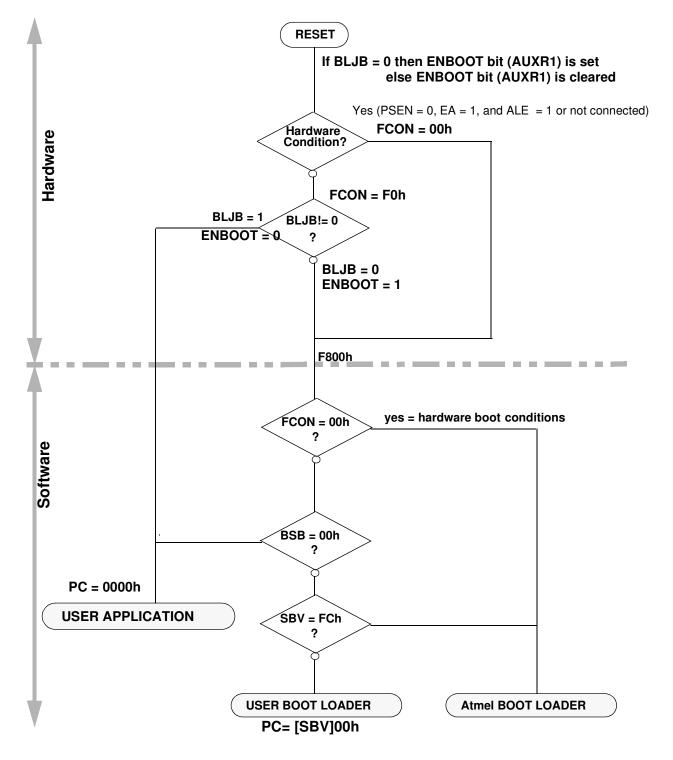

#### **Boot Process**

Figure 46. Bootloader process

|                              |                                                                                                                                                                                                                                                                                                                                           | R                                                                                                                                                                          |                               |  |  |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|

| Full Chip Erase              | <ul> <li>The ISP command "Full Chip Erase" erases all User Flash memory (fills with FFh) an sets some Bytes used by the bootloader at their default values:</li> <li>BSB = FFh</li> <li>SBV = FCh</li> <li>SSB = FFh and finally erase the Software Security Bits</li> <li>The Full Chip Erase does not affect the bootloader.</li> </ul> |                                                                                                                                                                            |                               |  |  |  |  |

| Checksum Error               | When a checksum error is detecte                                                                                                                                                                                                                                                                                                          | d send 'X' followed with C                                                                                                                                                 | R&LF.                         |  |  |  |  |

| Flow Description             |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                            |                               |  |  |  |  |

| Overview                     |                                                                                                                                                                                                                                                                                                                                           | An initialization step must be performed after each Reset. After microcontroller reset, he bootloader waits for an autobaud sequence (see section 'autobaud performance'). |                               |  |  |  |  |

|                              | When the communication is ini requested by the host.                                                                                                                                                                                                                                                                                      | tialized the protocol de                                                                                                                                                   | pends on the record type      |  |  |  |  |

|                              | FLIP, a software utility to impleme<br>Atmel the web site.                                                                                                                                                                                                                                                                                | ent ISP programming with                                                                                                                                                   | a PC, is available from the   |  |  |  |  |

| Communication Initialization | The host initializes the communica to compute the baudrate (autobau                                                                                                                                                                                                                                                                       |                                                                                                                                                                            | racter to help the bootloader |  |  |  |  |

|                              | Figure 47. Initialization<br><u>Host</u>                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                            | <u>Bootloader</u>             |  |  |  |  |

|                              | Init Communication                                                                                                                                                                                                                                                                                                                        | "U" <b>&gt;</b>                                                                                                                                                            | Performs Autobaud             |  |  |  |  |

|                              | If (not received "U")<br>Else<br>Communication Opened                                                                                                                                                                                                                                                                                     | <b>≺</b> "U"                                                                                                                                                               | Sends Back 'U' Character      |  |  |  |  |

MEI

#### Autobaud Performances

The ISP feature allows a wide range of baud rates in the user application. It is also adaptable to a wide range of oscillator frequencies. This is accomplished by measuring the bit-time of a single bit in a received character. This information is then used to program the baud rate in terms of timer counts based on the oscillator frequency. The ISP feature requires that an initial character (an uppercase U) be sent to the AT89C51IC2 to establish the baud rate. Table 91 shows the autobaud capability.

| Frequency (MHz)<br>Baudrate (bit/s) | 1.8432 | 2       | 2.4576 | 3      | 3.6864 | 4  | 5  | 6  | 7.3728 | 8  |

|-------------------------------------|--------|---------|--------|--------|--------|----|----|----|--------|----|

| 2400                                | ОК     | ОК      | OK     | OK     | OK     | OK | OK | OK | ОК     | OK |

| 4800                                | ОК     | -       | OK     | OK     | OK     | OK | OK | OK | ОК     | ОК |

| 9600                                | OK     | -       | OK     | OK     | ОК     | ОК | ОК | ОК | ОК     | ОК |

| 19200                               | ОК     | -       | OK     | ОК     | ОК     | -  | -  | ОК | ОК     | ОК |

| 38400                               | -      | -       | OK     |        | ОК     | -  | ОК | ОК | ОК     |    |

| 57600                               | -      | -       | -      | -      | ОК     | -  | -  | -  | ОК     |    |

| 115200                              | -      | -       | -      | -      | -      | -  | -  | -  | ОК     |    |

|                                     | 1      |         |        | I      |        |    |    |    |        |    |

| Frequency (MHz)                     |        |         |        |        |        |    |    |    |        |    |

| Baudrate (bit/s)                    | 10     | 11.0592 | 12     | 14.318 | 14.746 | 16 | 20 | 24 | 26.6   |    |

| 2400                                | ОК     | ОК      | ОК     | ОК     | ОК     | ОК | ОК | ОК | ОК     |    |

| 4800                                | ОК     | ОК      | ОК     | OK     | ОК     | ОК | ОК | ОК | ОК     |    |

| 9600                                | ОК     | ОК      | ОК     | ОК     | ОК     | ОК | ОК | ОК | ок     |    |

| 19200                               | ОК     | ОК      | ОК     | OK     | ОК     | ОК | ОК | ОК | ОК     |    |

| 38400                               | -      | ОК      | OK     | OK     | ОК     | OK | OK | OK | ОК     |    |

| 57600                               | -      | ОК      | -      | OK     | ОК     | OK | OK | OK | ОК     |    |

| 115200                              | -      | ОК      | -      | OK     | OK     | -  | -  | -  | -      |    |

#### Table 91. Autobaud Performances

# Command Data Stream Protocol

All commands are sent using the same flow. Each frame sent by the host is echoed by the bootloader.

# **Electrical Characteristics**

## **Absolute Maximum Ratings**

|                                                                  | Note: Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage                          |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| C = commercial                                                   | to the device. This is a stress rating only and func-                                                                        |

| I = industrial40°C to 85°C<br>Storage Temperature65°C to + 150°C | tional operation of the device at these or any other<br>conditions above those indicated in the operational                  |

| Voltage on $V_{CC}$ to $V_{SS}$                                  | sections of this specification is not implied. Expo-                                                                         |

| Voltage on Any Pin to $V_{SS}$ 0.5V to $V_{CC}$ + 0.5V           | sure to absolute maximum rating conditions may                                                                               |

| Power Dissipation 1 W                                            | affect device reliability.                                                                                                   |

|                                                                  | Power dissipation value is based on the maximum<br>allowable die temperature and the thermal resis-<br>tance of the package. |

# DC Parameters for Standard Voltage

$T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ;  $V_{SS} = 0V$ ;

$V_{\text{CC}}$  =2.7V to 5.5V and F = 0 to 40 MHz (both internal and external code execution)

$V_{CC}$  =4.5V to 5.5V and F = 0 to 60 MHz (internal code execution only)

| Symbol           | Parameter                                            | Min                                                                     | Тур | Мах                       | Unit        | Test Conditions                                                                                                                                                                                                                                      |

|------------------|------------------------------------------------------|-------------------------------------------------------------------------|-----|---------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIL              | Input Low Voltage                                    | -0.5                                                                    |     | 0.2 V <sub>CC</sub> - 0.1 | V           |                                                                                                                                                                                                                                                      |

| V <sub>IH</sub>  | Input High Voltage except RST, XTAL1                 | 0.2 V <sub>CC</sub> + 0.9                                               |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                                                                                                                                                      |

| $V_{IH1}^{(9)}$  | Input High Voltage RST, XTAL1                        | 0.7 V <sub>CC</sub>                                                     |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                                                                                                                                                      |

| V <sub>OL</sub>  | Output Low Voltage, ports 1, 2, 3, 4 <sup>(6)</sup>  |                                                                         |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} & \text{VCC} = 4.5\text{V to } 5.5\text{V} \\ & \text{I}_{\text{OL}} = 100 \; \mu\text{A}^{(4)} \\ & \text{I}_{\text{OL}} = 1.6 \; \text{m}\text{A}^{(4)} \\ & \text{I}_{\text{OL}} = 3.5 \; \text{m}\text{A}^{(4)} \end{split}$      |

|                  |                                                      |                                                                         |     | 0.45                      | V           | VCC = 2.7V to 5.5V<br>$I_{OL} = 0.8 \text{ mA}^{(4)}$                                                                                                                                                                                                |

| V <sub>OL1</sub> | Output Low Voltage, port 0, ALE, PSEN <sup>(6)</sup> |                                                                         |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} & \text{VCC} = 4.5 \text{V to } 5.5 \text{V} \\ & \text{I}_{\text{OL}} = 200 \; \mu \text{A}^{(4)} \\ & \text{I}_{\text{OL}} = 3.2 \; \text{m} \text{A}^{(4)} \\ & \text{I}_{\text{OL}} = 7.0 \; \text{m} \text{A}^{(4)} \end{split}$ |

|                  |                                                      |                                                                         |     | 0.45                      | V           | VCC = 2.7V to 5.5V<br>$I_{OL} = 1.6 \text{ mA}^{(4)}$                                                                                                                                                                                                |

| V <sub>OH</sub>  | Output High Voltage, ports 1, 2, 3, 4                | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |     |                           | V<br>V<br>V | $V_{CC} = 5V \pm 10\%$<br>$I_{OH} = -10 \ \mu A$<br>$I_{OH} = -30 \ \mu A$<br>$I_{OH} = -60 \ \mu A$                                                                                                                                                 |

|                  |                                                      | 0.9 V <sub>CC</sub>                                                     |     |                           | v           | VCC = 2.7V to 5.5V<br>$I_{OH}$ = -10 $\mu$ A                                                                                                                                                                                                         |

|                   | -М  |     |     | -L  |       |

|-------------------|-----|-----|-----|-----|-------|

| Symbol            | Min | Max | Min | Max | Units |

| T <sub>RLRH</sub> | 125 |     | 125 |     | ns    |

| T <sub>WLWH</sub> | 125 |     | 125 |     | ns    |

| T <sub>RLDV</sub> |     | 95  |     | 95  | ns    |

| T <sub>RHDX</sub> | 0   |     | 0   |     | ns    |

| T <sub>RHDZ</sub> |     | 25  |     | 25  | ns    |

| T <sub>LLDV</sub> |     | 155 |     | 155 | ns    |

| T <sub>AVDV</sub> |     | 160 |     | 160 | ns    |

| T <sub>LLWL</sub> | 45  | 105 | 45  | 105 | ns    |

| T <sub>AVWL</sub> | 70  |     | 70  |     | ns    |

| T <sub>QVWX</sub> | 5   |     | 5   |     | ns    |

| T <sub>QVWH</sub> | 155 |     | 155 |     | ns    |

| T <sub>WHQX</sub> | 10  |     | 10  |     | ns    |

| T <sub>RLAZ</sub> | 0   |     | 0   |     | ns    |

| T <sub>WHLH</sub> | 5   | 45  | 5   | 45  | ns    |

Table 98.

AC Parameters for a Fix Clock

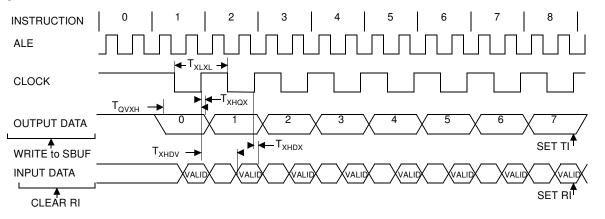

# Shift Register Timing Waveforms

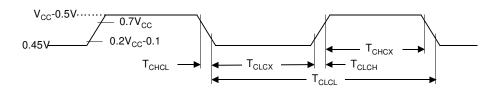

# External Clock Drive Waveforms

# AC Testing Input/Output Waveforms

INPUT/OUTPUT

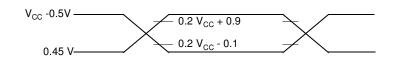

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

### **Float Waveforms**

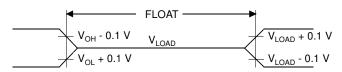

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

#### **Clock Waveforms**

Valid in normal clock mode. In X2 mode XTAL2 must be changed to XTAL2/2.