Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ic2-slrim |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 10. Two-Wire Interface Controller SFRs

| Mnemonic | Add | Name                       | 7     | 6    | 5     | 4     | 3    | 2    | 1     | 0     |

|----------|-----|----------------------------|-------|------|-------|-------|------|------|-------|-------|

| SSCON    | 93h | Synchronous Serial control | SSCR2 | SSPE | SSSTA | SSSTO | SSI  | SSAA | SSCR1 | SSCR0 |

| SSCS     | 94h | Synchronous Serial Status  | SSC4  | SSC3 | SSC2  | SSC1  | SSC0 | 0    | 0     | 0     |

| SSDAT    | 95h | Synchronous Serial Data    | SSD7  | SSD6 | SSD5  | SSD4  | SSD3 | SSD2 | SSD1  | SSD0  |

| SSADR    | 96h | Synchronous Serial Address | SSA7  | SSA6 | SSA5  | SSA4  | SSA3 | SSA2 | SSA1  | SSGC  |

### Table 11. Keyboard Interface SFRs

| Mnemonic | Add | Name                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| KBLS     | 9Ch | Keyboard Level Selector | KBLS7 | KBLS6 | KBLS5 | KBLS4 | KBLS3 | KBLS2 | KBLS1 | KBLS0 |

| KBE      | 9Dh | Keyboard Input Enable   | KBE7  | KBE6  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  |

| KBF      | 9Eh | Keyboard Flag Register  | KBF7  | KBF6  | KBF5  | KBF4  | KBF3  | KBF2  | KBF1  | KBF0  |

• It is always possible to switch dynamically by software from OscA to OscB, and vice versa by changing CKS bit.

Idle Modes

- IDLE modes are achieved by using any instruction that writes into PCON.0 bit (IDL)

- IDLE modes A and B depend on previous software sequence, prior to writing into PCON.0 bit:

- IDLE MODE A: OscA is running (OscAEn = 1) and selected (CKS = 1)

- IDLE MODE B: OscB is running (OscBEn = 1) and selected (CKS = 0)

- The unused oscillator OscA or OscB can be stopped by software by clearing OscAEn or OscBEn respectively.

- IDLE mode can be canceled either by Reset, or by activation of any enabled interruption

- In both cases, PCON.0 bit (IDL) is cleared by hardware

- Exit from IDLE modes will leave Oscillators control bits (OscEnA, OscEnB, CKS) unchanged.

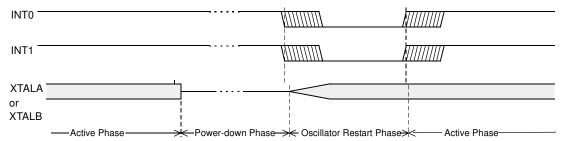

- Power Down Modes

POWER DOWN modes are achieved by using any instruction that writes into PCON.1 bit (PD)

- POWER DOWN modes A and B depend on previous software sequence, prior to writing into PCON.1 bit:

- Both OscA and OscB will be stopped.

- POWER DOWN mode can be cancelled either by a hardware Reset, an external interruption, or the keyboard interrupt.

- By Reset signal: The CPU will restart according to OSC bit in Hardware Security Bit (HSB) register.

- By INT0 or INT1 interruption, if enabled: (standard behavioral), request on Pads must be driven low enough to ensure correct restart of the oscillator which was selected when entering in Power down.

- By keyboard Interrupt if enabled: a hardware clear of the PCON.1 flag ensure the restart of the oscillator which was selected when entering in Power down.

Table 18. Overview

| PCON.1 | PCON.0 | OscBEn | OscAEn | CKS | Selected Mode                  | Comment                                                     |

|--------|--------|--------|--------|-----|--------------------------------|-------------------------------------------------------------|

| 0      | 0      | 0      | 1      | 1   | NORMAL MODE<br>A, OscB stopped | Default mode after power-up or<br>Warm Reset                |

| 0      | 0      | 1      | 1      | 1   | NORMAL MODE<br>A, OscB running | Default mode after power-up or<br>Warm Reset + OscB running |

| 0      | 0      | 1      | 0      | 0   | NORMAL MODE<br>B, OscA stopped | OscB running and selected                                   |

| 0      | 0      | 1      | 1      | 0   | NORMAL MODE<br>B, OscA running | OscB running and selected +<br>OscA running                 |

| х      | х      | 0      | 0      | х   | INVALID                        | OscA & OscB cannot be stopped at the same time              |

| х      | х      | х      | 0      | 1   | INVALID                        | OscA must not be stopped, as used for CPU and peripherals   |

| х      | х      | 0      | х      | 0   | INVALID                        | OscB must not be stopped as used for CPU and peripherals    |

## Enhanced Features

In comparison to the original 80C52, the AT89C51IC2 implements some new features, which are:

- The X2 option

- The Dual Data Pointer

- The extended RAM

- The Programmable Counter Array (PCA)

- The Hardware Watchdog

- The SPI interface

- The 2-wire interface

- The 4 level interrupt priority system

- The power-off flag

- The Power On Reset

- The ONCE mode

- The ALE disabling

- Some enhanced features are also located in the UART and the timer 2

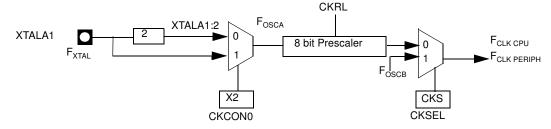

### X2 Feature and OSCA Clock Generation

The AT89C51IC2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTALA1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

The clock for the whole circuit and peripherals is first divided by two before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTALA1 input. In X2 mode, as this divider is bypassed, the signals on XTALA1 must have a cyclic ratio between 40 to 60%.

Figure 5. shows the clock generation block diagram.x2 bit is validated on the rising edge of the XTALA1÷2 to avoid glitches when switching from X2 to STD mode. Figure 6. shows the switching mode waveforms.

### Figure 5. Clock Generation Diagram

Description

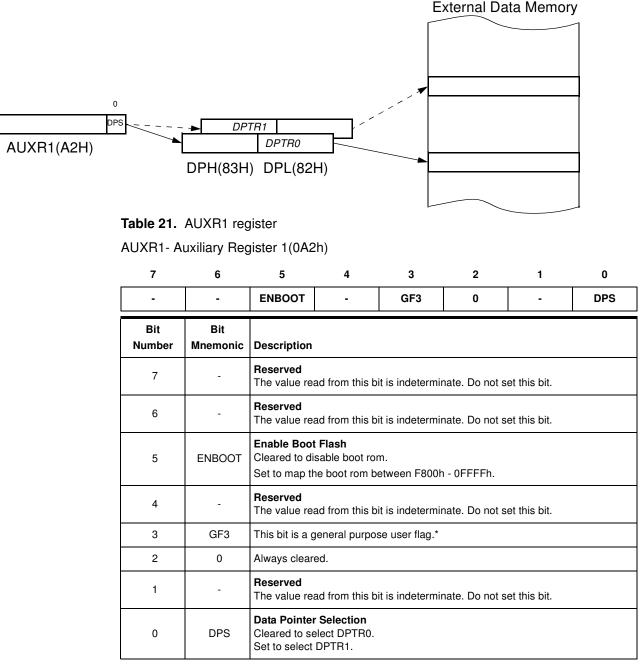

## Dual Data Pointer Register

The additional data pointer can be used to speed up code execution and reduce code size.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1.0 (see Table 21) that allows the program code to switch between them (Refer to Figure 7).

### Figure 7. Use of Dual Pointer

7

Reset Value: XXXX XX0X0b Not bit addressable

Note: \*Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.

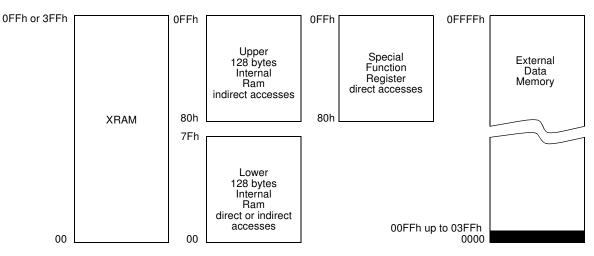

## Expanded RAM (XRAM)

The AT89C51IC2 provides additional Bytes of random access memory (RAM) space for increased data parameter handling and high level language usage.

AT89C51IC2 devices have expanded RAM in external data space; maximum size and location are described in Table 22.

Table 22. Expanded RAM

|            |           | Addre | ess  |

|------------|-----------|-------|------|

|            | XRAM size | Start | End  |

| AT89C51IC2 | 1024      | 00h   | 3FFh |

The AT89C51IC2 has internal data memory that is mapped into four separate segments.

The four segments are:

1. The Lower 128 bytes of RAM (addresses 00h to 7Fh) are directly and indirectly addressable.

2. The Upper 128 bytes of RAM (addresses 80h to FFh) are indirectly addressable only.

3. The Special Function Registers, SFRs, (addresses 80h to FFh) are directly address-able only.

4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register (see Table 22)

The lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

### Figure 8. Internal and External Data Memory Address

When an instruction accesses an internal location above address 7Fh, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction.

Instructions that use direct addressing access SFR space. For example: MOV 0A0H, # data, accesses the SFR at location 0A0h (which is P2).

### Table 27. CCON Register

CCON - PCA Counter Control Register (D8h)

| 7             | 6               | 5                               | 4                                                                                                                                                                                                                  | 3    | 2          | 1    | 0    |  |  |  |  |

|---------------|-----------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|------|------|--|--|--|--|

| CF            | CR              | -                               | CCF4                                                                                                                                                                                                               | CCF3 | CCF2       | CCF1 | CCF0 |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                                                                                                                                                    |      |            |      |      |  |  |  |  |

| 7             | CF              | Set by hardw<br>CMOD is set     | PCA Counter Overflow flag<br>Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in<br>CMOD is set. CF<br>may be set by either hardware or software but can only be cleared by software. |      |            |      |      |  |  |  |  |

| 6             | CR              | Must be clea                    | PCA Counter Run control bit<br>Must be cleared by software to turn the PCA counter off.<br>Set by software to turn the PCA counter on.                                                                             |      |            |      |      |  |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                    |      |            |      |      |  |  |  |  |

| 4             | CCF4            | Must be clea                    | <b>e 4 interrupt</b><br>ared by softwa<br>vare when a n                                                                                                                                                            | -    | re occurs. |      |      |  |  |  |  |

| 3             | CCF3            | Must be clea                    | <b>e 3 interrupt</b><br>ared by softwa<br>vare when a n                                                                                                                                                            |      | re occurs. |      |      |  |  |  |  |

| 2             | CCF2            | Must be clea                    | <b>e 2 interrupt</b><br>ared by softwa<br>vare when a n                                                                                                                                                            | •    | re occurs. |      |      |  |  |  |  |

| 1             | CCF1            | Must be clea                    | PCA Module 1 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                     |      |            |      |      |  |  |  |  |

| 0             | CCF0            | Must be clea                    | e 0 interrupt<br>ared by softwa<br>vare when a n                                                                                                                                                                   |      | re occurs. |      |      |  |  |  |  |

Reset Value = 00X0 0000b Not bit addressable

The watchdog timer function is implemented in module 4 (See Figure 14).

The PCA interrupt system is shown in Figure 12.

Table 28 shows the CCAPMn settings for the various PCA functions.

- Table 28.

CCAPMn Registers (n = 0-4)

- CCAPM0 PCA Module 0 Compare/Capture Control Register (0DAh)

- CCAPM1 PCA Module 1 Compare/Capture Control Register (0DBh)

- CCAPM2 PCA Module 2 Compare/Capture Control Register (0DCh)

- CCAPM3 PCA Module 3 Compare/Capture Control Register (0DDh)

- CCAPM4 PCA Module 4 Compare/Capture Control Register (0DEh)

| 7             | 6               | 5                               | 4                                                                                                          | 3                                              | 2                | 1          | 0     |  |  |  |  |

|---------------|-----------------|---------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------|------------|-------|--|--|--|--|

| -             | ECOMn           | CAPPn                           | CAPNn                                                                                                      | MATn                                           | TOGn             | PWMn       | ECCFn |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                                            |                                                |                  |            |       |  |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value re | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                     |                                                |                  |            |       |  |  |  |  |

| 6             | ECOMn           | Cleared to di                   | Enable Comparator<br>Cleared to disable the comparator function.<br>Set to enable the comparator function. |                                                |                  |            |       |  |  |  |  |

| 5             | CAPPn           | Cleared to di                   | apture Positive<br>leared to disable positive edge capture.<br>et to enable positive edge capture.         |                                                |                  |            |       |  |  |  |  |

| 4             | CAPNn           | Cleared to di                   | Capture Negative<br>Cleared to disable negative edge capture.<br>Set to enable negative edge capture.      |                                                |                  |            |       |  |  |  |  |

| 3             | MATn            | compare/cap                     | oture register                                                                                             | of the PCA co<br>causes the<br>et, flagging an |                  | s module's |       |  |  |  |  |

| 2             | TOGn            |                                 | oture register of                                                                                          | of the PCA co<br>causes the                    | ounter with this | s module's |       |  |  |  |  |

| 1             | PWMn            | Cleared to di                   |                                                                                                            | Xn pin to be u                                 | •                |            |       |  |  |  |  |

| 0             | CCF0            | Cleared to di<br>an interrupt.  | Set to enable compare/capture flag CCFn in the CCON register to generate an                                |                                                |                  |            |       |  |  |  |  |

Reset Value = X000 0000b Not bit addressable

### Table 37. SCON Register

SCON - Serial Control Register (98h)

| 7             | 6               | 5                              | 4                                                                                                                                                                                                                                                                 | 3                            | 2                                                     | 1       | 0              |  |  |  |  |

|---------------|-----------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------|---------|----------------|--|--|--|--|

| FE/SM0        | SM1             | SM2                            | REN                                                                                                                                                                                                                                                               | TB8                          | RB8                                                   | ті      | RI             |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptior                    | Description                                                                                                                                                                                                                                                       |                              |                                                       |         |                |  |  |  |  |

| 7             | FE              | Clear to res<br>Set by hard    | ware when an                                                                                                                                                                                                                                                      | ate, not cleare              | ed by a valid s<br>bit is detected.<br>to the FE bit. |         |                |  |  |  |  |

|               | SM0             | Refer to SM                    | Serial port Mode bit 0<br>Refer to SM1 for serial port mode selection.<br>SMOD0 must be cleared to enable access to the SM0 bit.                                                                                                                                  |                              |                                                       |         |                |  |  |  |  |

| 6             | SM1             |                                | <ul> <li>0 Shift Register F<sub>XTAL</sub>/12 (or F<sub>XTAL</sub> /6 in mode X2)</li> <li>1 8-bit UART Variable</li> <li>0 9-bit UART F<sub>XTAL</sub>/64 or F<sub>XTAL</sub>/32</li> </ul>                                                                      |                              |                                                       |         |                |  |  |  |  |

| 5             | SM2             | Clear to disa<br>Set to enable | Serial port Mode 2 bit / Multiprocessor Communication Enable bit<br>Clear to disable multiprocessor communication feature.<br>Set to enable multiprocessor communication feature in mode 2 and 3, and<br>eventually mode 1. This bit should be cleared in mode 0. |                              |                                                       |         |                |  |  |  |  |

| 4             | REN             |                                | <b>Enable bit</b><br>able serial rec<br>le serial recep                                                                                                                                                                                                           |                              |                                                       |         |                |  |  |  |  |

| 3             | TB8             | o transmit a                   | r <b>Bit 8</b> / <b>Ninth</b><br>logic 0 in the<br>mit a logic 1 ir                                                                                                                                                                                               | 9th bit.                     | nit in modes 2                                        | 2 and 3 |                |  |  |  |  |

| 2             | RB8             | Cleared by Set by hard         | hardware if 9t<br>ware if 9th bit                                                                                                                                                                                                                                 | h bit received received is a |                                                       | -       | 3 is not used. |  |  |  |  |

| 1             | TI              | Clear to ack<br>Set by hard    | Transmit Interrupt flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of<br>the stop bit in the other modes.                                                                                 |                              |                                                       |         |                |  |  |  |  |

| 0             | RI              | Clear to ack<br>Set by hard    | <b>Receive Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0, see Figure 18. and<br>Figure 19. in the other modes.                                                                                |                              |                                                       |         |                |  |  |  |  |

Reset Value = 0000 0000b

Bit addressable

### Figure 25. Power-down Exit Waveform

Exit from Power-down by reset redefines all the SFRs, exit from Power-down by external interrupt does no affect the SFRs.

Exit from Power-down by either reset or external interrupt does not affect the internal RAM content.

Note: If idle mode is activated with Power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

Table 55 shows the state of ports during idle and power-down modes.

### Table 55. State of Ports

| Mode       | Program Memory | ALE | PSEN | PORT0                    | PORT1     | PORT2     | PORT3     |

|------------|----------------|-----|------|--------------------------|-----------|-----------|-----------|

| Idle       | Internal       | 1   | 1    | Port Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Idle       | External       | 1   | 1    | Floating                 | Port Data | Address   | Port Data |

| Power Down | Internal       | 0   | 0    | Port Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Power Down | External       | 0   | 0    | Floating                 | Port Data | Port Data | Port Data |

Port 0 can force a 0 level. A "one" will leave port floating.

### **Functional Description**

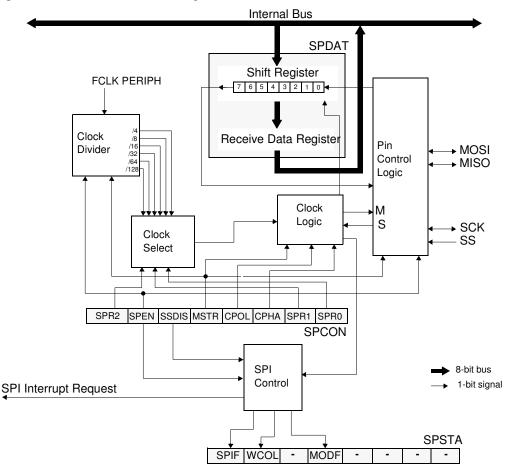

Figure 27 shows a detailed structure of the SPI Module.

Figure 27. SPI Module Block Diagram

### **Operating Modes**

The Serial Peripheral Interface can be configured in one of the two modes: Master mode or Slave mode. The configuration and initialization of the SPI Module is made through one register:

• The Serial Peripheral Control register (SPCON)

Once the SPI is configured, the data exchange is made using:

- SPCON

- The Serial Peripheral STAtus register (SPSTA)

- The Serial Peripheral DATa register (SPDAT)

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (SCK) synchronizes shifting and sampling on the two serial data lines (MOSI and MISO). A Slave Select line (SS) allows individual selection of a Slave SPI device; Slave devices that are not selected do not interfere with SPI bus activities.

When the Master device transmits data to the Slave device via the MOSI line, the Slave device responds by sending data to the Master device via the MISO line. This implies full-duplex transmission with both data out and data in synchronized with the same clock (Figure 28).

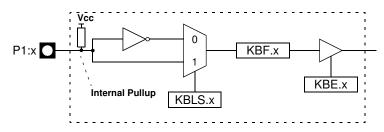

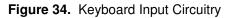

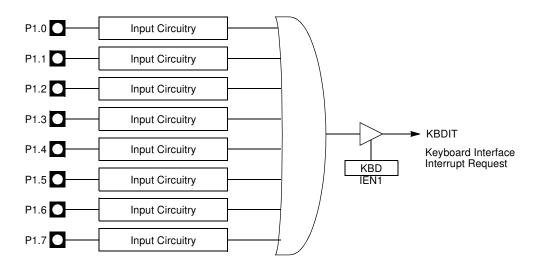

## **Keyboard Interface**

The AT89C51IC2 implements a keyboard interface allowing the connection of a 8 x n matrix keyboard. It is based on 8 inputs with programmable interrupt capability on both high or low level. These inputs are available as alternate function of P1 and allow to exit from idle and power down modes.

The keyboard interface interfaces with the C51 core through 3 special function registers: KBLS, the Keyboard Level Selection register (Table 63), KBE, The Keyboard interrupt Enable register (Table 62), and KBF, the Keyboard Flag register (Table 61).

Interrupt

The keyboard inputs are considered as 8 independent interrupt sources sharing the same interrupt vector. An interrupt enable bit (KBD in IEN1) allows global enable or disable of the keyboard interrupt (see Figure 33). As detailed in Figure 34 each keyboard input has the capability to detect a programmable level according to KBLS.x bit value. Level detection is then reported in interrupt flags KBF.x that can be masked by software using KBE.x bits.

This structure allow keyboard arrangement from 1 by n to 8 by n matrix and allow usage of P1 inputs for other purpose.

### Figure 33. Keyboard Interface Block Diagram

### **Power Reduction Mode**

P1 inputs allow exit from idle and power down modes as detailed in Section "Power Management", page 67.

## Table 63. KBLS Register

KBLS-Keyboard Level Selector Register (9Ch)

| 7             | 6               | 5             | 4                                                                                                                                                             | 3                                                  | 2                               | 1     | 0     |  |  |  |

|---------------|-----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------|-------|-------|--|--|--|

| KBLS7         | KBLS6           | KBLS5         | KBLS4                                                                                                                                                         | KBLS3                                              | KBLS2                           | KBLS1 | KBLS0 |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description   | Description                                                                                                                                                   |                                                    |                                 |       |       |  |  |  |

| 7             | KBLS7           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on F |                                 |       |       |  |  |  |

| 6             | KBLS6           | Cleared to en | eyboard line 6 Level Selection bit<br>eared to enable a low level detection on Port line 6.<br>et to enable a high level detection on Port line 6.            |                                                    |                                 |       |       |  |  |  |

| 5             | KBLS5           | Cleared to en | <b>Ceyboard line 5 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 5.<br>Set to enable a high level detection on Port line 5. |                                                    |                                 |       |       |  |  |  |

| 4             | KBLS4           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection o<br>detection on F  |                                 |       |       |  |  |  |

| 3             | KBLS3           | Cleared to en |                                                                                                                                                               |                                                    | on Port line 3.<br>Port line 3. |       |       |  |  |  |

| 2             | KBLS2           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on F |                                 |       |       |  |  |  |

| 1             | KBLS1           | Cleared to en | Keyboard line 1 Level Selection bit<br>Cleared to enable a low level detection on Port line 1.<br>Set to enable a high level detection on Port line 1.        |                                                    |                                 |       |       |  |  |  |

| 0             | KBLS0           | Cleared to en | Keyboard line 0 Level Selection bit<br>Cleared to enable a low level detection on Port line 0.<br>Set to enable a high level detection on Port line 0.        |                                                    |                                 |       |       |  |  |  |

Reset Value= 0000 0000b

## AT89C51IC2

### Table 80. WDTPRG Register

WDTPRG - Watchdog Timer Out Register (0A7h)

| 7             | 6               | 5                                                     | 4                                                                                                                                                            | 3                                                                                                                                                         | 2                                                                                                                                                                                                                                             | 1                                                       | 0  |  |  |  |  |

|---------------|-----------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----|--|--|--|--|

| -             | -               | -                                                     | -                                                                                                                                                            | -                                                                                                                                                         | S2                                                                                                                                                                                                                                            | S1                                                      | S0 |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                           |                                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                                                                                               |                                                         |    |  |  |  |  |

| 7             | -               |                                                       |                                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                                                                                               |                                                         |    |  |  |  |  |

| 6             | -               |                                                       |                                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                                                                                               |                                                         |    |  |  |  |  |

| 5             | -               | Reserved<br>The value rea                             | ad from this bi                                                                                                                                              | t is undetermi                                                                                                                                            | ned. Do not try                                                                                                                                                                                                                               | y to set this bit                                       | t. |  |  |  |  |

| 4             | -               |                                                       |                                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                                                                                               |                                                         |    |  |  |  |  |

| 3             | -               |                                                       |                                                                                                                                                              |                                                                                                                                                           |                                                                                                                                                                                                                                               |                                                         |    |  |  |  |  |

| 2             | S2              | WDT Time-o                                            | out select bit                                                                                                                                               | 2                                                                                                                                                         |                                                                                                                                                                                                                                               |                                                         |    |  |  |  |  |

| 1             | S1              | WDT Time-o                                            | out select bit                                                                                                                                               | 1                                                                                                                                                         |                                                                                                                                                                                                                                               |                                                         |    |  |  |  |  |

| 0             | S0              | WDT Time-o                                            | out select bit                                                                                                                                               | 0                                                                                                                                                         |                                                                                                                                                                                                                                               |                                                         |    |  |  |  |  |

|               |                 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 2 <sup>15</sup> - 1) machir<br>- 1) machine c<br>2 <sup>17</sup> - 1) machir<br>2 <sup>18</sup> - 1) machir<br>- 1) machine c<br>2 <sup>20</sup> - 1) machir | -out<br>ne cycles, 16. :<br>ne cycles, 32.7<br>cycles, 65.5 m<br>ne cycles, 131<br>ne cycles, 262<br>cycles, 542 ms<br>ne cycles, 1.05<br>ne cycles, 2.09 | $7 \text{ ms } @ \text{F}_{OSCA}$<br>$1 \text{ ms } @ \text{F}_{OSCA} = 1$<br>$1 \text{ ms } @ \text{F}_{OSCA} =$<br>$1 \text{ ms } @ \text{F}_{OSCA} = 12$<br>$2 \text{ s } @ \text{F}_{OSCA} = 12$<br>$2 \text{ s } @ \text{F}_{OSCA} = 12$ | =12 MHz<br>2 MHz<br>=12 MHz<br>=12 MHz<br>MHz<br>12 MHz |    |  |  |  |  |

Reset value XXXX X000

# WDT During Power Down and Idle

In Power Down mode the oscillator stops, which means the WDT also stops. While in Power Down mode the user does not need to service the WDT. There are 2 methods of exiting Power Down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power Down mode. When Power Down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the AT89C51IC2 is reset. Exiting Power Down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is better to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the AT89C51IC2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

## **Power-off Flag**

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (Table 81). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

### Table 81. PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                                             | 4                                                                                                               | 3                             | 2               | 1             | 0              |  |  |  |

|---------------|-----------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|---------------|----------------|--|--|--|

| SMOD1         | SMOD0           | -                                             | POF                                                                                                             | GF1                           | GF0             | PD            | IDL            |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   |                                                                                                                 |                               |                 |               |                |  |  |  |

| 7             | SMOD1           | Serial port I<br>Set to select                |                                                                                                                 | rate in mode 1                | , 2 or 3.       |               |                |  |  |  |

| 6             | SMOD0           | Cleared to se                                 | Serial port Mode bit 0<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register. |                               |                 |               |                |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value re               | ad from this b                                                                                                  | it is indetermir              | nate. Do not se | et this bit.  |                |  |  |  |

| 4             | POF             |                                               | cognize next                                                                                                    |                               | o its nominal v | oltage. Can a | llso be set by |  |  |  |

| 3             | GF1             |                                               |                                                                                                                 | Il purpose usa<br>pose usage. | ge.             |               |                |  |  |  |

| 2             | GF0             |                                               |                                                                                                                 | Il purpose usa<br>pose usage. | ge.             |               |                |  |  |  |

| 1             | PD              | Cleared by h                                  | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                  |                               |                 |               |                |  |  |  |

| 0             | IDL             | Idle mode b<br>Cleared by h<br>Set to enter i | ardware wher                                                                                                    | n interrupt or re             | eset occurs.    |               |                |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

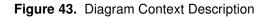

## **Bootloader Architecture**

Introduction

The bootloader manages a communication according to a specific defined protocol to provide the whole access and service on Flash memory. Furthermore, all accesses and routines can be called from the user application.

Acronyms

ISP: In-system Programming SBV: Software Boot Vector BSB: Boot Status Byte SSB: Software Security Bit HW : Hardware Byte

## **ISP Protocol Description**

### **Physical Layer**

The UART used to transmit information has the following configuration:

- Character: 8-bit data

- Parity: none

- Stop: 1 bit

- Flow control: none

- Baud rate: autobaud is performed by the bootloader to compute the baud rate choosen by the host.

### **Frame Description** The Serial Protocol is based on the Intel Hex-type records.

Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below.

### Table 89. Intel Hex Type Frame

| Record Mark ':' | Reclen | Load Offset | Record Type | Data or Info | Checksum |

|-----------------|--------|-------------|-------------|--------------|----------|

| 1 byte          | 1 byte | 2 bytes     | 1 bytes     | n byte       | 1 byte   |

- Record Mark:

- Record Mark is the start of frame. This field must contain ':'.

- Reclen:

- Reclen specifies the number of Bytes of information or data which follows the Record Type field of the record.

- Load Offset:

- Load Offset specifies the 16-bit starting load offset of the data Bytes, therefore this field is used only for

- Data Program Record (see Section "ISP Commands Summary").

- Record Type:

- Record Type specifies the command type. This field is used to interpret the remaining information within the frame. The encoding for all the current record types is described in Section "ISP Commands Summary".

- Data/Info:

- Data/Info is a variable length field. It consists of zero or more Bytes encoded as pairs of hexadecimal digits. The meaning of data depends on the Record Type.

- Checksum:

- The two's complement of the 8-bit Bytes that result from converting each pair of ASCII hexadecimal digits to one Byte of binary, and including the Reclen field to and including the last Byte of the Data/Info field. Therefore, the sum of all the ASCII pairs in a record after converting to binary, from the Reclen field to and including the Checksum field, is zero.

|                              |                                                                                                                                                                                                 | R                                                         |                             |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------|--|--|

| Full Chip Erase              | <ul> <li>The ISP command "Full Chip Erast some Bytes used by the boot</li> <li>BSB = FFh</li> <li>SBV = FCh</li> <li>SSB = FFh and finally erase the full Chip Erast does not affect</li> </ul> | loader at their default valu<br>ne Software Security Bits |                             |  |  |

| Checksum Error               | When a checksum error is detecte                                                                                                                                                                | d send 'X' followed with C                                | R&LF.                       |  |  |

| Flow Description             |                                                                                                                                                                                                 |                                                           |                             |  |  |

| Overview                     | An initialization step must be performed after each Reset. After microcontroller reset, the bootloader waits for an autobaud sequence (see section 'autobaud performance').                     |                                                           |                             |  |  |

|                              | When the communication is initialized the protocol depends on the record type requested by the host.                                                                                            |                                                           |                             |  |  |

|                              | FLIP, a software utility to impleme<br>Atmel the web site.                                                                                                                                      | ent ISP programming with                                  | a PC, is available from the |  |  |

| Communication Initialization | The host initializes the communication by sending a 'U' character to help the bootloader to compute the baudrate (autobaud).                                                                    |                                                           |                             |  |  |

|                              | Figure 47. Initialization<br><u>Host</u>                                                                                                                                                        |                                                           | <u>Bootloader</u>           |  |  |

|                              | Init Communication                                                                                                                                                                              | "U" <b>&gt;</b>                                           | Performs Autobaud           |  |  |

|                              | If (not received "U")<br>Else<br>Communication Opened                                                                                                                                           | <b>≺</b> "U"                                              | Sends Back 'U' Character    |  |  |

MEI

## Example

| Programming  | Data (write 55h at address 0010h in the Flash) |

|--------------|------------------------------------------------|

| HOST         | : 01 0010 00 55 9A                             |

| BOOTLOADER   | : 01 0010 00 55 9A . CR LF                     |

| Programming  | Atmel function (write SSB to level 2)          |

| HOST         | : 02 0000 03 05 01 F5                          |

| BOOTLOADER   | : 02 0000 03 05 01 F5. CR LF                   |

| Writing Fram | me (write BSB to 55h)                          |

| HOST         | : 03 0000 03 06 00 55 9F                       |

| BOOTLOADER   | : 03 0000 03 06 00 55 9F . CR LF               |

| HOST         | : 03 0000 03 06 00 55 9F                       |

### **API Call Description**

Several Application Program Interface (API) calls are available for use by an application program to permit selective erasing and programming of Flash pages. All calls are made through a common interface, PGM\_MTP. The programming functions are selected by setting up the microcontroller's registers before making a call to PGM\_MTP at FFF0h. Results are returned in the registers.

When several Bytes have to be programmed, it is highly recommended to use the Atmel API "PROGRAM DATA PAGE" call. Indeed, this API call writes up to 128 Bytes in a single command.

All routines for software access are provided in the C Flash driver available at Atmel's web site.

The API calls description and arguments are shown in Table 93.

### Table 93. API Call Summary

| Command         | R1  | Α                | DPTR0                            | DPTR1 | Returned Value           | Command Effect                                                                |

|-----------------|-----|------------------|----------------------------------|-------|--------------------------|-------------------------------------------------------------------------------|

| READ MANUF ID   | 00h | XXh              | 0000h                            | XXh   | ACC = Manufacturer<br>Id | Read Manufacturer identifier                                                  |

| READ DEVICE ID1 | 00h | XXh              | 0001h                            | XXh   | ACC = Device Id 1        | Read Device identifier 1                                                      |

| READ DEVICE ID2 | 00h | XXh              | 0002h                            | XXh   | ACC = Device Id 2        | Read Device identifier 2                                                      |

| READ DEVICE ID3 | 00h | XXh              | 0003h                            | XXh   | ACC = Device Id 3        | Read Device identifier 3                                                      |

|                 |     | XXh              | DPH = 00h                        | 00h   | ACC = DPH                | Erase block 0                                                                 |

|                 |     |                  | DPH = 20h                        |       |                          | Erase block 1                                                                 |

|                 |     |                  | DPH = 40h                        |       |                          | Erase block 2                                                                 |

| ERASE BLOCK     | 01h |                  | Address of<br>byte to<br>program |       |                          | Program one Data Byte in user Flash                                           |

|                 |     |                  | XXh                              |       |                          | Erase Software boot vector and boot status<br>byte. (SBV = FCh and BSB = FFh) |

|                 | 05h | XXh              | DPH = 00h<br>DPL = 00h           | - 00h | ACC = SSB value          | Set SSB level 1                                                               |

| PROGRAM SSB     |     |                  | DPH = 00h<br>DPL = 01h           |       |                          | Set SSB level 2                                                               |

| FROGRAM 335     |     |                  | DPH = 00h<br>DPL = 10h           |       |                          | Set SSB level 0                                                               |

|                 |     |                  | DPH = 00h<br>DPL = 11h           |       |                          | Set SSB level 1                                                               |

| PROGRAM BSB     | 06h | New BSB<br>value | 0000h                            | XXh   | none                     | Program boot status byte                                                      |

| PROGRAM SBV     | 06h | New SBV<br>value | 0001h                            | XXh   | none                     | Program software boot vector                                                  |

| READ SSB        | 07h | XXh              | 0000h                            | XXh   | ACC = SSB                | Read Software Security Byte                                                   |

| READ BSB        | 07h | XXh              | 0001h                            | XXh   | ACC = BSB                | Read Boot Status Byte                                                         |

| READ SBV        | 07h | XXh              | 0002h                            | XXh   | ACC = SBV                | Read Software Boot Vector                                                     |

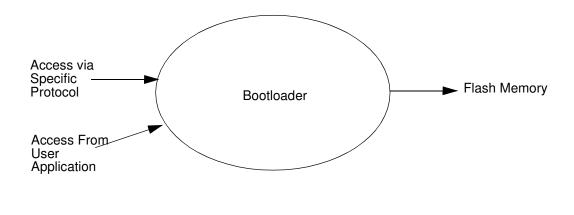

# Shift Register Timing Waveforms

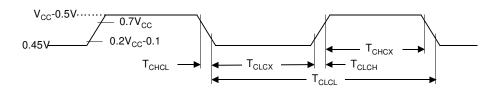

## External Clock Drive Waveforms

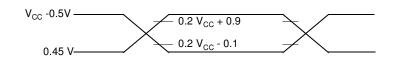

# AC Testing Input/Output Waveforms

INPUT/OUTPUT

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

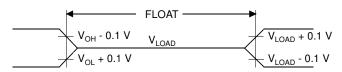

### **Float Waveforms**

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

### **Clock Waveforms**

Valid in normal clock mode. In X2 mode XTAL2 must be changed to XTAL2/2.