Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ic2-slsil |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Description

AT89C51IC2 is a high performance Flash version of the 80C51 8-bit microcontrollers. It contains a 32K bytes Flash memory block for program and data.

The 32K bytes Flash memory can be programmed either in parallel mode or in serial mode with the ISP capability or with software. The programming voltage is internally generated from the standard  $V_{CC}$  pin.

The AT89C51IC2 retains all features of the 80C52 with 256 bytes of internal RAM, a 10-source 4-level interrupt controller and three timer/counters.

In addition, the AT89C51IC2 has a 32 kHz Subsidiary clock Oscillator, a Programmable Counter Array, an XRAM of 1024 byte, a Hardware Watchdog Timer, a Keyboard Interface, a 2-wire interface, an SPI Interface, a more versatile serial channel that facilitates multiprocessor communication (EUART) and a speed improvement mechanism (X2 mode).

The fully static design of the AT89C51IC2 allows to reduce system power consumption by bringing the clock frequency down to any value, even DC, without loss of data.

The AT89C51IC2 has 2 software-selectable modes of reduced activity and 8-bit clock prescaler for further reduction in power consumption. In the Idle mode the CPU is frozen while the peripherals and the interrupt system are still operating. In the power-down mode the RAM is saved and all other functions are inoperative.

The added features of the AT89C51IC2 make it more powerful for applications that need pulse width modulation, high speed I/O and counting capabilities such as alarms, motor control, corded phones, smart card readers.

| PLCC44<br>VQFP44 1.4 | Flash (bytes) | XRAM (bytes) | TOTAL RAM<br>(bytes) | I/O |

|----------------------|---------------|--------------|----------------------|-----|

| T89C51IC2            | 32k           | 1024         | 1280                 | 34  |

### Table 5. Port SFRs

| Mnemonic | Add | Name         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|--------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0 |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1 |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2 |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3 |   |   |   |   |   |   |   |   |

### Table 6. Timer SFRs

| Mnemonic | Add | Name                                        | 7     | 6     | 5    | 4    | 3     | 2     | 1     | 0       |

|----------|-----|---------------------------------------------|-------|-------|------|------|-------|-------|-------|---------|

| TCON     | 88h | Timer/Counter 0 and 1 Control               | TF1   | TR1   | TF0  | TR0  | IE1   | IT1   | IE0   | IT0     |

| TMOD     | 89h | Timer/Counter 0 and 1 Modes                 | GATE1 | C/T1# | M11  | M01  | GATE0 | C/T0# | M10   | M00     |

| TL0      | 8Ah | Timer/Counter 0 Low Byte                    |       |       |      |      |       |       |       |         |

| TH0      | 8Ch | Timer/Counter 0 High Byte                   |       |       |      |      |       |       |       |         |

| TL1      | 8Bh | Timer/Counter 1 Low Byte                    |       |       |      |      |       |       |       |         |

| TH1      | 8Dh | Timer/Counter 1 High Byte                   |       |       |      |      |       |       |       |         |

| WDTRST   | A6h | WatchDog Timer Reset                        |       |       |      |      |       |       |       |         |

| WDTPRG   | A7h | WatchDog Timer Program                      | -     | -     | -    | -    | -     | WTO2  | WTO1  | WTO0    |

| T2CON    | C8h | Timer/Counter 2 control                     | TF2   | EXF2  | RCLK | TCLK | EXEN2 | TR2   | C/T2# | CP/RL2# |

| T2MOD    | C9h | Timer/Counter 2 Mode                        | -     | -     | -    | -    | -     | -     | T2OE  | DCEN    |

| RCAP2H   | CBh | Timer/Counter 2 Reload/Capture<br>High byte |       |       |      |      |       |       |       |         |

| RCAP2L   | CAh | Timer/Counter 2 Reload/Capture<br>Low byte  |       |       |      |      |       |       |       |         |

| TH2      | CDh | Timer/Counter 2 High Byte                   |       |       |      |      |       |       |       |         |

| TL2      | CCh | Timer/Counter 2 Low Byte                    |       |       |      |      |       |       |       |         |

### Table 7. PCA SFRs

| Mnemo<br>-nic | Add | Name                        | 7    | 6    | 5 | 4    | 3    | 2    | 1    | 0    |

|---------------|-----|-----------------------------|------|------|---|------|------|------|------|------|

| CCON          | D8h | PCA Timer/Counter Control   | CF   | CR   | - | CCF4 | CCF3 | CCF2 | CCF1 | CCF0 |

| CMOD          | D9h | PCA Timer/Counter Mode      | CIDL | WDTE | - | -    | -    | CPS1 | CPS0 | ECF  |

| CL            | E9h | PCA Timer/Counter Low byte  |      |      |   |      |      |      |      |      |

| СН            | F9h | PCA Timer/Counter High byte |      |      |   |      |      |      |      |      |

|                  | ®                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timer 2          | The Timer 2 in the AT89C51IC2 is the standard C52 the Timer 2.<br>It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2<br>and TL2 are cascaded. It is controlled by T2CON (Table 24) and T2MOD (Table 25)<br>registers. Timer 2 operation is similar to Timer 0 and Timer 1. C/T2 selects $F_{OSC}/12$<br>(timer operation) or external pin T2 (counter operation) as the timer clock input. Setting<br>TR2 allows TL2 to be incremented by the selected input. |

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud <u>Rate</u> Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).                                                                                                                                                                                                                                                                                                                                       |

|                  | Refer to the Atmel 8-bit Microcontroller Hardware description for the description of Cap-<br>ture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                                                                                                       |

|                  | Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  | Auto-reload mode with up or down counter                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Auto-Reload Mode | The auto-reload mode configures timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, timer 2 behaves as in 80C52 (refer to the<br>Atmel 8-bit Microcontroller Hardware description). If DCEN bit is set, timer 2 acts as an<br>Up/down timer/counter as shown in Figure 9. In this mode the T2EX pin controls the<br>direction of count.                                                                                                            |

|                  | When T2EX is high, timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                                                                           |

|                  | When T2EX is low, timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                                                                        |

|                  | The EXF2 bit toggles when timer 2 overflows or underflows according to the direction of the count. EXE2 does not generate any interrupt. This bit can be used to provide 17 bit                                                                                                                                                                                                                                                                                                                        |

MEL

A

The EXF2 bit toggles when timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.

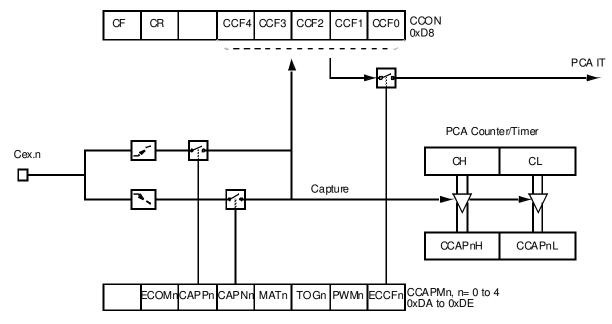

# PCA Capture Mode

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (Refer to Figure 13).

### Figure 13. PCA Capture Mode

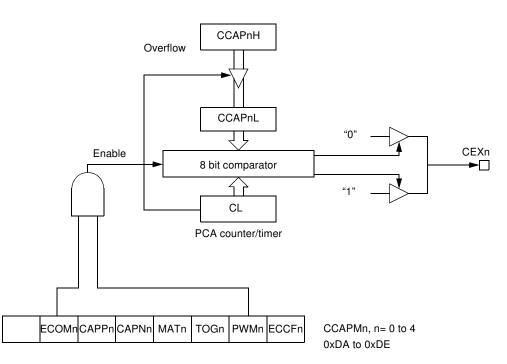

# 16-bit Software Timer/ Compare Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (See Figure 14).

Figure 16. PCA PWM Mode

**PCA Watchdog Timer** An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 14 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

1. periodically change the compare value so it will never match the PCA timer,

2. periodically change the PCA timer value so it will never match the compare values, or

3. disable the watchdog by clearing the WDTE bit before a match occurs and then reenable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

# Interrupt Sources and Vector Addresses

### Table 54. Interrupt Sources and Vector Addresses

| Number | Polling Priority | Interrupt Source | Interrupt<br>Request | Vector<br>Address |

|--------|------------------|------------------|----------------------|-------------------|

| 0      | 0                | Reset            |                      | 0000h             |

| 1      | 1                | INT0             | IE0                  | 0003h             |

| 2      | 2                | Timer 0          | TF0                  | 000Bh             |

| 3      | 3                | INT1             | IE1                  | 0013h             |

| 4      | 4                | Timer 1          | IF1                  | 001Bh             |

| 5      | 6                | UART             | RI+TI                | 0023h             |

| 6      | 7                | Timer 2          | TF2+EXF2             | 002Bh             |

| 7      | 5                | PCA              | CF + CCFn (n = 0-4)  | 0033h             |

| 8      | 8                | Keyboard         | KBDIT                | 003Bh             |

| 9      | 9                | TWI              | TWIIT                | 0043h             |

| 10     | 10               | SPI              | SPIIT                | 004Bh             |

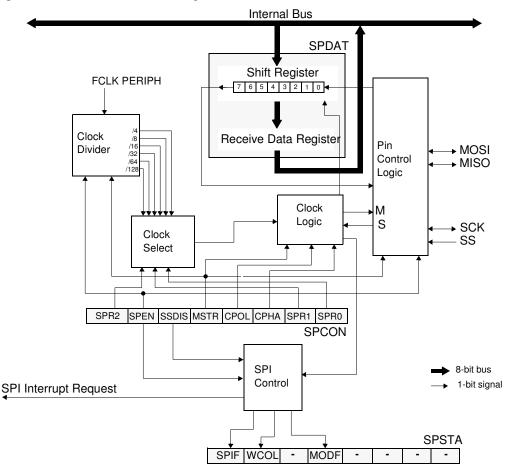

### **Functional Description**

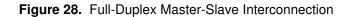

Figure 27 shows a detailed structure of the SPI Module.

Figure 27. SPI Module Block Diagram

### **Operating Modes**

The Serial Peripheral Interface can be configured in one of the two modes: Master mode or Slave mode. The configuration and initialization of the SPI Module is made through one register:

• The Serial Peripheral Control register (SPCON)

Once the SPI is configured, the data exchange is made using:

- SPCON

- The Serial Peripheral STAtus register (SPSTA)

- The Serial Peripheral DATa register (SPDAT)

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (SCK) synchronizes shifting and sampling on the two serial data lines (MOSI and MISO). A Slave Select line (SS) allows individual selection of a Slave SPI device; Slave devices that are not selected do not interfere with SPI bus activities.

When the Master device transmits data to the Slave device via the MOSI line, the Slave device responds by sending data to the Master device via the MISO line. This implies full-duplex transmission with both data out and data in synchronized with the same clock (Figure 28).

8-bit Shift register

MISO

MISC

8-bit Shift register

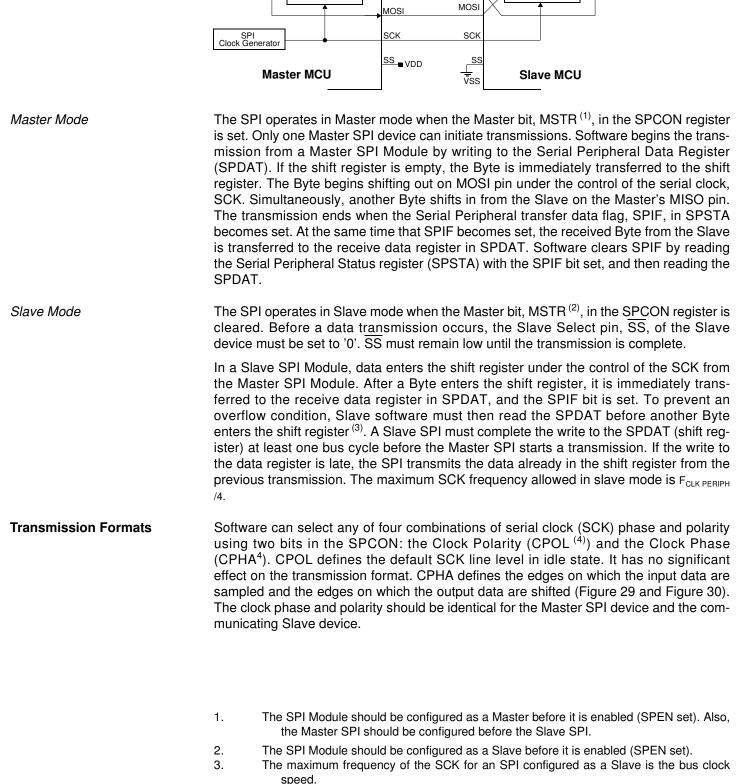

4. Before writing to the CPOL and CPHA bits, the SPI should be disabled (SPEN = '0').

74 **AT89C51IC2**

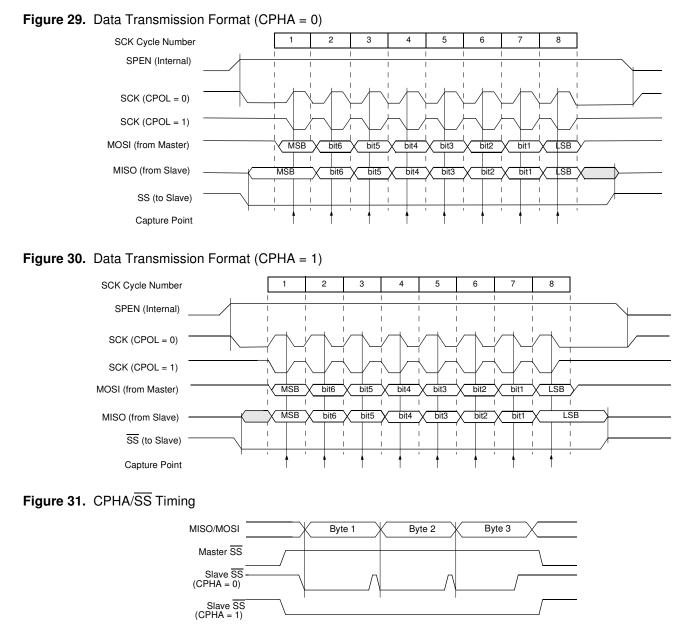

As shown in Figure 29, the first SCK edge is the MSB capture strobe. Therefore, the Slave must begin driving its data before the first SCK edge, and a falling edge on the  $\overline{SS}$  pin is used to start the transmission. The  $\overline{SS}$  pin must be toggled high and then low between each Byte transmitted (Figure 31).

Figure 30 shows an SPI transmission in which CPHA is '1'. In this case, the Master begins driving its MOSI pin on the first SCK edge. Therefore, the Slave uses the first SCK edge as a start transmission signal. The SS pin can remain low between transmissions (Figure 31). This format may be preffered in systems having only one Master and only one Slave driving the MISO data line.

## Table 63. KBLS Register

KBLS-Keyboard Level Selector Register (9Ch)

| 7             | 6               | 5             | 4                                                                                                                                                             | 3                                                  | 2                               | 1     | 0     |

|---------------|-----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------|-------|-------|

| KBLS7         | KBLS6           | KBLS5         | KBLS4                                                                                                                                                         | KBLS3                                              | KBLS2                           | KBLS1 | KBLS0 |

| Bit<br>Number | Bit<br>Mnemonic | Description   |                                                                                                                                                               |                                                    |                                 |       |       |

| 7             | KBLS7           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on F |                                 |       |       |

| 6             | KBLS6           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on F |                                 |       |       |

| 5             | KBLS5           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection on<br>detection on F |                                 |       |       |

| 4             | KBLS4           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection o<br>detection on F  |                                 |       |       |

| 3             | KBLS3           | Cleared to en |                                                                                                                                                               |                                                    | on Port line 3.<br>Port line 3. |       |       |

| 2             | KBLS2           | Cleared to en | Keyboard line 2 Level Selection bit<br>Cleared to enable a low level detection on Port line 2.<br>Set to enable a high level detection on Port line 2.        |                                                    |                                 |       |       |

| 1             | KBLS1           | Cleared to en | Keyboard line 1 Level Selection bit<br>Cleared to enable a low level detection on Port line 1.<br>Set to enable a high level detection on Port line 1.        |                                                    |                                 |       |       |

| 0             | KBLS0           | Cleared to en | <b>Keyboard line 0 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 0.<br>Set to enable a high level detection on Port line 0. |                                                    |                                 |       |       |

Reset Value= 0000 0000b

### Description

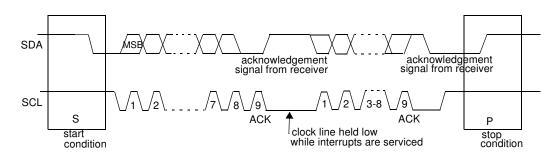

The CPU interfaces to the 2-wire logic via the following four 8-bit special function registers: the Synchronous Serial Control register (SSCON; Table 73), the Synchronous Serial Data register (SSDAT; Table 74), the Synchronous Serial Control and Status register (SSCS; Table 75) and the Synchronous Serial Address register (SSADR Table 78).

SSCON is used to enable SSLC, to program the bit rate (see Table 66), to enable slave modes, to acknowledge or not a received data, to send a START or a STOP condition on the 2-wire bus, and to acknowledge a serial interrupt. A hardware reset disables SSLC.

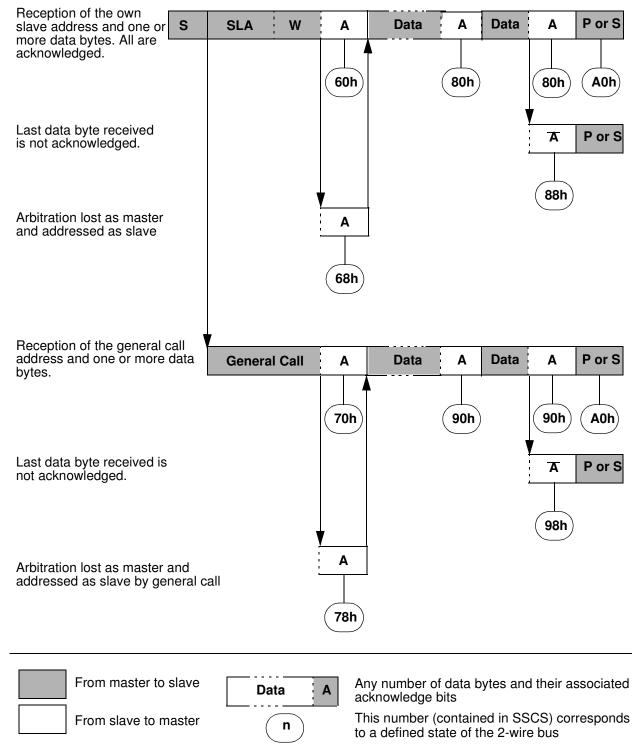

In write mode, SSCS is used to select the 2-wire interface and to select the bit rate source. In read mode, SSCS contains a status code which reflects the status of the 2-wire logic and the 2-wire bus. The three least significant bits are always zero. The five most significant bits contains the status code. There are 26 possible status codes. When SSCS contains F8h, no relevant state information is available and no serial interrupt is requested. A valid status code is available in SSCS one machine cycle after SI is set by hardware and is still present one machine cycle after SI has been reset by software. Table 68.to Table 72. give the status for the master modes and miscellaneous states.

SSDAT contains a byte of serial data to be transmitted or a byte which has just been received. It is addressable while it is not in process of shifting a byte. This occurs when 2-wire logic is in a defined state and the serial interrupt flag is set. Data in SSDAT remains stable as long as SI is set. While data is being shifted out, data on the bus is simultaneously shifted in; SSDAT always contains the last byte present on the bus.

SSADR may be loaded with the 7-bit slave address (7 most significant bits) to which SSLC will respond when programmed as a slave transmitter or receiver. The LSB is used to enable general call address (00h) recognition.

Figure 37 shows how a data transfer is accomplished on the 2-wire bus.

Figure 37. Complete data transfer on 2-wire bus

The four operating modes are:

- Master Transmitter

- Master Receiver

- Slave transmitter

- Slave receiver

Data transfer in each mode of operation is shown in Table 68 to Table 72 and Figure 38. to Figure 41.. These figures contain the following abbreviations:

S: START condition

R : Read bit (high level at SDA)

W: Write bit (low level at SDA)

A: Acknowledge bit (low level at SDA)

A: Not acknowledge bit (high level at SDA)

Data: 8-bit data byte

P : STOP condition

In Figure 38 to Figure 41, circles are used to indicate when the serial interrupt flag is set. The numbers in the circles show the status code held in SSCS. At these points, a service routine must be executed to continue or complete the serial transfer. These service routines are not critical since the serial transfer is suspended until the serial interrupt flag is cleared by software.

When the serial interrupt routine is entered, the status code in SSCS is used to branch to the appropriate service routine. For each status code, the required software action and details of the following serial transfer are given in Table 68 to Table 72.

Master Transmitter Mode In the master transmitter mode, a number of data bytes are transmitted to a slave receiver (Figure 38). Before the master transmitter mode can be entered, SSCON must be initialised as follows:

Table 64. SSCON Initialization

| CR2      | SSIE | STA | STO | SI | AA | CR1      | CR0      |

|----------|------|-----|-----|----|----|----------|----------|

| bit rate | 1    | 0   | 0   | 0  | х  | bit rate | bit rate |

CR0, CR1 and CR2 define the internal serial bit rate if external bit rate generator is not used. SSIE must be set to enable SSLC. STA, STO and SI must be cleared.

The master transmitter mode may now be entered by setting the STA bit. The 2-wire logic will now test the 2-wire bus and generate a START condition as soon as the bus becomes free. When a START condition is transmitted, the serial interrupt flag (SI bit in SSCON) is set, and the status code in SSCS will be 08h. This status must be used to vector to an interrupt routine that loads SSDAT with the slave address and the data direction bit (SLA+W).

When the slave address and the direction bit have been transmitted and an acknowledgement bit has been received, SI is set again and a number of status code in SSCS are possible. There are 18h, 20h or 38h for the master mode and also 68h, 78h or B0h if the slave mode was enabled (AA=logic 1). The appropriate action to be taken for each of these status code is detailed in Table 68. This scheme is repeated until a STOP condition is transmitted.

SSIE, CR2, CR1 and CR0 are not affected by the serial transfer and are referred to Table 7 to Table 11. After a repeated START condition (state 10h) SSLC may switch to the master receiver mode by loading SSDAT with SLA+R.

Master Receiver ModeIn the master receiver mode, a number of data bytes are received from a slave transmit-<br/>ter (Figure 39). The transfer is initialized as in the master transmitter mode. When the<br/>START condition has been transmitted, the interrupt routine must load SSDAT with the<br/>7-bit slave address and the data direction bit (SLA+R). The serial interrupt flag SI must<br/>then be cleared before the serial transfer can continue.

### Figure 40. Format and State in the Slave Receiver Mode

# AT89C51IC2

Table 77. SSADR (096h) - Synchronus Serial Address Register (read/write)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                       |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 7             | A7              | Slave Address bit 7                                                                                                               |

| 6             | A6              | Slave Address bit 6                                                                                                               |

| 5             | A5              | Slave Address bit 5                                                                                                               |

| 4             | A4              | Slave Address bit 4                                                                                                               |

| 3             | A3              | Slave Address bit 3                                                                                                               |

| 2             | A2              | Slave Address bit 2                                                                                                               |

| 1             | A1              | Slave Address bit 1                                                                                                               |

| 0             | GC              | General Call bit<br>Clear to disable the general call address recognition.<br>Set to enable the general call address recognition. |

### Table 78. SSADR Register - Reset value = FEh

# **Power-off Flag**

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (Table 81). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

### Table 81. PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                                                                                                                                                             | 4   | 3   | 2   | 1  | 0   |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|-----|

| SMOD1         | SMOD0           | -                                                                                                                                                             | POF | GF1 | GF0 | PD | IDL |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                   |     |     |     |    |     |

| 7             | SMOD1           | Serial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                                                                   |     |     |     |    |     |

| 6             | SMOD0           | Serial port Mode bit 0<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register.                                               |     |     |     |    |     |

| 5             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                               |     |     |     |    |     |

| 4             | POF             | Power-Off Flag<br>Cleared to recognize next reset type.<br>Set by hardware when $V_{CC}$ rises from 0 to its nominal voltage. Can also be set by<br>software. |     |     |     |    |     |

| 3             | GF1             | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                                  |     |     |     |    |     |

| 2             | GF0             | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                                  |     |     |     |    |     |

| 1             | PD              | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                                |     |     |     |    |     |

| 0             | IDL             | Idle mode bit<br>Cleared by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                               |     |     |     |    |     |

Reset Value = 00X1 0000b Not bit addressable

# Flash Registers and Memory Map

The AT89C51IC2 Flash memory uses several registers for its management:

- Hardware registers can only be accessed through the parallel programming modes which are handled by the parallel programmer.

- Software registers are in a special page of the Flash memory which can be accessed through the API or with the parallel programming modes. This page, called "Extra Flash Memory", is not in the internal Flash program memory addressing space.

Hardware Register The only hardware register of the AT89C51IC2 is called Hardware Security Byte (HSB).

7 6 5 4 3 2 1 0 X2 BLJB osc XRAM LB2 LB1 LB0 Bit Bit Number Mnemonic Description X2 Mode Programmed ('0' value) to force X2 mode (6 clocks per instruction) after reset. 7 X2 Unprogrammed ('1' Value) to force X1 mode, Standard Mode, after reset (Default). Boot Loader Jump Bit Unprogrammed ('1' value) to start the user's application on next reset at address BLJB 6 0000h. Programmed ('0' value) to start the boot loader at address F800h on next reset (Default). Oscillator Bit OSC 5 Programmed to allow oscillator B at startup Unprogrammed this bit to allow oscillator A at startup ( Default). 4 Reserved \_ XRAM config bit (only programmable by programmer tools) XRAM 3 Programmed to inhibit XRAM Unprogrammed, this bit to valid XRAM (Default) User Memory Lock Bits (only programmable by programmer tools) 2-0 LB2-0 See Table 85

Table 84. Hardware Security Byte (HSB)

Boot Loader Jump Bit (BLJB)

One bit of the HSB, the BLJB bit, is used to force the boot address:

- When this bit is programmed ('1' value) the boot address is 0000h.

- When this bit is unprogrammed ('1' value) the boot address is F800h. By default, this bit is unprogrammed and the ISP is enabled.

Flash Memory Lock Bits

The three lock bits provide different levels of protection for the on-chip code and data, when programmed as shown in Table 85.

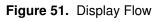

# **Display Data**

Description

Note: The maximum size of block is 400h. To read more than 400h Bytes, the Host must send a new command.

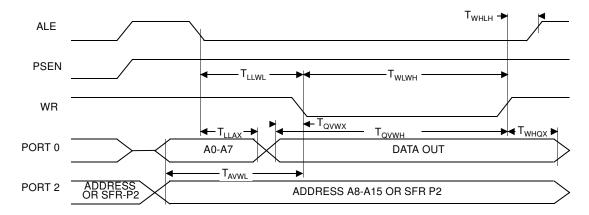

### External Program Memory Read Cycle

#### External Data Memory Characteristics

Table 97. Symbol Description

| Symbol            | Parameter                   |  |

|-------------------|-----------------------------|--|

| T <sub>RLRH</sub> | RD Pulse Width              |  |

| T <sub>WLWH</sub> | WR Pulse Width              |  |

| T <sub>RLDV</sub> | RD to Valid Data In         |  |

| T <sub>RHDX</sub> | Data Hold After RD          |  |

| T <sub>RHDZ</sub> | Data Float After RD         |  |

| T <sub>LLDV</sub> | ALE to Valid Data In        |  |

| T <sub>AVDV</sub> | Address to Valid Data In    |  |

| T <sub>LLWL</sub> | ALE to WR or RD             |  |

| T <sub>AVWL</sub> | Address to WR or RD         |  |

| T <sub>QVWX</sub> | Data Valid to WR Transition |  |

| T <sub>QVWH</sub> | Data set-up to WR High      |  |

| T <sub>WHQX</sub> | Data Hold After WR          |  |

| T <sub>RLAZ</sub> | RD Low to Address Float     |  |

| T <sub>WHLH</sub> | RD or WR High to ALE high   |  |

| B |

|---|

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X Parameter for -<br>M Range | X Parameter for -<br>L Range | Units |

|-------------------|------|-------------------|-----------|------------------------------|------------------------------|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 25                           | 25                           | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 25                           | 25                           | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 30                           | 30                           | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0                            | 0                            | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 25                           | 25                           | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 45                           | 45                           | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 65                           | 65                           | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 30                           | 30                           | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 30                           | 30                           | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 30                           | 30                           | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 20                           | 20                           | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 20                           | 20                           | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 15                           | 15                           | ns    |

| T <sub>RLAZ</sub> | Max  | x                 | х         | 0                            | 0                            | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 20                           | 20                           | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 20                           | 20                           | ns    |

# External Data Memory Write Cycle

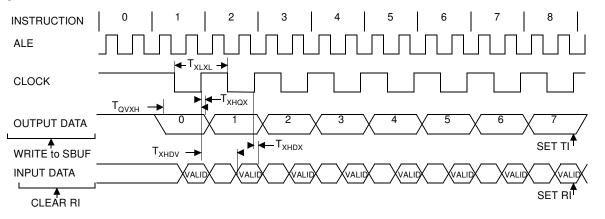

# Shift Register Timing Waveforms

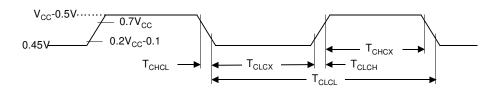

# External Clock Drive Waveforms

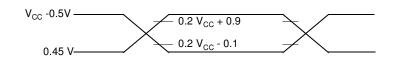

# AC Testing Input/Output Waveforms

INPUT/OUTPUT

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

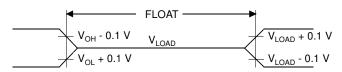

### **Float Waveforms**

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

### **Clock Waveforms**

Valid in normal clock mode. In X2 mode XTAL2 must be changed to XTAL2/2.