Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51ic2-slsum |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 10. Two-Wire Interface Controller SFRs

| Mnemonic | Add | Name                       | 7     | 6    | 5     | 4     | 3    | 2    | 1     | 0     |

|----------|-----|----------------------------|-------|------|-------|-------|------|------|-------|-------|

| SSCON    | 93h | Synchronous Serial control | SSCR2 | SSPE | SSSTA | SSSTO | SSI  | SSAA | SSCR1 | SSCR0 |

| SSCS     | 94h | Synchronous Serial Status  | SSC4  | SSC3 | SSC2  | SSC1  | SSC0 | 0    | 0     | 0     |

| SSDAT    | 95h | Synchronous Serial Data    | SSD7  | SSD6 | SSD5  | SSD4  | SSD3 | SSD2 | SSD1  | SSD0  |

| SSADR    | 96h | Synchronous Serial Address | SSA7  | SSA6 | SSA5  | SSA4  | SSA3 | SSA2 | SSA1  | SSGC  |

#### Table 11. Keyboard Interface SFRs

| Mnemonic | Add | Name                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| KBLS     | 9Ch | Keyboard Level Selector | KBLS7 | KBLS6 | KBLS5 | KBLS4 | KBLS3 | KBLS2 | KBLS1 | KBLS0 |

| KBE      | 9Dh | Keyboard Input Enable   | KBE7  | KBE6  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  |

| KBF      | 9Eh | Keyboard Flag Register  | KBF7  | KBF6  | KBF5  | KBF4  | KBF3  | KBF2  | KBF1  | KBF0  |

Table 18. Overview (Continued)

| PCON.1 | PCON.0 | OscBEn | OscAEn | CKS | Selected Mode      | Comment                                                                          |

|--------|--------|--------|--------|-----|--------------------|----------------------------------------------------------------------------------|

| 0      | 1      | х      | 1      | 1   | IDLE MODE A        | The CPU is off, OscA supplies the peripherals, OscB can be disabled (OscBEn = 0) |

| 0      | 1      | 1      | х      | 0   | IDLE MODE B        | The CPU is off, OscB supplies the peripherals, OscA can be disabled (OscAEn = 0) |

| 1      | х      | х      | 1      | х   | POWER DOWN<br>MODE | The CPU and peripherals are off, OscA and OscB are stopped                       |

### **Design Considerations**

#### **Oscillators Control**

- PwdOscA and PwdOscB signals are generated in the Clock generator and used to control the hard blocks of oscillators A and B.

- PwdOscA ='1' stops OscA

- PwdOscB ='1' stops OscB

- The following tables summarize the Operating modes:

| PCON.1      | OscAEn           | PwdOscA      | Comments                           |

|-------------|------------------|--------------|------------------------------------|

| 0           | 1                | 0            | OscA running                       |

| 1           | х                | 1            | OscA stopped by<br>Power-down mode |

| 0           | 0                | 1            | OscA stopped by<br>clearing OscAEn |

|             |                  |              |                                    |

| PCON.1      | OscBEn           | PwdOscB      | Comments                           |

| PCON.1<br>0 | OscBEn<br>1      | PwdOscB<br>0 | Comments<br>OscB running           |

|             | OscBEn<br>1<br>X |              |                                    |

#### **Prescaler Divider**

- A hardware RESET puts the prescaler divider in the following state:

- CKRL = FFh:  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSCA}/2$  (Standard C51 feature)

- CKS signal selects OSCA or OSCB: F<sub>CLK OUT</sub> = F<sub>OSCA</sub> or F<sub>OSCB</sub>

- Any value between FFh down to 00h can be written by software into CKRL register in order to divide frequency of the selected oscillator:

- CKRL = 00h: minimum frequency  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSCA}/1020$  (Standard Mode)  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSCA}/510$  (X2 Mode)

- $\begin{array}{ll} & \mathsf{CKRL} = \mathsf{FFh:} \mbox{ maximum frequency} \\ & \mathsf{F}_{\mathsf{CLK}\ \mathsf{CPU}} = \mathsf{F}_{\mathsf{CLK}\ \mathsf{PERIPH}} = \mathsf{F}_{\mathsf{OSCA}}/2 \mbox{ (Standard Mode)} \\ & \mathsf{F}_{\mathsf{CLK}\ \mathsf{CPU}} = \mathsf{F}_{\mathsf{CLK}\ \mathsf{PERIPH}} = \mathsf{F}_{\mathsf{OSCA}} \mbox{ (X2 Mode)} \end{array}$

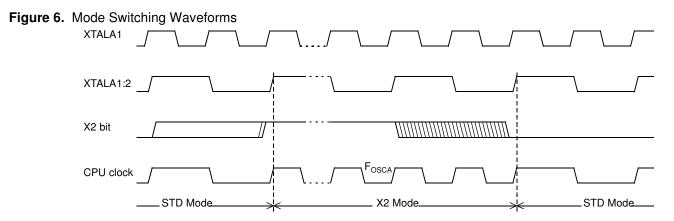

The X2 bit in the CKCON0 register (see Table 19) allow to switch from 12 clock periods per instruction to 6 clock periods and vice versa. At reset, the speed is setting according to X2 bit of Hardware Security Byte (HSB). By default, Standard mode is actived. Setting the X2 bit activates the X2 feature (X2 mode).

The T0X2, T1X2, T2X2, UartX2, PcaX2, WdX2 and I2CX2 bits in the CKCON0 register (See Table 19.) and SPIX2 bit in the CKCON1 register (see Table 20) allow to switch from standard peripheral speed (12 clock periods per peripheral clock cycle) to fast peripheral speed (6 clock periods per peripheral clock cycle). These bits are active only in X2 mode.

More information about the X2 mode can be found in the application note "How to take advantage of the X2 features in TS80C51 microcontroller?"

## Table 19. CKCON0 Register

CKCON0 - Clock Control Register (8Fh)

| 7             | 6               | 5                                                           | 4                                                                                                                                                                                                                                                                           | 3                                                                 | 2               | 1             | 0            |  |  |  |

|---------------|-----------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|---------------|--------------|--|--|--|

| SPIX2         | WDX2            | PCAX2                                                       | SIX2                                                                                                                                                                                                                                                                        | T2X2                                                              | T1X2            | T0X2          | X2           |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptior                                                 | Description                                                                                                                                                                                                                                                                 |                                                                   |                 |               |              |  |  |  |

| 7             | I2CX2           | X2 is low, th<br>Cleared to s                               | <b>2-wire clock</b> (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                     |                                                                   |                 |               |              |  |  |  |

| 6             | WDX2            | when X2 is<br>Cleared to s                                  | Watchdog clock (This control bit is validated when the CPU clock X2 is set;<br>when X2 is low, this bit has no effect)<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                       |                                                                   |                 |               |              |  |  |  |

| 5             | PCAX2           | CPU clock ><br>Cleared to s                                 | <b>Programmable Counter Array clock</b> (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |                                                                   |                 |               |              |  |  |  |

| 4             | SIX2            | CPU clock X<br>Cleared to s                                 | Enhanced UART clock (Mode 0 and 2) (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.      |                                                                   |                 |               |              |  |  |  |

| 3             | T2X2            | X2 is low, th<br>Cleared to s                               | is bit has no e<br>elect 6 clock                                                                                                                                                                                                                                            | ol bit is validat<br>effect)<br>periods per pe<br>iods per perip  | eripheral clock | cycle.        | is set; when |  |  |  |

| 2             | T1X2            | X2 is low, th<br>Cleared to s                               | is bit has no e<br>elect 6 clock                                                                                                                                                                                                                                            | ol bit is validat<br>effect)<br>periods per pe<br>iods per peripl | eripheral clock | cycle.        | is set; when |  |  |  |

| 1             | T0X2            | X2 is low, th<br>Cleared to s                               | <b>Timer0 clock</b> (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                     |                                                                   |                 |               |              |  |  |  |

| 0             | X2              | all the perip<br>Set to selec<br>individual pe<br>Programme | herals.<br>t 6clock perio<br>eripherals "X2                                                                                                                                                                                                                                 | e after Power-                                                    | e cycle (X2 m   | ode) and to e | nable the    |  |  |  |

Reset Value = 0000 000'HSB.X2'b Not bit addressable

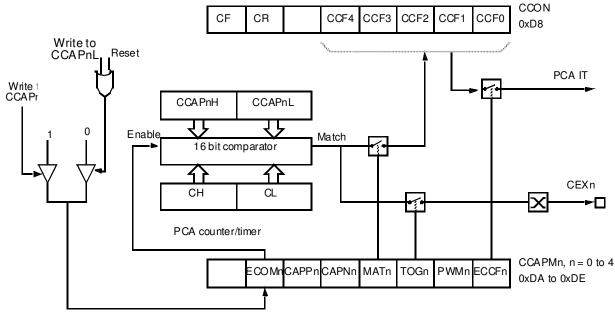

## Programmable Counter Array PCA

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture modules. Its clock input can be programmed to count any one of the following signals:

- Peripheral clock frequency (F<sub>CLK PERIPH</sub>) ÷ 6

- Peripheral clock frequency (F<sub>CLK PERIPH</sub>) ÷ 2

- Timer 0 overflow

- External input on ECI (P1.2)

Each compare/capture modules can be programmed in any one of the following modes:

- rising and/or falling edge capture

- software timer

- high-speed output

- pulse width modulator

Module 4 can also be programmed as a watchdog timer (See Section "PCA Watchdog Timer", page 46).

When the compare/capture modules are programmed in the capture mode, software timer, or high speed output mode, an interrupt can be generated when the module executes its function. All five modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If the port is not used for the PCA, it can still be used for standard I/O.

| PCA component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2 / ECI       |

| 16-bit Module 0 | P1.3 / CEX0      |

| 16-bit Module 1 | P1.4 / CEX1      |

| 16-bit Module 2 | P1.5 / CEX2      |

| 16-bit Module 3 | P1.6 / CEX3      |

The PCA timer is a common time base for all five modules (See Figure 11). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD register (Table 26) and can be programmed to run at:

- 1/6 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- 1/2 the peripheral clock frequency (F<sub>CLK PERIPH</sub>)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

Figure 15. PCA High Speed Output Mode

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

**Pulse Width Modulator** Mode All of the PCA modules can be used as PWM outputs. Figure 16 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

| Baud Rates | F <sub>OSCA</sub> = 1 | 6.384 MHz | F <sub>OSCA</sub> = 24MHz |           |  |

|------------|-----------------------|-----------|---------------------------|-----------|--|

|            | BRL                   | Error (%) | BRL                       | Error (%) |  |

| 115200     | 247                   | 1.23      | 243                       | 0.16      |  |

| 57600      | 238                   | 1.23      | 230                       | 0.16      |  |

| 38400      | 229                   | 1.23      | 217                       | 0.16      |  |

| 28800      | 220                   | 1.23      | 204                       | 0.16      |  |

| 19200      | 203                   | 0.63      | 178                       | 0.16      |  |

| 9600       | 149                   | 0.31      | 100                       | 0.16      |  |

| 4800       | 43                    | 1.23      | -                         | -         |  |

Table 38.

Example of computed value when X2=1, SMOD1=1, SPD=1

Table 39.

Example of computed value when X2=0, SMOD1=0, SPD=0

| Baud Rates | F <sub>OSCA</sub> = 16 | 6.384 MHz     | F <sub>OSCA</sub> = 24MHz |           |  |

|------------|------------------------|---------------|---------------------------|-----------|--|

|            | BRL                    | BRL Error (%) |                           | Error (%) |  |

| 4800       | 247                    | 1.23          | 243                       | 0.16      |  |

| 2400       | 238                    | 1.23          | 230                       | 0.16      |  |

| 1200       | 220                    | 1.23          | 202                       | 3.55      |  |

| 600        | 185                    | 0.16          | 152                       | 0.16      |  |

The baud rate generator can be used for mode 1 or 3 (refer to Figure 20.), but also for mode 0 for UART, thanks to the bit SRC located in BDRCON register (Table 46.)

## Table 53. IPH1 Register

IPH1 - Interrupt Priority High Register (B3h)

| 7             | 6               | 5                                                                                                                                                      | 4                                                             | 3               | 2              | 1            | 0    |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------|----------------|--------------|------|

| -             | -               | -                                                                                                                                                      | -                                                             | -               | SPIH           | тwін         | KBDH |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                            |                                                               |                 |                |              |      |

| 7             | -               | <b>Reserved</b><br>The value re                                                                                                                        | ad from this b                                                | it is indetermi | nate. Do not s | et this bit. |      |

| 6             | -               | <b>Reserved</b><br>The value re                                                                                                                        | ad from this b                                                | it is indetermi | nate. Do not s | et this bit. |      |

| 5             | -               | <b>Reserved</b><br>The value re                                                                                                                        | ad from this b                                                | it is indetermi | nate. Do not s | et this bit. |      |

| 4             | -               | <b>Reserved</b><br>The value re                                                                                                                        | ad from this b                                                | it is indetermi | nate. Do not s | et this bit. |      |

| 3             | -               | Reserved<br>The value re                                                                                                                               | ad from this b                                                | it is indetermi | nate. Do not s | et this bit. |      |

| 2             | SPIH            | SPIHSPILPr<br>0 0 Low<br>0 1<br>1 0                                                                                                                    | <b>t Priority Hig</b><br>i <u>ority Level</u><br>vest<br>hest | ıh bit          |                |              |      |

| 1             | TWIH            | TWI interrupt Priority High bit         TWIHTWILPriority Level         0       0         0       1         1       0         1       1         Highest |                                                               |                 |                |              |      |

| 0             | KBDH            | <u>KB DHKBDL</u><br>0 0 Lov<br>0 1<br>1 0                                                                                                              | nterrupt Prior<br>Priority Level<br>west<br>hest              |                 |                |              |      |

Reset Value = XXXX X000b Not bit addressable

|           | drive the network. The Master may select each Slave device by software through port pins (Figure 27). To prevent bus conflicts on the MISO line, only one slave should be selected at a time by the Master for a transmission.                                                                                                              |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | In a Master configuration, the $\overline{SS}$ line can be used in conjunction with the MODF flag in the SPI Status register (SPSTA) to prevent multiple masters from driving MOSI and SCK (see Error conditions).                                                                                                                          |

|           | A high level on the $\overline{\text{SS}}$ pin puts the MISO line of a Slave SPI in a high-impedance state.                                                                                                                                                                                                                                 |

|           | The $\overline{SS}$ pin could be used as a general-purpose if the following conditions are met:                                                                                                                                                                                                                                             |

|           | <ul> <li>The device is configured as a Master and the SSDIS control bit in SPCON is set.<br/>This kind of configuration can be found when only one Master is driving the network<br/>and there is no way that the SS pin could be pulled low. Therefore, the MODF flag in<br/>the SPSTA will never be set<sup>(1)</sup>.</li> </ul>         |

|           | • The Device is configured as a Slave with CPHA and SSDIS control bits set <sup>(2)</sup> . This kind of configuration can happen when the system comprises one Master and one Slave only. Therefore, the device should always be selected and there is no reason that the Master uses the SS pin to select the communicating Slave device. |

|           | Note: 1. Clearing SSDIS control bit does not clear MODF.                                                                                                                                                                                                                                                                                    |

|           | 2. Special care should be taken not to set SSDIS control bit when CPHA = '0' because in this mode, the $\overline{SS}$ is used to start the transmission.                                                                                                                                                                                   |

| Baud Rate | In Master mode, the baud rate can be selected from a baud rate generator which is con-<br>trolled by three bits in the SPCON register: SPR2, SPR1 and SPR0.The Master clock is<br>selected from one of seven clock rates resulting from the division of the internal clock by<br>2, 4, 8, 16, 32, 64 or 128.                                |

|           | Table 56 gives the different clock rates selected by SPR2:SPR1:SPR0.                                                                                                                                                                                                                                                                        |

|           | Table 56.         SPI Master Baud Rate Selection                                                                                                                                                                                                                                                                                            |

| SPR2 | SPR1 | SPR0 | Clock Rate                   | Baud Rate Divisor (BD) |

|------|------|------|------------------------------|------------------------|

| 0    | 0    | 0    | F <sub>CLK PERIPH</sub> /2   | 2                      |

| 0    | 0    | 1    | F <sub>CLK PERIPH</sub> /4   | 4                      |

| 0    | 1    | 0    | F <sub>CLK PERIPH</sub> /8   | 8                      |

| 0    | 1    | 1    | F <sub>CLK PERIPH</sub> /16  | 16                     |

| 1    | 0    | 0    | F <sub>CLK PERIPH</sub> /32  | 32                     |

| 1    | 0    | 1    | F <sub>CLK PERIPH</sub> /64  | 64                     |

| 1    | 1    | 0    | F <sub>CLK PERIPH</sub> /128 | 128                    |

| 1    | 1    | 1    | Don't Use                    | No BRG                 |

Table 56.

SPI Master Baud Rate Selection

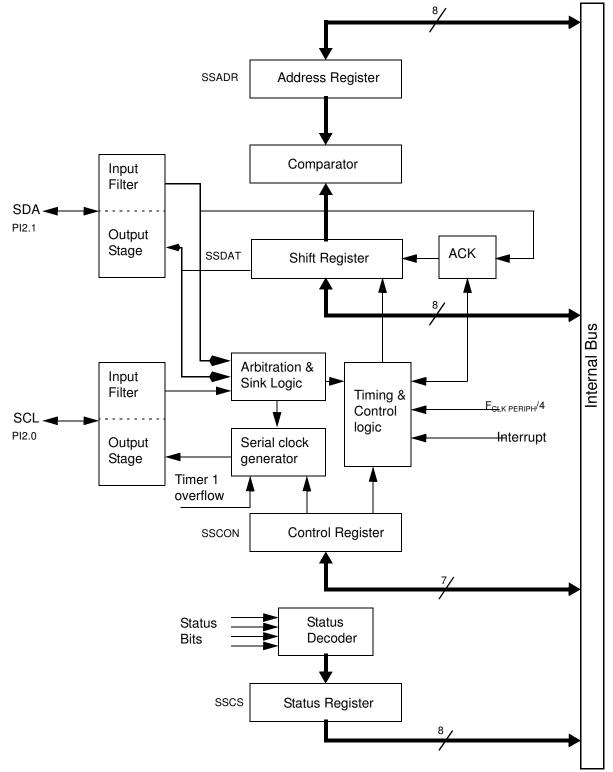

## 2-wire Interface (TWI)

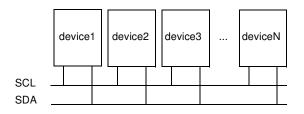

This section describes the 2-wire interface. In the rest of the section SSLC means Twowire. The 2-wire bus is a bi-directional 2-wire serial communication standard. It is designed primarily for simple but efficient integrated circuit (IC) control. The system is comprised of two lines, SCL (Serial Clock) and SDA (Serial Data) that carry information between the ICs connected to them. The serial data transfer is limited to 400Kbit/s in standard mode. Various communication configuration can be designed using this bus. Figure 35 shows a typical 2-wire bus configuration. All the devices connected to the bus can be master and slave.

Figure 35. 2-wire Bus Configuration

# AT89C51IC2

|                |                                                                                                        | Application S      | Software | e Respo | nse |    |                                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------------|--------------------|----------|---------|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status         |                                                                                                        | To/from SSDAT      |          | To SS   | CON |    |                                                                                                                                                                                      |

| Code<br>(SSCS) | Status of the 2-wire bus and<br>2-wire hardware                                                        |                    | STA      | STO     | SI  | AA | Next Action Taken By 2-wire Software                                                                                                                                                 |

|                |                                                                                                        | Read data byte or  | 0        | 0       | 0   | 0  | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA<br>Switched to the not addressed slave mode; own                                                       |

|                |                                                                                                        | Read data byte or  | 0        | 0       | 0   | 1  | SLA will be recognised; GCA will be recognised if GC=logic 1                                                                                                                         |

| 98h            | Previously addressed with<br>general call; data has been<br>received; NOT ACK has been<br>returned     | Read data byte or  | 1        | 0       | 0   | 0  | Switched to the not addressed slave mode; no recognition of own SLA or GCA. A START condition will be transmitted when the bus becomes free                                          |

|                |                                                                                                        | Read data byte     | 1        | 0       | 0   | 1  | Switched to the not addressed slave mode; own<br>SLA will be recognised; GCA will be recognised if<br>GC=logic 1. A START condition will be<br>transmitted when the bus becomes free |

|                |                                                                                                        | No SSDAT action or | 0        | 0       | 0   | 0  | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA<br>Switched to the not addressed slave mode; own                                                       |

|                |                                                                                                        | No SSDAT action or | 0        | 0       | 0   | 1  | SLA will be recognised; GCA will be recognised if GC=logic 1                                                                                                                         |

| A0h            | A STOP condition or repeated<br>START condition has been<br>received while still addressed<br>as slave | No SSDAT action or | 1        | 0       | 0   | 0  | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA. A START<br>condition will be transmitted when the bus<br>becomes free                                 |

|                |                                                                                                        | No SSDAT action    | 1        | 0       | 0   | 1  | Switched to the not addressed slave mode; own<br>SLA will be recognised; GCA will be recognised if<br>GC=logic 1. A START condition will be<br>transmitted when the bus becomes free |

#### Table 88. Program Lock Bits of the SSB

| Program Lock Bits |     | Bits |                                                                       |

|-------------------|-----|------|-----------------------------------------------------------------------|

| Security<br>level | LB0 | LB1  | Protection Description                                                |

| 1                 | U   | U    | No program lock features enabled.                                     |

| 2                 | Р   | U    | ISP programming of the Flash is disabled.                             |

| 3                 | Х   | Р    | Same as 2, also verify through ISP programming interface is disabled. |

Note: U: unprogrammed or "one" level.

P: programmed or "zero" level.

X: don't care

WARNING: Security level 2 and 3 should only be programmed after Flash and code verification.

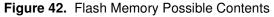

**Flash Memory Status** AT89C51IC2 parts are delivered in standard with the ISP boot in the Flash memory. After ISP or parallel programming, the possible contents of the Flash memory are summarized on Figure 42.

### **Memory Organization**

In the AT89C51IC2, the lowest 32K of the 64 KB program memory address space is filled by internal Flash.

When the  $\overline{EA}$  pin is high, the processor fetches instructions from internal program Flash. Bus expansion for accessing program memory from 32K upward automatic since external instruction fetches occur automatically when the program counter exceeds 7FFFh (32K). If the  $\overline{EA}$  pin is tied low, all program memory fetches are from external memory.

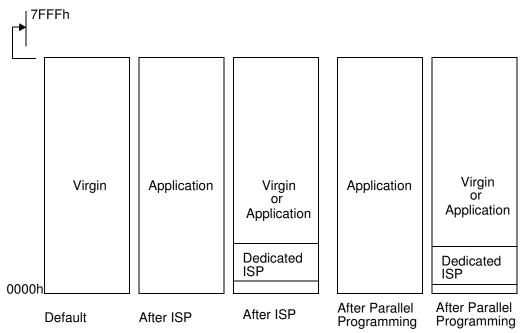

#### **Blank Check Command**

#### Description

#### Figure 50. Blank Check Flow

Example

| Blank  | Check | ok  |      |       |     |       |      |    |    |    |    |    |    |    |

|--------|-------|-----|------|-------|-----|-------|------|----|----|----|----|----|----|----|

| HOST   |       | :   | 05   | 0000  | 04  | 0000  | 7fff | 01 | 78 |    |    |    |    |    |

| BOOTL  | OADER | :   | 05   | 0000  | 04  | 0000  | 7fff | 01 | 78 | •  | CR | LF |    |    |

| Blank  | Check | ko  | at   | addr  | ess | XXXX  | x    |    |    |    |    |    |    |    |

| HOST   |       | :   | 05   | 0000  | 04  | 0000  | 7fff | 01 | 78 |    |    |    |    |    |

| BOOTLO | ADER  | :   | 05   | 0000  | 04  | 0000  | 7fff | 01 | 78 | XX | XX | CR | LF |    |

| Blank  | Check | wit | th d | check | sur | n err | or   |    |    |    |    |    |    |    |

| HOST   |       | :   | 05   | 0000  | 04  | 0000  | 7fff | 01 | 70 |    |    |    |    |    |

| BOOTL  | OADER | :   | 05   | 0000  | 04  | 0000  | 7fff | 01 | 70 | Х  | CR | LF | CR | LF |

# AT89C51IC2

Table 93. API Call Summary (Continued)

| Command              | R1  | Α                               | DPTR0                                                                | DPTR1                                                 | Returned Value     | Command Effect                                                                                                                                                                                                             |

|----------------------|-----|---------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROGRAM DATA<br>PAGE | 09h | Number of<br>byte to<br>program | Address of<br>the first byte<br>to program in<br>the Flash<br>memory | Address in<br>XRAM of the<br>first data to<br>program | ACC = 0: DONE      | Program up to 128 bytes in user Flash.<br>Remark: number of bytes to program is<br>limited such as the Flash write remains in a<br>single 128 bytes page. Hence, when ACC<br>is 128, valid values of DPL are 00h, or, 80h. |

| PROGRAM X2 FUSE      | 0Ah | Fuse value<br>00h or 01h        | 0008h                                                                | XXh                                                   | none               | Program X2 fuse bit with ACC                                                                                                                                                                                               |

| PROGRAM BLJB<br>FUSE | 0Ah | Fuse value<br>00h or 01h        | 0004h                                                                | XXh                                                   | none               | Program BLJB fuse bit with ACC                                                                                                                                                                                             |

| READ HSB             | 0Bh | XXh                             | XXXXh                                                                | XXh                                                   | ACC = HSB          | Read Hardware Byte                                                                                                                                                                                                         |

| READ BOOT ID1        | 0Eh | XXh                             | DPL = 00h                                                            | XXh                                                   | ACC = ID1          | Read boot ID1                                                                                                                                                                                                              |

| READ BOOT ID2        | 0Eh | XXh                             | DPL = 01h                                                            | XXh                                                   | ACC = ID2          | Read boot ID2                                                                                                                                                                                                              |

| READ BOOT VERSION    | 0Fh | XXh                             | XXXXh                                                                | XXh                                                   | ACC = Boot_Version | Read bootloader version                                                                                                                                                                                                    |

## $T_A = -40^{\circ}C$ to $+85^{\circ}C$ ; $V_{SS} = 0V$ ;

$V_{\text{CC}}$  =2.7V to 5.5V and F = 0 to 40 MHz (both internal and external code execution)

| Symbol              | Parameter                                           | Min                                                                     | Тур                              | Мах                       | Unit        | Test Conditions                                                                                                       |

|---------------------|-----------------------------------------------------|-------------------------------------------------------------------------|----------------------------------|---------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|

| V <sub>OH1</sub>    | Output High Voltage, port 0, ALE, PSEN              | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |                                  |                           | V<br>V<br>V | $V_{CC} = 5V \pm 10\%$<br>$I_{OH} = -200 \ \mu\text{A}$<br>$I_{OH} = -3.2 \ \text{mA}$<br>$I_{OH} = -7.0 \ \text{mA}$ |

|                     |                                                     | 0.9 V <sub>CC</sub>                                                     |                                  |                           | V           | VCC = 2.7V to 5.5V<br>I <sub>OH</sub> = -10 μA                                                                        |

| R <sub>RST</sub>    | RST Pulldown Resistor                               | 50                                                                      | 200 <sup>(5)</sup>               | 250                       | kΩ          |                                                                                                                       |

| $I_{IL}$            | Logical 0 Input Current ports 1, 2, 3, 4 and 5      |                                                                         |                                  | -50                       | μA          | V <sub>IN</sub> = 0.45V                                                                                               |

| ILI                 | Input Leakage Current for P0 only                   |                                                                         |                                  | ±10                       | μA          | $0.45V < V_{IN} < V_{CC}$                                                                                             |

| I <sub>TL</sub>     | Logical 1 to 0 Transition Current, ports 1, 2, 3, 4 |                                                                         |                                  | -650                      | μA          | V <sub>IN</sub> = 2.0V                                                                                                |

| C <sub>IO</sub>     | Capacitance of I/O Buffer                           |                                                                         |                                  | 10                        | pF          | Fc = 3 MHz<br>TA = 25°C                                                                                               |

| I <sub>PD</sub>     | Power Down Current                                  |                                                                         | 100                              | 150                       | μA          | $4.5V < V_{CC} < 5.5V^{(3)}$                                                                                          |

| I <sub>CCOP</sub>   | Power Supply Current on normal mode                 |                                                                         |                                  | 0.4 x Frequency (MHz) + 5 | mA          | $V_{\rm CC} = 5.5 V^{(1)}$                                                                                            |

|                     | Power Supply Current on idle mode                   |                                                                         |                                  | 0.3 x Frequency (MHz) + 5 | mA          | $V_{\rm CC} = 5.5 V^{(1)}$                                                                                            |

| I <sub>CCProg</sub> | Power Supply Current during flash Write / Erase     |                                                                         | 0.4 x<br>Frequency<br>(MHz) + 20 |                           | mA          | V <sub>CC</sub> = 5.5V <sup>(8)</sup>                                                                                 |

Notes: 1. Operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL} = 5$  ns (see Figure 56.),  $V_{IL} = V_{SS} + 0.5V$ ,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used (see Figure 53).

- 2. Idle I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5V, V<sub>IH</sub> = V<sub>CC</sub> 0.5V; XTAL2 N.C; Port 0 = V<sub>CC</sub>;  $\overline{EA}$  = RST = V<sub>SS</sub> (see Figure 54).

- Power Down I<sub>CC</sub> is measured with all output pins disconnected; EA = V<sub>SS</sub>, PORT 0 = V<sub>CC</sub>; XTAL2 NC.; RST = V<sub>SS</sub> (see Figure 55).

- 4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

- 5. Typical are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port: Port 0: 26 mA Ports 1, 2 and 3: 15 mA

Maximum total  $I_{OL}$  for all output pins: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

- 8. Icc Flash Write operation current while an on-chip flash page write is on going.

- 9. Flash Retention is guaranteed with the same formula for  $V_{\rm CC}$  Min down to 0.

| Symbol            | -М  |      |     | -L  | Units |

|-------------------|-----|------|-----|-----|-------|

|                   | Min | Max  | Min | Мах |       |

| Т                 | 25  |      | 25  |     | ns    |

| T <sub>LHLL</sub> | 35  |      | 35  |     | ns    |

| T <sub>AVLL</sub> | 5   |      | 5   |     | ns    |

| T <sub>LLAX</sub> | 5   |      | 5   |     | ns    |

| T <sub>LLIV</sub> |     | n 65 |     | 65  | ns    |

| T <sub>LLPL</sub> | 5   |      | 5   |     | ns    |

| T <sub>PLPH</sub> | 50  |      | 50  |     | ns    |

| T <sub>PLIV</sub> |     | 30   |     | 30  | ns    |

| T <sub>PXIX</sub> | 0   |      | 0   |     | ns    |

| T <sub>PXIZ</sub> |     | 10   |     | 10  | ns    |

| T <sub>AVIV</sub> |     | 80   |     | 80  | ns    |

| T <sub>PLAZ</sub> |     | 10   |     | 10  | ns    |

Table 95.

AC Parameters for a Fix Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X Parameter for -<br>M Range | X Parameter for<br>-L Range | Units |

|-------------------|------|-------------------|-----------|------------------------------|-----------------------------|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 15                           | 15                          | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 20                           | 20                          | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 20                           | 20                          | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 35                           | 35                          | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 15                           | 15                          | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 25                           | 25                          | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 45                           | 45                          | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0                            | 0                           | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 15                           | 15                          | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 45                           | 45                          | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10                           | 10                          | ns    |

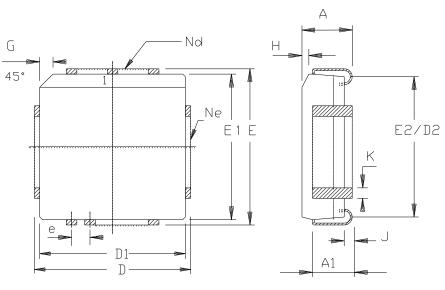

# Package Drawing

PLCC44

|    | M      | 1M ·  | IN    | СН    |  |

|----|--------|-------|-------|-------|--|

| A  | 4.20   | 4. 57 | . 165 | . 180 |  |

| A1 | 2. 29  | 3.04  | . 090 | . 120 |  |

| D  | 17.40  | 17.65 | . 685 | . 695 |  |

| D1 | 16.44  | 16.66 | . 647 | . 656 |  |

| D2 | 14.99  | 16.00 | . 590 | . 630 |  |

| E  | 17.40  | 17.65 | . 685 | . 695 |  |

| E1 | 16.44  | 16.66 | . 647 | . 656 |  |

| E5 | 14.99  | 16.00 | . 590 | . 630 |  |

| e  | 1.27   | BSC   | . 050 | BSC   |  |

| G  | 1.07   | 1.22  | . 042 | . 048 |  |

| н  | 1.07   | 1.42  | . 042 | .056  |  |

| J  | 0.51   | -     | . 020 | -     |  |

| К  | 0.33   | 0.53  | . 013 | . 021 |  |

| Nd | 11     |       | 11    |       |  |

| Ne | 1      | 1     | 11    |       |  |

| P  | KG STD | 00    |       |       |  |

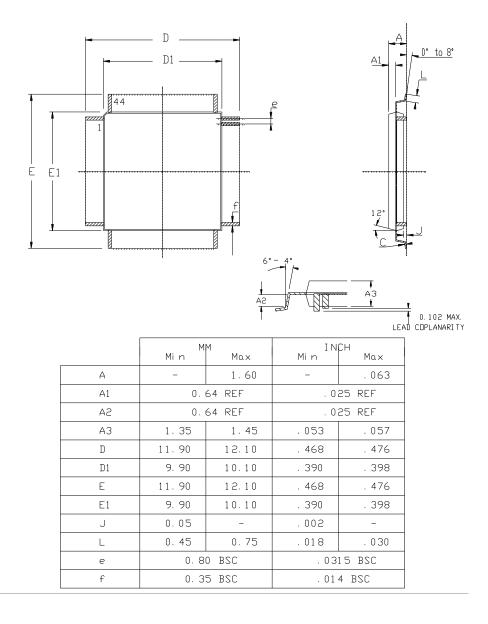

## Package Drawing

## VQFP44

| DC Parameters for Low Voltage<br>AC Parameters |                |

|------------------------------------------------|----------------|

| Ordering Information                           | 140            |

| Package Drawing                                |                |

| PLCC44                                         | 141            |

| Package Drawing                                | <b>142</b><br> |

| Datasheet Revision History                     |                |

| Changes from Rev. A 01/04 - Rev. B 01/06       | 143            |

| Changes from Rev. B 01/06 - Rev. C 06/06       | 143            |

| Changes from Rev. C 06/06 - Rev. D 02/08       | 143            |

| Table of Contents                              | i              |