# E. Renesas Electronics America Inc - UPD78F0401GA-GAM-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | LINbus, UART/USART                                                                   |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 30                                                                                   |

| Program Memory Size        | 16KB (16K × 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 768 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | ·                                                                                    |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 48-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0401ga-gam-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

[MEMO]

| 13.4.4 Calculation of baud rate                             |     |

|-------------------------------------------------------------|-----|

|                                                             |     |

| CHAPTER 14 SERIAL INTERFACE UART6                           | 335 |

| 14.1 Functions of Serial Interface UART6                    | 335 |

| 14.2 Configuration of Serial Interface UART6                | 339 |

| 14.3 Registers Controlling Serial Interface UART6           |     |

| 14.4 Operation of Serial Interface UART6                    | 353 |

| -<br>14.4.1 Operation stop mode                             |     |

| 14.4.2 Asynchronous serial interface (UART) mode            |     |

| 14.4.3 Dedicated baud rate generator                        |     |

| 14.4.4 Calculation of baud rate                             |     |

| CHAPTER 15 LCD CONTROLLER/DRIVER                            |     |

| 15.1 Functions of LCD Controller/Driver                     |     |

| 15.2 Configuration of LCD Controller/Driver                 |     |

| 15.3 Registers Controlling LCD Controller/Driver            |     |

| 15.4 Setting LCD Controller/Driver                          |     |

| 15.5 LCD Display Data Memory                                |     |

| 15.6 Common and Segment Signals                             |     |

| 15.7 Display Modes                                          |     |

| 15.7.1 Static display example                               |     |

| 15.7.2 Two-time-slice display example                       |     |

| 15.7.3 Three-time-slice display example                     |     |

| 15.7.4 Four-time-slice display example                      |     |

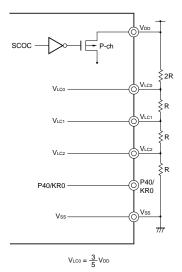

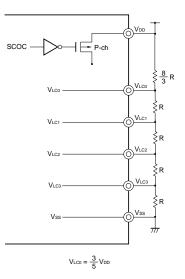

| 15.8 Supplying LCD Drive Voltages VLc0, VLc1, VLc2 and VLc3 |     |

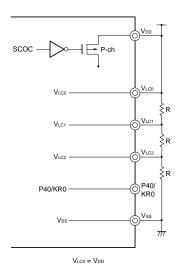

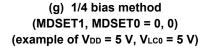

| 15.8.1 Internal resistance division method                  |     |

| 15.8.2 External resistance division method                  |     |

|                                                             |     |

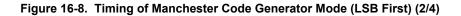

| CHAPTER 16 MANCHESTER CODE GENERATOR                        | 410 |

| 16.1 Functions of Manchester Code Generator                 | 410 |

| 16.2 Configuration of Manchester Code Generator             | 410 |

| 16.3 Registers Controlling Manchester Code Generator        | 413 |

| 16.4 Operation of Manchester Code Generator                 | 416 |

| 16.4.1 Operation stop mode                                  | 416 |

| 16.4.2 Manchester code generator mode                       | 417 |

| 16.4.3 Bit sequential buffer mode                           |     |

| CHAPTER 17 INTERRUPT FUNCTIONS                              | 435 |

| 17.1 Interrupt Function Types                               | 435 |

| 17.2 Interrupt Sources and Configuration                    |     |

| 17.3 Registers Controlling Interrupt Functions              |     |

| 17.4 Interrupt Servicing Operations                         |     |

| 17.4.1 Maskable interrupt acknowledgment                    |     |

| 17.4.2 Software interrupt request acknowledgment            |     |

| 17.4.3 Multiple interrupt servicing                         |     |

| 17.4.4 Interrupt request hold                               |     |

|                                                             |     |

78K0/LF3

Part Number

(3/3)

| RAM (KB)         0.75         1         1         2         2         0.75         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         1         1         1 <th1< th="">         1</th1<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |                             |                                       |                          | D78F0                                                          | 47x |        | μPD78F048x |                      |                   |                       |                 | μPD78F049x |                      |         |       |    |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------|---------------------------------------|--------------------------|----------------------------------------------------------------|-----|--------|------------|----------------------|-------------------|-----------------------|-----------------|------------|----------------------|---------|-------|----|----|

| RAM (KB)         0.75         1         1         2         2         0.75         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         1         2         2         0.75         1         1         1         2         2         0.75         1         1         1         1         2         2         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Iter          | n                           |                                       |                          |                                                                |     |        |            | 1                    |                   | 80 Pins               | 3               |            |                      |         |       |    |    |

| Power supply voltage         Void = 1.8 to 5.5 V           Regulator         Provided           Minimum instruction<br>execution time         0.2 µs (10 MH2: Void = 2.7 to 5.5 V/3 0.4 µs (5 MH2: Void = 1.8 to 5.5 V)           execution time         10 MH2: Void = 2.7 to 5.5 V/3 0.4 µs (5 MH2: Void = 1.8 to 5.5 V)           execution time         10 MH2: Void = 2.7 to 5.5 V/3 0.4 µs (5 MH2: Void = 1.8 to 5.5 V)           execution time         2.7 to 5.5 V/3 0.4 µs (5 MH2: Void = 1.8 to 5.5 V)           execution time         2.7 to 5.5 V/3 0.4 µs (5 MH2: Void = 1.8 to 5.5 V)           Subclock         32.768 kH2 (TYP.): Void = 1.8 to 5.5 V           Subclock         32.768 kH2 (TYP.): Void = 1.8 to 5.5 V           Itemaal low-speed<br>descillation clock         3 ch           Bits (TM0)         1 ch           Bits (TM1)         3 ch           Bits (TM1)         3 ch           Bits (TM1)         1 ch           WDT         1 ch           MAUT supporting LIN-<br>treelve 3-wire CSI         1 ch           Segment signal         40 (36) <sup>MM3</sup> 32 (28) <sup>MM3</sup> Common signal         4 (8) <sup>MM43</sup> 32 (28) <sup>MM3</sup> Common signal         4 (8) <sup>MM43</sup> 32 (28) <sup>MM3</sup> Common signal         20         21         22           Metand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Fla           | sh r                        | nemory (KB)                           | 16                       | 24                                                             | 32  | 48     | 60         | 16                   | 24                | 32                    | 48              | 60         | 16                   | 24      | 32    | 48 | 60 |

| Regulator         Provided           Minimum instruction<br>execution time         0.2 µs (10 MHz: Voo = 2.7 to 5.5 V/) 0.4 µs (5 MHz: Voo = 1.8 to 5.5 V)           Image: State of the system<br>oscillation clock         10 MHz: Voo = 2.7 to 5.5 V/5 MHz: Voo = 1.8 to 5.5 V           Image: State of the system<br>oscillation clock         10 MHz: Voo = 2.7 to 5.5 V/5 MHz: Voo = 1.8 to 5.5 V           Subclock         32.768 kHz (TYP.): Voo = 1.8 to 5.5 V           Subclock         32.768 kHz (TYP.): Voo = 1.8 to 5.5 V           Subclock         32.768 kHz (TYP.): Voo = 1.8 to 5.5 V           Subclock         32.768 kHz (TYP.): Voo = 1.8 to 5.5 V           Subclock         32.768 kHz (TYP.): Voo = 1.8 to 5.5 V           Subclock         32.768 kHz (TYP.): Voo = 1.8 to 5.5 V           Subclock         32.768 kHz (TYP.): Voo = 1.8 to 5.5 V           Subclock         32.768 kHz (TYP.): Voo = 1.8 to 5.6 V           Subclock         32.768 kHz (TYP.): Voo = 1.8 to 5.6 V           Subclock         32.08 kHz (TYP.): Voo = 1.8 to 5.6 V           Subclock         32.08 kHz (TYP.): Voo = 1.8 to 5.6 V           Subclock         32.08 kHz (TYP.): Voo = 1.8 to 5.6 V           Subclock         32.08 kHz (TYP.): Voo = 1.8 to 5.6 V           Subclock         32.08 kHz (TYP.): Voo = 1.8 to 5.6 V           Subclock         32.08 kHz (TYP.): Voo = 1.8 to 5.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RA            | M (ł                        | (В)                                   | 0.75                     | 1                                                              | 1   | 2      | 2          | 0.75                 | 1                 | 1                     | 2               | 2          | 0.75                 | 1       | 1     | 2  | 2  |

| Minimum instruction time         0.2 µs (10 MHz: Von = 2.7 to 5.5 V/) 0.4 µs (5 MHz: Von = 1.8 to 5.5 V) <ul> <li></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Po            | wer                         | supply voltage                        |                          |                                                                |     |        |            |                      | V <sub>DD</sub> = | = 1.8 to              | 5.5 V           |            |                      |         |       |    |    |

| execution time High-Speed system 10 MHz: Voo = 2.7 to 5.5 V/SMHz: Voo = 1.8 to 5.5 V<br>file control high-Speed system 2.7 to 5.5 V/SMHz: Voo = 1.8 to 5.5 V<br>subclock 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>subclock 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 240 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.708 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.768 kHz (TYP.): Voo = 1.8 to 5.5 V<br>filemail low-speed 32.777<br>filemail low-speed 32.777<br>filem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Re            | gula                        | tor                                   |                          |                                                                |     |        |            |                      | I                 | Provide               | d               |            |                      |         |       |    |    |

| $ \begin{array}{ c c c } \hline \hline \begin{tabular}{ c c } \hline \hline \bellambol{tabular}{ c c c } \hline \hline \begin{tabular}{ c c } \hline \hline \begin{tabular}{ c c } \hline \hline \begin{tabular}{ c c } \hline \hline \bellambol{tabular}{ c c } \hline \hline \begin{tabular}{ c c } \hline \hline \begin{tabular}{ c c } \hline \hline \begin{tabular}{ c c } \hline \hline \bellambol{tabular}{ c c } \hline \hline \bellambol{tabular}{ c c c c } \hline \hline \bellambol{tabular}{ c c c c c } \hline \hline \belambol{tabular}{ c c c } \hline \hline \bellambol{tabular}{ c $ |               |                             |                                       |                          |                                                                | 0.2 | μs (10 | MHz: \     | ∕ <sub>DD</sub> = 2. | 7 to 5.           | 5 V)/ 0. <sup>,</sup> | 4 <i>μ</i> s (5 | MHz:       | V <sub>DD</sub> = 1  | .8 to 5 | .5 V) |    |    |

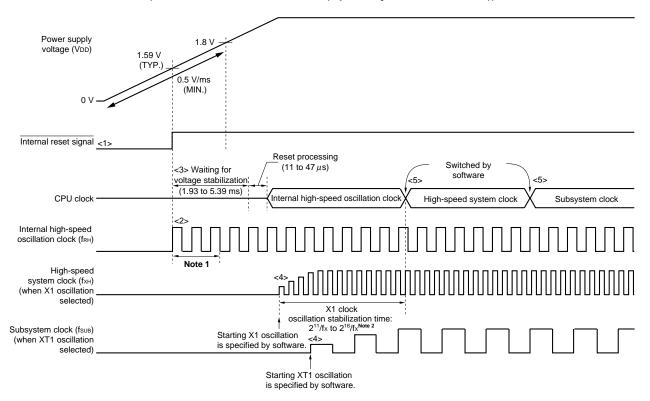

| Constrained         Constrained         Constrained           Subclock         32.768 kHz (TYP.): Vac) = 1.8 to 5.5 V           Internal low-speed<br>oscillation clock         62           Total         62           Ib bits (TM0)         1 ch           8 bits (TM5)         3 ch           8 bits (TM1)         3 ch           8 bits (TM1)         3 ch           9 bits (TM1)         1 ch           WDT         1 ch           WDT         1 ch           WDT         1 ch           9 bits (TM1)         3 ch           9 wire CSI/UART*host         1 ch           9 bits (TM2)         1 ch </td <td></td> <td>ain</td> <td>High-speed system<br/>clock</td> <td></td> <td colspan="9">10 MHz: <math>V_{DD}</math> = 2.7 to 5.5 V/5 MHz: <math>V_{DD}</math> = 1.8 to 5.5 V</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | ain                         | High-speed system<br>clock            |                          | 10 MHz: $V_{DD}$ = 2.7 to 5.5 V/5 MHz: $V_{DD}$ = 1.8 to 5.5 V |     |        |            |                      |                   |                       |                 |            |                      |         |       |    |    |

| SUGOCK         32.768 kH2 (17P). Voc = 1.8 to 5.5 V           Internal low-speed<br>oscillation clock         240 kH2 (17P). Voc = 1.8 to 5.5 V           It         62           It         62           It         8 bits (TM0)           It         1 c h           B bits (TM5)         3 c h           RC         1 c h           WDT         1 c h           Veg         3-wire CSI/UART*Now1           It         1 c h           Automatic transmit/         1 c h           Veg         Segment signal           OPP         External resistance division and internal resistance division are switchable.           Segment signal         40 (36)*New3           Common signal         4 (8)*New3           It-bit Successive approximation type A/D         -           Stack type A/D         -           Internal         20           External         7           Internal         20           External         7           Internal         20           Stack type A/D         -           It is uscessive approximation type A/D         -           It is uscessive approximation type A/D         -           It is Up A/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | clock         | Ma                          | Internal high-speed oscillation clock |                          |                                                                |     |        |            |                      | •                 |                       |                 |            |                      |         |       |    |    |

| oscillation clock         Call           Total         62           16 bits (TM0)         1 ch           3 bits (TM5)         3 ch           3 bits (TM1)         3 ch           3 bits (TM1)         3 ch           3 bits (TM1)         3 ch           3 wire CSI/UART <sup>Note1</sup> 1 ch           4utomatic transmit/         1 ch           Automatic transmit/         2 (28) <sup>Note3</sup> Common signal         40 (36) <sup>Note3</sup> Common signal         4 (8) <sup>Note3</sup> 10-bit successive         -           Segment signal         20           External         7           Internal         20           External         7           Internal         20           POC         1.59 V ±0.15 V (Time for rising up to 1.8 V : 3.6 m s (MAX.))           VI         The detection level of the supply voitage is selectable in 16 steps.           WOT <td>0</td> <td>Sul</td> <td>oclock</td> <td></td> <td></td> <td></td> <td></td> <td>3</td> <td>2.768 k</td> <td>(Hz (T</td> <td>YP.): Vo</td> <td>od = 1.8</td> <td>8 to 5.5</td> <td>V</td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0             | Sul                         | oclock                                |                          |                                                                |     |        | 3          | 2.768 k              | (Hz (T            | YP.): Vo              | od = 1.8        | 8 to 5.5   | V                    |         |       |    |    |

| $ \frac{1}{10} $ $ $                                                                                                                     |               |                             |                                       |                          |                                                                |     |        |            | 240 k⊦               | iz (tyf           | <b>P.): V</b> dd      | = 1.8 t         | o 5.5 V    | /                    |         |       |    |    |

| B bits (TM5)         3 ch           8 bits (TM4)         3 ch           8 bits (TM4)         3 ch           RTC         1 ch           WDT         1 ch           3-wire CSI/UART Notert         1 ch           Automatic transmit/<br>receive 3-wire CSI         1 ch           WDT         1 ch           Automatic transmit/<br>receive 3-wire CSI         1 ch           0         Type         External resistance division and internal resistance division are switchable.           Segment signal         40 (36) <sup>Notes3</sup> 32 (28) <sup>Notes3</sup> 10-bit successive<br>approximation type A/D         -         8 ch           16-bit ΔΣ type A/D         -         3 ch           16-bit ΔΣ type A/D         -         3 ch           110-bit successive<br>approximation type A/D         -         3 ch           16-bit ΔΣ type A/D         -         3 ch           16-bit ΔΣ type A/D         -         3 ch           110-bit successive<br>approximation type A/D         -         22           Key interrupt         8 ch         -           16-bit ΔΣ type A/D         -         22           16-bit ΔΣ type A/D         -         1.59 V ±0.15 V (Time for rising up to 1.8 V : 3.6 ms (MAX.))           16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Port          | Tot                         | al                                    |                          |                                                                |     |        |            |                      |                   | 62                    |                 |            |                      |         |       |    |    |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               | 16                          | bits (TM0)                            |                          |                                                                |     |        |            |                      |                   | 1 ch                  |                 |            |                      |         |       |    |    |

| $\begin{tabular}{ c                                   $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | L             | 8 b                         | its (TM5)                             |                          |                                                                |     |        |            |                      |                   | 3 ch                  |                 |            |                      |         |       |    |    |

| $\begin{tabular}{ c                                   $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ime           | 8 b                         | its (TMH)                             |                          |                                                                |     |        |            |                      |                   | 3 ch                  |                 |            |                      |         |       |    |    |

| 3-wire CSI/UART <sup>Note1</sup> 1 ch         4utomatic transmit/<br>receive 3-wire CSI       1 ch         UART supporting LIN-<br>bus <sup>Note2</sup> 1 ch         Common signal       40 (36) <sup>Note3</sup> 32 (28) <sup>Note3</sup> Common signal       4 (8) <sup>Note3</sup> 32 (28) <sup>Note3</sup> 10-bit successive<br>approximation type A/D       8 ch         External       7       3 ch         Internal       20       21       22         RESET pin       Provided       9         POC       1.59 V ±0.15 V (Time for rising up to 1.8 V : 3.6 ms (MAX.))       1.59 V ±0.15 V (Time for rising up to 1.8 V : 3.6 ms (MAX.))         LVI       The detection level of the supply voltage is selectable in 16 steps.       WAT         WDT       Provided       Provided         REmote controller receiver       Provided       Provided         WDT       Provided       Provided         Remote controller receiver       Provided       Provided         MCG       Onchip debug function       Provided         Onchip debug function       Provided       Provided                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | μ             | RT                          | С                                     |                          |                                                                |     |        |            |                      |                   | 1 ch                  |                 |            |                      |         |       |    |    |

| QuestionAutomatic transmit/<br>receive 3-wire CSI1 chUART supporting LIN-<br>bus Note21 chUART supporting LIN-<br>bus Note21 chSegment signal40 (36) Note3Common signal40 (36) Note310-bit successive<br>approximation type A/D-16-bit $\Delta\Sigma$ type A/D-16-bit $\Delta\Sigma$ type A/D-16-bit $\Delta\Sigma$ type A/D-16-bit $\Delta\Sigma$ type A/D20172218RESET pinPOC1.59 V ±0.15 V (Time for rising up to 1.8 V : 3.6 ms (MAX.))19VDTVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvidedVDTProvided                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |                             |                                       |                          |                                                                |     |        |            |                      |                   | 1 ch                  |                 |            |                      |         |       |    |    |

| Image: Provided                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | e             | 3-v                         | /ire CSI/UART <sup>Note1</sup>        |                          |                                                                |     |        |            |                      |                   | 1 ch                  |                 |            |                      |         |       |    |    |

| Image: Provided                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | erfac         | Aut                         | omatic transmit/                      | 1 ch                     |                                                                |     |        |            |                      |                   |                       |                 |            |                      |         |       |    |    |

| TypeExternal resistance division and internal resistance division are switchable.Segment signal40 (36)^Note332 (28)^Note310-bit successive<br>aproximation type A/D-8 ch16-bit $\Delta\Sigma$ type A/D-3 ch16-bit $\Delta\Sigma$ type A/D-3 ch16-bit $\Delta\Sigma$ type A/D-3 ch16-bit $\Delta\Sigma$ type A/D-2216-bit $\Delta\Sigma$ type A/D-3 ch16-bit $\Delta\Sigma$ type A/D16-bit $\Delta\Sigma$ type A/D-3 ch16-bit $\Delta\Sigma$ type A/D16-bit $\Delta\Sigma$ type A/D1718191010101010101010101010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | inte          |                             |                                       |                          |                                                                |     |        |            |                      |                   |                       |                 |            |                      |         |       |    |    |

| Common signal40 (36) Note332 (28) Note310-bit successive<br>approximation type A/D-8 ch16-bit $\Delta\Sigma$ type A/D-3 ch16-bit $\Delta\Sigma$ type A/D-716-bit $\Delta\Sigma$ type A/D212216-bit $\Delta\Sigma$ type A/D212216-bit $\Delta\Sigma$ type A/D0116-bit $\Delta\Sigma$ type A/D-716-bit $\Delta\Sigma$ type A/D-716-bit $\Delta\Sigma$ type A/D202116-bit $\Delta\Sigma$ type A/D202110-bit $\Delta\Sigma$ type A/D8 chKey internupt8 chRESET pinProvidedPOC1.59 V ±0.15 V (Time for rising up to 1.8 V : 3.6 ms (MAX.))VVDTProvidedVDTProvidedVDTProvidedRemote controller receiverProvidedMCGProvidedOn-chip debug functionProvidedOperating ambientTA = -40 to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Serial        | UA<br>bus                   | RT supporting LIN-                    | 1 ch                     |                                                                |     |        |            |                      |                   |                       |                 |            |                      |         |       |    |    |

| Common signal $4 (8)^{Note3}$ 10-bit successive<br>approximation type A/D-8 ch16-bit $\Delta\Sigma$ type A/D-3 ch16-bit $\Delta\Sigma$ type A/D-7Internal202110 ker2021Key interrupt8 chRESET pinProvidedPOC1.59 V $\pm 0.15$ V (Time for rising up to 1.8 V : 3.6 ms (MAX.))VUThe detection level of the supply voltage is selectable in 16 steps.WDTProvidedClock output/ Buzzer outputProvidedRESET pinProvidedVDTProvidedVDTProvidedOn-chip debug functionProvidedOperating ambientTA = -40 to +85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _             | Тур                         | )e                                    |                          |                                                                |     |        |            |                      |                   |                       |                 |            |                      |         |       |    |    |

| Common signal         4 (8) <sup>Note3</sup> 10-bit successive<br>approximation type A/D         8 ch           16-bit ΔΣ type A/D         -           16-bit ΔΣ type A/D         -           16-bit ΔΣ type A/D         -           16-bit ΔΣ type A/D         3 ch           16-bit ΔΣ type A/D         3 ch           16-bit ΔΣ type A/D         -           10-bit ΔΣ type A/D         -           10-bit ΔΣ type A/D         -           10-bit ΔΣ type A/D         20           10-bit ΔΣ type A/D         -           10-bit ΔΣ type A/D         - <tr< td=""><td>5</td><td>Se</td><td>gment signal</td><td colspan="9">40 (36)<sup>Note3</sup></td><td>33</td><td>2 (28)<sup>No</sup></td><td>ote3</td><td></td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5             | Se                          | gment signal                          | 40 (36) <sup>Note3</sup> |                                                                |     |        |            |                      |                   |                       |                 | 33         | 2 (28) <sup>No</sup> | ote3    |       |    |    |

| $\begin{array}{c c c c c c } \hline \begin{tabular}{ c c c c } \hline \begin{tabular}{ c c c c } \hline \begin{tabular}{ c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c c } \hline \begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _             | Co                          | mmon signal                           | 4 (8) <sup>Note3</sup>   |                                                                |     |        |            |                      |                   |                       |                 |            |                      |         |       |    |    |

| $\begin{tabular}{ c c c c }\hline \hline External & \hline & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                             |                                       |                          | – 8 ch                                                         |     |        |            |                      |                   |                       |                 |            |                      |         |       |    |    |