# E. Renesas Electronics America Inc - UPD78F0402GA-GAM-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | LINbus, UART/USART                                                                   |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 30                                                                                   |

| Program Memory Size        | 24KB (24K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | -                                                                                    |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 48-LQFP                                                                              |

| Supplier Device Package    | •                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0402ga-gam-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **1** VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

# (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

# **③** PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

# **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

# 5 POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

# 6 INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

| 8.4.3 Carrier generator operation (8-bit timer H1 only)                   | 255 |

|---------------------------------------------------------------------------|-----|

| CHAPTER 9 REAL-TIME COUNTER                                               | 262 |

| 9.1 Functions of Real-Time Counter                                        | 262 |

| 9.2 Configuration of Real-Time Counter                                    | 262 |

| 9.3 Registers Controlling Real-Time Counter                               |     |

| 9.4 Real-Time Counter Operation                                           |     |

| 9.4.1 Starting operation of real-time counter                             |     |

| 9.4.2 Reading/writing real-time counter                                   | 277 |

| 9.4.3 Setting alarm of real-time counter                                  | 279 |

| CHAPTER 10 WATCHDOG TIMER                                                 | 280 |

| 10.1 Functions of Watchdog Timer                                          | 280 |

| 10.2 Configuration of Watchdog Timer                                      |     |

| 10.3 Register Controlling Watchdog Timer                                  |     |

| 10.4 Operation of Watchdog Timer                                          |     |

| 10.4.1 Controlling operation of watchdog timer                            |     |

| 10.4.2 Setting overflow time of watchdog timer                            |     |

| 10.4.3 Setting window open period of watchdog timer                       |     |

| CHAPTER 11 BUZZER OUTPUT CONTROLLER                                       | 287 |

|                                                                           |     |

| 11.1 Functions of Buzzer Output Controller                                |     |

| 11.2 Configuration of Buzzer Output Controller                            |     |

| 11.3 Registers Controlling Buzzer Output Controller                       |     |

| 11.4 Operations of Buzzer Output Controller                               |     |

| CHAPTER 12 10-BIT SUCCESSIVE APPROXIMATION TYPE A/D CONVERTER             |     |

| (μPD78F041x only)                                                         | 291 |

| 12.1 Function of 10-Bit Successive Approximation Type A/D Converter       | 291 |

| 12.2 Configuration of 10-Bit Successive Approximation Type A/D Converter  | 292 |

| 12.3 Registers Used in 10-Bit Successive Approximation Type A/D Converter | 294 |

| 12.4 10-Bit Successive Approximation Type A/D Converter Operations        | 302 |

| 12.4.1 Basic operations of A/D converter                                  |     |

| 12.4.2 Input voltage and conversion results                               |     |

| 12.4.3 A/D converter operation mode                                       |     |

| 12.5 How to Read A/D Converter Characteristics Table                      | 307 |

| 12.6 Cautions for 10-Bit Successive Approximation Type A/D Converter      | 309 |

| CHAPTER 13 SERIAL INTERFACE UART0                                         | 313 |

| 13.1 Functions of Serial Interface UART0                                  | 313 |

| 13.2 Configuration of Serial Interface UART0                              |     |

| 13.3 Registers Controlling Serial Interface UART0                         |     |

| 13.4 Operation of Serial Interface UART0                                  |     |

| 13.4.1 Operation stop mode                                                |     |

| 13.4.2 Asynchronous serial interface (UART) mode                          |     |

| 13.4.3 Dedicated baud rate generator.                                     |     |

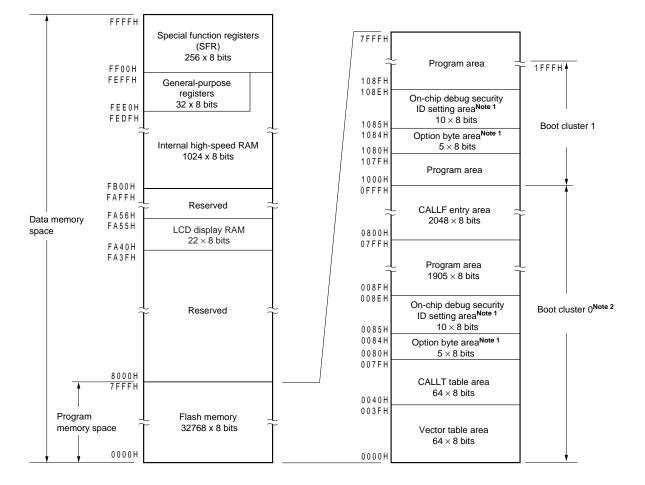

**Notes 1.** When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used:

Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- Writing boot cluster 0 can be prohibited depending on the setting of security (see 24.7 Security Setting).

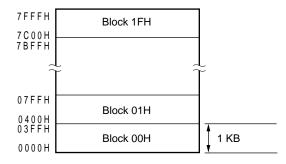

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

# 3.4 Operand Address Addressing

The following methods are available to specify the register and memory (addressing) to undergo manipulation during instruction execution.

# 3.4.1 Implied addressing

# [Function]

The register that functions as an accumulator (A and AX) among the general-purpose registers is automatically (implicitly) addressed.

Of the 78K0/LC3 instruction words, the following instructions employ implied addressing.

| Instruction | Register to Be Specified by Implied Addressing                                  |

|-------------|---------------------------------------------------------------------------------|

| MULU        | A register for multiplicand and AX register for product storage                 |

| DIVUW       | AX register for dividend and quotient storage                                   |

| ADJBA/ADJBS | A register for storage of numeric values that become decimal correction targets |

| ROR4/ROL4   | A register for storage of digit data that undergoes digit rotation              |

#### [Operand format]

Because implied addressing can be automatically determined with an instruction, no particular operand format is necessary.

#### [Description example]

In the case of MULU X

With an 8-bit  $\times$  8-bit multiply instruction, the product of the A register and X register is stored in AX. In this example, the A and AX registers are specified by implied addressing.

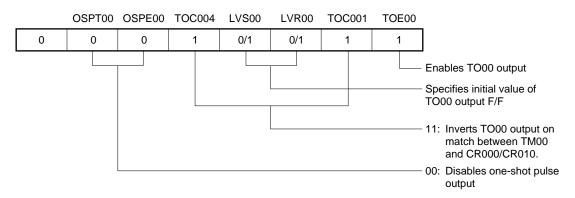

#### Figure 6-8. Format of 16-Bit Timer Output Control Register 00 (TOC00)

| Address: F | FBDH After | reset: 00H | R/W    |        |       |       |        |       |

|------------|------------|------------|--------|--------|-------|-------|--------|-------|

| Symbol     | 7          | <6>        | <5>    | 4      | <3>   | <2>   | 1      | <0>   |

| TOC00      | 0          | OSPT00     | OSPE00 | TOC004 | LVS00 | LVR00 | TOC001 | TOE00 |

| OSPT00       | One-shot pulse output trigger via software                                                                  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------|--|--|

| 0            | _                                                                                                           |  |  |

| 1            | One-shot pulse output                                                                                       |  |  |

| The value of | The value of this bit is always "0" when it is read. Do not set this bit to 1 in a mode other than the one- |  |  |

shot pulse output mode.

If it is set to 1, TM00 is cleared and started.

| OSPE00                                                                                                   | One-shot pulse output operation control |  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| 0                                                                                                        | Successive pulse output                 |  |

| 1                                                                                                        | One-shot pulse output                   |  |

| One-shot pulse output operates correctly in the free-running timer mode or clear & start mode entered by |                                         |  |

TI000 pin valid edge input. The one-shot pulse cannot be output in the clear & start mode entered upon a match between TM00 and CR000.

| TOC004                                                              | TO00 output control on match between CR010 and TM00 |  |

|---------------------------------------------------------------------|-----------------------------------------------------|--|

| 0                                                                   | Disables inversion operation                        |  |

| 1                                                                   | Enables inversion operation                         |  |

| The intermut since $(N TTN040)$ is generated over when $TOC024 = 0$ |                                                     |  |

The interrupt signal (INTTM010) is generated even when TOC004 = 0.

| LVS00 | LVR00 | Setting of TO00 output status                                            |

|-------|-------|--------------------------------------------------------------------------|

| 0     | 0     | No change                                                                |

| 0     | 1     | Initial value of TO00 output is low level (TO00 output is cleared to 0). |

| 1     | 0     | Initial value of TO00 output is high level (TO00 output is set to 1).    |

| 1     | 1     | Setting prohibited                                                       |

• LVS00 and LVR00 can be used to set the initial value of the TO00 output level. If the initial value does not have to be set, leave LVS00 and LVR00 as 00.

• Be sure to set LVS00 and LVR00 when TOE00 = 1. LVS00, LVR00, and TOE00 being simultaneously set to 1 is prohibited.

• LVS00 and LVR00 are trigger bits. By setting these bits to 1, the initial value of the TO00 output level can be set. Even if these bits are cleared to 0, TO00 output is not affected.

• The values of LVS00 and LVR00 are always 0 when they are read.

- For how to set LVS00 and LVR00, see 6.5.2 Setting LVS00 and LVR00.

- The actual TO00/TI010/P34/TI52/RTC1HZ/INTP1 pin output is determined depending on PM34 and P34, besides TO00 output.

| TOC001                                                             | TO00 output control on match between CR000 and TM00 |  |

|--------------------------------------------------------------------|-----------------------------------------------------|--|

| 0                                                                  | Disables inversion operation                        |  |

| 1                                                                  | Enables inversion operation                         |  |

| The interrupt signal (INTTM000) is generated even when TOC001 = 0. |                                                     |  |

| TOE00 | TO00 output control                              |

|-------|--------------------------------------------------|

| 0     | Disables output (TO00 output fixed to low level) |

| 1     | Enables output                                   |

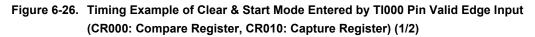

(2) Operation in clear & start mode entered by TI000 pin valid edge input (CR000: compare register, CR010: capture register)

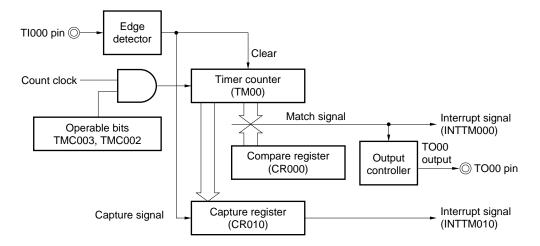

> Figure 6-25. Block Diagram of Clear & Start Mode Entered by TI000 Pin Valid Edge Input (CR000: Compare Register, CR010: Capture Register)

(a) TOC00 = 13H, PRM00 = 10H, CRC00, = 04H, TMC00 = 08H, CR000 = 0001H

This is an application example where the TO00 output level is inverted when the count value has been captured & cleared.

The count value is captured to CR010 and TM00 is cleared (to 0000H) when the valid edge of the TI000 pin is detected. When the count value of TM00 is 0001H, a compare match interrupt signal (INTTM000) is generated, and the TO00 output level is inverted.

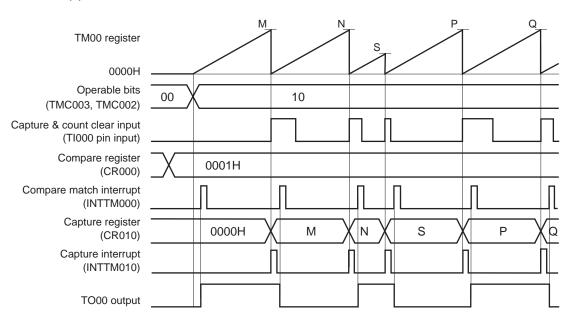

(4) Operation in clear & start mode entered by TI000 pin valid edge input (CR000: capture register, CR010: capture register)

Figure 6-29. Block Diagram of Clear & Start Mode Entered by TI000 Pin Valid Edge Input (CR000: Capture Register, CR010: Capture Register)

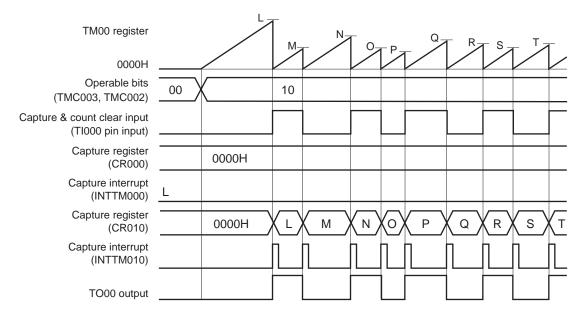

# Figure 6-30. Timing Example of Clear & Start Mode Entered by TI000 Pin Valid Edge Input (CR000: Capture Register, CR010: Capture Register) (1/3)

(a) TOC00 = 13H, PRM00 = 30H, CRC00 = 05H, TMC00 = 0AH

This is an application example where the count value is captured to CR010, TM00 is cleared, and the TO00 output is inverted when the rising or falling edge of the TI000 pin is detected.

When the edge of the TI010 pin is detected, an interrupt signal (INTTM000) is generated. Mask the INTTM000 signal when it is not used.

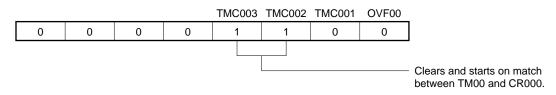

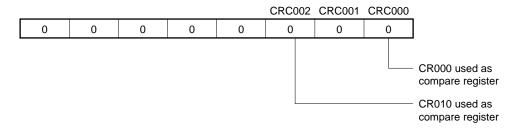

# Figure 6-42. Example of Register Settings for PPG Output Operation

#### (a) 16-bit timer mode control register 00 (TMC00)

#### (b) Capture/compare control register 00 (CRC00)

# (c) 16-bit timer output control register 00 (TOC00)

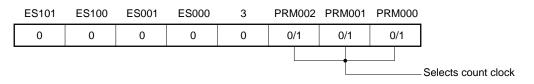

#### (d) Prescaler mode register 00 (PRM00)

#### (e) 16-bit timer counter 00 (TM00)

By reading TM00, the count value can be read.

#### (f) 16-bit capture/compare register 000 (CR000)

An interrupt signal (INTTM000) is generated when the value of this register matches the count value of TM00. The count value of TM00 is not cleared.

# (g) 16-bit capture/compare register 010 (CR010)

An interrupt signal (INTTM010) is generated when the value of this register matches the count value of TM00. The count value of TM00 is not cleared.

Caution Set values to CR000 and CR010 such that the condition  $0000H \le CR010 < CR000 \le FFFFH$  is satisfied.

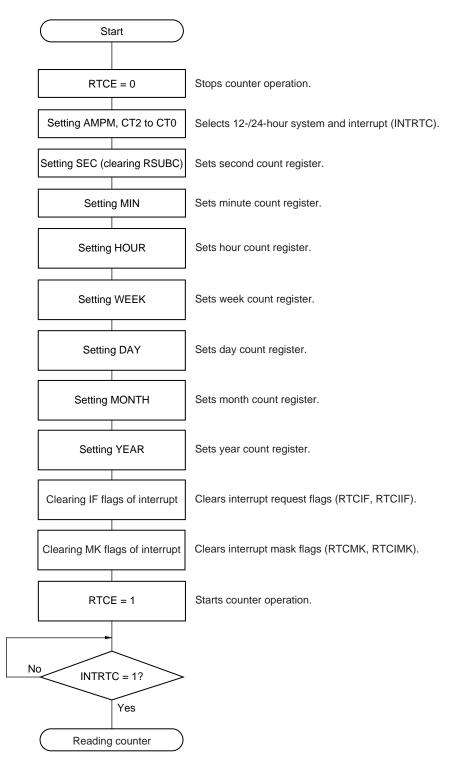

# 9.4 Real-Time Counter Operation

# 9.4.1 Starting operation of real-time counter

# Figure 9-18. Procedure for Starting Operation of Real-Time Counter

# (e) Reception error

Three types of errors may occur during reception: a parity error, framing error, or overrun error. If the error flag of asynchronous serial interface reception error status register 0 (ASIS0) is set as a result of data reception, a reception error interrupt (INTSR0) is generated.

Which error has occurred during reception can be identified by reading the contents of ASIS0 in the reception error interrupt (INTSR0) servicing (see **Figure 13-3**).

The contents of ASIS0 are cleared to 0 when ASIS0 is read.

| Table 13-3. | Cause o | f Reception | Error |

|-------------|---------|-------------|-------|

|-------------|---------|-------------|-------|

| Reception Error | Cause                                                                                              |

|-----------------|----------------------------------------------------------------------------------------------------|

| Parity error    | The parity specified for transmission does not match the parity of the receive data.               |

| Framing error   | Stop bit is not detected.                                                                          |

| Overrun error   | Reception of the next data is completed before data is read from receive buffer register 0 (RXB0). |

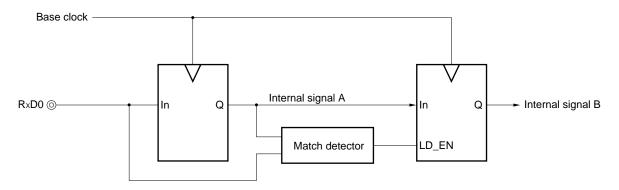

# (f) Noise filter of receive data

The RxD0 signal is sampled using the base clock output by the prescaler block.

If two sampled values are the same, the output of the match detector changes, and the data is sampled as input data.

Because the circuit is configured as shown in Figure 13-11, the internal processing of the reception operation is delayed by two clocks from the external signal status.

# (4) Clock selection register 6 (CKSR6)

This register selects the base clock of serial interface UART6. CKSR6 can be set by an 8-bit memory manipulation instruction. Reset signal generation sets this register to 00H.

**Remark** CKSR6 can be refreshed (the same value is written) by software during a communication operation (when bits 7 and 6 (POWER6, TXE6) of ASIM6 = 1 or bits 7 and 5 (POWER6, RXE6) of ASIM6 = 1).

#### Figure 14-8. Format of Clock Selection Register 6 (CKSR6)

Address: FF56H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|--------|---|---|---|---|-------|-------|-------|-------|

| CKSR6  | 0 | 0 | 0 | 0 | TPS63 | TPS62 | TPS61 | TPS60 |

| TPS63 | TPS62            | TPS61 | TPS60 | Base clock (fxcLK6) selection <sup>Note 1</sup> |                             |                             |                             |                              |

|-------|------------------|-------|-------|-------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|

|       |                  |       |       |                                                 | f <sub>PRS</sub> =<br>2 MHz | f <sub>PRS</sub> =<br>5 MHz | f <sub>PRS</sub> =<br>8 MHz | f <sub>PRS</sub> =<br>10 MHz |

| 0     | 0                | 0     | 0     | fprs <sup>Note 2</sup>                          | 2 MHz                       | 5 MHz                       | 8 MHz                       | 10 MHz                       |

| 0     | 0                | 0     | 1     | fprs/2                                          | 1 MHz                       | 2.5 MHz                     | 4 MHz                       | 5 MHz                        |

| 0     | 0                | 1     | 0     | $f_{PRS}/2^2$                                   | 500 kHz                     | 1.25 MHz                    | 2 MHz                       | 2.5 MHz                      |

| 0     | 0                | 1     | 1     | fprs/2 <sup>3</sup>                             | 250 kHz                     | 625 kHz                     | 1 MHz                       | 1.25 MHz                     |

| 0     | 1                | 0     | 0     | fprs/2 <sup>4</sup>                             | 125 kHz                     | 312.5 kHz                   | 500 kHz                     | 625 kHz                      |

| 0     | 1                | 0     | 1     | fprs/2 <sup>5</sup>                             | 62.5 kHz                    | 156.25 kHz                  | 250 kHz                     | 312.5 kHz                    |

| 0     | 1                | 1     | 0     | fprs/2 <sup>6</sup>                             | 31.25 kHz                   | 78.13 kHz                   | 125 kHz                     | 156.25 kHz                   |

| 0     | 1                | 1     | 1     | fprs/27                                         | 15.625 kHz                  | 39.06 kHz                   | 62.5 kHz                    | 78.13 kHz                    |

| 1     | 0                | 0     | 0     | fprs/2 <sup>8</sup>                             | 7.813 kHz                   | 19.53 kHz                   | 31.25 kHz                   | 39.06 kHz                    |

| 1     | 0                | 0     | 1     | fprs/29                                         | 3.906 kHz                   | 9.77 kHz                    | 15.625 kHz                  | 19.53 kHz                    |

| 1     | 0                | 1     | 0     | fprs/2 <sup>10</sup>                            | 1.953 kHz                   | 4.88 kHz                    | 7.513 kHz                   | 9.77 kHz                     |

| 1     | 0                | 1     | 1     | TM50 output <sup>Note 3</sup>                   |                             |                             |                             |                              |

|       | Other than above |       |       |                                                 | Setting prohibited          |                             |                             |                              |

- **Notes 1.** If the peripheral hardware clock (fPRs) operates on the high-speed system clock (fXH) (XSEL = 1), the fPRs operating frequency varies depending on the supply voltage.

- VDD = 2.7 to 5.5 V: fprs  $\leq$  10 MHz

- VDD = 1.8 to 2.7 V: fPRs  $\leq$  5 MHz

- If the peripheral hardware clock (fPRS) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when 1.8 V ≤ VDD < 2.7 V, the setting of TPS63 = TPS62 = TPS61 = TPS60 = 0 (base clock: fPRS) is prohibited.</li>

- **3.** When selecting the TM50 output as the base clock. Start the operation of 8-bit timer/event counter 50 first and then enable the timer F/F inversion operation (TMC501 = 1).

#### Caution Make sure POWER6 = 0 when rewriting TPS63 to TPS60.

**Remark** fprs: Peripheral hardware clock frequency

# (2) Error of baud rate

The baud rate error can be calculated by the following expression.

- Error (%) =  $\left(\frac{\text{Actual baud rate (baud rate with error)}}{\text{Desired baud rate (correct baud rate)}} 1\right) \times 100 [\%]$

- Cautions 1. Keep the baud rate error during transmission to within the permissible error range at the reception destination.

- 2. Make sure that the baud rate error during reception satisfies the range shown in (4) Permissible baud rate range during reception.

- Example: Frequency of base clock = 10 MHz = 10,000,000 Hz Set value of MDL67 to MDL60 bits of BRGC6 register = 00100001B (k = 33) Target baud rate = 153600 bps

Baud rate = 10 M / (2 × 33) = 10000000 / (2 × 33) = 151,515 [bps]

Error = (151515/153600 - 1) × 100 = -1.357 [%]

# 16.3 Registers Controlling Manchester Code Generator

The following six types of registers are used to control the Manchester code generator.

- MCG control register 0 (MC0CTL0)

- MCG control register 1 (MC0CTL1)

- MCG control register 2 (MC0CTL2)

- MCG status register (MC0STR)

- Port mode register 3 (PM3)

- Port register 3 (P3)

# (1) MCG control register 0 (MC0CTL0)

This register is used to set the operation mode and to enable/disable the operation. This register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 10H.

# Figure 16-4. Format of MCG Control Register 0 (MC0CTL0)

| Address: FF4 | After res | set: 10H | R/W |        |   |   |        |        |

|--------------|-----------|----------|-----|--------|---|---|--------|--------|

| Symbol       | <7>       | 6        | 5   | <4>    | 3 | 2 | <1>    | <0>    |

| MC0CTL0      | MC0PWR    | 0        | 0   | MC0DIR | 0 | 0 | MC0OSL | MC00LV |

| MC0PWR | Operation control |

|--------|-------------------|

| 0      | Operation stopped |

| 1      | Operation enabled |

| MC0DIR | First bit specification |

|--------|-------------------------|

| 0      | MSB                     |

| 1      | LSB                     |

| MC0OSL | Data format         |

|--------|---------------------|

| 0      | Manchester code     |

| 1      | Bit sequential data |

| MC00LV | Output level when transmission suspended |

|--------|------------------------------------------|

| 0      | Low level                                |

| 1      | High level                               |

Caution Clear (0) the MC0PWR bit before rewriting the MC0DIR, MC0OSL, and MC0OLV bits (it is possible to rewrite these bits by an 8-bit memory manipulation instruction at the same time when the MC0PWR bit is set (1)).

# (2) MCG control register 1 (MC0CTL1)

This register is used to set the base clock of the Manchester code generator. This register can be set by an 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

# Figure 16-5. Format of MCG Control Register 1 (MC0CTL1)

| Address: FF4DH Afte |   | eset: 00H | R/W |   |   |         |         |         |

|---------------------|---|-----------|-----|---|---|---------|---------|---------|

| Symbol              | 7 | 6         | 5   | 4 | 3 | 2       | 1       | 0       |

| MC0CTL1             | 0 | 0         | 0   | 0 | 0 | MC0CKS2 | MC0CKS1 | MC0CKS0 |

| MC0CKS2 | MC0CKS1 | MC0CKS0 | Base clock (fxcLK) selection <sup>Note 1</sup> |

|---------|---------|---------|------------------------------------------------|

| 0       | 0       | 0       | fprs <sup>Note 2</sup> (10 MHz)                |

| 0       | 0       | 1       | fprs/2 (5 MHz)                                 |

| 0       | 1       | 0       | f <sub>PRS</sub> /2 <sup>2</sup> (2.5 MHz)     |

| 0       | 1       | 1       | fprs/2 <sup>3</sup> (1.25 MHz)                 |

| 1       | 0       | 0       | f <sub>PRS</sub> /2 <sup>4</sup> (625 kHz)     |

| 1       | 0       | 1       | fprs/2 <sup>5</sup> (312.5 kHz)                |

| 1       | 1       | 0       | Setting prohibited                             |

| 1       | 1       | 1       |                                                |

**Notes 1.** If the peripheral hardware clock (fPRS) operates on the high-speed system clock (fXH) (XSEL = 1), the fPRS operating frequency varies depending on the supply voltage.

- VDD = 2.7 to 5.5 V: fPRs  $\leq$  10 MHz

- VDD = 1.8 to 2.7 V: fprs  $\leq$  5 MHz

- 2. If the peripheral hardware clock (fPRs) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when 1.8 V ≤ VDD < 2.7 V, the setting of MC0CKS2 = MC0CKS1 = MC0CKS0 = 0 (base clock: fPRs) is prohibited.</p>

# Caution Clear bit 7 (MC0PWR) of the MC0CTL0 register to 0 before rewriting the MC0CKS2 to MC0CKS0 bits.

#### Remarks 1. fprs: Peripheral hardware clock frequency

2. Figures in parentheses are for operation with fPRs = 10 MHz.

#### (b) Release by reset signal generation

When the reset signal is generated, HALT mode is released, and then, as in the case with a normal reset operation, the program is executed after branching to the reset vector address.

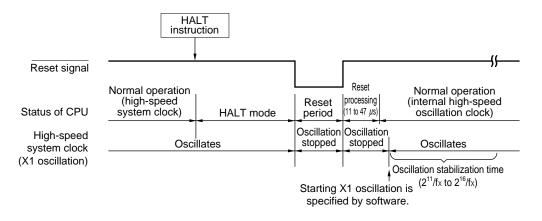

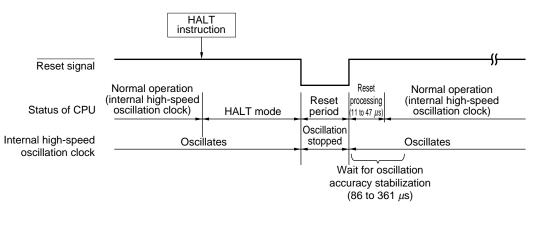

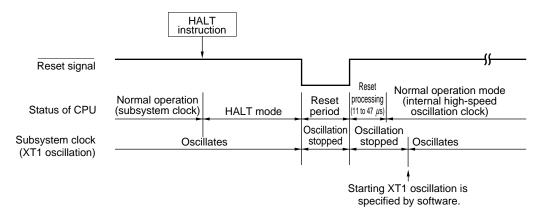

Figure 19-4. HALT Mode Release by Reset

#### (1) When high-speed system clock is used as CPU clock

#### (2) When internal high-speed oscillation clock is used as CPU clock

#### (3) When subsystem clock is used as CPU clock

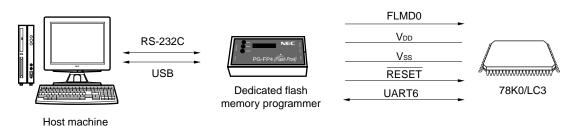

# 24.2 Writing with Flash memory programmer

Data can be written to the flash memory on-board or off-board, by using a dedicated flash memory programmer.

# (1) On-board programming

The contents of the flash memory can be rewritten after the 78K0/LC3 has been mounted on the target system. The connectors that connect the dedicated flash memory programmer must be mounted on the target system.

# (2) Off-board programming

Data can be written to the flash memory with a dedicated program adapter (FA series) before the 78K0/LC3 is mounted on the target system.

Remark The FA series is a product of Naito Densei Machida Mfg. Co., Ltd.

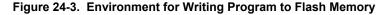

| Pin Configuration | of Dedicated | With UART               | 6                       |         |  |

|-------------------|--------------|-------------------------|-------------------------|---------|--|

| Signal Name       | I/O          | Pin Function            | Pin Name                | Pin No. |  |

| SI/RxD            | Input        | Receive signal          | TxD6/SEG6/P112          | 24      |  |

| SO/TxD            | Output       | Transmit signal         | RxD6/SEG7/P113          | 23      |  |

| SCK               | Output       | Transfer clock          | _                       | -       |  |

| CLK               | Output       | Clock to 78K0/LC3       | Note 1                  | Note 1  |  |

| /RESET            | Output       | Reset signal            | RESET                   | 6       |  |

| FLMD0             | Output       | Mode signal             | FLMD0                   | 9       |  |

| VDD               | I/O          | VDD voltage generation/ | VDD                     | 14      |  |

|                   |              | power monitoring        | VDD <sup>Note 2</sup>   | 35      |  |

|                   |              |                         | AVREF <sup>Note 3</sup> |         |  |

| GND               | -            | Ground                  | Vss                     | 13      |  |

|                   |              |                         | Vss <sup>Note 2</sup>   | 36      |  |

|                   |              |                         | AVss <sup>Note 3</sup>  |         |  |

Table 24-2. Wiring Between 78K0/LC3 and Dedicated Flash memory programmer

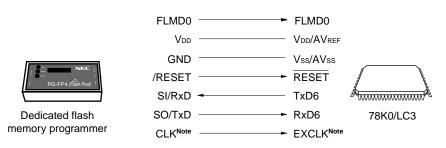

- **Notes 1.** Only the X1 clock (fx) or external main system clock (fEXCLK) can be used when UART6 is used. When using the clock output of the dedicated flash memory programmer, pin connection varies depending on the type of the dedicated flash memory programmer used.

- PG-FP4, FL-PR4: Connect CL

- PR4: Connect CLK of the programmer to EXCLK/X2/P122 (pin 10).

- PG-FPL3, FP-LITE3: Connect CLK of the programmer to X1/P121 (pin 11), and connect its inverted signal to X2/EXCLK/P122 (pin 10).

- **2.** μPD78F040x only.

- **3.** *μ*PD78F041x only.

# 24.3 Programming Environment

The environment required for writing a program to the flash memory of the 78K0/LC3 is illustrated below.

A host machine that controls the dedicated flash memory programmer is necessary.

To interface between the dedicated flash memory programmer and the 78K0/LC3, UART6 is used for manipulation such as writing and erasing. To write the flash memory off-board, a dedicated program adapter (FA series) is necessary.

#### 24.4 Communication Mode

Communication between the dedicated flash memory programmer and the 78K0/LC3 is established by serial communication via UART6 of the 78K0/LC3.

#### • UART6

Transfer rate: 115200 bps

**Note** The above figure illustrates an example of wiring when using the clock output from the PG-FP4 or FL-PR4. When using the clock output from the PG-FPL3 or FP-LITE3, connect CLK to X1/P121, and connect its inverted signal to X2/EXCLK/P122.

Caution Only the bottom side pins (pin numbers 23 and 24) correspond to the UART6 pins (RxD6 and TxD6) when writing by a flash memory programmer. Writing cannot be performed by the top side pins (pin numbers 48 and 47).

Standard products

# DC Characteristics (4/5) (T<sub>A</sub> = -40 to +85°C, 1.8 V $\leq$ V<sub>DD</sub> $\leq$ 5.5 V, AV<sub>REF</sub> $\leq$ V<sub>DD</sub>, V<sub>SS</sub> = AV<sub>SS</sub> = 0 V)

| Parameter      | Symbol                 |                | Conditions                                                                   |                      | MIN. | TYP. | MAX. | Unit |

|----------------|------------------------|----------------|------------------------------------------------------------------------------|----------------------|------|------|------|------|

| Supply current | IDD1                   | Operating mode | $f_{XH} = 10 \text{ MHz}^{\text{Note 2}},$                                   | Square wave input    |      | 1.6  | 3.0  | mA   |

| Note 1         |                        |                | V <sub>DD</sub> = 5.0 V                                                      | Resonator connection |      | 2.3  | 3.4  |      |

|                |                        |                | $f_{XH} = 10 \text{ MHz}^{\text{Note 2}},$                                   | Square wave input    |      | 1.5  | 2.9  | mA   |

|                |                        |                | V <sub>DD</sub> = 3.0 V                                                      | Resonator connection |      | 2.2  | 3.3  |      |

|                |                        |                | f <sub>XH</sub> = 5 MHz <sup>Note 2</sup> ,                                  | Square wave input    |      | 0.9  | 1.7  | mA   |

|                |                        |                | V <sub>DD</sub> = 3.0 V                                                      | Resonator connection |      | 1.3  | 2.0  |      |

|                |                        |                | f <sub>XH</sub> = 5 MHz <sup>Note 2</sup> ,                                  | Square wave input    |      | 0.7  | 1.4  | mA   |

|                |                        |                | V <sub>DD</sub> = 2.0 V                                                      | Resonator connection |      | 1.0  | 1.6  |      |

|                |                        |                | $f_{RH}$ = 8 MHz, V_{DD} = 5.0 V <sup>Note 3</sup>                           |                      |      | 1.4  | 2.3  | mA   |

|                |                        |                | f <sub>SUB</sub> = 32.768 kHz <sup>Note 4</sup> ,<br>V <sub>DD</sub> = 5.0 V | Resonator connection |      | 6.7  | 26   | μA   |

|                | Idd2 HAL               | HALT mode      | f <sub>XH</sub> = 10 MHz <sup>Note 2</sup> ,                                 | Square wave input    |      | 0.4  | 1.4  | mA   |

|                |                        |                | V <sub>DD</sub> = 5.0 V                                                      | Resonator connection |      | 1.0  | 1.7  |      |

|                |                        |                | f <sub>XH</sub> = 5 MHz <sup>Note 2</sup> ,                                  | Square wave input    |      | 0.2  | 0.7  | mA   |

|                |                        |                | V <sub>DD</sub> = 3.0 V                                                      | Resonator connection |      | 0.5  | 1.0  |      |

|                |                        |                | frh = 8 MHz, VDD = 5.0 \                                                     | /Note 3              |      | 0.4  | 1.2  | mA   |

|                |                        |                | f <sub>SUB</sub> = 32.768 kHz <sup>Note 4</sup> ,<br>V <sub>DD</sub> = 5.0 V | Resonator connection |      | 2.4  | 22   | μA   |

|                | IDD3 <sup>Note 5</sup> | STOP mode      | V <sub>DD</sub> = 5.0 V                                                      |                      |      | 1    | 20   | μA   |

|                |                        |                | V <sub>DD</sub> = 5.0 V, T <sub>A</sub> = -40 to +70°C                       |                      |      | 1    | 10   | μA   |

**Notes 1.** Total current flowing into the internal power supply (VDD), including the peripheral operation current and the input leakage current flowing when the level of the input pin is fixed to VDD or VSS. However, the current flowing into the pull-up resistors and the output current of the port are not included.

- 2. Not including the operating current of the 8 MHz internal oscillator, 240 kHz internal oscillator and XT1 oscillation, and the current flowing into the A/D converter, watchdog timer, LVI circuit and LCD controller/driver.

- **3.** Not including the operating current of the X1 oscillation, XT1 oscillation and 240 kHz internal oscillator, and the current flowing into the A/D converter, watchdog timer, LVI circuit and LCD controller/driver.

- 4. Not including the operating current of the X1 oscillation, 8 MHz internal oscillator and 240 kHz internal oscillator, and the current flowing into the A/D converter, watchdog timer, LVI circuit and LCD controller/driver.

- **5.** Not including the operating current of the 240 kHz internal oscillator and XT1 oscillation, and the current flowing into the A/D converter, watchdog timer, LVI circuit and LCD controller/driver.

- **Remarks 1.** fxH: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. free: Internal high-speed oscillation clock frequency

- **3.** fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

# Standard products

|              | Parameter                               | Symbol         | Conditions                                 | MIN. | TYP. | MAX. | Unit |

|--------------|-----------------------------------------|----------------|--------------------------------------------|------|------|------|------|

| Detection    |                                         | VLVIO          |                                            | 4.14 | 4.24 | 4.34 | V    |

| voltage      |                                         | VLVI1          |                                            | 3.99 | 4.09 | 4.19 | V    |

|              |                                         | VLVI2          |                                            | 3.83 | 3.93 | 4.03 | V    |

|              |                                         | VLVI3          |                                            | 3.68 | 3.78 | 3.88 | V    |

|              |                                         | VLVI4          |                                            | 3.52 | 3.62 | 3.72 | V    |

|              |                                         | VLVI5          |                                            | 3.37 | 3.47 | 3.57 | V    |

|              |                                         | VLVI6          |                                            | 3.22 | 3.32 | 3.42 | V    |

|              |                                         | VLVI7          |                                            | 3.06 | 3.16 | 3.26 | V    |

|              |                                         | VLVI8          |                                            | 2.91 | 3.01 | 3.11 | V    |

|              |                                         | VLVI9          |                                            | 2.75 | 2.85 | 2.95 | V    |

|              |                                         | VLVI10         |                                            | 2.60 | 2.70 | 2.80 | V    |

|              |                                         | VLVI11         |                                            | 2.45 | 2.55 | 2.65 | V    |

|              |                                         | VLVI12         |                                            | 2.29 | 2.39 | 2.49 | V    |

|              |                                         | VLVI13         |                                            | 2.14 | 2.24 | 2.34 | V    |

|              |                                         | VLVI14         |                                            | 1.98 | 2.08 | 2.18 | V    |

|              |                                         | VLVI15         |                                            | 1.83 | 1.93 | 2.03 | V    |

|              | External input pin <sup>Note 1</sup>    | EXLVI          | EXLVI < VDD, 1.8 V $\leq$ VDD $\leq$ 5.5 V | 1.11 | 1.21 | 1.31 | V    |

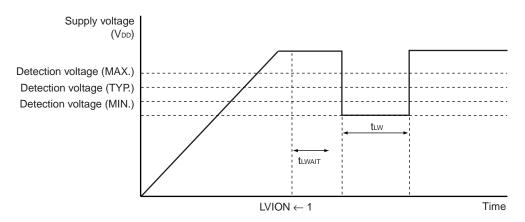

| Minimum pu   | Ilse width                              | t∟w            |                                            | 200  |      |      | μs   |

| Operation st | abilization wait time <sup>Note 2</sup> | <b>t</b> lwait |                                            |      |      | 10   | μs   |

# LVI Circuit Characteristics (T<sub>A</sub> = -40 to +85°C, $V_{POC} \le V_{DD} \le 5.5 \text{ V}$ , $V_{SS} = 0 \text{ V}$ )

Notes 1. The EXLVI/P120/INTP0 pin is used.

2. Time required from setting bit 7 (LVION) of the low-voltage detection register (LVIM) to 1 to operation stabilization.

**Remark**  $V_{LVI(n-1)} > V_{LVIn}$ : n = 1 to 15

# LVI Circuit Timing

Standard products

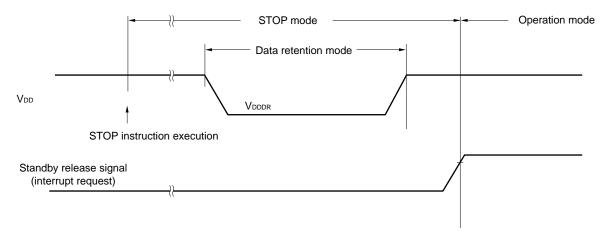

### Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics (T<sub>A</sub> = -40 to +85°C)

| Parameter                     | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-------------------------------|--------|------------|----------------------|------|------|------|

| Data retention supply voltage | VDDDR  |            | 1.44 <sup>Note</sup> |      | 5.5  | V    |

# **Note** The value depends on the POC detection voltage. When the voltage drops, the data is retained until a POC reset is effected, but data is not retained when a POC reset is effected.

# Flash Memory Programming Characteristics (T<sub>A</sub> = -40 to +85°C, 2.7 V $\leq$ V<sub>DD</sub> $\leq$ 5.5 V, V<sub>SS</sub> = AV<sub>SS</sub> = 0 V)

#### Basic characteristics

| Parameter                    |            | Symbol | Conditions                                                                         | MIN. | TYP. | MAX. | Unit  |

|------------------------------|------------|--------|------------------------------------------------------------------------------------|------|------|------|-------|

| VDD supply current           |            | Idd    |                                                                                    |      | 4.5  | 11.0 | mA    |

| Erase time <sup>Note 1</sup> | All block  | Teraca |                                                                                    |      | 20   | 200  | ms    |

|                              | Block unit | Terasa |                                                                                    |      | 20   | 200  | ms    |

| Write time (in 8-bit units)  |            | Twrwa  |                                                                                    |      | 10   | 100  | μs    |

| Number of rewrites per chip  |            | Cerwr  | Retention: 15 years<br>1 erase + 1 write after erase = 1 rewrite <sup>Note 2</sup> | 1000 |      |      | Times |

Notes 1. The prewrite time before erasure and the erase verify time (writeback time) are not included.

2. When a product is first written after shipment, "erase → write" and "write only" are both taken as one rewrite.

**Remark** fxp: Main system clock oscillation frequency