# E. Renesas Electronics America Inc - UPD78F0403GA-GAM-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | LINbus, UART/USART                                                                   |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 30                                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | -                                                                                    |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 48-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0403ga-gam-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Description of Pin Functions

# 2.2.1 P12, P13 (port 1)

P12 and P13 function as a 2-bit I/O port. These pins also function as pins for key interrupt and serial interface data I/O. P13 can be selected to function as pins, using port function register 1 (PF1) (see Figure 4-19).

The following operation modes can be specified in 1-bit units.

## (1) Port mode

P12 and P13 function as a 2-bit I/O port. P12 and P13 can be set to input or output port in 1-bit units using port mode register 1 (PM1). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 1 (PU1).

#### (2) Control mode

P12 and P13 function as key interrupt and serial interface data I/O.

#### (a) KR3, KR4

These are key interrupt input pins.

## (b) RxD0, RxD6

These are the serial data input pins of the asynchronous serial interface.

#### (c) TxD0, TxD6

These are the serial data output pins of the asynchronous serial interface.

# 2.2.2 P20 to P25 (port 2)

P20 to P25 function as a 6-bit I/O port. These pins also function as pins for segment signal output pins for the LCD controller/driver, 10-bit successive approximation type A/D converter analog input ( $\mu$ PD78F041x only). Either I/O port function or segment signal output function can be selected using port function register 2 (PF2).

The following operation modes can be specified in 1-bit units.

#### (1) Port mode

P20 to P25 function as a 6-bit I/O port. P20 to P25 can be set to input or output port in 1-bit units using port mode register 2 (PM2).

## (2) Control mode

P20 to P25 function as segment signal output for the LCD controller/driver and 10-bit successive approximation type A/D converter analog input ( $\mu$ PD78F041x only).

## (a) SEG16 to SEG21

These pins are the segment signal output pins for the LCD controller/driver.

# (b) ANI0 to ANI5 (µPD78F041x only)

These are 10-bit successive approximation type A/D converter analog input pins. When using these pins as analog input pins, see (5) ANI0/SEG21/P20 to ANI5/SEG16/P25 pins in 12.6 Cautions for 10-bit successive approximation type A/D Converter.

## Caution P20 to P25 are set in the digital input mode after release of reset.

# (1) Port mode

P140 to P143 function as a 4-bit I/O port. P140 to P143 can be set to input or output port in 1-bit units using port mode register 14 (PM14). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 14 (PU14).

# (2) Control mode

P140 to P143 function as segment signal output pins for the LCD controller/driver.

## (a) SEG8 to SEG11

These pins are the segment signal output pins for the LCD controller/driver.

# 2.2.9 P150 to P153 (port 15)

P150 to P153 function as a 4-bit I/O port. These pins also function as pins for segment signal output pins for the LCD controller/driver. Either I/O port function or segment signal output function can be selected using port function register ALL (PFALL).

## (1) Port mode

P150 to P153 function as a 4-bit I/O port. P150 to P153 can be set to input or output port in 1-bit units using port mode register 15 (PM15). Use of an on-chip pull-up resistor can be specified by pull-up resistor option register 15 (PU15).

#### (2) Control mode

P150 to P153 function as segment signal output for the LCD controller/driver.

## (a) SEG12 to SEG15

These pins are the segment signal output pins for the LCD controller/driver.

#### 2.2.10 AVREF (µPD78F041x only)

This is the 10-bit successive approximation type A/D converter reference voltage input pin and the positive power supply pin of port 2.

When the A/D converter is not used, connect this pin directly to  $V_{DD}^{Note}$ .

**Note** When one or more of the pins of port 2 is used as the digital port pins or for segment output, make AV<sub>REF</sub> the same potential as V<sub>DD</sub>.

## 2.2.11 AVss (µPD78F041x only)

This is the A/D converter ground potential pin. Even when the A/D converter is not used, always use this pin with the same potential as the Vss pin.

## 2.2.12 COM0 to COM7

These pins are the common signal output pins for the LCD controller/driver.

# 2.2.13 VLC0 to VLC3

These pins are the power supply voltage pins for driving the LCD.

## 2.2.14 RESET

This is the active-low system reset input pin.

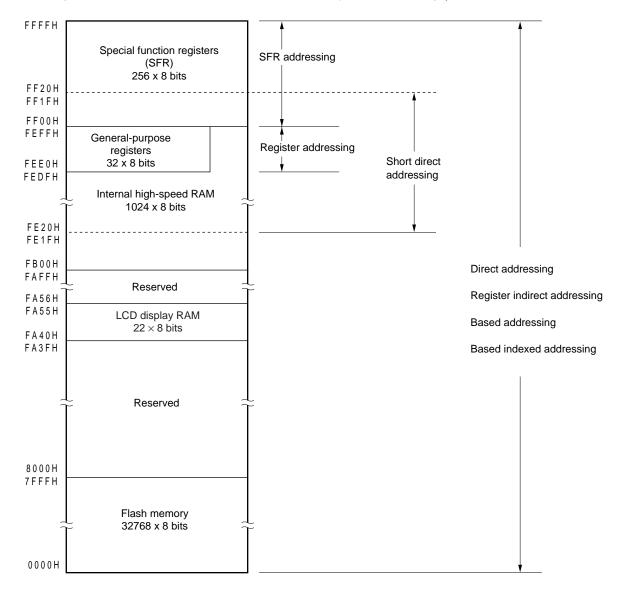

Figure 3-8. Correspondence Between Data Memory and Addressing (µPD78F0403, 78F0413)

# 3.4 Operand Address Addressing

The following methods are available to specify the register and memory (addressing) to undergo manipulation during instruction execution.

# 3.4.1 Implied addressing

# [Function]

The register that functions as an accumulator (A and AX) among the general-purpose registers is automatically (implicitly) addressed.

Of the 78K0/LC3 instruction words, the following instructions employ implied addressing.

| Instruction                                                                                 | Register to Be Specified by Implied Addressing                     |  |  |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

| MULU A register for multiplicand and AX register for product storage                        |                                                                    |  |  |

| DIVUW AX register for dividend and quotient storage                                         |                                                                    |  |  |

| ADJBA/ADJBS A register for storage of numeric values that become decimal correction targets |                                                                    |  |  |

| ROR4/ROL4                                                                                   | A register for storage of digit data that undergoes digit rotation |  |  |

## [Operand format]

Because implied addressing can be automatically determined with an instruction, no particular operand format is necessary.

## [Description example]

In the case of MULU X

With an 8-bit  $\times$  8-bit multiply instruction, the product of the A register and X register is stored in AX. In this example, the A and AX registers are specified by implied addressing.

# 4.3 Registers Controlling Port Function

Port functions are controlled by the following seven types of registers.

- Port mode registers (PM1 to PM4, PM10 to PM12, PM14, PM15)

- Port registers (P1 to P4, P10 to P12, P14, P15)

- Pull-up resistor option registers (PU1, PU3, PU4, PU10 to PU12, PU14, PU15)

- Port function register 1 (PF1)

- Port function register 2 (PF2)

- Port function register ALL (PFALL)

- A/D port configuration register 0 (ADPC0)<sup>Note</sup>

**Note** μPD78F041x only

# (1) Port mode registers (PM1 to PM4, PM10 to PM12, PM14, PM15)

These registers specify input or output mode for the port in 1-bit units.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

When port pins are used as alternate-function pins, set the port mode register by referencing **4.5** Settings of Port Mode Register and Output Latch When Using Alternate Function.

| Symbol | 7    | 6                                          | 5           | 4    | 3     | 2     | 1     | 0     | Address | After reset | R/W |

|--------|------|--------------------------------------------|-------------|------|-------|-------|-------|-------|---------|-------------|-----|

| PM1    | 1    | 1                                          | 1           | 1    | PM13  | PM12  | 1     | 1     | FF21H   | FFH         | R/W |

|        |      |                                            |             |      |       |       |       |       |         |             |     |

| PM2    | 1    | 1                                          | PM25        | PM24 | PM23  | PM22  | PM21  | PM20  | FF22H   | FFH         | R/W |

|        |      |                                            |             |      |       |       |       |       |         |             |     |

| PM3    | 1    | 1                                          | 1           | PM34 | PM33  | PM32  | PM31  | 1     | FF23H   | FFH         | R/W |

|        |      |                                            |             |      |       |       |       |       |         |             |     |

| PM4    | 1    | 1                                          | 1           | 1    | 1     | 1     | 1     | PM40  | FF24H   | FFH         | R/W |

|        |      |                                            |             | 1    | 1     |       | 1     |       |         |             |     |

| PM10   | 1    | 1                                          | 1           | 1    | 1     | 1     | PM101 | PM100 | FF2AH   | FFH         | R/W |

|        |      |                                            |             |      |       |       |       |       | L       |             |     |

| PM11   | 1    | 1                                          | 1           | 1    | PM113 | PM112 | 1     | 1     | FF2BH   | FFH         | R/W |

|        |      |                                            |             |      | 1     |       |       |       |         |             |     |

| PM12   | 1    | 1                                          | 1           | 1    | 1     | 1     | 1     | PM120 | FF2CH   | FFH         | R/W |

|        |      |                                            |             | 1    |       |       |       |       |         |             |     |

| PM14   | 1    | 1                                          | 1           | 1    | PM143 | PM142 | PM141 | PM140 | FF2EH   | FFH         | R/W |

|        |      |                                            | 1           |      |       |       |       |       |         |             |     |

| PM15   | 1    | 1                                          | 1           | 1    | PM153 | PM152 | PM151 | PM150 | FF2FH   | FFH         | R/W |

|        | r    |                                            |             |      |       |       |       |       |         |             |     |

|        | PMmn |                                            |             |      |       |       |       |       |         |             |     |

|        |      | (m = 1 to 4, 10 to 12, 14, 15; n = 0 to 5) |             |      |       |       |       |       |         |             |     |

|        | 0    | •                                          | node (outpu |      | 1)    |       |       |       |         |             |     |

|        | 1    | Input mode (output buffer off)             |             |      |       |       |       |       |         |             |     |

# Figure 4-16. Format of Port Mode Register

Caution Be sure to set bits 0, 1, and 4 to 7 of PM1, bits 6 and 7 of PM2, bits 0, and 5 to 7 of PM3, bits 1 to 7 of PM4, bits 2 to 7 of PM10, bits 0, 1, and 4 to 7 of PM11, bits 1 to 7 of PM12, bits 4 to 7 of PM14, and bits 4 to 7 of PM15 to "1".

## Figure 6-52. Example of Register Settings for Pulse Width Measurement (2/2)

# (e) 16-bit timer counter 00 (TM00)

By reading TM00, the count value can be read.

# (f) 16-bit capture/compare register 000 (CR000)

This register is used as a capture register. Either the TI000 or TI010 pin is selected as a capture trigger. When a specified edge of the capture trigger is detected, the count value of TM00 is stored in CR000.

# (g) 16-bit capture/compare register 010 (CR010)

This register is used as a capture register. The signal input to the TI000 pin is used as a capture trigger. When the capture trigger is detected, the count value of TM00 is stored in CR010.

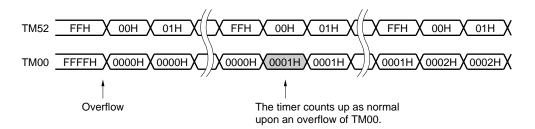

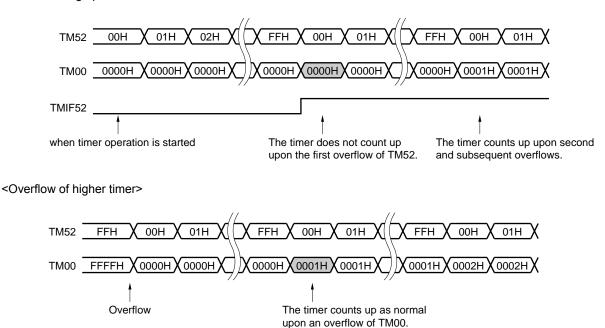

# (2) Cautions for input enable control for TI52 pin

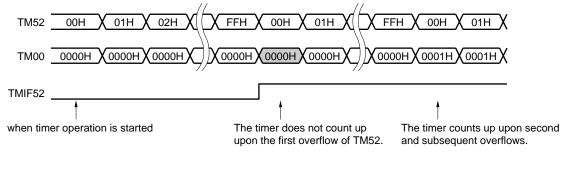

The input enable control signal (TMH2 output signal) for the TI52 pin is synchronized by the TI52 pin input clock, as described in Figure 6-54 Configuration Diagram of External 24-bit Event Counter and Figure 6-55 Operation Timing of External 24-bit Event Counter. Thus, when the counter is operated as an external event counter, an error up to one count may be caused.

# (3) Cautions for 16-bit timer/event counter 00 count up during external 24-bit event counter operation

16-bit timer/event counter 00 has an internal synchronization circuit to eliminate noise when starting operation, and the first clock immediately after operation start is not counted.

When using the counter as a 24-bit counter, by setting 16-bit timer/event counter 00 and 8-bit timer/event counter 52 as the higher and lower timer and connecting them in cascade, the interrupt request flag of 8-bit timer/event counter 52 which is the lower timer must be checked as described below, in order to accurately read the 24-bit count values.

- If TMIF52 = 1 when TM52 and TM00 are read:

The actual TM00 count value is "read value of TM00 + 1".

- If TMIF52 = 0 when TM52 and TM00 are read:

The read value is the correct value.

This phenomenon of 16-bit timer/event counter 00 occurs only when operation is started. A count delay will not occur when 16-bit timer/event counter 00 overflows and the count is restarted from 0000H, since synchronization has already been implemented.

<When starting operation>

<When starting operation>

Internal bus 8-bit timer H mode register 0 (TMHMD0) TMHE0 CKS02 CKS01 CKS00 TMMD01 TMMD00 TOLEV0 TOEN0 8-bit timer H 8-bit timer H compare register 10 (CMP10) compare register 00 (CMP00) ∕3 *1*2 TOH0 output - TOH0/P32/MCGO Decoder Selector Output latch (P32) F/F PM32 Output Match Interrupt generator Level controller inversion R **f**PRS fprs/2 Selector 8-bit timer fprs/2<sup>2</sup> counter H0 fprs/2<sup>6</sup> fprs/2<sup>10</sup> Clear 8-bit timer/ event counter 50 output PWM mode signal Timer H enable signal ► INTTMH0

CHAPTER 8 8-BIT TIMERS H0, H1, AND H2

#### Figure 8-7. Format of 8-Bit Timer H Mode Register 1 (TMHMD1)

Address: FF6CH After reset: 00H R/W

TMHMD1

<7>

6

5

4

3

2

<1>

<0>

TMHE1

CKS12

CKS11

CKS10

TMMD11

TMMD10

TOLEV1

TOEN1

| TMHE1 | Timer operation enable                                                     |

|-------|----------------------------------------------------------------------------|

| 0     | Stops timer count operation (counter is cleared to 0)                      |

| 1     | Enables timer count operation (count operation started by inputting clock) |

| CKS12 | CKS11 | CKS10 | Count clock selection <sup>Note 1</sup> |                             |                 |                              |  |

|-------|-------|-------|-----------------------------------------|-----------------------------|-----------------|------------------------------|--|

|       |       |       |                                         | f <sub>PRS</sub> =<br>2 MHz | fprs =<br>5 MHz | f <sub>PRS</sub> =<br>10 MHz |  |

| 0     | 0     | 0     | fprs <sup>Note 2</sup>                  | 2 MHz                       | 5 MHz           | 10 MHz                       |  |

| 0     | 0     | 1     | fprs/2 <sup>2</sup>                     | 500 kHz                     | 1.25 MHz        | 2.5 MHz                      |  |

| 0     | 1     | 0     | fprs/2 <sup>4</sup>                     | 125 kHz                     | 312.5 kHz       | 625 kHz                      |  |

| 0     | 1     | 1     | fprs/2 <sup>6</sup>                     | 31.25 kHz                   | 78.13 kHz       | 156.25 kHz                   |  |

| 1     | 0     | 0     | fprs/2 <sup>12</sup>                    | 0.49 kHz                    | 1.22 kHz        | 2.44 kHz                     |  |

| 1     | 0     | 1     | frl/2 <sup>7</sup>                      | 1.88 kHz (TYP.)             |                 |                              |  |

| 1     | 1     | 0     | frl/2 <sup>9</sup>                      | 0.47 kHz (TYP.)             |                 |                              |  |

| 1     | 1     | 1     | frl                                     | 240 kHz (TYP.)              |                 |                              |  |

| TMMD11 | TMMD10 | Timer operation mode   |  |  |  |

|--------|--------|------------------------|--|--|--|

| 0      | 0      | Interval timer mode    |  |  |  |

| 0      | 1      | Carrier generator mode |  |  |  |

| 1      | 0      | PWM output mode        |  |  |  |

| 1      | 1      | Setting prohibited     |  |  |  |

| TOLEV1 | Timer output level control (in default mode) |

|--------|----------------------------------------------|

| 0      | Low level                                    |

| 1      | High level                                   |

| TOEN1 | Timer output control |  |  |  |

|-------|----------------------|--|--|--|

| 0     | Disables output      |  |  |  |

| 1     | Enables output       |  |  |  |

# **Notes 1.** If the peripheral hardware clock (fPRs) operates on the high-speed system clock (fXH) (XSEL = 1), the fPRs operating frequency varies depending on the supply voltage.

- Vdd = 2.7 to 5.5 V: fprs  $\leq$  10 MHz

- VDD = 1.8 to 2.7 V: fPRs  $\leq$  5 MHz

- If the peripheral hardware clock (fPRS) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when 1.8 V ≤ VDD < 2.7 V, the setting of CKS12 = CKS11 = CKS10 = 0 (count clock: fPRS) is prohibited.</li>

# 12.3 Registers Used in 10-Bit Successive Approximation Type A/D Converter

The A/D converter uses the following seven registers.

- A/D converter mode register (ADM)

- A/D port configuration register 0 (ADPC0)

- Analog input channel specification register (ADS)

- Port function register 2 (PF2)

- Port mode register 2 (PM2)

- 10-bit A/D conversion result register (ADCR)

- 8-bit A/D conversion result register (ADCRH)

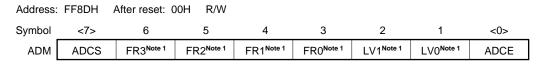

# (1) A/D converter mode register (ADM)

This register sets the conversion time for analog input to be A/D converted, and starts/stops conversion. ADM can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

# Figure 12-3. Format of A/D Converter Mode Register (ADM)

| ADCS | A/D conversion operation control |  |  |  |  |

|------|----------------------------------|--|--|--|--|

| 0    | Stops conversion operation       |  |  |  |  |

| 1    | Enables conversion operation     |  |  |  |  |

| ADCE | Comparator operation control <sup>Note 2</sup> |  |  |  |

|------|------------------------------------------------|--|--|--|

| 0    | Stops comparator operation                     |  |  |  |

| 1    | Enables comparator operation                   |  |  |  |

- Notes 1. For details of FR3 to FR0, LV1, LV0, and A/D conversion, see Table 12-2 A/D Conversion Time Selection.

- 2. The operation of the comparator is controlled by ADCS and ADCE, and it takes 1  $\mu$ s from operation start to operation stabilization. Therefore, when ADCS is set to 1 after 1  $\mu$ s or more has elapsed from the time ADCE is set to 1, the conversion result at that time has priority over the first conversion result. Otherwise, ignore data of the first conversion.

| ADCS | ADCE | A/D Conversion Operation                                                       |  |  |  |

|------|------|--------------------------------------------------------------------------------|--|--|--|

| 0    | 0    | top status (DC power consumption path does not exist)                          |  |  |  |

| 0    | 1    | Conversion waiting mode (comparator operation, only comparator consumes power) |  |  |  |

| 1    | 0    | Conversion mode (comparator operation stopped <sup>Note</sup> )                |  |  |  |

| 1    | 1    | Conversion mode (comparator operation)                                         |  |  |  |

Table 12-1. Settings of ADCS and ADCE

**Note** Ignore data of the first conversion.

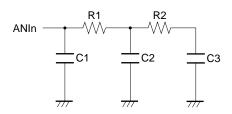

# (11) Internal equivalent circuit

The equivalent circuit of the analog input block is shown below.

# Figure 12-22. Internal Equivalent Circuit of ANIn Pin

Table 12-4. Resistance and Capacitance Values of Equivalent Circuit (Reference Values)

| AVREF | R1  | R2  | C1  | C2  | C3  |

|-------|-----|-----|-----|-----|-----|

| 2.7 V | TBD | TBD | TBD | TBD | TBD |

| 4.5 V | TBD | TBD | TBD | TBD | TBD |

Remarks 1. The resistance and capacitance values shown in Table 12-4 are not guaranteed values.2. n = 0 to 5

# (3) Baud rate generator control register 0 (BRGC0)

This register selects the base clock of serial interface UART0 and the division value of the 5-bit counter. BRGC0 can be set by an 8-bit memory manipulation instruction. Reset signal generation sets this register to 1FH.

## Figure 13-4. Format of Baud Rate Generator Control Register 0 (BRGC0)

Address: FF71H After reset: 1FH R/W

| Symbol | 7     | 6     | 5 | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|---|-------|-------|-------|-------|-------|

| BRGC0  | TPS01 | TPS00 | 0 | MDL04 | MDL03 | MDL02 | MDL01 | MDL00 |

| TPS01 | TPS00 | Base clock (fxCLK0) selection <sup>Note 1</sup> |                           |            |              |               |  |  |

|-------|-------|-------------------------------------------------|---------------------------|------------|--------------|---------------|--|--|

|       |       |                                                 | fprs = 2 MHz fprs = 5 MHz |            | fprs = 8 MHz | fprs = 10 MHz |  |  |

| 0     | 0     | TM50 output <sup>Note 2</sup>                   |                           |            |              |               |  |  |

| 0     | 1     | fprs/2                                          | 1 MHz                     | 2.5 MHz    | 4 MHz        | 5 MHz         |  |  |

| 1     | 0     | fprs/2 <sup>3</sup>                             | 250 kHz                   | 625 kHz    | 1 MHz        | 1.25 MHz      |  |  |

| 1     | 1     | fprs/2 <sup>5</sup>                             | 62.5 kHz                  | 156.25 kHz | 250 kHz      | 312.5 kHz     |  |  |

| MDL04 | MDL03 | MDL02 | MDL01 | MDL00 | k  | Selection of 5-bit counter<br>output clock |

|-------|-------|-------|-------|-------|----|--------------------------------------------|

| 0     | 0     | ×     | ×     | ×     | ×  | Setting prohibited                         |

| 0     | 1     | 0     | 0     | 0     | 8  | fxclko/8                                   |

| 0     | 1     | 0     | 0     | 1     | 9  | fxclko/9                                   |

| 0     | 1     | 0     | 1     | 0     | 10 | fxclko/10                                  |

| •     | •     | •     | •     | •     | •  | •                                          |

| •     | •     | •     | •     | •     | •  | •                                          |

| •     | •     | •     | •     | •     | •  | •                                          |

| •     | •     | •     | •     | •     | •  | •                                          |

| •     | •     | •     | •     | •     | •  | •                                          |

| 1     | 1     | 0     | 1     | 0     | 26 | fxclк0/26                                  |

| 1     | 1     | 0     | 1     | 1     | 27 | fxclko/27                                  |

| 1     | 1     | 1     | 0     | 0     | 28 | fxclk0/28                                  |

| 1     | 1     | 1     | 0     | 1     | 29 | fxclk0/29                                  |

| 1     | 1     | 1     | 1     | 0     | 30 | fxclк0/30                                  |

| 1     | 1     | 1     | 1     | 1     | 31 | fxclкo/31                                  |

**Notes 1.** If the peripheral hardware clock (fPRs) operates on the high-speed system clock (fXH) (XSEL = 1), the fPRs operating frequency varies depending on the supply voltage.

• VDD = 2.7 to 5.5 V: fPRs  $\leq$  10 MHz

• VDD = 1.8 to 2.7 V: fPRS  $\leq$  5 MHz

- **2.** When selecting the TM50 output as the base clock, Start the operation of 8-bit timer/event counter 50 first and then enable the timer F/F inversion operation (TMC501 = 1).

- Cautions 1. Make sure that bit 6 (TXE0) and bit 5 (RXE0) of the ASIM0 register = 0 when rewriting the MDL04 to MDL00 bits.

- 2. The baud rate value is the output clock of the 5-bit counter divided by 2.

# (b) Parity types and operation

The parity bit is used to detect a bit error in communication data. Usually, the same type of parity bit is used on both the transmission and reception sides. With even parity and odd parity, a 1-bit (odd number) error can be detected. With zero parity and no parity, an error cannot be detected.

## Caution Fix the PS61 and PS60 bits to 0 when the device is used in LIN communication operation.

# (i) Even parity

Transmission

Transmit data, including the parity bit, is controlled so that the number of bits that are "1" is even. The value of the parity bit is as follows.

If transmit data has an odd number of bits that are "1": 1 If transmit data has an even number of bits that are "1": 0

Reception

The number of bits that are "1" in the receive data, including the parity bit, is counted. If it is odd, a parity error occurs.

# (ii) Odd parity

Transmission

Unlike even parity, transmit data, including the parity bit, is controlled so that the number of bits that are "1" is odd.

If transmit data has an odd number of bits that are "1": 0 If transmit data has an even number of bits that are "1": 1

Reception

The number of bits that are "1" in the receive data, including the parity bit, is counted. If it is even, a parity error occurs.

# (iii) 0 parity

The parity bit is cleared to 0 when data is transmitted, regardless of the transmit data. The parity bit is not detected when the data is received. Therefore, a parity error does not occur regardless of whether the parity bit is "0" or "1".

#### (iv) No parity

No parity bit is appended to the transmit data.

Reception is performed assuming that there is no parity bit when data is received. Because there is no parity bit, a parity error does not occur.

# 17.4.4 Interrupt request hold

There are instructions where, even if an interrupt request is issued for them while another instruction is being executed, request acknowledgment is held pending until the end of execution of the next instruction. These instructions (interrupt request hold instructions) are listed below.

- MOV PSW, #byte

- MOV A, PSW

- MOV PSW, A

- MOV1 PSW. bit, CY

- MOV1 CY, PSW. bit

- AND1 CY, PSW. bit

- OR1 CY, PSW. bit

- XOR1 CY, PSW. bit

- SET1 PSW. bit

- CLR1 PSW. bit

- RETB

- RETI

- PUSH PSW

- POP PSW

- BT PSW. bit, \$addr16

- BF PSW. bit, \$addr16

- BTCLR PSW. bit, \$addr16

- El

- DI

- Manipulation instructions for the IF0L, IF0H, IF1L, IF1H, MK0L, MK0H, MK1L, MK1H, PR0L, PR0H, PR1L, and PR1H registers.

- Caution The BRK instruction is not one of the above-listed interrupt request hold instructions. However, the software interrupt activated by executing the BRK instruction causes the IE flag to be cleared. Therefore, even if a maskable interrupt request is generated during execution of the BRK instruction, the interrupt request is not acknowledged.

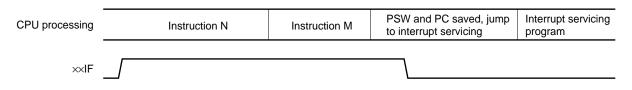

Figure 17-11 shows the timing at which interrupt requests are held pending.

## Figure 17-11. Interrupt Request Hold

Remarks 1. Instruction N: Interrupt request hold instruction

- 2. Instruction M: Instruction other than interrupt request hold instruction

- 3. The xxPR (priority level) values do not affect the operation of xxIF (interrupt request).

| HALT                                                               | Mode Setting   | When HALT Instruction Is Executed While CPU Is Operating on Main System Clock             |                                             |                                             |  |  |  |  |

|--------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------|--|--|--|--|

| Item                                                               |                | When CPU Is Operating on<br>Internal High-Speed<br>Oscillation Clock (fRH)                | X1 Clock (fx) External Main                 |                                             |  |  |  |  |

| System clock                                                       |                | Clock supply to the CPU is stopped                                                        |                                             |                                             |  |  |  |  |

| Main system c                                                      | lock frн       | Operation continues (cannot Status before HALT mode was set is retained be stopped)       |                                             |                                             |  |  |  |  |

|                                                                    | fx             | Status before HALT mode was set is retained                                               | Operation continues (cannot be stopped)     | Status before HALT mode was set is retained |  |  |  |  |

|                                                                    | <b>f</b> exclk | Operates or stops by external of                                                          | clock input                                 | Operation continues (cannot be stopped)     |  |  |  |  |

| Subsystem clo                                                      | ck fxt         | Status before HALT mode was                                                               | set is retained                             |                                             |  |  |  |  |

| f <sub>RL</sub>                                                    |                | Status before HALT mode was                                                               | Status before HALT mode was set is retained |                                             |  |  |  |  |

| CPU                                                                |                | Operation stopped                                                                         |                                             |                                             |  |  |  |  |

| Flash memory                                                       |                |                                                                                           |                                             |                                             |  |  |  |  |

| RAM                                                                |                | Status before HALT mode was set is retained                                               |                                             |                                             |  |  |  |  |

| Port (latch)                                                       |                |                                                                                           |                                             |                                             |  |  |  |  |

| 16-bit timer/event of                                              | counter 00     | Operable                                                                                  |                                             |                                             |  |  |  |  |

| 8-bit timer/event                                                  | 50             |                                                                                           |                                             |                                             |  |  |  |  |

| counter                                                            | 51             |                                                                                           |                                             |                                             |  |  |  |  |

|                                                                    | 52             |                                                                                           |                                             |                                             |  |  |  |  |

| 8-bit timer                                                        | H0             |                                                                                           |                                             |                                             |  |  |  |  |

|                                                                    | H1             |                                                                                           |                                             |                                             |  |  |  |  |

|                                                                    | H2             |                                                                                           |                                             |                                             |  |  |  |  |

| Real-time counter                                                  |                |                                                                                           |                                             |                                             |  |  |  |  |

| Watchdog timer                                                     |                | Operable. Clock supply to watchdog timer stops when "internal low-speed oscillator can be |                                             |                                             |  |  |  |  |

|                                                                    |                | stopped by software" is set by option byte.                                               |                                             |                                             |  |  |  |  |

| Buzzer output                                                      |                | Operable                                                                                  |                                             |                                             |  |  |  |  |

| 10-bit successive approximation type A/D converter <sup>Note</sup> |                |                                                                                           |                                             |                                             |  |  |  |  |

| Serial interface                                                   | UART0<br>UART6 | -                                                                                         |                                             |                                             |  |  |  |  |

| LCD controller/driver                                              |                | 1                                                                                         |                                             |                                             |  |  |  |  |

| Manchester code g                                                  |                | 1                                                                                         |                                             |                                             |  |  |  |  |

| Remote controller receiver                                         |                | 1                                                                                         |                                             |                                             |  |  |  |  |

| Power-on-clear fur                                                 | nction         | 1                                                                                         |                                             |                                             |  |  |  |  |

| Low-voltage detect                                                 | tion function  | 1                                                                                         |                                             |                                             |  |  |  |  |

| External interrupt                                                 |                | 1                                                                                         |                                             |                                             |  |  |  |  |

| Table 19-1. | Operating Statuses in HALT Mode (1/2) |

|-------------|---------------------------------------|

|-------------|---------------------------------------|

**Note** μPD78F041x only.

Internal high-speed oscillation clock X1 clock Remark free: fx: fexclk: External main system clock fxT: XT1 clock

Internal low-speed oscillation clock frl:

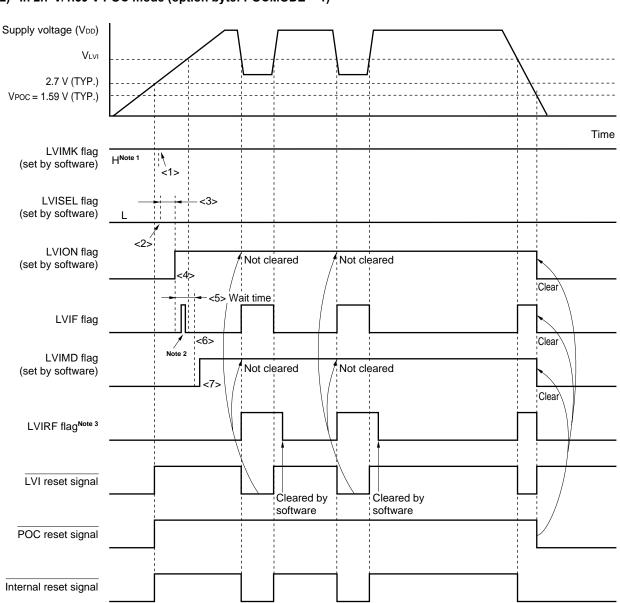

# (2) In 2.7 V/1.59 V POC mode (option byte: POCMODE = 1)

**Notes 1.** The LVIMK flag is set to "1" by reset signal generation.

- **2.** The LVIF flag may be set (1).

- LVIRF is bit 0 of the reset control flag register (RESF). For details of RESF, see CHAPTER 20 RESET FUNCTION.

- **Remark** <1> to <7> in Figure 22-5 above correspond to <1> to <7> in the description of "When starting operation" in **22.4.1 (1) When detecting level of supply voltage (V**<sub>DD</sub>).

# (3) 0084H/1084H

- O On-chip debug operation control

- Disabling on-chip debug operation

- Enabling on-chip debug operation and erasing data of the flash memory in case authentication of the onchip debug security ID fails

- Enabling on-chip debug operation and not erasing data of the flash memory even in case authentication of the on-chip debug security ID fails

- Caution To use the on-chip debug function, set 02H or 03H to 0084H. Set a value that is the same as that of 0084H to 1084H because 0084H and 1084H are switched during the boot operation.

| Instruction       | Mnemonic | Operands      | Bytes | Clocks |        | Orientian                                       | Flag                       |

|-------------------|----------|---------------|-------|--------|--------|-------------------------------------------------|----------------------------|

| Group             |          | Operands      |       | Note 1 | Note 2 | Operation                                       | Z AC CY                    |

| Bit<br>manipulate | AND1     | CY, saddr.bit | 3     | 6      | 7      | $CY \leftarrow CY \land (saddr.bit)$            | ×                          |

|                   |          | CY, sfr.bit   | 3     | -      | 7      | $CY \leftarrow CY \land sfr.bit$                | ×                          |

|                   |          | CY, A.bit     | 2     | 4      | -      | $CY \leftarrow CY \land A.bit$                  | ×                          |

|                   |          | CY, PSW.bit   | 3     | _      | 7      | $CY \gets CY \land PSW.bit$                     | ×                          |

|                   |          | CY, [HL].bit  | 2     | 6      | 7      | $CY \gets CY \land (HL).bit$                    | ×                          |

|                   | OR1      | CY, saddr.bit | 3     | 6      | 7      | $CY \gets CY \lor (saddr.bit)$                  | ×                          |

|                   |          | CY, sfr.bit   | 3     | _      | 7      | $CY \gets CY \lor sfr.bit$                      | ×                          |

|                   |          | CY, A.bit     | 2     | 4      | _      | $CY \gets CY \lor A.bit$                        | ×                          |

|                   |          | CY, PSW.bit   | 3     | -      | 7      | $CY \gets CY \lor PSW.bit$                      | ×                          |

|                   |          | CY, [HL].bit  | 2     | 6      | 7      | $CY \gets CY \lor (HL).bit$                     | ×                          |

|                   | XOR1     | CY, saddr.bit | 3     | 6      | 7      | $CY \leftarrow CY \nleftrightarrow (saddr.bit)$ | ×                          |

|                   |          | CY, sfr.bit   | 3     | -      | 7      | $CY \leftarrow CY \leftrightarrow sfr.bit$      | ×                          |

|                   |          | CY, A.bit     | 2     | 4      | -      | $CY \leftarrow CY \neq A.bit$                   | ×                          |

|                   |          | CY, PSW. bit  | 3     | -      | 7      | $CY \leftarrow CY \nleftrightarrow PSW.bit$     | ×                          |

|                   |          | CY, [HL].bit  | 2     | 6      | 7      | $CY \leftarrow CY \leftrightarrow (HL).bit$     | ×                          |

|                   | SET1     | saddr.bit     | 2     | 4      | 6      | $(saddr.bit) \leftarrow 1$                      |                            |

|                   |          | sfr.bit       | 3     | -      | 8      | sfr.bit $\leftarrow$ 1                          |                            |

|                   |          | A.bit         | 2     | 4      | -      | A.bit ← 1                                       |                            |

|                   |          | PSW.bit       | 2     | -      | 6      | PSW.bit ← 1                                     | $\times$ $\times$ $\times$ |

|                   |          | [HL].bit      | 2     | 6      | 8      | (HL).bit $\leftarrow$ 1                         |                            |

|                   | CLR1     | saddr.bit     | 2     | 4      | 6      | $(saddr.bit) \leftarrow 0$                      |                            |

|                   |          | sfr.bit       | 3     | -      | 8      | sfr.bit $\leftarrow$ 0                          |                            |

|                   |          | A.bit         | 2     | 4      | -      | A.bit $\leftarrow$ 0                            |                            |

|                   |          | PSW.bit       | 2     | _      | 6      | PSW.bit ← 0                                     | $\times$ $\times$ $\times$ |

|                   |          | [HL].bit      | 2     | 6      | 8      | (HL).bit $\leftarrow 0$                         |                            |

|                   | SET1     | CY            | 1     | 2      | _      | CY ← 1                                          | 1                          |

|                   | CLR1     | CY            | 1     | 2      | _      | $CY \leftarrow 0$                               | 0                          |

|                   | NOT1     | CY            | 1     | 2      | -      | $CY \leftarrow \overline{CY}$                   | ×                          |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

- 2. This clock cycle applies to the internal ROM program.