Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | S08                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | -                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 4                                                                    |

| Program Memory Size        | 2KB (2K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 128 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 4x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                        |

| Supplier Device Package    | 8-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qd2msc |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

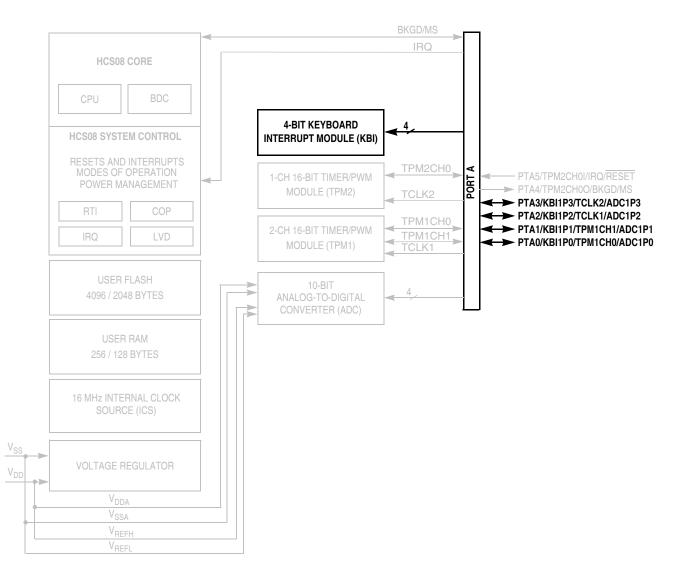

# **MC9S08QD4 Series Features**

### 8-Bit HCS08 Central Processor Unit (CPU)

- 16 MHz HCS08 CPU (central processor unit)

- HC08 instruction set with added BGND instruction

- Background debugging system

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints in on-chip debug module)

- Support for up to 32 interrupt/reset sources

### Memory

- Flash read/program/erase over full operating voltage and temperature

- Flash size:

- MC9S08QD4/S9S08QD4: 4096 bytes

- MC9S08QD2/S9S08QD2: 2048 bytes

- RAM size

- MC9S08QD4/S9S08QD4: 256 bytes

- MC9S08QD2/S9S08QD2: 128 bytes

### **Power-Saving Modes**

• Wait plus three stops

### **Clock Source Options**

• ICS — Internal clock source module (ICS) containing a frequency-locked-loop (FLL) controlled by internal. Precision trimming of internal reference allows 0.2% resolution and 2% deviation over temperature and voltage.

### **System Protection**

- Watchdog computer operating properly (COP) reset with option to run from dedicated 32 kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt

- Illegal opcode detection with reset

- Illegal address detection with reset

Flash block protect

#### Peripherals

- ADC 4-channel, 10-bit analog-to-digital converter with automatic compare function, asynchronous clock source, temperature sensor and internal bandgap reference channel. ADC is hardware triggerable using the RTI counter.

- **TIM1** 2-channel timer/pulse-width modulator; each channel can be used for input capture, output compare, buffered edge-aligned PWM, or buffered center-aligned PWM

- **TIM2** 1-channel timer/pulse-width modulator; each channel can be used for input capture, output compare, buffered edge-aligned PWM, or buffered center-aligned PWM

- **KBI** 4-pin keyboard interrupt module with software selectable polarity on edge or edge/level modes

### Input/Output

- Four General-purpose input/output (I/O) pins, one input-only pin and one output-only pin. Outputs 10 mA each, 60 mA maximum for package.

- Software selectable pullups on ports when used as input

- Software selectable slew rate control and drive strength on ports when used as output

- Internal pullup on RESET and IRQ pin to reduce customer system cost

### **Development Support**

• Single-wire background debug interface

### **Package Options**

- 8-pin SOIC package

- 8-pin PDIP (Only for MC9S08QD4 and MC9S08QD2)

- All package options are RoHS compliant

| 9.5 | Module | Initialization                     |  |

|-----|--------|------------------------------------|--|

|     |        | ICS Module Initialization Sequence |  |

# Chapter 10 Keyboard Interrupt (S08KBIV2)

| 10.1 | Introduction                                   |     |

|------|------------------------------------------------|-----|

|      | 10.1.1 Features                                |     |

|      | 10.1.2 Modes of Operation                      |     |

|      | 10.1.3 Block Diagram                           |     |

| 10.2 | External Signal Description                    |     |

| 10.3 | Register Definition                            |     |

|      | 10.3.1 KBI Status and Control Register (KBISC) |     |

|      | 10.3.2 KBI Pin Enable Register (KBIPE)         |     |

|      | 10.3.3 KBI Edge Select Register (KBIES)        |     |

| 10.4 | Functional Description                         |     |

|      | 10.4.1 Edge Only Sensitivity                   |     |

|      | 10.4.2 Edge and Level Sensitivity              |     |

|      | 10.4.3 KBI Pullup/Pulldown Resistors           | 141 |

|      | 10.4.4 KBI Initialization                      |     |

# Chapter 11 Timer/Pulse-Width Modulator (S08TPMV2)

| 11.1 | Introduc | tion                                                   | 143 |

|------|----------|--------------------------------------------------------|-----|

|      | 11.1.1   | TPM2 Configuration Information                         | 143 |

|      | 11.1.2   | TCLK1 and TCLK2 Configuration Information              | 143 |

|      | 11.1.3   | Features                                               | 145 |

|      | 11.1.4   | Block Diagram                                          | 145 |

| 11.2 | External | Signal Description                                     | 147 |

|      |          | External TPM Clock Sources                             |     |

|      |          | TPMxCHn — TPMx Channel n I/O Pins                      |     |

| 11.3 |          | Definition                                             |     |

|      | 11.3.1   | Timer Status and Control Register (TPMxSC)             | 148 |

|      | 11.3.2   | Timer Counter Registers (TPMxCNTH:TPMxCNTL)            | 149 |

|      |          | Timer Counter Modulo Registers (TPMxMODH:TPMxMODL)     |     |

|      | 11.3.4   | Timer Channel n Status and Control Register (TPMxCnSC) | 151 |

|      | 11.3.5   | Timer Channel Value Registers (TPMxCnVH:TPMxCnVL)      | 152 |

| 11.4 | Function | nal Description                                        | 153 |

|      |          | Counter                                                |     |

|      | 11.4.2   | Channel Mode Selection                                 | 154 |

|      | 11.4.3   | Center-Aligned PWM Mode                                | 156 |

| 11.5 | TPM In   | terrupts                                               | 157 |

|      | 11.5.1   | Clearing Timer Interrupt Flags                         | 157 |

|      | 11.5.2   | Timer Overflow Interrupt Description                   | 157 |

|      | 11.5.3   | Channel Event Interrupt Description                    | 158 |

|      | 11.5.4   | PWM End-of-Duty-Cycle Events                           | 158 |

|      |          |                                                        |     |

the CPU executes a STOP instruction, the MCU will not enter either of the stop modes and an illegal opcode reset is forced. The stop modes are selected by setting the appropriate bits in SPMSC2.

HCS08 devices that are designed for low voltage operation (1.8V to 3.6V) also include stop1 mode. The MC9S08QD4 series does not include stop1 mode.

| Mode  | PPDC | CPU, Digital<br>Peripherals,<br>Flash | RAM     | ICS              | ADC1          | Regulator | I/O Pins    | RTI           |

|-------|------|---------------------------------------|---------|------------------|---------------|-----------|-------------|---------------|

| Stop2 | 1    | Off                                   | Standby | Off              | Disabled      | Standby   | States held | Optionally on |

| Stop3 | 0    | Standby                               | Standby | Off <sup>1</sup> | Optionally on | Standby   | States held | Optionally on |

Table 3-1 summarizes the behavior of the MCU in each of the stop modes.

<sup>1</sup> ICS can be configured to run in stop3. Please see the ICS registers.

### 3.6.1 Stop2 Mode

The stop2 mode provides very low standby power consumption and maintains the contents of RAM and the current state of all of the I/O pins. To enter stop2, the user must execute a STOP instruction with stop2 selected (PPDC = 1) and stop mode enabled (STOPE = 1). In addition, the LVD must not be enabled to operate in stop (LVDSE = 0 or LVDE = 0). If the LVD is enabled in stop, then the MCU enters stop3 upon the execution of the STOP instruction regardless of the state of PPDC.

Before entering stop2 mode, the user must save the contents of the I/O port registers, as well as any other memory-mapped registers which they want to restore after exit of stop2, to locations in RAM. Upon exit of stop2, these values can be restored by user software before pin latches are opened.

When the MCU is in stop2 mode, all internal circuits that are powered from the voltage regulator are turned off, except for the RAM. The voltage regulator is in a low-power standby state, as is the ADC. Upon entry into stop2, the states of the I/O pins are latched. The states are held while in stop2 mode and after exiting stop2 mode until a logic 1 is written to PPDACK in SPMSC2.

Exit from stop2 is done by asserting either of the wake-up pins:  $\overline{\text{RESET}}$  or IRQ, or by an RTI interrupt. IRQ is always an active low input when the MCU is in stop2, regardless of how it was configured before entering stop2.

#### NOTE

Although this IRQ pin is automatically configured as active low input, the pullup associated with the IRQ pin is not automatically enabled. Therefore, if an external pullup is not used, the internal pullup must be enabled by setting IRQPE in IRQSC.

Upon wake-up from stop2 mode, the MCU will start up as from a power-on reset (POR) except pin states remain latched. The CPU will take the reset vector. The system and all peripherals will be in their default reset states and must be initialized.

Chapter 5 Resets, Interrupts, and General System Control

The IRQ pin when enabled defaults to use an internal pull device (IRQPDD = 0), the device is a pullup or pulldown depending on the polarity to detect. If the user desires to use an external pullup or pulldown, the IRQPDD can be written to a 1 to turn off the internal device.

BIH and BIL instructions may be used to detect the level on the IRQ pin when the pin is configured to act as the IRQ input.

### NOTE

This pin does not contain a clamp diode to  $V_{\mbox{\scriptsize DD}}$  and must not be driven above  $V_{\mbox{\scriptsize DD}}.$

The voltage measured on the internally pulled up IRQ pin may be as low as  $V_{DD} - 0.7$  V. The internal gates connected to this pin are pulled all the way to  $V_{DD}$ .

### 5.5.2.2 Edge and Level Sensitivity

The IRQMOD control bit reconfigures the detection logic so it detects edge events and pin levels. In this edge detection mode, the IRQF status flag becomes set when an edge is detected (when the IRQ pin changes from the deasserted to the asserted level), but the flag is continuously set (and cannot be cleared) as long as the IRQ pin remains at the asserted level.

### 5.5.3 Interrupt Vectors, Sources, and Local Masks

Table 5-2 provides a summary of all interrupt sources. Higher-priority sources are located toward the bottom of the table. The high-order byte of the address for the interrupt service routine is located at the first address in the vector address column, and the low-order byte of the address for the interrupt service routine is located at the next higher address.

When an interrupt condition occurs, an associated flag bit becomes set. If the associated local interrupt enable is 1, an interrupt request is sent to the CPU. Within the CPU, if the global interrupt mask (I bit in the CCR) is 0, the CPU will finish the current instruction; stack the PCL, PCH, X, A, and CCR CPU registers; set the I bit; and then fetch the interrupt vector for the highest priority pending interrupt. Processing then continues in the interrupt service routine.

### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the  $V_{POR}$  level, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the  $V_{LVDL}$  level. Both the POR bit and the LVD bit in SRS are set following a POR.

### 5.6.2 LVD Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the level determined by LVDV. The LVD bit in the SRS register is set following either an LVD reset or POR.

### 5.6.3 LVD Interrupt Operation

When a low voltage condition is detected and the LVD circuit is configured using SPMSC1 for interrupt operation (LVDE set, LVDIE set, and LVDRE clear), then LVDF in SPMSC1 will be set and an LVD interrupt request will occur.

### 5.6.4 Low-Voltage Warning (LVW)

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching, but is above, the LVD voltage. The LVW does not have an interrupt associated with it. There are two user selectable trip voltages for the LVW, one high ( $V_{LVWH}$ ) and one low ( $V_{LVWL}$ ). The trip voltage is selected by LVWV in SPMSC2.

### 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts. The RTI can accept two sources of clocks, the 1 kHz internal clock or an 32 kHz ICS clock if available. The RTICLKS bit in SRTISC is used to select the RTI clock source.

Both clock source can be used when the MCU is in run, wait or stop3 mode. When using the 32 kHz ICS clock in stop3, it must be enabled in stop (EREFSTEN = 1) and configured for low frequency operation (RANGE = 0). Only the internal 1 kHz clock source can be selected to wake the MCU from stop1 or stop2 modes.

The SRTISC register includes a read-only status flag, a write-only acknowledge bit, and a 3-bit control value (RTIS) used to select one of seven wakeup periods. The RTI has a local interrupt enable, RTIE, to allow masking of the real-time interrupt. The RTI can be disabled by writing each bit of RTIS to zeroes, and no interrupts will be generated. See Section 5.8.7, "System Real-Time Interrupt Status and Control Register (SRTISC)," for detailed information about this register.

Chapter 5 Resets, Interrupts, and General System Control

#### **Reset, Interrupt, and System Control Registers and Control Bits** 5.8

One 8-bit register in the direct page register space and eight 8-bit registers in the high-page register space are related to reset and interrupt systems.

Refer to the direct-page register summary in Chapter 3, "Modes of Operation," for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some control bits in the SOPT1, SOPT2 and SPMSC2 registers are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation."

#### 5.8.1 Interrupt Pin Request Status and Control Register (IRQSC)

This direct page register includes status and control bits which are used to configure the IRQ function, report status, and acknowledge IRQ events.

| _     | 7 | 6            | 5               | 4     | 3    | 2      | 1     | 0      |

|-------|---|--------------|-----------------|-------|------|--------|-------|--------|

| R     | 0 | חחפספו       |                 | IRQPE | IRQF | 0      | IRQIE | IRQMOD |

| W     |   | IRQPDD       | IRQEDG          | INQPE |      | IRQACK | INQIE |        |

| Reset | 0 | 0            | 0               | 0     | 0    | 0      | 0     | 0      |

|       |   | = Unimplemer | nted or Reserve | ed    |      |        |       |        |

#### Figure 5-2. Interrupt Request Status and Control Register (IRQSC)

|             | Table 5-3. IRQSC Register Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6<br>IRQPDD | Interrupt Request (IRQ) Pull Device Disable— This read/write control bit is used to disable the internal pullup/pulldown device when the IRQ pin is enabled (IRQPE = 1) allowing for an external device to be used.<br>0 IRQ pull device enabled if IRQPE = 1.<br>1 IRQ pull device disabled if IRQPE = 1.                                                                                                                                                                                                                                                                                                                                            |

| 5<br>IRQEDG | <ul> <li>Interrupt Request (IRQ) Edge Select — This read/write control bit is used to select the polarity of edges or levels on the IRQ pin that cause IRQF to be set. The IRQMOD control bit determines whether the IRQ pin is sensitive to both edges and levels or only edges. When the IRQ pin is enabled as the IRQ input and is configured to detect rising edges. When IRQEDG = 1 and the internal pull device is enabled, the pullup device is reconfigured as an optional pulldown device.</li> <li>0 IRQ is falling edge or falling edge/low-level sensitive.</li> <li>1 IRQ is rising edge or rising edge/high-level sensitive.</li> </ul> |

| 4<br>IRQPE  | <ul> <li>IRQ Pin Enable — This read/write control bit enables the IRQ pin function. When this bit is set the IRQ pin can be used as an interrupt request.</li> <li>IRQ pin function is disabled.</li> <li>IRQ pin function is enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3<br>IRQF   | <ul> <li>IRQ Flag — This read-only status bit indicates when an interrupt request event has occurred.</li> <li>0 No IRQ request.</li> <li>1 IRQ event detected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Table 5.9 JDOCO Deviator Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out.</li> <li>This reset source can be blocked by COPE = 0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                                        |

| 4<br>ILOP | <ul> <li>Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.</li> <li>0 Reset not caused by an illegal opcode.</li> <li>1 Reset caused by an illegal opcode.</li> </ul> |

| 3<br>ILAD | Illegal Address       — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.         0       Reset not caused by an illegal address         1       Reset caused by an illegal address                                                                                                                                                                                              |

| 1<br>LVD  | <ul> <li>Low Voltage Detect — If the LVDRE bit is set and the supply drops below the LVD trip voltage, an LVD reset will occur. This bit is also set by POR.</li> <li>Reset not caused by LVD trip or POR.</li> <li>Reset caused by LVD trip or POR.</li> </ul>                                                                                                                                                                           |

#### Table 5-4. SRS Register Field Descriptions (continued)

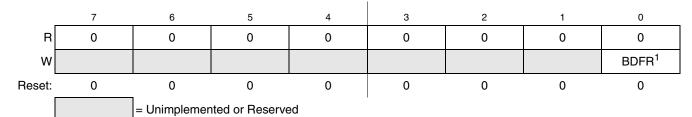

### 5.8.3 System Background Debug Force Reset Register (SBDFR)

This high-page register contains a single write-only control bit. A serial background command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

<sup>1</sup> BDFR is writable only through serial background debug commands, not from user programs.

#### Figure 5-4. System Background Debug Force Reset Register (SBDFR)

#### Table 5-5. SBDFR Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>BDFR | <b>Background Debug Force Reset</b> — A serial background command such as WRITE_BYTE can be used to allow<br>an external debug host to force a target system reset. Writing 1 to this bit forces an MCU reset. This bit cannot<br>be written from a user program. To enter user mode, PTA4/TPM2CH0O/BKGD/MS must be high immediately<br>after issuing WRITE_BYTE command. To enter BDM, PTA4/TPM2CH0O/BKGD/MS must be low immediately<br>after issuing WRITE_BYTE command. See A.8.1, "Control Timing," for more information. |

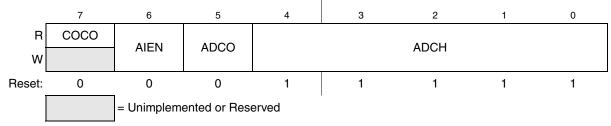

| Figure 8-3. Status and Control Register (ADCSC1 | Figure 8-3. | Status and | Control | Register | (ADCSC1 |

|-------------------------------------------------|-------------|------------|---------|----------|---------|

|-------------------------------------------------|-------------|------------|---------|----------|---------|

| Table 8-3. | ADCSC1 | Register | Field | Descriptions |

|------------|--------|----------|-------|--------------|

|------------|--------|----------|-------|--------------|

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COCO   | <ul> <li>Conversion Complete Flag — The COCO flag is a read-only bit which is set each time a conversion is completed when the compare function is disabled (ACFE = 0). When the compare function is enabled (ACFE = 1) the COCO flag is set upon completion of a conversion only if the compare result is true. This bit is cleared whenever ADCSC1 is written or whenever ADCRL is read.</li> <li>0 Conversion not completed</li> <li>1 Conversion completed</li> </ul>                                                                                                                                                                                                                                                                            |

| 6<br>AIEN   | Interrupt Enable — AIEN is used to enable conversion complete interrupts. When COCO becomes set while         AIEN is high, an interrupt is asserted.         0 Conversion complete interrupt disabled         1 Conversion complete interrupt enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5<br>ADCO   | <ul> <li>Continuous Conversion Enable — ADCO is used to enable continuous conversions.</li> <li>One conversion following a write to the ADCSC1 when software triggered operation is selected, or one conversion following assertion of ADHWT when hardware triggered operation is selected.</li> <li>Continuous conversions initiated following a write to ADCSC1 when software triggered operation is selected. Continuous conversions are initiated by an ADHWT event when hardware triggered operation is selected.</li> </ul>                                                                                                                                                                                                                    |

| 4:0<br>ADCH | Input Channel Select — The ADCH bits form a 5-bit field which is used to select one of the input channels. The input channels are detailed in Figure 8-4.<br>The successive approximation converter subsystem is turned off when the channel select bits are all set to 1.<br>This feature allows for explicit disabling of the ADC and isolation of the input channel from all sources.<br>Terminating continuous conversions this way will prevent an additional, single conversion from being performed.<br>It is not necessary to set the channel select bits to all 1s to place the ADC in a low-power state when continuous conversions are not enabled because the module automatically enters a low-power state when a conversion completes. |

#### Figure 8-4. Input Channel Select

| ADCH  | Input Select |

|-------|--------------|

| 00000 | AD0          |

| 00001 | AD1          |

| 00010 | AD2          |

| 00011 | AD3          |

| 00100 | AD4          |

| 00101 | AD5          |

| 00110 | AD6          |

| ADCH  | Input Select |

|-------|--------------|

| 10000 | AD16         |

| 10001 | AD17         |

| 10010 | AD18         |

| 10011 | AD19         |

| 10100 | AD20         |

| 10101 | AD21         |

| 10110 | AD22         |

### 8.4.7.2 Stop3 Mode With ADACK Enabled

If ADACK is selected as the conversion clock, the ADC continues operation during stop3 mode. For guaranteed ADC operation, the MCU's voltage regulator must remain active during stop3 mode. Consult the module introduction for configuration information for this MCU.

If a conversion is in progress when the MCU enters stop3 mode, it continues until completion. Conversions can be initiated while the MCU is in stop3 mode by means of the hardware trigger or if continuous conversions are enabled.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from stop3 mode if the ADC interrupt is enabled (AIEN = 1).

#### NOTE

It is possible for the ADC module to wake the system from low power stop and cause the MCU to begin consuming run-level currents without generating a system level interrupt. To prevent this scenario, software must ensure that the data transfer blocking mechanism (discussed in Section 8.4.4.2, "Completing Conversions,") is cleared when entering stop3 and continuing ADC conversions.

### 8.4.8 MCU Stop1 and Stop2 Mode Operation

The ADC module is automatically disabled when the MCU enters either stop1 or stop2 mode. All module registers contain their reset values following exit from stop1 or stop2. Therefore the module must be re-enabled and re-configured following exit from stop1 or stop2.

### 8.5 Initialization Information

This section gives an example which provides some basic direction on how a user would initialize and configure the ADC module. The user has the flexibility of choosing between configuring the module for 8-bit or 10-bit resolution, single or continuous conversion, and a polled or interrupt approach, among many other options. Refer to Table 8-6, Table 8-7, and Table 8-8 for information used in this example.

#### NOTE

Hexadecimal values designated by a preceding 0x, binary values designated by a preceding %, and decimal values have no preceding character.

### 8.5.1 ADC Module Initialization Example

### 8.5.1.1 Initialization Sequence

Before the ADC module can be used to complete conversions, an initialization procedure must be performed. A typical sequence is as follows:

1. Update the configuration register (ADCCFG) to select the input clock source and the divide ratio used to generate the internal clock, ADCK. This register is also used for selecting sample time and low-power configuration.

Internal Clock Source (S08ICSV1)

# 9.4 Functional Description

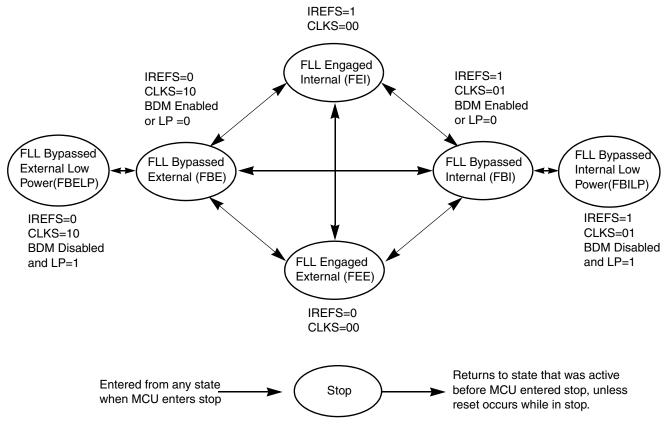

# 9.4.1 Operational Modes

Figure 9-7. Clock Switching Modes

The seven states of the ICS are shown as a state diagram and are described below. The arrows indicate the allowed movements between the states.

### 9.4.1.1 FLL Engaged Internal (FEI)

FLL engaged internal (FEI) is the default mode of operation and is entered when all the following conditions occur:

- CLKS bits are written to 00

- IREFS bit is written to 1

- RDIV bits are written to divide trimmed reference clock to be within the range of 31.25 kHz to 39.0625 kHz.

In FLL engaged internal mode, the ICSOUT clock is derived from the FLL clock, which is controlled by the internal reference clock. The FLL loop will lock the frequency to 512 times the filter frequency, as selected by the RDIV bits. The ICSLCLK is available for BDC communications, and the internal reference clock is enabled.

#### Chapter 10 Keyboard Interrupt (S08KBIV2)

#### NOTES:

- <sup>1</sup> Port pins are software configurable with pullup device if input port.

- <sup>2</sup> Port pins are software configurable for output drive strength.

- <sup>3</sup> Port pins are software configurable for output slew rate control.

- <sup>4</sup> IRQ contains a software configurable (IRQPDD) pullup/pulldown device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- $^{5}$  RESET contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>6</sup> PTA5 does not contain a clamp diode to  $V_{DD}$  and must not be driven above  $V_{DD}$ . The voltage measured on this pin when internal pullup is enabled may be as low as  $V_{DD} 0.7$  V. The internal gates connected to this pin are pulled to  $V_{DD}$ .

- $^{7}$  PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

#### Figure 10-1. MC9S08QD4 Series Block Diagram Highlighting KBI Block and Pins

### 10.1.1 Features

The KBI features include:

- Up to eight keyboard interrupt pins with individual pin enable bits.

- Each keyboard interrupt pin is programmable as falling edge (or rising edge) only, or both falling edge and low level (or both rising edge and high level) interrupt sensitivity.

- One software enabled keyboard interrupt.

- Exit from low-power modes.

### 10.1.2 Modes of Operation

This section defines the KBI operation in wait, stop, and background debug modes.

### 10.1.2.1 KBI in Wait Mode

The KBI continues to operate in wait mode if enabled before executing the WAIT instruction. Therefore, an enabled KBI pin (KBPEx = 1) can be used to bring the MCU out of wait mode if the KBI interrupt is enabled (KBIE = 1).

### 10.1.2.2 KBI in Stop Modes

The KBI operates asynchronously in stop3 mode if enabled before executing the STOP instruction. Therefore, an enabled KBI pin (KBPEx = 1) can be used to bring the MCU out of stop3 mode if the KBI interrupt is enabled (KBIE = 1).

During either stop1 or stop2 mode, the KBI is disabled. In some systems, the pins associated with the KBI may be sources of wakeup from stop1 or stop2, see the stop modes section in the Modes of Operation chapter. Upon wake-up from stop1 or stop2 mode, the KBI module will be in the reset state.

### 10.1.2.3 KBI in Active Background Mode

When the microcontroller is in active background mode, the KBI will continue to operate normally.

### 10.1.3 Block Diagram

The block diagram for the keyboard interrupt module is shown Figure 10-2.

Keyboard Interrupts (S08KBIV2)

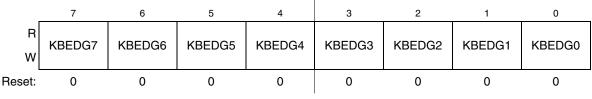

Figure 10-5. KBI Edge Select Register

Table 10-4. KBIES Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>KBEDGn | <ul> <li>Keyboard Edge Selects — Each of the KBEDGn bits selects the falling edge/low level or rising edge/high level function of the corresponding pin).</li> <li>Falling edge/low level.</li> <li>Rising edge/high level.</li> </ul> |

# **10.4 Functional Description**

This on-chip peripheral module is called a keyboard interrupt (KBI) module because originally it was designed to simplify the connection and use of row-column matrices of keyboard switches. However, these inputs are also useful as extra external interrupt inputs and as an external means of waking the MCU from stop or wait low-power modes.

The KBI module allows up to eight pins to act as additional interrupt sources. Writing to the KBIPEn bits in the keyboard interrupt pin enable register (KBIPE) independently enables or disables each KBI pin. Each KBI pin can be configured as edge sensitive or edge and level sensitive based on the KBMOD bit in the keyboard interrupt status and control register (KBISC). Edge sensitive can be software programmed to be either falling or rising; the level can be either low or high. The polarity of the edge or edge and level sensitivity is selected using the KBEDGn bits in the keyboard interrupt edge select register (KBISC).

# 10.4.1 Edge Only Sensitivity

Synchronous logic is used to detect edges. A falling edge is detected when an enabled keyboard interrupt (KBIPEn=1) input signal is seen as a logic 1 (the deasserted level) during one bus cycle and then a logic 0 (the asserted level) during the next cycle. A rising edge is detected when the input signal is seen as a logic 0 (the deasserted level) during one bus cycle and then a logic 1 (the asserted level) during the next cycle. Before the first edge is detected, all enabled keyboard interrupt input signals must be at the deasserted logic levels. After any edge is detected, all enabled keyboard interrupt input signals must return to the deasserted level before any new edge can be detected.

A valid edge on an enabled KBI pin will set KBF in KBISC. If KBIE in KBISC is set, an interrupt request will be presented to the CPU. Clearing of KBF is accomplished by writing a 1 to KBACK in KBISC.

# 10.4.2 Edge and Level Sensitivity

A valid edge or level on an enabled KBI pin will set KBF in KBISC. If KBIE in KBISC is set, an interrupt request will be presented to the CPU. Clearing of KBF is accomplished by writing a 1 to KBACK in

# NP,

Timer/Pulse-Width Modulator (S08TPMV2)

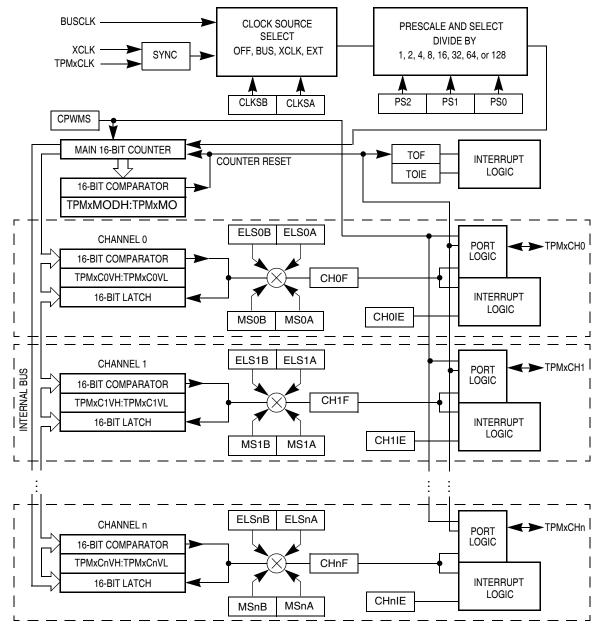

Figure 11-2. TPM Block Diagram

The central component of the TPM is the 16-bit counter that can operate as a free-running counter, a modulo counter, or an up-/down-counter when the TPM is configured for center-aligned PWM. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture, output compare, and edge-aligned PWM functions. The timer counter modulo registers, TPMxMODH:TPMxMODL, control the modulo value of the counter. (The values 0x0000 or 0xFFFF effectively make the counter free running.) Software can read the counter value at any time without affecting the counting sequence. Any write to either byte of the TPMxCNT counter resets the counter regardless of the data value written.

All TPM channels are programmable independently as input capture, output compare, or buffered edge-aligned PWM channels.

# 11.2 External Signal Description

When any pin associated with the timer is configured as a timer input, a passive pullup can be enabled. After reset, the TPM modules are disabled and all pins default to general-purpose inputs with the passive pullups disabled.

# 11.2.1 External TPM Clock Sources

When control bits CLKSB:CLKSA in the timer status and control register are set to 1:1, the prescaler and consequently the 16-bit counter for TPMx are driven by an external clock source, TPMxCLK, connected to an I/O pin. A synchronizer is needed between the external clock and the rest of the TPM. This synchronizer is clocked by the bus clock so the frequency of the external source must be less than one-half the frequency of the bus rate clock. The upper frequency limit for this external clock source is specified to be one-fourth the bus frequency to conservatively accommodate duty cycle and phase-locked loop (PLL) or frequency-locked loop (FLL) frequency jitter effects.

On some devices the external clock input is shared with one of the TPM channels. When a TPM channel is shared as the external clock input, the associated TPM channel cannot use the pin. (The channel can still be used in output compare mode as a software timer.) Also, if one of the TPM channels is used as the external clock input, the corresponding ELSnB:ELSnA control bits must be set to 0:0 so the channel is not trying to use the same pin.

# 11.2.2 TPMxCHn — TPMx Channel n I/O Pins

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the configuration of the channel. In some cases, no pin function is needed so the pin reverts to being controlled by general-purpose I/O controls. When a timer has control of a port pin, the port data and data direction registers do not affect the related pin(s). See the Pins and Connections chapter for additional information about shared pin functions.

# 11.3 Register Definition

The TPM includes:

- An 8-bit status and control register (TPMxSC)

- A 16-bit counter (TPMxCNTH:TPMxCNTL)

- A 16-bit modulo register (TPMxMODH:TPMxMODL)

Each timer channel has:

- An 8-bit status and control register (TPMxCnSC)

- A 16-bit channel value register (TPMxCnVH:TPMxCnVL)

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all TPM registers. This section refers to registers and control bits only by their names. A

Timer/Pulse-Width Modulator (S08TPMV2)

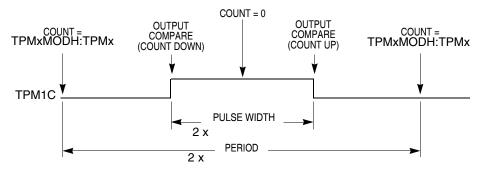

# 11.4.3 Center-Aligned PWM Mode

This type of PWM output uses the up-/down-counting mode of the timer counter (CPWMS = 1). The output compare value in TPMxCnVH:TPMxCnVL determines the pulse width (duty cycle) of the PWM signal and the period is determined by the value in TPMxMODH:TPMxMODL.

TPMxMODH:TPMxMODL must be kept in the range of 0x0001 to 0x7FFF because values outside this range can produce ambiguous results. ELSnA will determine the polarity of the CPWM output.

#### period = 2 x (TPMxMODH:TPMxMODL); for TPMxMODH:TPMxMODL = 0x0001–0x7FFF Eqn. 11-2

If the channel value register TPMxCnVH:TPMxCnVL is zero or negative (bit 15 set), the duty cycle will be 0%. If TPMxCnVH:TPMxCnVL is a positive value (bit 15 clear) and is greater than the (nonzero) modulus setting, the duty cycle will be 100% because the duty cycle compare will never occur. This implies the usable range of periods set by the modulus register is 0x0001 through 0x7FFE (0x7FFF if generation of 100% duty cycle is not necessary). This is not a significant limitation because the resulting period is much longer than required for normal applications.

TPMxMODH:TPMxMODL = 0x0000 is a special case that must not be used with center-aligned PWM mode. When CPWMS = 0, this case corresponds to the counter running free from 0x0000 through 0xFFFF, but when CPWMS = 1 the counter needs a valid match to the modulus register somewhere other than at 0x0000 in order to change directions from up-counting to down-counting.

Figure 11-12 shows the output compare value in the TPM channel registers (multiplied by 2), which determines the pulse width (duty cycle) of the CPWM signal. If ELSnA = 0, the compare match while counting up forces the CPWM output signal low and a compare match while counting down forces the output high. The counter counts up until it reaches the modulo setting in TPMxMODH:TPMxMODL, then counts down until it reaches zero. This sets the period equal to two times TPMxMODH:TPMxMODL.

Figure 11-12. CPWM Period and Pulse Width (ELSnA = 0)

Center-aligned PWM outputs typically produce less noise than edge-aligned PWMs because fewer I/O pin transitions are lined up at the same system clock edge. This type of PWM is also required for some types of motor drives.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers, TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers. Values are

# Chapter 12 Development Support

# 12.1 Introduction

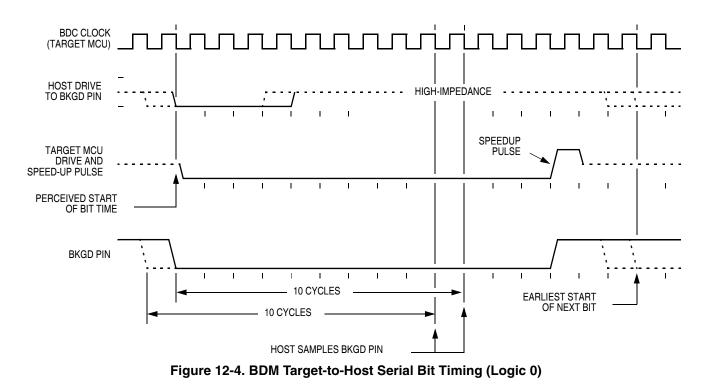

Development support systems in the HCS08 include the background debug controller (BDC). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip flash and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

# 12.1.1 Forcing Active Background

The method for forcing active background mode depends on the specific HCS08 derivative. For the MC9S08QD4 series, you can force active background mode by holding the BKGD pin low as the MCU exits the reset condition independent of what caused the reset. If no debug pod is connected to the BKGD pin, the MCU will always reset into normal operating mode.

# 12.1.2 Module Configuration

The alternative BDC clock source for MC9S08QD4 series is the ICGCLK. See Chapter 9, "Internal Clock Source (S08ICSV1)," for more information about ICGCLK and how to select clock sources.

**Development Support**

### 12.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 12-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 12-1 to describe the coding structure of the BDC commands.

# Appendix A Electrical Characteristics

# A.1 Introduction

This chapter contains electrical and timing specifications.

# A.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table A-1 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ) or the programmable pull-up resistor associated with the pin is enabled.

| Rating                                                                                          | Symbol           | Value                         | Unit |

|-------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                                  | V <sub>DD</sub>  | -0.3 to +5.8                  | V    |

| Maximum current into V <sub>DD</sub>                                                            | I <sub>DD</sub>  | 120                           | mA   |

| Digital input voltage                                                                           | V <sub>In</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | Ι <sub>D</sub>   | ±25                           | mA   |

| Storage temperature range                                                                       | T <sub>stg</sub> | –55 to 150                    | °C   |

Table A-1. Absolute Maximum Ratings

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2~$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}.$

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- A DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- A. DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |              | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------|--------------|----------------------------|-------------|

| TITLE:                                                  |                    | DOCUMENT NO  | ): 98ASB42564B             | REV: U      |

| 8LD SOIC NARROW BODY                                    |                    | CASE NUMBER  | 2: 751–07                  | 07 APR 2005 |

|                                                         |                    | STANDARD: JE | DEC MS-012AA               |             |