Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Active                                                               |

| Core Processor             | S08                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | -                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 4                                                                    |

| Program Memory Size        | 2KB (2K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 128 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 4x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                        |

| Supplier Device Package    | 8-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qd2vsc |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

#### http://freescale.com/

The following revision history table summarizes changes contained in this document.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | 15 Sep 06        | Initial public release                                                                                                                                                                                                |

| 2                  | 09 Jan 07        | Added MC9S08QD2 information; added "M" temperature range (-40 °C to 125 °C); updated temperature sensor equation in the ADC chapter.                                                                                  |

| 3                  | 19 Nov. 07       | Added S9S08QD4 and S9S08QD2 information for automotive applications. Revised "Accessing (read or write) any flash control register" to "Writing any flash control register" in Section 4.5.5, "Access Errors."        |

| 4                  | 9 Sep 08         | Changed the SPMSC3 in Section 5.6, "Low-Voltage Detect (LVD) System," and Section 5.6.4,<br>"Low-Voltage Warning (LVW)," to SPMSC2.<br>Added V <sub>POR</sub> to Table A-5.<br>Updated "How to Reach Us" information. |

| 5                  | 24 Nov 08        | Revised dc injection current in Table A-5.                                                                                                                                                                            |

| 6                  | 14 Oct 10        | Added T <sub>JMax</sub> in the Table A-2.                                                                                                                                                                             |

This product incorporates SuperFlash<sup>®</sup> technology licensed from SST.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. © Freescale Semiconductor, Inc., 2006-2010. All rights reserved.

MC9S08QD4 Series MCU Data Sheet, Rev. 6

## Chapter 12 Development Support

| 12.1 | Introduction                                                | 159 |

|------|-------------------------------------------------------------|-----|

|      | 12.1.1 Forcing Active Background                            | 159 |

|      | 12.1.2 Module Configuration                                 | 159 |

|      | 12.1.3 Features                                             |     |

| 12.2 | Background Debug Controller (BDC)                           | 160 |

|      | 12.2.1 BKGD Pin Description                                 | 161 |

|      | 12.2.2 Communication Details                                | 161 |

|      | 12.2.3 BDC Commands                                         | 164 |

|      | 12.2.4 BDC Hardware Breakpoint                              |     |

| 12.3 | Register Definition                                         |     |

|      | 12.3.1 BDC Registers and Control Bits                       |     |

|      | 12.3.2 System Background Debug Force Reset Register (SBDFR) | 170 |

### Appendix A Electrical Characteristics

| A.1 Introduction                          |     |

|-------------------------------------------|-----|

| A.2 Absolute Maximum Ratings              |     |

| A.3 Thermal Characteristics               | 174 |

| A.4 ESD Protection and Latch-Up Immunity  | 175 |

| A.5 DC Characteristics                    |     |

| A.6 Supply Current Characteristics        |     |

| A.7 Internal Clock Source Characteristics |     |

| A.8 AC Characteristics                    |     |

| A.8.1 Control Timing                      |     |

| A.8.2 Timer/PWM (TPM) Module Timing       |     |

| A.9 ADC Characteristics                   |     |

| A.10 Flash Specifications                 |     |

## Appendix B Ordering Information and Mechanical Drawings

| <b>B</b> .1 | Ordering Information          | 191 |

|-------------|-------------------------------|-----|

|             | B.1.1 Device Numbering Scheme |     |

| B.2         | Mechanical Drawings           |     |

# Chapter 1 Device Overview

# 1.1 Introduction

MC9S08QD4 series MCUs are members of the low-cost, high-performance HCS08 family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available with a variety of modules, memory sizes, memory types, and package types.

# 1.2 Devices in the MC9S08QD4 Series

This data sheet covers:

- MC9S08QD4

- MC9S08QD2

- S9S08QD4

- S9S08QD2

#### NOTE

- The MC9S08QD4 and MC9S08QD2 devices are qualified for, and are intended to be used in, *consumer and industrial* applications.

- The S9S08QD4 and S9S08QD2 devices are qualified for, and are intended to be used in, *automotive* applications.

Table 1-1 summarizes the features available in the MCUs.

**Chapter 4 Memory Map and Register Definition**

| Address                            | Register Name | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0    |

|------------------------------------|---------------|--------|-------|-------|-------|-------|-------|-------|----------|

| 0x00 <b>17</b>                     | APCTL1        | _      | _     | _     | _     | ADPC3 | ADPC2 | ADPC1 | ADPC0    |

| 0x00 <b>18</b>                     | Reserved      |        | _     |       |       | _     | _     | _     | _        |

| 0x00 <b>19</b>                     | Reserved      |        | _     |       |       |       | _     |       |          |

| 0x001 <b>A</b> –<br>0x001 <b>F</b> | Reserved      | _      | _     | _     |       | _     |       |       | _        |

| 0x00 <b>20</b>                     | TPM2SC        | TOF    | TOIE  | CPWMS | CLKSB | CLKSA | PS2   | PS1   | PS0      |

| 0x00 <b>21</b>                     | TPM2CNTH      | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8    |

| 0x00 <b>22</b>                     | TPM2CNTL      | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0    |

| 0x00 <b>23</b>                     | TPM2MODH      | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8    |

| 0x00 <b>24</b>                     | TPM2MODL      | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0    |

| 0x00 <b>25</b>                     | TPM2C0SC      | CH0F   | CH0IE | MS0B  | MS0A  | ELS0B | ELS0A | 0     | 0        |

| 0x00 <b>26</b>                     | TPM2C0VH      | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8    |

| 0x00 <b>27</b>                     | TPM2C0VL      | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0    |

| 0x00 <b>28</b> –<br>0x00 <b>37</b> | Reserved      |        | —     |       |       |       | —     |       | _        |

| 0x00 <b>38</b>                     | ICSC1         | 0      | CLKS  | 0     | 0     | 0     | 1     | 1     | IREFSTEN |

| 0x00 <b>39</b>                     | ICSC2         | BC     | VIV   | 0     | 0     | LP    | 0     | 0     | 0        |

| 0x00 <b>3A</b>                     | ICSTRM        |        |       | TRIM  |       |       |       |       |          |

| 0x00 <b>3B</b>                     | ICSSC         | 0      | 0     | 0     | 0     | 0     | CLKST | 0     | FTRIM    |

| 0x00 <b>3C</b>                     | Reserved      | _      | —     | _     | _     | _     | —     | _     |          |

| 0x00 <b>40</b>                     | TPMSC         | TOF    | TOIE  | CPWMS | CLKSB | CLKSA | PS2   | PS1   | PS0      |

| 0x00 <b>41</b>                     | TPMCNTH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8    |

| 0x00 <b>42</b>                     | TPMCNTL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0    |

| 0x00 <b>43</b>                     | TPMMODH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8    |

| 0x00 <b>44</b>                     | TPMMODL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0    |

| 0x00 <b>45</b>                     | TPMC0SC       | CH0F   | CH0IE | MS0B  | MS0A  | ELS0B | ELS0A | 0     | 0        |

| 0x00 <b>46</b>                     | TPMC0VH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8    |

| 0x00 <b>47</b>                     | TPMC0VL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0    |

| 0x00 <b>48</b>                     | TPMC1SC       | CH1F   | CH1IE | MS1B  | MS1A  | ELS1B | ELS1A | 0     | 0        |

| 0x00 <b>49</b>                     | TPMC1VH       | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8    |

| 0x00 <b>4A</b>                     | TPMC1VL       | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0    |

| 0x00 <b>4B</b> –<br>0x00 <b>5F</b> | Reserved      | _      | _     | _     |       |       | _     |       | _        |

Table 4-2. Direct-Page Register Summary (continued)

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

#### **Chapter 4 Memory Map and Register Definition**

program and erase pulses. An integer number of these timing pulses is used by the command processor to complete a program or erase command.

Table 4-5 shows program and erase times. The bus clock frequency and FCDIV determine the frequency of FCLK ( $f_{FCLK}$ ). The time for one cycle of FCLK is  $t_{FCLK} = 1/f_{FCLK}$ . The times are shown as a number of cycles of FCLK and as an absolute time for the case where  $t_{FCLK} = 5 \ \mu$ s. Program and erase times shown include overhead for the command state machine and enabling and disabling of program and erase voltages.

| Parameter            | Cycles of FCLK | Time if FCLK = 200 kHz |  |  |  |

|----------------------|----------------|------------------------|--|--|--|

| Byte program         | 9              | 45 μs                  |  |  |  |

| Byte program (burst) | 4              | 20 μs <sup>1</sup>     |  |  |  |

| Page erase           | 4000           | 20 ms                  |  |  |  |

| Mass erase           | 20,000         | 100 ms                 |  |  |  |

Table 4-5. Program and Erase Times

Excluding start/end overhead

### 4.5.3 **Program and Erase Command Execution**

The steps for executing any of the commands are listed below. The FCDIV register must be initialized and any error flags cleared before beginning command execution. The command execution steps are:

1. Write a data value to an address in the flash array. The address and data information from this write is latched into the flash interface. This write is a required first step in any command sequence. For erase and blank check commands, the value of the data is not important. For page erase commands, the address can be any address in the 512-byte page of flash to be erased. For mass erase and blank check commands, the address in the flash memory. Whole pages of 512 bytes are the smallest block of flash that can be erased.

#### NOTE

- A mass or page erase of the last page in flash will erase the factory programmed internal reference clock trim value.

- Do not program any byte in the flash more than once after a successful erase operation. Reprogramming bits in a byte which is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire flash memory. Programming without first erasing may disturb data stored in the flash.

- 2. Write the command code for the desired command to FCMD. The five valid commands are blank check (0x05), byte program (0x20), burst program (0x25), page erase (0x40), and mass erase (0x41). The command code is latched into the command buffer.

- 3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command.

Chapter 5 Resets, Interrupts, and General System Control

| Vector<br>Priority | Vector<br>Number    | Address<br>(High:Low)                 | Vector Name                                         | Module            | Source                                                              | Enable                                | Description                                                                                                 |  |  |  |

|--------------------|---------------------|---------------------------------------|-----------------------------------------------------|-------------------|---------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| Lower              | 31<br>through<br>24 | 0xFFC0:FFC1<br>through<br>0xFFCE:FFCF | Unused Vector Space<br>(available for user program) |                   |                                                                     |                                       |                                                                                                             |  |  |  |

|                    | 23                  | 0xFFD0:FFD1                           | Vrti                                                | System<br>control | RTIF                                                                | RTIE                                  | Real-time interrupt                                                                                         |  |  |  |

|                    | 22                  | 0xFFD2:FFD3                           | —                                                   |                   | —                                                                   |                                       | —                                                                                                           |  |  |  |

|                    | 21                  | 0xFFD4:FFD5                           | —                                                   | _                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 20                  | 0xFFD6:FFD7                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 19                  | 0xFFD8:FFD9                           | Vadc1                                               | ADC1              | COCO                                                                | AIEN                                  | ADC1                                                                                                        |  |  |  |

|                    | 18                  | 0xFFDA:FFDB                           | Vkeyboard1                                          | KBI1              | KBF                                                                 | KBIE                                  | Keyboard pins                                                                                               |  |  |  |

|                    | 17                  | 0xFFDC:FFDD                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 16                  | 0xFFDE:FFDF                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 15                  | 0xFFE0:FFE1                           | —                                                   | _                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 14                  | 0xFFE2:FFE3                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 13                  | 0xFFE4:FFE5                           | —                                                   | _                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 12                  | 0xFFE6:FFE7                           | —                                                   | _                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 11                  | 0xFFE8:FFE9                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 10                  | 0xFFEA:FFEB                           | Vtpm2ovf                                            | TPM2              | TOF                                                                 | TOIE                                  | TPM2 overflow                                                                                               |  |  |  |

|                    | 9                   | 0xFFEC:FFED                           | —                                                   |                   | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 8                   | 0xFFEE:FFEF                           | Vtpm2ch0                                            | TPM2              | CH0F                                                                | CH0IE                                 | TPM2 channel 0                                                                                              |  |  |  |

|                    | 7                   | 0xFFF0:FFF1                           | Vtpm1ovf                                            | TPM1              | TOF                                                                 | TOIE                                  | TPM1 overflow                                                                                               |  |  |  |

|                    | 6                   | 0xFFF2:FFF3                           | Vtpm1ch1                                            | TPM1              | CH1F                                                                | CH1IE                                 | TPM1 channel 1                                                                                              |  |  |  |

|                    | 5                   | 0xFFF4:FFF5                           | Vtpm1ch0                                            | TPM1              | CH0F                                                                | CH0IE                                 | TPM1 channel 0                                                                                              |  |  |  |

|                    | 4                   | 0xFFF6:FFF7                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |  |  |  |

|                    | 3                   | 0xFFF8:FFF9                           | Virq                                                | IRQ               | IRRQF                                                               | IRQIE                                 | IRQ pin                                                                                                     |  |  |  |

|                    | 2                   | 0xFFFA:FFFB                           | Vlvd                                                | System control    | LVDF                                                                | LVDIE                                 | Low voltage detect                                                                                          |  |  |  |

|                    | 1                   | 0xFFFC:FFFD                           | Vswi                                                | CPU               | SWI<br>Instruction                                                  | _                                     | Software interrupt                                                                                          |  |  |  |

| ¥<br>Higher        | 0                   | 0xFFFE:FFFF                           | Vreset                                              | System<br>control | COP<br>LVD<br>RESET pin<br>Illegal opcode<br>Illegal address<br>POR | COPE<br>LVDRE<br>RSTPE<br>—<br>—<br>— | Watchdog timer<br>Low-voltage detect<br>External pin<br>Illegal opcode<br>Illegal address<br>power-on-reset |  |  |  |

#### Table 5-2. Vector Summary

# 5.6 Low-Voltage Detect (LVD) System

The MC9S08QD4 series includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and an LVD circuit with a user selectable trip voltage, either high ( $V_{LVDH}$ ) or low ( $V_{LVDL}$ ). The LVD circuit is enabled when LVDE in SPMSC1 is high and the trip voltage is selected by LVDV in SPMSC2. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop1 or stop2, and the current consumption in stop3 with the LVD enabled will be greater.

- In stop1 mode, all internal registers including parallel I/O control and data registers are powered off. Each of the pins assumes its default reset state (output buffer and internal pullup disabled). Upon exit from stop1, all pins must be re-configured the same as if the MCU had been reset.

- Stop2 mode is a partial power-down mode, whereby latches maintain the pin state as before the STOP instruction was executed. CPU register status and the state of I/O registers must be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user must examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, I/O data previously stored in RAM, before the STOP instruction was executed, peripherals previously enabled will require being initialized and restored to their pre-stop condition. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access of pins is now permitted again in the user's application program.

- In stop3 mode, all pin states are maintained because internal logic stays powered up. Upon recovery, all pin functions are the same as before entering stop3.

# 6.4 Parallel I/O Registers

## 6.4.1 Port A Registers

This section provides information about the registers associated with the parallel I/O ports.

Refer to tables in Chapter 4, "Memory Map and Register Definition," for the absolute address assignments for all parallel I/O. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

## 6.4.1.1 Port A Data (PTAD)

|        | 7 | 6 | 5                  | 4                  | 3      | 2     | 1     | 0     |

|--------|---|---|--------------------|--------------------|--------|-------|-------|-------|

| R      | 0 | 0 | PTAD5 <sup>1</sup> | PTAD4 <sup>2</sup> | PTAD3  | PTAD2 | PTAD1 | PTAD0 |

| w      |   |   | T IADU             |                    | T IADO |       |       | TIADU |

| Reset: | 0 | 0 | 0                  | 0                  | 0      | 0     | 0     | 0     |

<sup>1</sup> Reads of bit PTAD5 always return the pin value of PTA5, regardless of the value stored in bit PTADD5.

<sup>2</sup> Reads of bit PTAD4 always return the contents of PTAD4, regardless of the value stored in bit PTADD4.

Figure 6-2. Port A Data Register (PTAD)

| Source<br>Form                                                                                                  | Operation                                                                                                | Address<br>Mode                                                                                          | Object Code                                                                      | es                              | Cyc-by-Cyc<br>Details                                                         |     | Affect<br>n CCR |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------|-----|-----------------|

|                                                                                                                 |                                                                                                          | Add<br>Mod                                                                                               |                                                                                  | Cycles                          |                                                                               | VH  | INZC            |

| BCLR <i>n,opr8a</i>                                                                                             | Clear Bit n in Memory<br>(Mn ← 0)                                                                        | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11 dd<br>13 dd<br>15 dd<br>17 dd<br>19 dd<br>1B dd<br>1D dd<br>1F dd             | 55555555                        | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp |     |                 |

| BCS rel                                                                                                         | Branch if Carry Bit Set (if C = 1)<br>(Same as BLO)                                                      | REL                                                                                                      | 25 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BEQ <i>rel</i>                                                                                                  | Branch if Equal (if Z = 1)                                                                               | REL                                                                                                      | 27 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BGE rel                                                                                                         | Branch if Greater Than or Equal To (if $N \oplus V = 0$ ) (Signed)                                       | REL                                                                                                      | 90 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BGND                                                                                                            | Enter active background if ENBDM=1<br>Waits for and processes BDM commands<br>until GO, TRACE1, or TAGGO | INH                                                                                                      | 82                                                                               | 5+                              | fpppp                                                                         |     |                 |

| BGT <i>rel</i>                                                                                                  | Branch if Greater Than (if Z I (N $\oplus$ V) = 0) (Signed)                                              | REL                                                                                                      | 92 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BHCC rel                                                                                                        | Branch if Half Carry Bit Clear (if H = 0)                                                                | REL                                                                                                      | 28 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BHCS rel                                                                                                        | Branch if Half Carry Bit Set (if H = 1)                                                                  | REL                                                                                                      | 29 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BHI <i>rel</i>                                                                                                  | Branch if Higher (if C   Z = 0)                                                                          | REL                                                                                                      | 22 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BHS rel                                                                                                         | Branch if Higher or Same (if C = 0)<br>(Same as BCC)                                                     | REL                                                                                                      | 24 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BIH <i>rel</i>                                                                                                  | Branch if IRQ Pin High (if IRQ pin = 1)                                                                  | REL                                                                                                      | 2F rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BIL <i>rel</i>                                                                                                  | Branch if IRQ Pin Low (if IRQ pin = 0)                                                                   | REL                                                                                                      | 2E rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BIT #opr8i<br>BIT opr8a<br>BIT opr16a<br>BIT oprx16,X<br>BIT oprx8,X<br>BIT ,X<br>BIT oprx16,SP<br>BIT oprx8,SP | Bit Test<br>(A) & (M)<br>(CCR Updated but Operands Not Changed)                                          | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                                      | A5 ii<br>B5 dd<br>C5 hh ll<br>D5 ee ff<br>E5 ff<br>F5<br>9E D5 ee ff<br>9E E5 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp                      | 0 – | - \$ \$ -       |

| BLE rel                                                                                                         | Branch if Less Than or Equal To (if Z   (N $\oplus$ V) = 1) (Signed)                                     | REL                                                                                                      | 93 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BLO <i>rel</i>                                                                                                  | Branch if Lower (if $C = 1$ ) (Same as BCS)                                                              | REL                                                                                                      | 25 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BLS <i>rel</i>                                                                                                  | Branch if Lower or Same (if $C \mid Z = 1$ )                                                             | REL                                                                                                      | 23 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BLT <i>rel</i>                                                                                                  | Branch if Less Than (if $N \oplus V = 1$ ) (Signed)                                                      | REL                                                                                                      | 91 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BMC rel                                                                                                         | Branch if Interrupt Mask Clear (if I = 0)                                                                | REL                                                                                                      | 2C rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BMI <i>rel</i>                                                                                                  | Branch if Minus (if N = 1)                                                                               | REL                                                                                                      | 2B rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BMS <i>rel</i>                                                                                                  | Branch if Interrupt Mask Set (if I = 1)                                                                  | REL                                                                                                      | 2D rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BNE <i>rel</i>                                                                                                  | Branch if Not Equal (if $Z = 0$ )                                                                        | REL                                                                                                      | 26 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BPL <i>rel</i>                                                                                                  | Branch if Plus (if $N = 0$ )                                                                             | REL                                                                                                      | 2A rr                                                                            | 3                               | qqq                                                                           |     |                 |

| Table 7-2 | Instruction | Set | Summarv | (Sheet 2 of 9) |

|-----------|-------------|-----|---------|----------------|

|           |             | Jei | Summary |                |

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                                     | Address<br>Mode                                     | Object Code                                                                      | es                                   | Cyc-by-Cyc<br>Details                                    | Affect<br>on CCR |                                  |  |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------|------------------|----------------------------------|--|

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                               | Add<br>Mod                                          |                                                                                  | Cycles                               |                                                          | VH               | INZC                             |  |

| CMP #opr8i<br>CMP opr8a<br>CMP opr16a<br>CMP oprx16,X<br>CMP oprx8,X<br>CMP ,X<br>CMP oprx16,SP<br>CMP oprx8,SP | Compare Accumulator with Memory<br>A – M<br>(CCR Updated But Operands Not Changed)                                                                                                                                                                                                                                                                                                                            | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A1 ii<br>B1 dd<br>C1 hh 11<br>D1 ee ff<br>E1 ff<br>F1<br>9E D1 ee ff<br>9E E1 ff | 2 3 4 4 3 3 5 4                      | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | ↓-               | - \$ \$ \$                       |  |

| COM opr8a<br>COMA<br>COMX<br>COM oprx8,X<br>COM ,X<br>COM oprx8,SP                                              | $\begin{array}{lll} \mbox{Complement} & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \\ \mbox{(One's Complement)} & \mbox{A} \leftarrow (\overline{A}) = \$ FF - (A) \\ & \mbox{X} \leftarrow (\overline{X}) = \$ FF - (X) \\ & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \\ & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \\ & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \end{array}$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33 dd<br>43<br>53<br>63 ff<br>73<br>9E 63 ff                                     | 5<br>1<br>1<br>5<br>4<br>6           | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp                    | 0 -              | - ↓ ↓ 1                          |  |

| CPHX <i>opr16a</i><br>CPHX # <i>opr16i</i><br>CPHX <i>opr8a</i><br>CPHX <i>oprx8</i> ,SP                        | Compare Index Register (H:X) with Memory<br>(H:X) – (M:M + \$0001)<br>(CCR Updated But Operands Not Changed)                                                                                                                                                                                                                                                                                                  | EXT<br>IMM<br>DIR<br>SP1                            | 3E hh ll<br>65 jj kk<br>75 dd<br>9E F3 ff                                        | 6<br>3<br>5<br>6                     | prrfpp<br>ppp<br>rrfpp<br>prrfpp                         | 1−               | - ↓ ↓ ↓                          |  |

| CPX #opr8i<br>CPX opr8a<br>CPX opr16a<br>CPX oprx16,X<br>CPX oprx8,X<br>CPX ,X<br>CPX oprx16,SP<br>CPX oprx8,SP | Compare X (Index Register Low) with<br>Memory<br>X – M<br>(CCR Updated But Operands Not Changed)                                                                                                                                                                                                                                                                                                              | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A3 ii<br>B3 dd<br>C3 hh 11<br>D3 ee ff<br>E3 ff<br>F3<br>9E D3 ee ff<br>9E E3 ff | 2 3 4 4 3 3 5 4                      | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | ↓-               | - \$ \$ \$                       |  |

| DAA                                                                                                             | Decimal Adjust Accumulator<br>After ADD or ADC of BCD Values                                                                                                                                                                                                                                                                                                                                                  | INH                                                 | 72                                                                               | 1                                    | p                                                        | U–               | $- \uparrow \uparrow \uparrow$   |  |

| DBNZ opr8a,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ oprx8,X,rel<br>DBNZ ,X,rel<br>DBNZ oprx8,SP,rel                | Decrement A, X, or M and Branch if Not Zero<br>(if (result) ≠ 0)<br>DBNZX Affects X Not H                                                                                                                                                                                                                                                                                                                     | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B dd rr<br>4B rr<br>5B rr<br>6B ff rr<br>7B rr<br>9E 6B ff rr                   | 7<br>4<br>7<br>6<br>8                | rfwpppp<br>fppp<br>fppp<br>rfwpppp<br>rfwppp<br>prfwppp  |                  |                                  |  |

| DEC opr8a<br>DECA<br>DECX<br>DEC oprx8,X<br>DEC ,X<br>DEC oprx8,SP                                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                          | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A dd<br>4A<br>5A<br>6A ff<br>7A<br>9E 6A ff                                     | 5<br>1<br>5<br>4<br>6                | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp               | ↓-               | - \$ \$ -                        |  |

| DIV                                                                                                             | Divide $A \leftarrow (H:A) \div (X); H \leftarrow Remainder$                                                                                                                                                                                                                                                                                                                                                  | INH                                                 | 52                                                                               | 6                                    | fffffp                                                   |                  | $$ $\updownarrow$ $\updownarrow$ |  |

| EOR #opr8i<br>EOR opr8a<br>EOR opr16a<br>EOR oprx16,X<br>EOR oprx8,X<br>EOR ,X<br>EOR oprx16,SP<br>EOR oprx8,SP | Exclusive OR Memory with Accumulator $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                              | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A8 ii<br>B8 dd<br>C8 hh 11<br>D8 ee ff<br>E8 ff<br>F8<br>9E D8 ee ff<br>9E E8 ff | 2<br>3<br>4<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp         | 0                | - \$ \$ -                        |  |

| Table 7-2. Instruction | Set Summary | (Sheet 4 of 9) |

|------------------------|-------------|----------------|

|------------------------|-------------|----------------|

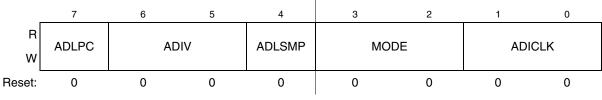

Figure 8-10. Configuration Register (ADCCFG)

#### Table 8-5. ADCCFG Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADLPC    | <ul> <li>Low Power Configuration — ADLPC controls the speed and power configuration of the successive approximation converter. This is used to optimize power consumption when higher sample rates are not required.</li> <li>0 High speed configuration</li> <li>1 Low power configuration: {FC31}The power is reduced at the expense of maximum clock speed.</li> </ul>                                                                                                    |

| 6:5<br>ADIV   | Clock Divide Select — ADIV select the divide ratio used by the ADC to generate the internal clock ADCK.<br>Table 8-6 shows the available clock configurations.                                                                                                                                                                                                                                                                                                               |

| 4<br>ADLSMP   | <ul> <li>Long Sample Time Configuration — ADLSMP selects between long and short sample time. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption when continuous conversions are enabled if high conversion rates are not required.</li> <li>Short sample time</li> <li>Long sample time</li> </ul> |

| 3:2<br>MODE   | <b>Conversion Mode Selection</b> — MODE bits are used to select between 10- or 8-bit operation. See Table 8-7.                                                                                                                                                                                                                                                                                                                                                               |

| 1:0<br>ADICLK | Input Clock Select — ADICLK bits select the input clock source to generate the internal clock ADCK. See Table 8-8.                                                                                                                                                                                                                                                                                                                                                           |

#### Table 8-6. Clock Divide Select

| ADIV | Divide Ratio | Clock Rate      |

|------|--------------|-----------------|

| 00   | 1            | Input clock     |

| 01   | 2            | Input clock ÷ 2 |

| 10   | 4            | Input clock ÷ 4 |

| 11   | 8            | Input clock ÷ 8 |

#### Table 8-7. Conversion Modes

| MODE | Mode Description         |  |  |

|------|--------------------------|--|--|

| 00   | 8-bit conversion (N=8)   |  |  |

| 01   | Reserved                 |  |  |

| 10   | 10-bit conversion (N=10) |  |  |

| 11   | Reserved                 |  |  |

result of the conversion is transferred to ADCRH and ADCRL upon completion of the conversion algorithm.

If the bus frequency is less than the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when short sample is enabled (ADLSMP=0). If the bus frequency is less than 1/11th of the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when long sample is enabled (ADLSMP=1).

The maximum total conversion time for different conditions is summarized in Table 8-12.

| Conversion Type                                            | ADICLK | ADLSMP | Max Total Conversion Time                |  |

|------------------------------------------------------------|--------|--------|------------------------------------------|--|

| Single or first continuous 8-bit                           | 0x, 10 | 0      | 20 ADCK cycles + 5 bus clock cycles      |  |

| Single or first continuous 10-bit                          | 0x, 10 | 0      | 23 ADCK cycles + 5 bus clock cycles      |  |

| Single or first continuous 8-bit                           | 0x, 10 | 1      | 40 ADCK cycles + 5 bus clock cycles      |  |

| Single or first continuous 10-bit                          | 0x, 10 | 1      | 43 ADCK cycles + 5 bus clock cycles      |  |

| Single or first continuous 8-bit                           | 11     | 0      | 5 μs + 20 ADCK + 5 bus clock cycles      |  |

| Single or first continuous 10-bit                          | 11     | 0      | 5 μs + 23 ADCK + 5 bus clock cycles      |  |

| Single or first continuous 8-bit                           | 11     | 1      | 5 $\mu$ s + 40 ADCK + 5 bus clock cycles |  |

| Single or first continuous 10-bit                          | 11     | 1      | 5 μs + 43 ADCK + 5 bus clock cycles      |  |

| Subsequent continuous 8-bit;<br>$f_{BUS} \ge f_{ADCK}$     | xx     | 0      | 17 ADCK cycles                           |  |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}$    | xx     | 0      | 20 ADCK cycles                           |  |

| Subsequent continuous 8-bit;<br>$f_{BUS} \ge f_{ADCK}/11$  | xx     | 1      | 37 ADCK cycles                           |  |

| Subsequent continuous 10-bit;<br>$f_{BUS} \ge f_{ADCK}/11$ | xx     | 1      | 40 ADCK cycles                           |  |

Table 8-12. Total Conversion Time vs. Control Conditions

The maximum total conversion time is determined by the clock source chosen and the divide ratio selected. The clock source is selectable by the ADICLK bits, and the divide ratio is specified by the ADIV bits. For example, in 10-bit mode, with the bus clock selected as the input clock source, the input clock divide-by-1 ratio selected, and a bus frequency of 8 MHz, then the conversion time for a single conversion is:

Conversion time =  $\frac{23 \text{ ADCK cyc}}{8 \text{ MHz/1}} + \frac{5 \text{ bus cyc}}{8 \text{ MHz}} = 3.5 \text{ }\mu\text{s}$

Number of bus cycles =  $3.5 \ \mu s \ x \ 8 \ MHz = 28 \ cycles$

#### NOTE

The ADCK frequency must be between  $f_{ADCK}$  minimum and  $f_{ADCK}$  maximum to meet ADC specifications.

MC9S08QD4 Series MCU Data Sheet, Rev. 6

Analog-to-Digital Converter (S08ADC10V1)

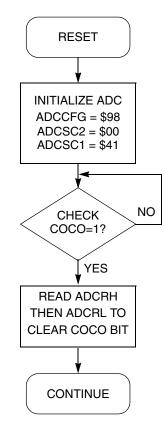

Figure 8-14. Initialization Flowchart for Example

# 8.6 Application Information

This section contains information for using the ADC module in applications. The ADC has been designed to be integrated into a microcontroller for use in embedded control applications requiring an A/D converter.

## 8.6.1 External Pins and Routing

The following sections discuss the external pins associated with the ADC module and how they must be used for best results.

### 8.6.1.1 Analog Supply Pins

The ADC module has analog power and ground supplies ( $V_{DDAD}$  and  $V_{SSAD}$ ) which are available as separate pins on some devices. On other devices,  $V_{SSAD}$  is shared on the same pin as the MCU digital  $V_{SS}$ , and on others, both  $V_{SSAD}$  and  $V_{DDAD}$  are shared with the MCU digital supply pins. In these cases, there are separate pads for the analog supplies which are bonded to the same pin as the corresponding digital supply so that some degree of isolation between the supplies is maintained.

When available on a separate pin, both  $V_{DDAD}$  and  $V_{SSAD}$  must be connected to the same voltage potential as their corresponding MCU digital supply ( $V_{DD}$  and  $V_{SS}$ ) and must be routed carefully for maximum noise immunity and bypass capacitors placed as near as possible to the package.

## 9.1.2 Features

Key features of the ICS module are:

- Frequency-locked loop (FLL) is trimmable for accuracy

- 0.2% resolution using internal 32 kHz reference

- 2% deviation over voltage and temperature using internal 32 kHz reference

- Internal or external reference clocks up to 5 MHz can be used to control the FLL

- 3 bit select for reference divider is provided

- Internal reference clock has 9 trim bits available

- Internal or external reference clocks can be selected as the clock source for the MCU

- Whichever clock is selected as the source can be divided down

- 2 bit select for clock divider is provided

- Allowable dividers are: 1, 2, 4, 8

- BDC clock is provided as a constant divide by 2 of the DCO output

- Control signals for a low power oscillator as the external reference clock are provided — HGO, RANGE, EREFS, ERCLKEN, EREFSTEN

- FLL engaged internal mode is automatically selected out of reset

### 9.1.3 Modes of Operation

There are seven modes of operation for the ICS: FEI, FEE, FBI, FBILP, FBE, FBELP, and stop.

## 9.1.3.1 FLL Engaged Internal (FEI)

In FLL engaged internal mode, which is the default mode, the ICS supplies a clock derived from the FLL which is controlled by the internal reference clock. The BDC clock is supplied from the FLL.

## 9.1.3.2 FLL Engaged External (FEE)

In FLL engaged external mode, the ICS supplies a clock derived from the FLL which is controlled by an external reference clock. The BDC clock is supplied from the FLL.

## 9.1.3.3 FLL Bypassed Internal (FBI)

In FLL bypassed internal mode, the FLL is enabled and controlled by the internal reference clock, but is bypassed. The ICS supplies a clock derived from the internal reference clock. The BDC clock is supplied from the FLL.

## 9.1.3.4 FLL Bypassed Internal Low Power (FBILP)

In FLL bypassed internal low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the internal reference clock. The BDC clock is not available.

Internal Clock Source (S08ICSV1)

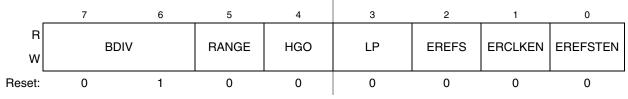

# 9.3.2 ICS Control Register 2 (ICSC2)

#### Figure 9-4. ICS Control Register 2 (ICSC2)

#### Table 9-2. ICS Control Register 2 Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>BDIV   | Bus Frequency Divider — Selects the amount to divide down the clock source selected by the CLKS bits. This controls the bus frequency.         00       Encoding 0 — Divides selected clock by 1         01       Encoding 1 — Divides selected clock by 2 (reset default)         10       Encoding 2 — Divides selected clock by 4         11       Encoding 3 — Divides selected clock by 8 |

| 5<br>RANGE    | <ul> <li>Frequency Range Select — Selects the frequency range for the external oscillator.</li> <li>1 High frequency range selected for the external oscillator</li> <li>0 Low frequency range selected for the external oscillator</li> </ul>                                                                                                                                                 |

| 4<br>HGO      | <ul> <li>High Gain Oscillator Select — The HGO bit controls the external oscillator mode of operation.</li> <li>Configure external oscillator for high gain operation</li> <li>Configure external oscillator for low power operation</li> </ul>                                                                                                                                                |

| 3<br>LP       | <ul> <li>Low Power Select — The LP bit controls whether the FLL is disabled in FLL bypassed modes.</li> <li>1 FLL is disabled in bypass modes unless BDM is active</li> <li>0 FLL is not disabled in bypass mode</li> </ul>                                                                                                                                                                    |

| 2<br>EREFS    | <ul> <li>External Reference Select — The EREFS bit selects the source for the external reference clock.</li> <li>1 Oscillator requested</li> <li>0 External Clock Source requested</li> </ul>                                                                                                                                                                                                  |

| 1<br>ERCLKEN  | External Reference Enable — The ERCLKEN bit enables the external reference clock for use as ICSERCLK.<br>1 ICSERCLK active<br>0 ICSERCLK inactive                                                                                                                                                                                                                                              |

| 0<br>EREFSTEN | <ul> <li>External Reference Stop Enable — The EREFSTEN bit controls whether or not the external reference clock remains enabled when the ICS enters stop mode.</li> <li>1 External reference clock stays enabled in stop if ERCLKEN is set or if ICS is in FEE, FBE, or FBELP mode before entering stop</li> <li>0 External reference clock is disabled in stop</li> </ul>                     |

Internal Clock Source (S08ICSV1)

# 9.4.7 Fixed Frequency Clock

The ICS presents the divided FLL reference clock as ICSFFCLK for use as an additional clock source for peripheral modules. The ICS provides an output signal (ICSFFE) which indicates when the ICS is providing ICSOUT frequencies four times or greater than the divided FLL reference clock (ICSFFCLK). In FLL engaged mode (FEI and FEE) this is always true and ICSFFE is always high. In ICS bypass modes, ICSFFE will get asserted for the following combinations of BDIV and RDIV values:

- BDIV=00 (divide by 1), RDIV  $\ge$  010

- BDIV=01 (divide by 2), RDIV  $\ge$  011

- BDIV=10 (divide by 4), RDIV  $\geq$  100

- BDIV=11 (divide by 8), RDIV  $\ge$  101

# 9.5 Module Initialization

This section describes how to initialize and configure the ICS module. The following sections contain two initialization examples.

## 9.5.1 ICS Module Initialization Sequence

The ICS comes out of POR configured for FEI mode with the BDIV set for divide-by 2. The internal reference will stabilize in  $t_{IRST}$  microseconds before the FLL can acquire lock. As soon as the internal reference is stable, the FLL will acquire lock in  $t_{Acquire}$  milliseconds.

Upon POR, the internal reference will require trimming to guarantee an accurate clock. Freescale recommends using FLASH location 0xFFAE for storing the fine trim bit, FTRIM in the ICSSC register, and 0xFFAF for storing the 8-bit trim value for the ICSTRM register. The MCU will not automatically copy the values in these FLASH locations to the respective registers. Therefore, user code must copy these values from FLASH to the registers.

#### NOTE

The BDIV value must not be changed to divide-by 1 without first trimming the internal reference. Failure to do so could result in the MCU running out of specification.

## 9.5.1.1 Initialization Sequence, Internal Clock Mode to External Clock Mode

To change from FEI or FBI clock modes to FEE or FBE clock modes, follow this procedure:

- 1. Enable the external clock source by setting the appropriate bits in ICSC2.

- If FBE will be the selected mode, also set the LP bit at this time to minimize power consumption.

- 2. If necessary, wait for the external clock source to stabilize. Typical crystal startup times are given in Electrical Characteristics appendix. If EREFS is set in step 1, then the OSCINIT bit will set as soon as the oscillator has completed the initialization cycles.

- 3. Write to ICSC1 to select the clock mode.

Internal Clock Source (S08ICSV1)

All TPM channels are programmable independently as input capture, output compare, or buffered edge-aligned PWM channels.

## 11.2 External Signal Description

When any pin associated with the timer is configured as a timer input, a passive pullup can be enabled. After reset, the TPM modules are disabled and all pins default to general-purpose inputs with the passive pullups disabled.

## 11.2.1 External TPM Clock Sources

When control bits CLKSB:CLKSA in the timer status and control register are set to 1:1, the prescaler and consequently the 16-bit counter for TPMx are driven by an external clock source, TPMxCLK, connected to an I/O pin. A synchronizer is needed between the external clock and the rest of the TPM. This synchronizer is clocked by the bus clock so the frequency of the external source must be less than one-half the frequency of the bus rate clock. The upper frequency limit for this external clock source is specified to be one-fourth the bus frequency to conservatively accommodate duty cycle and phase-locked loop (PLL) or frequency-locked loop (FLL) frequency jitter effects.

On some devices the external clock input is shared with one of the TPM channels. When a TPM channel is shared as the external clock input, the associated TPM channel cannot use the pin. (The channel can still be used in output compare mode as a software timer.) Also, if one of the TPM channels is used as the external clock input, the corresponding ELSnB:ELSnA control bits must be set to 0:0 so the channel is not trying to use the same pin.

## 11.2.2 TPMxCHn — TPMx Channel n I/O Pins

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the configuration of the channel. In some cases, no pin function is needed so the pin reverts to being controlled by general-purpose I/O controls. When a timer has control of a port pin, the port data and data direction registers do not affect the related pin(s). See the Pins and Connections chapter for additional information about shared pin functions.

# 11.3 Register Definition

The TPM includes:

- An 8-bit status and control register (TPMxSC)

- A 16-bit counter (TPMxCNTH:TPMxCNTL)

- A 16-bit modulo register (TPMxMODH:TPMxMODL)

Each timer channel has:

- An 8-bit status and control register (TPMxCnSC)

- A 16-bit channel value register (TPMxCnVH:TPMxCnVL)

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all TPM registers. This section refers to registers and control bits only by their names. A

#### Timer/Pulse-Width Modulator (S08TPMV2)

When center-aligned PWM operation is specified, the counter counts upward from 0x0000 through its terminal count and then counts downward to 0x0000 where it returns to up-counting. Both 0x0000 and the terminal count value (value in TPMxMODH:TPMxMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The 0x0000 count value corresponds to the center of a period.)

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter for read operations. Whenever either byte of the counter is read (TPMxCNTH or TPMxCNTL), both bytes are captured into a buffer so when the other byte is read, the value will represent the other byte of the count at the time the first byte was read. The counter continues to count normally, but no new value can be read from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer count TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only one byte of the counter was read before resetting the count.

### 11.4.2 Channel Mode Selection

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

#### 11.4.2.1 Input Capture Mode

With the input capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter into the channel value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An input capture event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

MC9S08QD4 Series MCU Data Sheet, Rev. 6

**Appendix A Electrical Characteristics**

# A.8 AC Characteristics

This section describes AC timing characteristics for each peripheral system.

## A.8.1 Control Timing

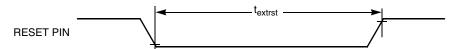

#### Table A-8. Control Timing

| Parameter                                                                                                                             | Symbol                                | Min                         | Typical <sup>1</sup> | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|----------------------|------|------|

| Bus frequency $(t_{cyc} = 1/f_{Bus})$                                                                                                 | f <sub>Bus</sub>                      | 1                           | _                    | 8    | MHz  |

| Real-time interrupt internal oscillator period                                                                                        | t <sub>RTI</sub>                      | 700                         | —                    | 1300 | μS   |

| External reset pulse width <sup>2</sup>                                                                                               | t <sub>extrst</sub>                   | 100                         | _                    | —    | ns   |