Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | S08                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | -                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 4                                                                    |

| Program Memory Size        | 4KB (4K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 4x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                               |

| Supplier Device Package    | 8-PDIP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qd4mpc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## MC9S08QD4 Data Sheet

Covers: MC9S08QD4

MC9S08QD2

S9S08QD4

S9S08QD2

MC9S08QD4 Rev. 6 10/2010

| 9.5  | Module Initialization                                                              | 132 |

|------|------------------------------------------------------------------------------------|-----|

|      | 9.5.1 ICS Module Initialization Sequence                                           | 132 |

|      | Chamtau 10                                                                         |     |

|      | Chapter 10 Keyboard Interrupt (S08KBIV2)                                           |     |

| 10.1 | Introduction                                                                       | 135 |

| 10.1 | 10.1.1 Features                                                                    |     |

|      | 10.1.2 Modes of Operation                                                          |     |

|      | 10.1.3 Block Diagram                                                               |     |

| 10.2 | External Signal Description                                                        |     |

|      | Register Definition                                                                |     |

|      | 10.3.1 KBI Status and Control Register (KBISC)                                     | 138 |

|      | 10.3.2 KBI Pin Enable Register (KBIPE)                                             | 139 |

|      | 10.3.3 KBI Edge Select Register (KBIES)                                            |     |

| 10.4 | Functional Description                                                             |     |

|      | 10.4.1 Edge Only Sensitivity                                                       |     |

|      | 10.4.2 Edge and Level Sensitivity                                                  |     |

|      | 10.4.3 KBI Pullup/Pulldown Resistors                                               |     |

|      | 10.4.4 KBI Initialization                                                          | 141 |

|      | Chapter 11                                                                         |     |

|      | Timer/Pulse-Width Modulator (S08TPMV2)                                             |     |

| 11.1 | Introduction                                                                       | 143 |

|      | 11.1.1 TPM2 Configuration Information                                              |     |

|      | 11.1.2 TCLK1 and TCLK2 Configuration Information                                   |     |

|      | 11.1.3 Features                                                                    |     |

|      | 11.1.4 Block Diagram                                                               | 145 |

| 11.2 | External Signal Description                                                        | 147 |

|      | 11.2.1 External TPM Clock Sources                                                  |     |

|      | 11.2.2 TPMxCHn — TPMx Channel n I/O Pins                                           |     |

| 11.3 | Register Definition                                                                |     |

|      | 11.3.1 Timer Status and Control Register (TPMxSC)                                  |     |

|      | 11.3.2 Timer Counter Registers (TPMxCNTH:TPMxCNTL)                                 |     |

|      | 11.3.3 Timer Counter Modulo Registers (TPMxMODH:TPMxMODL)                          |     |

|      | 11.3.4 Timer Channel n Status and Control Register (TPMxCnSC)                      |     |

| 11 / | 11.3.5 Timer Channel Value Registers (TPMxCnVH:TPMxCnVL)                           |     |

| 11.4 | Functional Description                                                             |     |

|      | 11.4.1 Counter                                                                     |     |

|      | 11.4.2 Channel Mode Selection  11.4.3 Center-Aligned PWM Mode                      |     |

| 11.5 | TPM Interrupts                                                                     |     |

| 11.3 | 11.5.1 Clearing Timer Interrupt Flags                                              |     |

|      | 11.5.1 Clearing Timer Interrupt Plags  11.5.2 Timer Overflow Interrupt Description |     |

|      | 11.5.3 Channel Event Interrupt Description                                         |     |

|      | 11.5.4 PWM End-of-Duty-Cycle Events                                                |     |

|      | The state of Day of Division                                                       | 130 |

Table 4-3. High-Page Register Summary

| Address           | Register Name | Bit 7   | 6      | 5       | 4       | 3      | 2      | 1      | Bit 0  |

|-------------------|---------------|---------|--------|---------|---------|--------|--------|--------|--------|

| 0x1800            | SRS           | POR     | PIN    | COP     | ILOP    | ILAD   | 0      | LVD    | 0      |

| 0x1801            | SBDFR         | 0       | 0      | 0       | 0       | 0      | 0      | 0      | BDFR   |

| 0x1802            | SOPT1         | COPE    | COPT   | STOPE   | 0       | 0      | 0      | BKGDPE | RSTPE  |

| 0x1803            | SOPT2         | COPCLKS | 0      | 0       | 0       | 0      | 0      | 0      | 0      |

| 0x <b>1804</b>    | Reserved      | _       | -      | _       | _       | _      | -      | -      | _      |

| 0x1805            | Reserved      | _       | -      | _       | _       | _      | -      | _      | _      |

| 0x1806            | SDIDH         | REV3    | REV2   | REV1    | REV0    | ID11   | ID10   | ID9    | ID8    |

| 0x1807            | SDIDL         | ID7     | ID6    | ID5     | ID4     | ID3    | ID2    | ID1    | ID0    |

| 0x1808            | SRTISC        | RTIF    | RTIACK | RTICLKS | RTIE    | 0      |        | RTIS   |        |

| 0x1809            | SPMSC1        | LVDF    | LVDACK | LVDIE   | LVDRE   | LVDSE  | LVDE   | 01     | BGBE   |

| 0x180A            | SPMSC2        | LVWF    | LVWACK | LVDV    | LVWV    | PPDF   | PPDACK | _      | PPDC   |

| 0x180B-<br>0x181F | Reserved      |         | _      | _<br>_  | _<br>_  |        | _<br>_ |        | _      |

| 0x1820            | FCDIV         | DIVLD   | PRDIV8 |         |         | D      | V      |        |        |

| 0x1821            | FOPT          | KEYEN   | FNORED | 0       | 0       | 0      | 0      | SEC01  | SEC00  |

| 0x1822            | Reserved      | _       | _      | _       | _       | _      | _      | _      | _      |

| 0x1823            | FCNFG         | 0       | 0      | KEYACC  | 0       | 0      | 0      | 0      | 0      |

| 0x1824            | FPROT         |         |        |         | FPS     |        |        |        | FPDIS  |

| 0x1825            | FSTAT         | FCBEF   | FCCF   | FPVIOL  | FACCERR | 0      | FBLANK | 0      | 0      |

| 0x1826            | FCMD          |         |        |         | FC      | MD     |        |        |        |

| 0x1827-<br>0x183F | Reserved      |         |        |         |         |        |        |        | _      |

| 0x1840            | PTAPE         | 0       | 0      | PTAPE5  | PTAPE4  | PTAPE3 | PTAPE2 | PTAPE1 | PTAPE0 |

| 0x1841            | PTASE         | 0       | 0      | PTASE5  | PTASE4  | PTASE3 | PTASE2 | PTASE1 | PTASE0 |

| 0x1842            | PTADS         | 0       | 0      | PTADS5  | PTADS4  | PTADS3 | PTADS2 | PTADS1 | PTADS0 |

| 0x1843-<br>0x1847 | Reserved      |         | 1 1    | 1 1     | 1 1     | 1 1    | 1 1    | 1 1    | _      |

<sup>&</sup>lt;sup>1</sup> This reserved bit must always be written to 0.

Nonvolatile flash registers, shown in Table 4-4, are located in the flash memory. These registers include an 8-byte backdoor key that optionally can be used to gain access to secure memory resources. During reset events, the contents of NVPROT and NVOPT in the nonvolatile register area of the flash memory are transferred into corresponding FPROT and FOPT working registers in the high-page registers to control security and block protection options.

**Chapter 4 Memory Map and Register Definition**

Chapter 5 Resets, Interrupts, and General System Control

Table 5-11. Real-Time Interrupt Period

| RTIS2:RTIS1:RTIS0 | Using Internal 1 kHz Clock Source <sup>1 2</sup> | Using 32 kHz ICS Clock Source<br>Period = t <sub>ext</sub> <sup>3</sup> |

|-------------------|--------------------------------------------------|-------------------------------------------------------------------------|

| 0:0:0             | Disable RTI                                      | Disable RTI                                                             |

| 0:0:1             | 8 ms                                             | t <sub>ext</sub> × 256                                                  |

| 0:1:0             | 32 ms                                            | t <sub>ext</sub> × 1024                                                 |

| 0:1:1             | 64 ms                                            | $t_{\text{ext}} \times 2048$                                            |

| 1:0:0             | 128 ms                                           | $t_{\text{ext}} \times 4096$                                            |

| 1:0:1             | 256 ms                                           | t <sub>ext</sub> × 8192                                                 |

| 1:1:0             | 512 ms                                           | t <sub>ext</sub> × 16384                                                |

| 1:1:1             | 1.024 s                                          | t <sub>ext</sub> × 32768                                                |

<sup>&</sup>lt;sup>1</sup> Values are shown in this column based on t<sub>RTI</sub> = 1 ms. See t<sub>RTI</sub> in the Section A.8.1, "Control Timing," for the tolerance of this value.

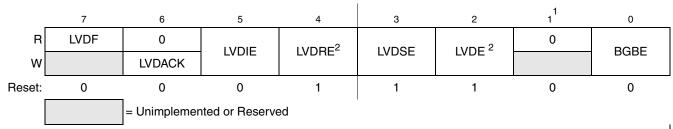

# 5.8.8 System Power Management Status and Control 1 Register (SPMSC1)

This high-page register contains status and control bits to support the low voltage detect function, and to enable the bandgap voltage reference for use by the ADC module. To configure the low voltage detect trip voltage, see Table 5-13 for the LVDV bit description in SPMSC2.

<sup>&</sup>lt;sup>1</sup> Bit 1 is a reserved bit that must always be written to 0.

Figure 5-10. System Power Management Status and Control 1 Register (SPMSC1)

Table 5-12. SPMSC1 Register Field Descriptions

| Field     | Description                                                                                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVDF | Low-Voltage Detect Flag — Provided LVDE = 1, this read-only status bit indicates a low-voltage detect event.                                                    |

|           | <b>Low-Voltage Detect Acknowledge</b> — This write-only bit is used to acknowledge low voltage detection errors (write 1 to clear LVDF). Reads always return 0. |

MC9S08QD4 Series MCU Data Sheet, Rev. 6

<sup>&</sup>lt;sup>2</sup> The initial RTI timeout period will be up to one 1 kHz clock period less than the time specified.

<sup>&</sup>lt;sup>3</sup> t<sub>ext</sub> is the period of the 32 kHz ICS frequency.

<sup>&</sup>lt;sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Chapter 5 Resets, Interrupts, and General System Control

#### Table 5-13. SPMSC2 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVWF   | Low-Voltage Warning Flag — The LVWF bit indicates the low voltage warning status.  0 Low voltage warning not preset.  1 Low voltage warning is present or was present.                                                                            |

| 6<br>LVWACK | Low-Voltage Warning Acknowledge — The LVWACK bit is the low-voltage warning acknowledge. Writing a 1 to LVWACK clears LVWF to a 0 if a low voltage warning is not present.                                                                        |

| 5<br>LVDV   | Low-Voltage Detect Voltage Select — The LVDV bit selects the LVD trip point voltage (V <sub>LVD</sub> ).  0 Low trip point selected (V <sub>LVD</sub> = V <sub>LVDL</sub> ).  1 High trip point selected (V <sub>LVD</sub> = V <sub>LVDH</sub> ). |

| 4<br>LVWV   | <b>Low-Voltage Warning Voltage Select</b> — The LVWV bit selects the LVW trip point voltage $(V_{LVW})$ .  0 Low trip point selected $(V_{LVW} = V_{LVWL})$ .  1 High trip point selected $(V_{LVW} = V_{LVWH})$ .                                |

| 3<br>PPDF   | Partial Power Down Flag — The PPDF bit indicates that the MCU has exited the stop2 mode.  0 Not stop2 mode recovery.  1 Stop2 mode recovery.                                                                                                      |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit.                                                                                                                                                                       |

| 0<br>PPDC   | Partial Power Down Control — The write-once PPDC bit controls whether stop2 or stop3 mode is selected.  O Stop3 mode enabled.  Stop2, partial power down, mode enabled.                                                                           |

#### Chapter 7 Central Processor Unit (S08CPUV2)

#### Table 7-3. Opcode Map (Sheet 2 of 2)

| Bit-Manipulation Branch Read-Modify-Write |     |  |  | Control Register/Memory |  |  |  |                        |      |            |                                 |                        |                         |

|-------------------------------------------|-----|--|--|-------------------------|--|--|--|------------------------|------|------------|---------------------------------|------------------------|-------------------------|

|                                           | 2.0 |  |  | 9E60 6                  |  |  |  |                        |      | . regione. | 9ED0 5                          | 9EE0 4                 |                         |

|                                           |     |  |  | NEG<br>3 SP1            |  |  |  |                        |      |            | 9ED0 5<br>SUB<br>4 SP2          | SUB<br>3 SP1           |                         |

|                                           |     |  |  | 9E61 6<br>CBEQ          |  |  |  |                        |      |            | 9ED1 5<br>CMP                   | 9EE1 4<br>CMP          |                         |

|                                           |     |  |  | 4 SP1                   |  |  |  |                        |      |            | 4 SP2                           | 3 SP1                  |                         |

|                                           |     |  |  |                         |  |  |  |                        |      |            | SBC<br>4 SP2                    | 9EE2 4<br>SBC<br>3 SP1 |                         |

|                                           |     |  |  | 9E63 6<br>COM<br>3 SP1  |  |  |  |                        |      |            | 9ED3 5<br>CPX<br>4 SP2          | CPX<br>3 SP1           | CPHX                    |

|                                           |     |  |  | 9E64 6<br>LSR<br>3 SP1  |  |  |  |                        |      |            | 9ED4 5<br>AND<br>4 SP2          | AND<br>3 SP1           |                         |

|                                           |     |  |  |                         |  |  |  |                        |      |            | 9ED5 5<br>BIT<br>4 SP2          | BIT<br>3 SP1           |                         |

|                                           |     |  |  | 9E66 6<br>ROR<br>3 SP1  |  |  |  |                        |      |            | 9ED6 5<br>LDA<br>4 SP2          | 9EE6 4<br>LDA<br>3 SP1 |                         |

|                                           |     |  |  | 9E67 6<br>ASR<br>3 SP1  |  |  |  |                        |      |            | 9ED7 5<br>STA<br>4 SP2          | STΔ                    |                         |

|                                           |     |  |  | 9E68 6<br>LSL<br>3 SP1  |  |  |  |                        |      |            | 4 SP2<br>9ED8 5<br>EOR<br>4 SP2 | 9EE8 4<br>EOR<br>3 SP1 |                         |

|                                           |     |  |  | 9E69 6<br>ROL<br>3 SP1  |  |  |  |                        |      |            | 9ED9 5<br>ADC<br>4 SP2          | 9EE9 4<br>ADC<br>3 SP1 |                         |

|                                           |     |  |  | 9E6A 6<br>DEC<br>3 SP1  |  |  |  |                        |      |            | ORA<br>4 SP2                    | 9EEA 4<br>ORA<br>3 SP1 |                         |

|                                           |     |  |  | 9E6B 8<br>DBNZ<br>4 SP1 |  |  |  |                        |      |            | 9EDB 5<br>ADD<br>4 SP2          | ADD                    |                         |

|                                           |     |  |  | 9E6C 6<br>INC<br>3 SP1  |  |  |  |                        |      |            |                                 |                        |                         |

|                                           |     |  |  | 9E6D 5<br>TST<br>3 SP1  |  |  |  |                        |      |            |                                 |                        |                         |

|                                           |     |  |  |                         |  |  |  | 9EAE 5<br>LDHX<br>2 IX | LDHX | LDHX       | 9EDE 5<br>LDX<br>4 SP2          | LDX<br>3 SP1           | LDHX<br>3 SP1           |

|                                           |     |  |  | 9E6F 6<br>CLR<br>3 SP1  |  |  |  |                        |      |            | 9EDF 5<br>STX<br>4 SP2          | STX                    | 9EFF 5<br>STHX<br>3 SP1 |

| INH  | Inherent   | REL  | Relative               | SP1  | Stack Pointer, 8-Bit Offset  |

|------|------------|------|------------------------|------|------------------------------|

| IMM  | Immediate  | IX   | Indexed, No Offset     | SP2  | Stack Pointer, 16-Bit Offset |

| DIR  | Direct     | IX1  | Indexed, 8-Bit Offset  | IX+  | Indexed, No Offset with      |

| EXT  | Extended   | IX2  | Indexed, 16-Bit Offset |      | Post Increment               |

| DD   | DIR to DIR | IMD  | IMM to DIR             | IX1+ | Indexed, 1-Byte Offset with  |

| IX+D | IX+ to DIR | DIX+ | DIR to IX+             |      | Post Increment               |

|      |            |      |                        |      |                              |

Note: All Sheet 2 Opcodes are Preceded by the Page 2 Prebyte (9E)

Prebyte (9E) and Opcode in Hexadecimal NEG Number of Bytes HCS08 Cycles Instruction Mnemonic Addressing Mode

# **Chapter 8 Analog-to-Digital Converter (ADC10V1)**

### 8.1 Introduction

The 10-bit analog-to-digital converter (ADC) is a successive approximation ADC designed for operation within an integrated microcontroller system-on-chip.

The ADC module design supports up to 28 separate analog inputs (AD0–AD27). Only four (ADC1P0–ADC1P3) of the possible inputs are implemented on the MC9S08QD4 series MCU. These inputs are selected by the ADCH bits.

Chapter 8 Analog-to-Digital Converter (ADC10V1)

The RTI can be configured to cause a hardware trigger in MCU run, wait, and stop3.

#### 8.1.1.4 Analog Pin Enables

The ADC on MC9S08QD4 contains only one analog pin enable register, APCTL1.

#### 8.1.1.5 Temperature Sensor

To use the on-chip temperature sensor, the user must perform the following:

- Configure ADC for long sample with a maximum of 1 MHz clock

- Convert the bandgap voltage reference channel (AD27)

- By converting the digital value of the bandgap voltage reference channel using the value of V<sub>BG</sub> the user can determine V<sub>DD</sub>. For value of bandgap voltage, see Appendix A.5, "DC Characteristics".

- Convert the temperature sensor channel (AD26)

- By using the calculated value of  $V_{DD}$ , convert the digital value of AD26 into a voltage,  $V_{TEMP}$

Equation 8-1 provides an approximate transfer function of the on-chip temperature sensor for  $V_{DD} = 3.0V$ , Temp = 25°C, using the ADC at  $f_{ADCK} = 1.0$  MHz and configured for long sample.

TempC =

$$25 - ((V_{TEMP} - 1.3894) / (0.0033))$$

Eqn. 8-1

0.0017 is the uncalibrated voltage versus temperature slope in V/°C. Uncalibrated accuracy of the temperature sensor is approximately  $\pm$  12°C, using Equation 8-1.

To improve accuracy the user must calibrate the bandgap voltage reference and temperature sensor.

Calibrating at 25°C will improve accuracy to ± 4.5°C.

Calibration at 3 points, -40°C, 25°C and 105°C will improve accuracy to ± 2.5°C. Once calibration has been completed, the user will need to calculate the slope for both hot and cold. In application code, the user would then calculate the temperature using Equation 8-1 as detailed above and then determine if the temperature is above or below 25°C. Once determined if the temperature is above or below 25°C, the user can recalculate the temperature using the hot or cold slope value obtained during calibration.

#### 8.1.1.6 Low-Power Mode Operation

The ADC is capable of running in stop3 mode but requires LVDSE in SPMSC1 to be set.

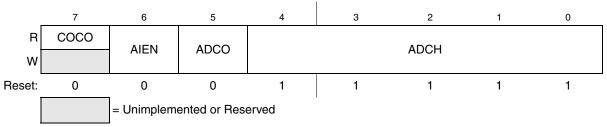

Figure 8-3. Status and Control Register (ADCSC1)

Table 8-3. ADCSC1 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COCO   | Conversion Complete Flag — The COCO flag is a read-only bit which is set each time a conversion is completed when the compare function is disabled (ACFE = 0). When the compare function is enabled (ACFE = 1) the COCO flag is set upon completion of a conversion only if the compare result is true. This bit is cleared whenever ADCSC1 is written or whenever ADCRL is read.  0 Conversion not completed 1 Conversion completed                                                                                                                                                                                                                                                                                                      |

| 6<br>AIEN   | Interrupt Enable — AIEN is used to enable conversion complete interrupts. When COCO becomes set while AIEN is high, an interrupt is asserted.  O Conversion complete interrupt disabled  Conversion complete interrupt enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>ADCO   | Continuous Conversion Enable — ADCO is used to enable continuous conversions.  One conversion following a write to the ADCSC1 when software triggered operation is selected, or one conversion following assertion of ADHWT when hardware triggered operation is selected.  Continuous conversions initiated following a write to ADCSC1 when software triggered operation is selected. Continuous conversions are initiated by an ADHWT event when hardware triggered operation is selected.                                                                                                                                                                                                                                             |

| 4:0<br>ADCH | Input Channel Select — The ADCH bits form a 5-bit field which is used to select one of the input channels. The input channels are detailed in Figure 8-4.  The successive approximation converter subsystem is turned off when the channel select bits are all set to 1. This feature allows for explicit disabling of the ADC and isolation of the input channel from all sources. Terminating continuous conversions this way will prevent an additional, single conversion from being performed. It is not necessary to set the channel select bits to all 1s to place the ADC in a low-power state when continuous conversions are not enabled because the module automatically enters a low-power state when a conversion completes. |

Figure 8-4. Input Channel Select

| ADCH  | Input Select |

|-------|--------------|

| 00000 | AD0          |

| 00001 | AD1          |

| 00010 | AD2          |

| 00011 | AD3          |

| 00100 | AD4          |

| 00101 | AD5          |

| 00110 | AD6          |

| ADCH  | Input Select |  |  |  |

|-------|--------------|--|--|--|

| 10000 | AD16         |  |  |  |

| 10001 | AD17         |  |  |  |

| 10010 | AD18         |  |  |  |

| 10011 | AD19         |  |  |  |

| 10100 | AD20         |  |  |  |

| 10101 | AD21         |  |  |  |

| 10110 | AD22         |  |  |  |

MC9S08QD4 Series MCU Data Sheet, Rev. 6

| Figure 8-4. Input | Channel | Select | (continued) |

|-------------------|---------|--------|-------------|

|-------------------|---------|--------|-------------|

| ADCH  | Input Select |

|-------|--------------|

| 00111 | AD7          |

| 01000 | AD8          |

| 01001 | AD9          |

| 01010 | AD10         |

| 01011 | AD11         |

| 01100 | AD12         |

| 01101 | AD13         |

| 01110 | AD14         |

| 01111 | AD15         |

| ADCH  | Input Select      |

|-------|-------------------|

| 10111 | AD23              |

| 11000 | AD24              |

| 11001 | AD25              |

| 11010 | AD26              |

| 11011 | AD27              |

| 11100 | Reserved          |

| 11101 | V <sub>REFH</sub> |

| 11110 | V <sub>REFL</sub> |

| 11111 | Module disabled   |

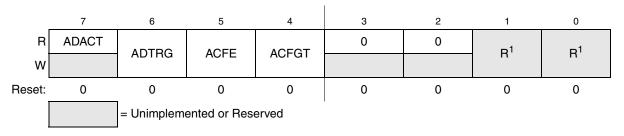

## 8.3.2 Status and Control Register 2 (ADCSC2)

The ADCSC2 register is used to control the compare function, conversion trigger and conversion active of the ADC module.

<sup>&</sup>lt;sup>1</sup> Bits 1 and 0 are reserved bits that must always be written to 0.

Figure 8-5. Status and Control Register 2 (ADCSC2)

**Table 8-4. ADCSC2 Register Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Conversion Active — ADACT indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.  0 Conversion not in progress 1 Conversion in progress                                                                                                                                                                                                                        |

| 6<br>ADTRG | Conversion Trigger Select — ADTRG is used to select the type of trigger to be used for initiating a conversion. Two types of trigger are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.  O Software trigger selected  Hardware trigger selected |

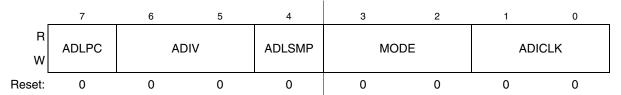

Figure 8-10. Configuration Register (ADCCFG)

**Table 8-5. ADCCFG Register Field Descriptions**

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADLPC    | Low Power Configuration — ADLPC controls the speed and power configuration of the successive approximation converter. This is used to optimize power consumption when higher sample rates are not required.  O High speed configuration  Low power configuration: {FC31}The power is reduced at the expense of maximum clock speed.                                                                                                        |

| 6:5<br>ADIV   | Clock Divide Select — ADIV select the divide ratio used by the ADC to generate the internal clock ADCK.  Table 8-6 shows the available clock configurations.                                                                                                                                                                                                                                                                               |

| 4<br>ADLSMP   | Long Sample Time Configuration — ADLSMP selects between long and short sample time. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption when continuous conversions are enabled if high conversion rates are not required.  O Short sample time  Long sample time |

| 3:2<br>MODE   | Conversion Mode Selection — MODE bits are used to select between 10- or 8-bit operation. See Table 8-7.                                                                                                                                                                                                                                                                                                                                    |

| 1:0<br>ADICLK | Input Clock Select — ADICLK bits select the input clock source to generate the internal clock ADCK. See Table 8-8.                                                                                                                                                                                                                                                                                                                         |

**Table 8-6. Clock Divide Select**

| ADIV | Divide Ratio | Clock Rate      |

|------|--------------|-----------------|

| 00   | 1            | Input clock     |

| 01   | 2            | Input clock ÷ 2 |

| 10   | 4            | Input clock ÷ 4 |

| 11   | 8            | Input clock ÷ 8 |

**Table 8-7. Conversion Modes**

| MODE | Mode Description         |  |  |

|------|--------------------------|--|--|

| 00   | 8-bit conversion (N=8)   |  |  |

| 01   | Reserved                 |  |  |

| 10   | 10-bit conversion (N=10) |  |  |

| 11   | Reserved                 |  |  |

#### MC9S08QD4 Series MCU Data Sheet, Rev. 6

Table 8-11. APCTL3 Register Field Descriptions (continued)

| Field       | Description                                                                                                                                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC17 | ADC Pin Control 17 — ADPC17 is used to control the pin associated with channel AD17.  0 AD17 pin I/O control enabled  1 AD17 pin I/O control disabled |

| 0<br>ADPC16 | ADC Pin Control 16 — ADPC16 is used to control the pin associated with channel AD16.  0 AD16 pin I/O control enabled  1 AD16 pin I/O control disabled |

## 8.4 Functional Description

The ADC module is disabled during reset or when the ADCH bits are all high. The module is idle when a conversion has completed and another conversion has not been initiated. When idle, the module is in its lowest power state.

The ADC can perform an analog-to-digital conversion on any of the software selectable channels. The selected channel voltage is converted by a successive approximation algorithm into an 11-bit digital result. In 8-bit mode, the selected channel voltage is converted by a successive approximation algorithm into a 9-bit digital result.

When the conversion is completed, the result is placed in the data registers (ADCRH and ADCRL).In 10-bit mode, the result is rounded to 10 bits and placed in ADCRH and ADCRL. In 8-bit mode, the result is rounded to 8 bits and placed in ADCRL. The conversion complete flag (COCO) is then set and an interrupt is generated if the conversion complete interrupt has been enabled (AIEN = 1).

The ADC module has the capability of automatically comparing the result of a conversion with the contents of its compare registers. The compare function is enabled by setting the ACFE bit and operates in conjunction with any of the conversion modes and configurations.

#### 8.4.1 Clock Select and Divide Control

One of four clock sources can be selected as the clock source for the ADC module. This clock source is then divided by a configurable value to generate the input clock to the converter (ADCK). The clock is selected from one of the following sources by means of the ADICLK bits.

- The bus clock, which is equal to the frequency at which software is executed. This is the default selection following reset.

- The bus clock divided by 2. For higher bus clock rates, this allows a maximum divide by 16 of the bus clock.

- ALTCLK, as defined for this MCU (See module section introduction).

- The asynchronous clock (ADACK) This clock is generated from a clock source within the ADC module. When selected as the clock source this clock remains active while the MCU is in wait or stop3 mode and allows conversions in these modes for lower noise operation.

Whichever clock is selected, its frequency must fall within the specified frequency range for ADCK. If the available clocks are too slow, the ADC will not perform according to specifications. If the available clocks

MC9S08QD4 Series MCU Data Sheet, Rev. 6

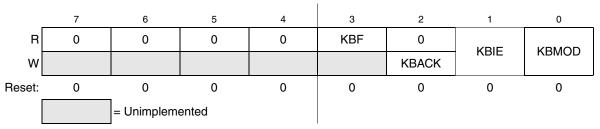

Figure 10-3. KBI Status and Control Register

**Table 10-2. KBISC Register Field Descriptions**

| Field      | Description                                                                                                                                                                                                     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4        | Unused register bits, always read 0.                                                                                                                                                                            |

| 3<br>KBF   | <ul> <li>Keyboard Interrupt Flag — KBF indicates when a keyboard interrupt is detected. Writes have no effect on KBF.</li> <li>No keyboard interrupt detected.</li> <li>Keyboard interrupt detected.</li> </ul> |

| 2<br>KBACK | <b>Keyboard Acknowledge</b> — Writing a 1 to KBACK is part of the flag clearing mechanism. KBACK always reads as 0.                                                                                             |

| 1<br>KBIE  | Keyboard Interrupt Enable — KBIE determines whether a keyboard interrupt is requested.  0 Keyboard interrupt request not enabled.  1 Keyboard interrupt request enabled.                                        |

| 0<br>KBMOD | Keyboard Detection Mode — KBMOD (along with the KBEDG bits) controls the detection mode of the keyboard interrupt pins.0Keyboard detects edges only.  1 Keyboard detects both edges and levels.                 |

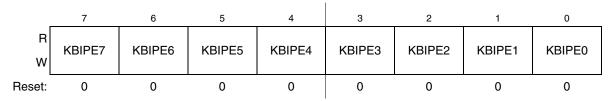

## 10.3.2 KBI Pin Enable Register (KBIPE)

KBIPE contains the pin enable control bits.

Figure 10-4. KBI Pin Enable Register

**Table 10-3. KBIPE Register Field Descriptions**

| Field         | Description                                                                                                                                                                     |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>KBIPEn | Keyboard Pin Enables — Each of the KBIPEn bits enable the corresponding keyboard interrupt pin.  O Pin not enabled as keyboard interrupt.  1 Pin enabled as keyboard interrupt. |

## 10.3.3 KBI Edge Select Register (KBIES)

KBIES contains the edge select control bits.

#### Timer/Pulse-Width Modulator (S08TPMV2)

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

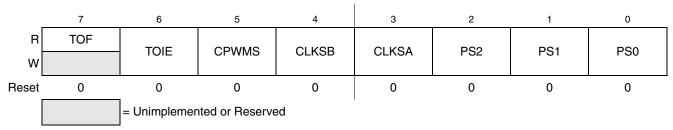

## 11.3.1 Timer Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits that are used to configure the interrupt enable, TPM configuration, clock source, and prescale divisor. These controls relate to all channels within this timer module.

Figure 11-3. Timer Status and Control Register (TPMxSC)

Table 11-1. TPMxSC Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | Timer Overflow Flag — This flag is set when the TPM counter changes to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. When the TPM is configured for CPWM, TOF is set after the counter has reached the value in the modulo register, at the transition to the next lower count value. Clear TOF by reading the TPM status and control register when TOF is set and then writing a 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. Reset clears TOF. Writing a 1 to TOF has no effect.  0 TPM counter has not reached modulo value or overflow 1 TPM counter has overflowed |

| 6<br>TOIE        | Timer Overflow Interrupt Enable — This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals 1. Reset clears TOIE.  0 TOF interrupts inhibited (use software polling)  1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5<br>CPWMS       | Center-Aligned PWM Select — This read/write bit selects CPWM operating mode. Reset clears this bit so the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up-/down-counting mode for CPWM functions. Reset clears CPWMS.  O All TPMx channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register  All TPMx channels operate in center-aligned PWM mode                                                                                                                                                                                              |

| 4:3<br>CLKS[B:A] | Clock Source Select — As shown in Table 11-2, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The external source and the XCLK are synchronized to the bus clock by an on-chip synchronization circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2:0<br>PS[2:0]   | Prescale Divisor Select — This 3-bit field selects one of eight divisors for the TPM clock input as shown in Table 11-3. This prescaler is located after any clock source synchronization or clock source selection, so it affects whatever clock source is selected to drive the TPM system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

MC9S08QD4 Series MCU Data Sheet, Rev. 6

#### Timer/Pulse-Width Modulator (S08TPMV2)

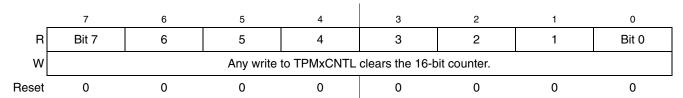

Figure 11-5. Timer Counter Register Low (TPMxCNTL)

When background mode is active, the timer counter and the coherency mechanism are frozen such that the buffer latches remain in the state they were in when the background mode became active even if one or both bytes of the counter are read while background mode is active.

#### 11.3.3 Timer Counter Modulo Registers (TPMxMODH:TPMxMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock (CPWMS = 0) or starts counting down (CPWMS = 1), and the overflow flag (TOF) becomes set. Writing to TPMxMODH or TPMxMODL inhibits TOF and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000, which results in a free-running timer counter (modulo disabled).

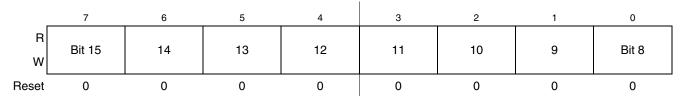

Figure 11-6. Timer Counter Modulo Register High (TPMxMODH)

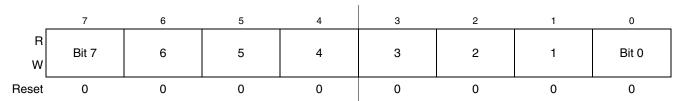

Figure 11-7. Timer Counter Modulo Register Low (TPMxMODL)

It is good practice to wait for an overflow interrupt so both bytes of the modulo register can be written well before a new overflow. An alternative approach is to reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

In output compare or PWM modes, writing to either byte (TPMxCnVH or TPMxCnVL) latches the value into a buffer. When both bytes have been written, they are transferred as a coherent 16-bit value into the timer channel value registers. This latching mechanism may be manually reset by writing to the TPMxCnSC register.

This latching mechanism allows coherent 16-bit writes in either order, which is friendly to various compiler implementations.

## 11.4 Functional Description

All TPM functions are associated with a main 16-bit counter that allows flexible selection of the clock source and prescale divisor. A 16-bit modulo register also is associated with the main 16-bit counter in the TPM. Each TPM channel is optionally associated with an MCU pin and a maskable interrupt function.

The TPM has center-aligned PWM capabilities controlled by the CPWMS control bit in TPMxSC. When CPWMS is set to 1, timer counter TPMxCNT changes to an up-/down-counter and all channels in the associated TPM act as center-aligned PWM channels. When CPWMS = 0, each channel can independently be configured to operate in input capture, output compare, or buffered edge-aligned PWM mode.

The following sections describe the main 16-bit counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend on the operating mode, these topics are covered in the associated mode sections.

#### 11.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, up-counting vs. up-/down-counting, end-of-count overflow, and manual counter reset.

After any MCU reset, CLKSB:CLKSA = 0:0 so no clock source is selected and the TPM is inactive. Normally, CLKSB:CLKSA would be set to 0:1 so the bus clock drives the timer counter. The clock source for the TPM can be selected to be off, the bus clock (BUSCLK), the fixed system clock (XCLK), or an external input. The maximum frequency allowed for the external clock option is one-fourth the bus rate. Refer to Section 11.3.1, "Timer Status and Control Register (TPMxSC)" and Table 11-2 for more information about clock source selection.

When the microcontroller is in active background mode, the TPM temporarily suspends all counting until the microcontroller returns to normal user operating mode. During stop mode, all TPM clocks are stopped; therefore, the TPM is effectively disabled until clocks resume. During wait mode, the TPM continues to operate normally.

The main 16-bit counter has two counting modes. When center-aligned PWM is selected (CPWMS = 1), the counter operates in up-/down-counting mode. Otherwise, the counter operates as a simple up-counter. As an up-counter, the main 16-bit counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

#### **Appendix A Electrical Characteristics**

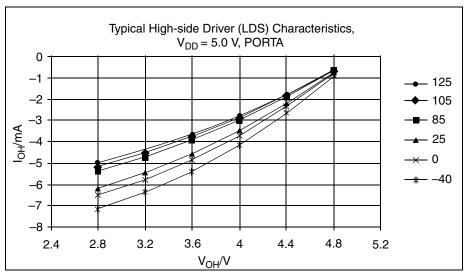

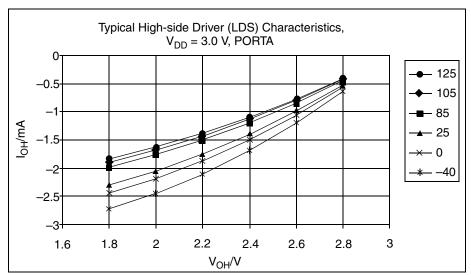

Figure A-5. Typical High-Side Driver (Source) Characteristics Low Drive (PTxDSn = 0),  $V_{DD}$  = 5.0 V,  $V_{OH}$  vs.  $I_{OH}$

Figure A-6. Typical High-Side Driver (Source) Characteristics Low Drive (PTxDSn = 0),  $V_{DD}$  = 3.0 V,  $V_{OH}$  vs.  $I_{OH}$

|                    |             |                 | -          |                  | -    |      |                                      |      |

|--------------------|-------------|-----------------|------------|------------------|------|------|--------------------------------------|------|

| Characteristic     | Conditions  | Symb            | Min        | Typ <sup>1</sup> | Max  | Unit | Comment                              |      |

| Zero-Scale Error   | 10 bit mode | F               | 0          | ±1.5             | ±3.1 | LSB  | V <sub>ADIN</sub> = V <sub>SSA</sub> |      |

|                    | 8 bit mode  | E <sub>ZS</sub> | 0          | ±0.5             | ±0.7 |      |                                      |      |

| Full-Scale Error   | 10 bit mode | E <sub>FS</sub> | <b>E</b> . | 0                | ±1.0 | ±1.5 | LSB                                  | V -V |

|                    | 8 bit mode  |                 | 0          | ±0.5             | ±0.5 | LOD  | $V_{ADIN} = V_{DDA}$                 |      |

| Quantization Error | 10 bit mode | EQ              | _          | _                | ±0.5 | LSB  | 8 bit mode is not truncated          |      |

**Table A-10. ADC Characteristics (continued)**

## A.10 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the flash memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see the Memory section.

| Characteristic                                                                                  | Symbol                  | Min    | Typical | Max               | Unit              |

|-------------------------------------------------------------------------------------------------|-------------------------|--------|---------|-------------------|-------------------|

| Supply voltage for program/erase –40°C to 125°C                                                 | V <sub>prog/erase</sub> | 2.7    |         | 5.5               | V                 |

| Supply voltage for read operation                                                               | V <sub>Read</sub>       | 2.7    |         | 5.5               | V                 |

| Internal FCLK frequency <sup>1</sup>                                                            | f <sub>FCLK</sub>       | 150    |         | 200               | kHz               |

| Internal FCLK period (1/FCLK)                                                                   | t <sub>Fcyc</sub>       | 5      |         | 6.67              | μS                |

| Byte program time (random location) <sup>(2)</sup>                                              | t <sub>prog</sub>       |        | 9       |                   | t <sub>Fcyc</sub> |

| Byte program time (burst mode) <sup>(2)</sup>                                                   | t <sub>Burst</sub>      | 4      |         | t <sub>Fcyc</sub> |                   |

| Page erase time <sup>2</sup>                                                                    | t <sub>Page</sub>       | 4000   |         | t <sub>Fcyc</sub> |                   |

| Mass erase time <sup>(2)</sup> t <sub>Mass</sub>                                                |                         | 20,000 |         |                   | t <sub>Fcyc</sub> |

| Program/erase endurance <sup>3</sup> $T_L$ to $T_H = -40^{\circ}C$ to + 125°C $T = 25^{\circ}C$ |                         | 10,000 | 100,000 |                   | cycles            |

| Data retention <sup>4</sup>                                                                     | t <sub>D_ret</sub>      | 15     | 100     | _                 | years             |

**Table A-11. Flash Characteristics**

Typical values assume V<sub>DDAD</sub> = 5.0 V, Temp = 25°C, f<sub>ADCK</sub>=1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>&</sup>lt;sup>2</sup> At 4 MHz, for maximum frequency, use proportionally lower source impedance.

The frequency of this clock is controlled by a software setting.

These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

Typical endurance for flash was evaluated for this product family on the 9S12Dx64. For additional information on how Freescale defines typical endurance, please refer to Engineering Bulletin EB619/D, Typical Endurance for Nonvolatile Memory.

Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale defines typical data retention, please refer to Engineering Bulletin EB618/D, Typical Data Retention for Nonvolatile Memory.