Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | S08                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | -                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 4                                                                    |

| Program Memory Size        | 4KB (4K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 4x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                        |

| Supplier Device Package    | 8-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08qd4msc |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **MC9S08QD4 Series Features**

### 8-Bit HCS08 Central Processor Unit (CPU)

- 16 MHz HCS08 CPU (central processor unit)

- HC08 instruction set with added BGND instruction

- Background debugging system

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints in on-chip debug module)

- Support for up to 32 interrupt/reset sources

#### Memory

- Flash read/program/erase over full operating voltage and temperature

- Flash size:

- MC9S08QD4/S9S08QD4: 4096 bytes

- MC9S08QD2/S9S08QD2: 2048 bytes

- RAM size

- MC9S08QD4/S9S08QD4: 256 bytes

- MC9S08QD2/S9S08QD2: 128 bytes

#### **Power-Saving Modes**

• Wait plus three stops

#### **Clock Source Options**

• ICS — Internal clock source module (ICS) containing a frequency-locked-loop (FLL) controlled by internal. Precision trimming of internal reference allows 0.2% resolution and 2% deviation over temperature and voltage.

#### **System Protection**

- Watchdog computer operating properly (COP) reset with option to run from dedicated 32 kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt

- Illegal opcode detection with reset

- Illegal address detection with reset

Flash block protect

#### Peripherals

- ADC 4-channel, 10-bit analog-to-digital converter with automatic compare function, asynchronous clock source, temperature sensor and internal bandgap reference channel. ADC is hardware triggerable using the RTI counter.

- **TIM1** 2-channel timer/pulse-width modulator; each channel can be used for input capture, output compare, buffered edge-aligned PWM, or buffered center-aligned PWM

- **TIM2** 1-channel timer/pulse-width modulator; each channel can be used for input capture, output compare, buffered edge-aligned PWM, or buffered center-aligned PWM

- **KBI** 4-pin keyboard interrupt module with software selectable polarity on edge or edge/level modes

### Input/Output

- Four General-purpose input/output (I/O) pins, one input-only pin and one output-only pin. Outputs 10 mA each, 60 mA maximum for package.

- Software selectable pullups on ports when used as input

- Software selectable slew rate control and drive strength on ports when used as output

- Internal pullup on RESET and IRQ pin to reduce customer system cost

#### **Development Support**

• Single-wire background debug interface

#### **Package Options**

- 8-pin SOIC package

- 8-pin PDIP (Only for MC9S08QD4 and MC9S08QD2)

- All package options are RoHS compliant

|     | 4.5.2    | Program and Erase Times                      | 37 |

|-----|----------|----------------------------------------------|----|

|     | 4.5.3    | Program and Erase Command Execution          | 38 |

|     | 4.5.4    | Burst Program Execution                      | 39 |

|     | 4.5.5    | Access Errors                                | 41 |

|     | 4.5.6    | Flash Block Protection                       | 42 |

|     | 4.5.7    | Vector Redirection                           | 43 |

| 4.6 | Security | /                                            | 43 |

| 4.7 | Flash R  | egisters and Control Bits                    | 44 |

|     | 4.7.1    | Flash Clock Divider Register (FCDIV)         | 44 |

|     | 4.7.2    | Flash Options Register (FOPT and NVOPT)      | 46 |

|     | 4.7.3    | Flash Configuration Register (FCNFG)         | 47 |

|     | 4.7.4    | Flash Protection Register (FPROT and NVPROT) | 47 |

|     | 4.7.5    | Flash Status Register (FSTAT)                | 48 |

|     |          | Flash Command Register (FCMD)                |    |

|     |          |                                              |    |

# Chapter 5 Resets, Interrupts, and General System Control

| 5.1 | Introdu  | ction                                                           | 51 |

|-----|----------|-----------------------------------------------------------------|----|

| 5.2 | Feature  | S                                                               | 51 |

| 5.3 | MCU R    | eset                                                            | 51 |

| 5.4 | Comput   | ter Operating Properly (COP) Watchdog                           |    |

| 5.5 | Interrup | ots                                                             | 53 |

|     | 5.5.1    | Interrupt Stack Frame                                           |    |

|     | 5.5.2    | External Interrupt Request (IRQ) Pin                            |    |

|     | 5.5.3    | Interrupt Vectors, Sources, and Local Masks                     |    |

| 5.6 | Low-Vo   | bltage Detect (LVD) System                                      |    |

|     | 5.6.1    | Power-On Reset Operation                                        | 57 |

|     | 5.6.2    | LVD Reset Operation                                             |    |

|     | 5.6.3    | LVD Interrupt Operation                                         |    |

|     | 5.6.4    | Low-Voltage Warning (LVW)                                       |    |

| 5.7 |          | me Interrupt (RTI)                                              |    |

| 5.8 | Reset, I | nterrupt, and System Control Registers and Control Bits         |    |

|     | 5.8.1    | Interrupt Pin Request Status and Control Register (IRQSC)       |    |

|     | 5.8.2    | System Reset Status Register (SRS)                              |    |

|     | 5.8.3    | System Background Debug Force Reset Register (SBDFR)            |    |

|     | 5.8.4    | System Options Register 1 (SOPT1)                               |    |

|     | 5.8.5    | System Options Register 2 (SOPT2)                               |    |

|     | 5.8.6    | System Device Identification Register (SDIDH, SDIDL)            |    |

|     | 5.8.7    | System Real-Time Interrupt Status and Control Register (SRTISC) |    |

|     | 5.8.8    | System Power Management Status and Control 1 Register (SPMSC1)  |    |

|     | 5.8.9    | System Power Management Status and Control 2 Register (SPMSC2)  | 65 |

|     |          |                                                                 |    |

# Chapter 6 Parallel Input/Output Control

| 6.1 | Port Data and Data Direction |  |

|-----|------------------------------|--|

|     |                              |  |

| 9.5 | Module | Initialization                     |  |

|-----|--------|------------------------------------|--|

|     |        | ICS Module Initialization Sequence |  |

# Chapter 10 Keyboard Interrupt (S08KBIV2)

| 10.1 | Introduction                                   |     |

|------|------------------------------------------------|-----|

|      | 10.1.1 Features                                |     |

|      | 10.1.2 Modes of Operation                      |     |

|      | 10.1.3 Block Diagram                           |     |

| 10.2 | External Signal Description                    |     |

| 10.3 | Register Definition                            |     |

|      | 10.3.1 KBI Status and Control Register (KBISC) |     |

|      | 10.3.2 KBI Pin Enable Register (KBIPE)         |     |

|      | 10.3.3 KBI Edge Select Register (KBIES)        |     |

| 10.4 | Functional Description                         |     |

|      | 10.4.1 Edge Only Sensitivity                   |     |

|      | 10.4.2 Edge and Level Sensitivity              |     |

|      | 10.4.3 KBI Pullup/Pulldown Resistors           | 141 |

|      | 10.4.4 KBI Initialization                      |     |

# Chapter 11 Timer/Pulse-Width Modulator (S08TPMV2)

| 11.1 | Introduc | tion                                                   | 143 |

|------|----------|--------------------------------------------------------|-----|

|      | 11.1.1   | TPM2 Configuration Information                         | 143 |

|      | 11.1.2   | TCLK1 and TCLK2 Configuration Information              | 143 |

|      | 11.1.3   | Features                                               | 145 |

|      | 11.1.4   | Block Diagram                                          | 145 |

| 11.2 | External | Signal Description                                     | 147 |

|      |          | External TPM Clock Sources                             |     |

|      |          | TPMxCHn — TPMx Channel n I/O Pins                      |     |

| 11.3 |          | Definition                                             |     |

|      | 11.3.1   | Timer Status and Control Register (TPMxSC)             | 148 |

|      | 11.3.2   | Timer Counter Registers (TPMxCNTH:TPMxCNTL)            | 149 |

|      |          | Timer Counter Modulo Registers (TPMxMODH:TPMxMODL)     |     |

|      | 11.3.4   | Timer Channel n Status and Control Register (TPMxCnSC) | 151 |

|      | 11.3.5   | Timer Channel Value Registers (TPMxCnVH:TPMxCnVL)      | 152 |

| 11.4 | Function | nal Description                                        | 153 |

|      |          | Counter                                                |     |

|      | 11.4.2   | Channel Mode Selection                                 | 154 |

|      | 11.4.3   | Center-Aligned PWM Mode                                | 156 |

| 11.5 | TPM In   | terrupts                                               | 157 |

|      | 11.5.1   | Clearing Timer Interrupt Flags                         | 157 |

|      | 11.5.2   | Timer Overflow Interrupt Description                   | 157 |

|      | 11.5.3   | Channel Event Interrupt Description                    | 158 |

|      | 11.5.4   | PWM End-of-Duty-Cycle Events                           | 158 |

|      |          |                                                        |     |

# Chapter 12 Development Support

| 12.1 | Introduction                                                | 159 |

|------|-------------------------------------------------------------|-----|

|      | 12.1.1 Forcing Active Background                            | 159 |

|      | 12.1.2 Module Configuration                                 | 159 |

|      | 12.1.3 Features                                             |     |

| 12.2 | Background Debug Controller (BDC)                           | 160 |

|      | 12.2.1 BKGD Pin Description                                 | 161 |

|      | 12.2.2 Communication Details                                | 161 |

|      | 12.2.3 BDC Commands                                         | 164 |

|      | 12.2.4 BDC Hardware Breakpoint                              |     |

| 12.3 | Register Definition                                         |     |

|      | 12.3.1 BDC Registers and Control Bits                       |     |

|      | 12.3.2 System Background Debug Force Reset Register (SBDFR) | 170 |

### Appendix A Electrical Characteristics

| A.1 Introduction                          |     |

|-------------------------------------------|-----|

| A.2 Absolute Maximum Ratings              |     |

| A.3 Thermal Characteristics               | 174 |

| A.4 ESD Protection and Latch-Up Immunity  | 175 |

| A.5 DC Characteristics                    |     |

| A.6 Supply Current Characteristics        |     |

| A.7 Internal Clock Source Characteristics |     |

| A.8 AC Characteristics                    |     |

| A.8.1 Control Timing                      |     |

| A.8.2 Timer/PWM (TPM) Module Timing       |     |

| A.9 ADC Characteristics                   |     |

| A.10 Flash Specifications                 |     |

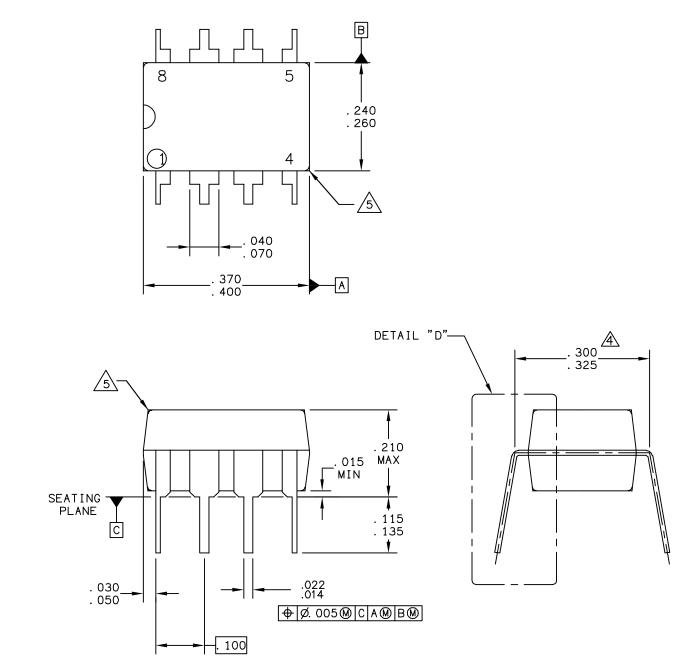

### Appendix B Ordering Information and Mechanical Drawings

| B.1 Ordering Information | 191                           |  |

|--------------------------|-------------------------------|--|

|                          | B.1.1 Device Numbering Scheme |  |

| B.2                      | Mechanical Drawings           |  |

### 2.2.2 Oscillator

Out of reset the MCU uses an internally generated clock provided by the internal clock source (ICS) module. The internal frequency is nominally 16 MHz and the default ICS settings will provide for a 4 MHz bus out of reset. For more information on the ICS, see the Internal Clock Source chapter.

### 2.2.3 Reset (Input Only)

After a power-on reset (POR) into user mode, the PTA5/TPM2CH0I/IRQ/RESET pin defaults to a general-purpose input port pin, PTA5. Setting RSTPE in SOPT1 configures the pin to be the RESET input pin. Once configured as RESET, the pin will remain RESET until the next POR. The RESET pin can be used to reset the MCU from an external source when the pin is driven low. When enabled as the RESET pin (RSTPE = 1), an internal pullup device is automatically enabled.

After a POR into active background mode, the PTA5/TPM2CH0I/IRQ/ $\overline{RESET}$  pin defaults to the  $\overline{RESET}$  pin.

When TPM2 is configured for input capture, the pin will be the input capture pin TPM2CH0I.

### NOTE

This pin does not contain a clamp diode to  $V_{\mbox{\scriptsize DD}}$  and must not be driven above  $V_{\mbox{\scriptsize DD}}.$

The voltage measured on the internally pulled up  $\overline{\text{RESET}}$  pin may be as low as  $V_{DD} - 0.7$  V. The internal gates connected to this pin are pulled to  $V_{DD}$ .

### 2.2.4 Background / Mode Select (BKGD/MS)

During a power-on-reset (POR) or background debug force reset (see Section 5.8.3, "System Background Debug Force Reset Register (SBDFR)" for more information), the PTA4/TPM2CH0O/BKGD/MS pin functions as a mode select pin. Immediately after any reset, the pin functions as the background pin and can be used for background debug communication. When enabled as the BKGD/MS pin (BKGDPE = 1), an internal pullup device is automatically enabled.

The background debug communication function is enabled when BKGDPE in SOPT1 is set. BKGDPE is set following any reset of the MCU and must be cleared to use the PTA4/TPM2CH0O/BKGD/MS pins alternative pin functions.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of the internal reset after a POR or force BDC reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during a POR or immediately after issuing a background debug force reset, which will force the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the maximum bus clock rate, so there must never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

### 2.2.5.2 Output Slew Rate Control

Slew rate control can be enabled for each port pin by setting the corresponding bit in one of the slew rate control registers (PTxSEn). When enabled, slew control limits the rate at which an output can transition in order to reduce EMC emissions. Slew rate control has no effect on pins that are configured as inputs.

### 2.2.5.3 Output Drive Strength Select

An output pin can be selected to have high output drive strength by setting the corresponding bit in one of the drive strength select registers (PTxDSn). When high drive is selected, a pin is capable of sourcing and sinking greater current. Even though every I/O pin can be selected as high drive, the user must ensure that the total current source and sink limits for the chip are not exceeded. Drive strength selection is intended to affect the DC behavior of I/O pins. However, the AC behavior is also affected. High drive allows a pin to drive a greater load with the same switching speed as a low drive enabled pin into a smaller load. Because of this, the EMC emissions may be affected by enabling pins as high drive.

| Lowe                                                      | st <- Pin Functi                                             | on Priority -> H                                       | Reference <sup>1</sup>                                                                            |                                                                                                                                                                                           |  |

|-----------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Port Pins                                                 | Alternative<br>Function                                      |                                                        |                                                                                                   |                                                                                                                                                                                           |  |

| PTA0<br>PTA1<br>PTA2<br>PTA3<br>PTA4<br>PTA5 <sup>2</sup> | KBI1P0<br>KBI1P1<br>KBI1P2<br>KBI1P3<br>TPM2CH00<br>TPM2CH01 | TPM1CH0<br>TPM1CH1<br>TCLK1<br>TCLK2<br>BKGD/MS<br>IRQ | ADC1P0 <sup>3</sup><br>ADC1P1 <sup>3</sup><br>ADC1P2 <sup>3</sup><br>ADC1P3 <sup>3</sup><br>RESET | KBI1, ADC1, and TPM1 Chapters<br>KBI1, ADC1, and TPM1 Chapters<br>KBI1, ADC1, and TPM1 Chapters<br>KBI1, ADC1, and TPM2 Chapters<br>TPM2 Chapters<br>IRQ <sup>4</sup> , and TPM2 Chapters |  |

Table 2-1. Pin Sharing Priority

<sup>1</sup> See the module section listed for information on modules that share these pins.

<sup>2</sup> Pin does not contain a clamp diode to V<sub>DD</sub> and must not be driven above V<sub>DD</sub>. The voltage measured on this pin when internal pullup is enabled may be as low as V<sub>DD</sub> – 0.7 V. The internal gates connected to this pin are pulled to V<sub>DD</sub>.

<sup>3</sup> If both of these analog modules are enabled both will have access to the pin.

<sup>4</sup> See Section 5.8, "Reset, Interrupt, and System Control Registers and Control Bits," for information on configuring the IRQ module.

# Chapter 3 Modes of Operation

# 3.1 Introduction

The operating modes of the MC9S08QD4 series are described in this chapter. Entry into each mode, exit from each mode, and functionality while in each of the modes are described.

### 3.2 Features

- Active background mode for code development

- Wait mode:

- CPU shuts down to conserve power

- System clocks running

- Full voltage regulation maintained

- Stop modes:

- CPU and bus clocks stopped

- Stop2 Partial power down of internal circuits, RAM contents retained

- Stop3 All internal circuits powered for fast recovery

### 3.3 Run Mode

This is the normal operating mode for the MC9S08QD4 series. This mode is selected when the BKGD/MS pin is high at the rising edge of reset. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at 0xFFFE:0xFFFF after reset.

# 3.4 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in the HCS08 core. The BDC provides the means for analyzing MCU operation during software development.

Active background mode is entered in any of five ways:

- When the BKGD/MS pin is low at the rising edge of reset

- When a BACKGROUND command is received through the BKGD pin

- When a BGND instruction is executed

- When encountering a BDC breakpoint

### 4.3 Register Addresses and Bit Assignments

The registers in the MC9S08QD4 series are divided into these groups:

- Direct-page registers are located in the first 96 locations in the memory map; these are accessible with efficient direct addressing mode instructions.

- High-page registers are used much less often, so they are located above 0x1800 in the memory map. This leaves more room in the direct page for more frequently used registers and RAM.

- The nonvolatile register area consists of a block of 16 locations in flash memory at 0xFFB0–0xFFBF. Nonvolatile register locations include:

- NVPROT and NVOPT are loaded into working registers at reset

- An 8-byte backdoor comparison key that optionally allows a user to gain controlled access to secure memory

Because the nonvolatile register locations are flash memory, they must be erased and programmed like other flash memory locations.

Direct-page registers can be accessed with efficient direct addressing mode instructions. Bit manipulation instructions can be used to access any bit in any direct-page register. Table 4-2 is a summary of all user-accessible direct-page registers and control bits.

The direct page registers in Table 4-2 can use the more efficient direct addressing mode that requires only the lower byte of the address. Because of this, the lower byte of the address in column one is shown in bold text. In Table 4-3 and Table 4-4, the whole address in column one is shown in bold. In Table 4-2, Table 4-3, and Table 4-4, the register names in column two are shown in bold to set them apart from the bit names to the right. Cells that are not associated with named bits are shaded. A shaded cell with a 0 indicates this unused bit always reads as a 0. Shaded cells with dashes indicate unused or reserved bit locations that could read as 1s or 0s.

| Address                            | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|------------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x00 <b>00</b>                     | PTAD          | 0      | 0      | PTAD5  | PTAD4  | PTAD3  | PTAD2  | PTAD1  | PTAD0  |

| 0x00 <b>01</b>                     | PTADD         | 0      | 0      | PTADD5 | PTADD4 | PTADD3 | PTADD2 | PTADD1 | PTADD0 |

| 0x00 <b>02</b> –<br>0x00 <b>0B</b> | Reserved      | _      | _      |        | _      |        |        |        | _      |

| 0x00 <b>0C</b>                     | KBISC         | 0      | 0      | 0      | 0      | KBF    | KBACK  | KBIE   | KBIMOD |

| 0x00 <b>0D</b>                     | KBIPE         | KBIPE7 | KBIPE6 | KBIPE5 | KBIPE4 | KBIPE3 | KBIPE2 | KBIPE1 | KBIPE0 |

| 0x00 <b>0E</b>                     | KBIES         | KBEDG7 | KBEDG6 | KBEDG5 | KBEDG4 | KBEDG3 | KBEDG2 | KBEDG1 | KBEDG0 |

| 0x00 <b>0F</b>                     | IRQSC         | 0      | IRQPDD | IRQEDG | IRQPE  | IRQF   | IRQACK | IRQIE  | IRQMOD |

| 0x00 <b>10</b>                     | ADCSC1        | 0000   | AIEN   | ADCO   | ADCH   |        |        |        |        |

| 0x00 <b>11</b>                     | ADCSC2        | ADACT  | ADTRG  | ACFE   | ACFGT  | —      | —      | —      | —      |

| 0x00 <b>12</b>                     | ADCRH         | 0      | 0      | 0      | 0      | 0      | 0      | ADR9   | ADR8   |

| 0x00 <b>13</b>                     | ADCRL         | ADR7   | ADR6   | ADR5   | ADR4   | ADR3   | ADR2   | ADR1   | ADR0   |

| 0x00 <b>14</b>                     | ADCCVH        | 0      | 0      | 0      | 0      | 0      | 0      | ADCV9  | ADCV8  |

| 0x00 <b>15</b>                     | ADCCVL        | ADCV7  | ADCV6  | ADCV5  | ADCV4  | ADCV3  | ADCV2  | ADCV1  | ADCV0  |

| 0x00 <b>16</b>                     | ADCCFG        | ADLPC  | AD     | DIV    | ADLSMP | MC     | DE     | ADI    | CLK    |

#### Table 4-2. Direct-Page Register Summary

### 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it was before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

If an event occurs in an enabled interrupt source, an associated read-only status flag will become set. The CPU will not respond until and unless the local interrupt enable is a 1 to enable the interrupt. The I bit in the CCR is 0 to allow interrupts. The global interrupt mask (I bit) in the CCR is initially set after reset which masks (prevents) all maskable interrupt sources. The user program initializes the stack pointer and performs other system setup before clearing the I bit to allow the CPU to respond to interrupts.

When the CPU receives a qualified interrupt request, it completes the current instruction before responding to the interrupt. The interrupt sequence obeys the same cycle-by-cycle sequence as the SWI instruction and consists of:

- Saving the CPU registers on the stack

- Setting the I bit in the CCR to mask further interrupts

- Fetching the interrupt vector for the highest-priority interrupt that is currently pending

- Filling the instruction queue with the first three bytes of program information starting from the address fetched from the interrupt vector locations

While the CPU is responding to the interrupt, the I bit is automatically set to avoid the possibility of another interrupt interrupting the ISR itself (this is called nesting of interrupts). Normally, the I bit is restored to 0 when the CCR is restored from the value stacked on entry to the ISR. In rare cases, the I bit can be cleared inside an ISR (after clearing the status flag that generated the interrupt) so that other interrupts can be serviced without waiting for the first service routine to finish. This practice is not recommended for anyone other than the most experienced programmers because it can lead to subtle program errors that are difficult to debug.

The interrupt service routine ends with a return-from-interrupt (RTI) instruction which restores the CCR, A, X, and PC registers to their pre-interrupt values by reading the previously saved information off the stack.

#### NOTE

For compatibility with M68HC08 devices, the H register is not automatically saved and restored. It is good programming practice to push H onto the stack at the start of the interrupt service routine (ISR) and restore it immediately before the RTI that is used to return from the ISR.

When two or more interrupts are pending when the I bit is cleared, the highest priority source is serviced first (see Table 5-2).

| Source<br>Form                                                                                                  | Operation                                                                                                | Address<br>Mode                                                                                          | Object Code                                                                      | es                              | Cyc-by-Cyc<br>Details                                                         |     | Affect<br>n CCR |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------|-----|-----------------|

|                                                                                                                 |                                                                                                          | Add<br>Mod                                                                                               |                                                                                  | Cycles                          |                                                                               | VH  | INZC            |

| BCLR <i>n,opr8a</i>                                                                                             | Clear Bit n in Memory<br>(Mn ← 0)                                                                        | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11 dd<br>13 dd<br>15 dd<br>17 dd<br>19 dd<br>1B dd<br>1D dd<br>1F dd             | 55555555                        | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp |     |                 |

| BCS rel                                                                                                         | Branch if Carry Bit Set (if C = 1)<br>(Same as BLO)                                                      | REL                                                                                                      | 25 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BEQ <i>rel</i>                                                                                                  | Branch if Equal (if Z = 1)                                                                               | REL                                                                                                      | 27 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BGE rel                                                                                                         | Branch if Greater Than or Equal To (if $N \oplus V = 0$ ) (Signed)                                       | REL                                                                                                      | 90 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BGND                                                                                                            | Enter active background if ENBDM=1<br>Waits for and processes BDM commands<br>until GO, TRACE1, or TAGGO | INH                                                                                                      | 82                                                                               | 5+                              | fpppp                                                                         |     |                 |

| BGT <i>rel</i>                                                                                                  | Branch if Greater Than (if Z I (N $\oplus$ V) = 0) (Signed)                                              | REL                                                                                                      | 92 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BHCC rel                                                                                                        | Branch if Half Carry Bit Clear (if H = 0)                                                                | REL                                                                                                      | 28 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BHCS rel                                                                                                        | Branch if Half Carry Bit Set (if H = 1)                                                                  | REL                                                                                                      | 29 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BHI <i>rel</i>                                                                                                  | Branch if Higher (if C   Z = 0)                                                                          | REL                                                                                                      | 22 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BHS rel                                                                                                         | Branch if Higher or Same (if C = 0)<br>(Same as BCC)                                                     | REL                                                                                                      | 24 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BIH <i>rel</i>                                                                                                  | Branch if IRQ Pin High (if IRQ pin = 1)                                                                  | REL                                                                                                      | 2F rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BIL <i>rel</i>                                                                                                  | Branch if IRQ Pin Low (if IRQ pin = 0)                                                                   | REL                                                                                                      | 2E rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BIT #opr8i<br>BIT opr8a<br>BIT opr16a<br>BIT oprx16,X<br>BIT oprx8,X<br>BIT ,X<br>BIT oprx16,SP<br>BIT oprx8,SP | Bit Test<br>(A) & (M)<br>(CCR Updated but Operands Not Changed)                                          | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                                      | A5 ii<br>B5 dd<br>C5 hh ll<br>D5 ee ff<br>E5 ff<br>F5<br>9E D5 ee ff<br>9E E5 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp                      | 0 – | - \$ \$ -       |

| BLE rel                                                                                                         | Branch if Less Than or Equal To (if Z   (N $\oplus$ V) = 1) (Signed)                                     | REL                                                                                                      | 93 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BLO <i>rel</i>                                                                                                  | Branch if Lower (if $C = 1$ ) (Same as BCS)                                                              | REL                                                                                                      | 25 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BLS <i>rel</i>                                                                                                  | Branch if Lower or Same (if $C \mid Z = 1$ )                                                             | REL                                                                                                      | 23 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BLT <i>rel</i>                                                                                                  | Branch if Less Than (if $N \oplus V = 1$ ) (Signed)                                                      | REL                                                                                                      | 91 rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BMC rel                                                                                                         | Branch if Interrupt Mask Clear (if I = 0)                                                                | REL                                                                                                      | 2C rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BMI <i>rel</i>                                                                                                  | Branch if Minus (if N = 1)                                                                               | REL                                                                                                      | 2B rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BMS <i>rel</i>                                                                                                  | Branch if Interrupt Mask Set (if I = 1)                                                                  | REL                                                                                                      | 2D rr                                                                            | 3                               | ppp                                                                           |     |                 |

| BNE <i>rel</i>                                                                                                  | Branch if Not Equal (if Z = 0)                                                                           | REL                                                                                                      | 26 rr                                                                            | 3                               | qqq                                                                           |     |                 |

| BPL <i>rel</i>                                                                                                  | Branch if Plus (if $N = 0$ )                                                                             | REL                                                                                                      | 2A rr                                                                            | 3                               | qqq                                                                           |     |                 |

| Table 7-2 | Instruction | Set | Summarv | (Sheet 2 of 9) |

|-----------|-------------|-----|---------|----------------|

|           |             | Jei | Summary |                |

#### Analog-to-Digital Converter (S08ADC10V1)

- 2. Update status and control register 2 (ADCSC2) to select the conversion trigger (hardware or software) and compare function options, if enabled.

- 3. Update status and control register 1 (ADCSC1) to select whether conversions will be continuous or completed only once, and to enable or disable conversion complete interrupts. The input channel on which conversions will be performed is also selected here.

### 8.5.1.2 Pseudo — Code Example

In this example, the ADC module will be set up with interrupts enabled to perform a single 10-bit conversion at low power with a long sample time on input channel 1, where the internal ADCK clock will be derived from the bus clock divided by 1.

#### ADCCFG = 0x98 (%10011000)

| Bit 7   | ADLPC  | 1  | Configures for low power (lowers maximum clock speed) |

|---------|--------|----|-------------------------------------------------------|

| Bit 6:5 | ADIV   | 00 | Sets the ADCK to the input clock $\div$ 1             |

| Bit 4   | ADLSMP | 1  | Configures for long sample time                       |

| Bit 3:2 | MODE   | 10 | Sets mode at 10-bit conversions                       |

| Bit 1:0 | ADICLK | 00 | Selects bus clock as input clock source               |

|         |        |    |                                                       |

#### ADCSC2 = 0x00 (%00000000)

| Bit 7   | ADACT | 0  | Flag indicates if a conversion is in progress            |

|---------|-------|----|----------------------------------------------------------|

| Bit 6   | ADTRG | 0  | Software trigger selected                                |

| Bit 5   | ACFE  | 0  | Compare function disabled                                |

| Bit 4   | ACFGT | 0  | Not used in this example                                 |

| Bit 3:2 |       | 00 | Unimplemented or reserved, always reads zero             |

| Bit 1:0 |       | 00 | Reserved for Freescale's internal use; always write zero |

|         |       |    |                                                          |

#### ADCSC1 = 0x41 (%01000001)

| Bit 7   | COCO | 0     | Read-only flag which is set when a conversion completes |

|---------|------|-------|---------------------------------------------------------|

| Bit 6   | AIEN | 1     | Conversion complete interrupt enabled                   |

| Bit 5   | ADCO | 0     | One conversion only (continuous conversions disabled)   |

| Bit 4:0 | ADCH | 00001 | Input channel 1 selected as ADC input channel           |

#### ADCRH/L = 0xxx

Holds results of conversion. Read high byte (ADCRH) before low byte (ADCRL) so that conversion data cannot be overwritten with data from the next conversion.

#### ADCCVH/L = 0xxx

Holds compare value when compare function enabled

#### APCTL1=0x02

AD1 pin I/O control disabled. All other AD pins remain general purpose I/O pins

#### APCTL2=0x00

All other AD pins remain general purpose I/O pins

#### Analog-to-Digital Converter (S08ADC10V1)

In cases where separate power supplies are used for analog and digital power, the ground connection between these supplies must be at the  $V_{SSAD}$  pin. This must be the only ground connection between these supplies if possible. The  $V_{SSAD}$  pin makes a good single point ground location.

### 8.6.1.2 Analog Reference Pins

In addition to the analog supplies, the ADC module has connections for two reference voltage inputs. The high reference is  $V_{REFH}$ , which may be shared on the same pin as  $V_{DDAD}$  on some devices. The low reference is  $V_{REFL}$ , which may be shared on the same pin as  $V_{SSAD}$  on some devices.

When available on a separate pin,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ). When available on a separate pin,  $V_{REFL}$  must be connected to the same voltage potential as  $V_{SSAD}$ . Both  $V_{REFH}$  and  $V_{REFL}$  must be routed carefully for maximum noise immunity and bypass capacitors placed as near as possible to the package.

AC current in the form of current spikes required to supply charge to the capacitor array at each successive approximation step is drawn through the  $V_{REFH}$  and  $V_{REFL}$  loop. The best external component to meet this current demand is a 0.1  $\mu$ F capacitor with good high frequency characteristics. This capacitor is connected between  $V_{REFH}$  and  $V_{REFL}$  and must be placed as near as possible to the package pins. Resistance in the path is not recommended because the current will cause a voltage drop which could result in conversion errors. Inductance in this path must be minimum (parasitic only).

### 8.6.1.3 Analog Input Pins

The external analog inputs are typically shared with digital I/O pins on MCU devices. The pin I/O control is disabled by setting the appropriate control bit in one of the pin control registers. Conversions can be performed on inputs without the associated pin control register bit set. It is recommended that the pin control register bit always be set when using a pin as an analog input. This avoids problems with contention because the output buffer will be in its high impedance state and the pullup is disabled. Also, the input buffer draws dc current when its input is not at either  $V_{DD}$  or  $V_{SS}$ . Setting the pin control register bits for all pins used as analog inputs must be done to achieve lowest operating current.

Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. Use of 0.01  $\mu$ F capacitors with good high-frequency characteristics is sufficient. These capacitors are not necessary in all cases, but when used they must be placed as near as possible to the package pins and be referenced to V<sub>SSA</sub>.

For proper conversion, the input voltage must fall between  $V_{REFH}$  and  $V_{REFL}$ . If the input is equal to or exceeds  $V_{REFH}$ , the converter circuit converts the signal to \$3FF (full scale 10-bit representation) or \$FF (full scale 8-bit representation). If the input is equal to or less than  $V_{REFL}$ , the converter circuit converts it to \$000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are straight-line linear conversions. There will be a brief current associated with  $V_{REFL}$  when the sampling capacitor is charging. The input is sampled for 3.5 cycles of the ADCK source when ADLSMP is low, or 23.5 cycles when ADLSMP is high.

For minimal loss of accuracy due to current injection, pins adjacent to the analog input pins must not be transitioning during conversions.

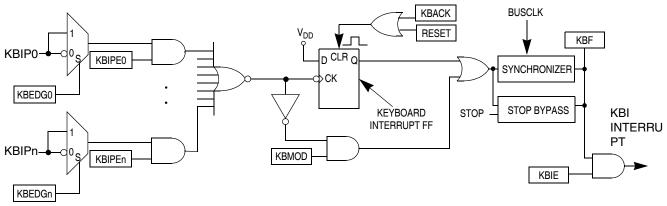

Keyboard Interrupts (S08KBIV2)

Figure 10-2. KBI Block Diagram

### **10.2 External Signal Description**

The KBI input pins can be used to detect either falling edges, or both falling edge and low level interrupt requests. The KBI input pins can also be used to detect either rising edges, or both rising edge and high level interrupt requests.

The signal properties of KBI are shown in Table 10-1.

Table 10-1. Signal Properties

| Signal | Function                | I/O |

|--------|-------------------------|-----|

| KBIPn  | Keyboard interrupt pins | I   |

### 10.3 Register Definition

The KBI includes three registers:

- An 8-bit pin status and control register.

- An 8-bit pin enable register.

- An 8-bit edge select register.

Refer to the direct-page register summary in the Memory chapter for the absolute address assignments for all KBI registers. This section refers to registers and control bits only by their names.

Some MCUs may have more than one KBI, so register names include placeholder characters to identify which KBI is being referenced.

### 10.3.1 KBI Status and Control Register (KBISC)

KBISC contains the status flag and control bits, which are used to configure the KBI.

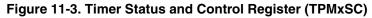

#### Figure 10-3. KBI Status and Control Register

#### Table 10-2. KBISC Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4        | Unused register bits, always read 0.                                                                                                                                                                                        |

| 3<br>KBF   | <ul> <li>Keyboard Interrupt Flag — KBF indicates when a keyboard interrupt is detected. Writes have no effect on KBF.</li> <li>0 No keyboard interrupt detected.</li> <li>1 Keyboard interrupt detected.</li> </ul>         |

| 2<br>KBACK | <b>Keyboard Acknowledge</b> — Writing a 1 to KBACK is part of the flag clearing mechanism. KBACK always reads as 0.                                                                                                         |

| 1<br>KBIE  | <ul> <li>Keyboard Interrupt Enable — KBIE determines whether a keyboard interrupt is requested.</li> <li>Keyboard interrupt request not enabled.</li> <li>Keyboard interrupt request enabled.</li> </ul>                    |

| 0<br>KBMOD | <ul> <li>Keyboard Detection Mode — KBMOD (along with the KBEDG bits) controls the detection mode of the keyboard interrupt pins.0Keyboard detects edges only.</li> <li>1 Keyboard detects both edges and levels.</li> </ul> |

### 10.3.2 KBI Pin Enable Register (KBIPE)

KBIPE contains the pin enable control bits.

Figure 10-4. KBI Pin Enable Register

#### Table 10-3. KBIPE Register Field Descriptions

| Field         | Description                                                                                                                                                                                                         |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>KBIPEn | <ul> <li>Keyboard Pin Enables — Each of the KBIPEn bits enable the corresponding keyboard interrupt pin.</li> <li>0 Pin not enabled as keyboard interrupt.</li> <li>1 Pin enabled as keyboard interrupt.</li> </ul> |

### 10.3.3 KBI Edge Select Register (KBIES)

KBIES contains the edge select control bits.

#### Timer/Pulse-Width Modulator (S08TPMV2)

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

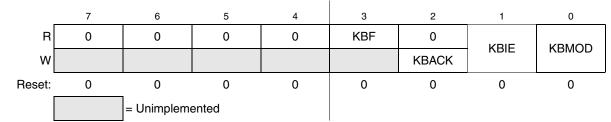

### 11.3.1 Timer Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits that are used to configure the interrupt enable, TPM configuration, clock source, and prescale divisor. These controls relate to all channels within this timer module.

|       | 7                           | 6    | 5     | 4     | 3     | 2   | 1   | 0   |  |

|-------|-----------------------------|------|-------|-------|-------|-----|-----|-----|--|

| R     | TOF                         | TOIL |       |       |       | DCO |     | DCO |  |

| W     |                             | TOIE | CPWMS | CLKSB | CLKSA | PS2 | PS1 | PS0 |  |

| Reset | 0                           | 0    | 0     | 0     | 0     | 0   | 0   | 0   |  |

|       | = Unimplemented or Reserved |      |       |       |       |     |     |     |  |

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | <b>Timer Overflow Flag</b> — This flag is set when the TPM counter changes to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. When the TPM is configured for CPWM, TOF is set after the counter has reached the value in the modulo register, at the transition to the next lower count value. Clear TOF by reading the TPM status and control register when TOF is set and then writing a 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. Reset clears TOF. Writing a 1 to TOF has no effect. 0 TPM counter has not reached modulo value or overflow 1 TPM counter has overflowed |

| 6<br>TOIE        | Timer Overflow Interrupt Enable — This read/write bit enables TPM overflow interrupts. If TOIE is set, aninterrupt is generated when TOF equals 1. Reset clears TOIE.0 TOF interrupts inhibited (use software polling)1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>CPWMS       | <ul> <li>Center-Aligned PWM Select — This read/write bit selects CPWM operating mode. Reset clears this bit so the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up-/down-counting mode for CPWM functions. Reset clears CPWMS.</li> <li>All TPMx channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register</li> <li>All TPMx channels operate in center-aligned PWM mode</li> </ul>                                                                                                                                                                  |

| 4:3<br>CLKS[B:A] | <b>Clock Source Select</b> — As shown in Table 11-2, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The external source and the XCLK are synchronized to the bus clock by an on-chip synchronization circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2:0<br>PS[2:0]   | <b>Prescale Divisor Select</b> — This 3-bit field selects one of eight divisors for the TPM clock input as shown in Table 11-3. This prescaler is located after any clock source synchronization or clock source selection, so it affects whatever clock source is selected to drive the TPM system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

In output compare or PWM modes, writing to either byte (TPMxCnVH or TPMxCnVL) latches the value into a buffer. When both bytes have been written, they are transferred as a coherent 16-bit value into the timer channel value registers. This latching mechanism may be manually reset by writing to the TPMxCnSC register.

This latching mechanism allows coherent 16-bit writes in either order, which is friendly to various compiler implementations.

# **11.4 Functional Description**

All TPM functions are associated with a main 16-bit counter that allows flexible selection of the clock source and prescale divisor. A 16-bit modulo register also is associated with the main 16-bit counter in the TPM. Each TPM channel is optionally associated with an MCU pin and a maskable interrupt function.

The TPM has center-aligned PWM capabilities controlled by the CPWMS control bit in TPMxSC. When CPWMS is set to 1, timer counter TPMxCNT changes to an up-/down-counter and all channels in the associated TPM act as center-aligned PWM channels. When CPWMS = 0, each channel can independently be configured to operate in input capture, output compare, or buffered edge-aligned PWM mode.

The following sections describe the main 16-bit counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend on the operating mode, these topics are covered in the associated mode sections.

### 11.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, up-counting vs. up-/down-counting, end-of-count overflow, and manual counter reset.

After any MCU reset, CLKSB:CLKSA = 0:0 so no clock source is selected and the TPM is inactive. Normally, CLKSB:CLKSA would be set to 0:1 so the bus clock drives the timer counter. The clock source for the TPM can be selected to be off, the bus clock (BUSCLK), the fixed system clock (XCLK), or an external input. The maximum frequency allowed for the external clock option is one-fourth the bus rate. Refer to Section 11.3.1, "Timer Status and Control Register (TPMxSC)" and Table 11-2 for more information about clock source selection.

When the microcontroller is in active background mode, the TPM temporarily suspends all counting until the microcontroller returns to normal user operating mode. During stop mode, all TPM clocks are stopped; therefore, the TPM is effectively disabled until clocks resume. During wait mode, the TPM continues to operate normally.

The main 16-bit counter has two counting modes. When center-aligned PWM is selected (CPWMS = 1), the counter operates in up-/down-counting mode. Otherwise, the counter operates as a simple up-counter. As an up-counter, the main 16-bit counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

# Chapter 12 Development Support

# 12.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip flash and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

# 12.1.1 Forcing Active Background

The method for forcing active background mode depends on the specific HCS08 derivative. For the MC9S08QD4 series, you can force active background mode by holding the BKGD pin low as the MCU exits the reset condition independent of what caused the reset. If no debug pod is connected to the BKGD pin, the MCU will always reset into normal operating mode.

### 12.1.2 Module Configuration

The alternative BDC clock source for MC9S08QD4 series is the ICGCLK. See Chapter 9, "Internal Clock Source (S08ICSV1)," for more information about ICGCLK and how to select clock sources.

**Appendix A Electrical Characteristics**

| Parameter                                                                                                                                                                                       | Symbol                | Min                                                                  | Typical | Мах                      | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------|---------|--------------------------|------|

| High impedance (off-state) leakage current (per pin) $V_{In} = V_{DD}$ or $V_{SS}$ , all input/output                                                                                           | II <sub>OZ</sub> I    | _                                                                    | 0.025   | 1.0                      | μA   |

| Internal pullup resistors <sup>4</sup>                                                                                                                                                          | R <sub>PU</sub>       | 17.5                                                                 |         | 52.5                     | kΩ   |

| Internal pulldown resistor (IRQ)                                                                                                                                                                | R <sub>PD</sub>       | 17.5                                                                 |         | 52.5                     | kΩ   |

| Output high voltage — Low Drive (PTxDSn = 0)<br>5 V, $I_{Load} = -2 \text{ mA}$<br>3 V, $I_{Load} = -0.6 \text{ mA}$<br>5 V, $I_{Load} = -0.4 \text{ mA}$<br>3 V, $I_{Load} = -0.24 \text{ mA}$ |                       | $V_{DD} - 1.5$<br>$V_{DD} - 1.5$<br>$V_{DD} - 0.8$<br>$V_{DD} - 0.8$ |         | <br>                     |      |

| Output high voltage — High Drive (PTxDSn = 1)<br>5 V, $I_{Load} = -10 \text{ mA}$<br>3 V, $I_{Load} = -3 \text{ mA}$<br>5 V, $I_{Load} = -2 \text{ mA}$<br>3 V, $I_{Load} = -0.4 \text{ mA}$    | V <sub>OH</sub>       | $V_{DD} - 1.5$<br>$V_{DD} - 1.5$<br>$V_{DD} - 0.8$<br>$V_{DD} - 0.8$ |         | <br>                     | v    |

| Maximum total I <sub>OH</sub> for all port pins<br>5V<br>3V                                                                                                                                     | II <sub>OHT</sub> I   | _                                                                    | _       | 100<br>60                | mA   |

| Output low voltage — Low Drive (PTxDSn = 0)<br>5 V, $I_{Load} = 2 \text{ mA}$<br>3 V, $I_{Load} = 0.6 \text{ mA}$<br>5 V, $I_{Load} = 0.4 \text{ mA}$<br>3 V, $I_{Load} = 0.24 \text{ mA}$      |                       | <br>                                                                 |         | 1.5<br>1.5<br>0.8<br>0.8 |      |

| Output low voltage — High Drive (PTxDSn = 1)<br>5 V, $I_{Load} = 10 \text{ mA}$<br>3 V, $I_{Load} = 3 \text{ mA}$<br>5 V, $I_{Load} = 2 \text{ mA}$<br>3 V, $I_{Load} = 0.4 \text{ mA}$         | V <sub>OL</sub>       | <br>                                                                 |         | 1.5<br>1.5<br>0.8<br>0.8 | V    |

| Maximum total I <sub>OL</sub> for all port pins<br>5V<br>3V                                                                                                                                     | I <sub>OLT</sub>      |                                                                      |         | 100<br>60                | mA   |

| DC injection current <sup>2, 5, 6, 7</sup><br>Single pin limit<br>V <sub>IN</sub> > V<br>V <sub>IN</sub> < V<br>Total MCU limit, includes sum of all stressed pins                              | ss I <sub>IC</sub>    | 0                                                                    | _       | 2<br>0.2                 | mA   |

| $V_{IN} > V_{V}$<br>$V_{IN} < V$<br>Input capacitance (all non-supply pins)                                                                                                                     | SS<br>C <sub>In</sub> | 0                                                                    |         | 12<br>-1.2<br>7          | pF   |

| input capacitance (an non-supply pins)                                                                                                                                                          | Uln                   |                                                                      |         |                          | μ    |

<sup>1</sup> Maximum is highest voltage that POR is guaranteed.

<sup>2</sup> RAM will retain data down to POR voltage. RAM data not guaranteed to be valid following a POR.

<sup>3</sup> This parameter is characterized and not tested on each device.

$^4$  Measurement condition for pull resistors:  $V_{In}$  =  $V_{SS}$  for pullup and  $V_{In}$  =  $V_{DD}$  for pulldown.

$^5\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$

<sup>6</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUT | LINE PRINT VERSION   | NOT TO SCALE |

|---------------------------------------------------------|----------------|----------------------|--------------|

| TITLE:                                                  | DOCU           | MENT NO: 98ASB42420B | REV: N       |

| 8 LD PDIP                                               | CASE           | NUMBER: 626-06       | 19 MAY 2005  |

|                                                         | STAN           | STANDARD: NON-JEDEC  |              |