# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | S08                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 10MHz                                                     |

| Connectivity               | -                                                         |

| Peripherals                | LVD, POR, PWM, WDT                                        |

| Number of I/O              | 4                                                         |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | 8-PDIP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08qd4vpc |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Chapter 2 External Signal Description

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

## 2.2.5 General-Purpose I/O and Peripheral Ports

The MC9S08QD4 series of MCUs support up to 4 general-purpose I/O pins, 1 input-only pin and 1 output-only pin, which are shared with on-chip peripheral functions (timers, serial I/O, ADC, keyboard interrupts, etc.). On each of the MC9S08QD4 series devices there is one input-only and one output-only port pin.

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pullup device.

For information about controlling these pins as general-purpose I/O pins, see the Chapter 6, "Parallel Input/Output Control." For information about how and when on-chip peripheral systems use these pins, see the appropriate chapter referenced in Table 2-1.

Immediately after reset, all pins that are not output-only are configured as high-impedance, general-purpose inputs with internal pullup devices disabled. After reset, the output-only port function is not enabled but is configured for low output drive strength with slew rate control enabled. The PTA4 pin defaults to BKGD/MS on any reset.

#### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program must either enable on-chip pullup devices or change the direction of unused pins to outputs so the pins do not float.

#### 2.2.5.1 Pin Control Registers

To select drive strength or enable slew rate control or pullup devices, the user writes to the appropriate pin control register located in the high-page register block of the memory map. The pin control registers operate independently of the parallel I/O registers and allow control of a port on an individual pin basis.

#### 2.2.5.1.1 Internal Pullup Enable

An internal pullup device can be enabled for each port pin by setting the corresponding bit in one of the pullup enable registers (PTxPEn). The pullup device is disabled if the pin is configured as an output by the parallel I/O control logic or any shared peripheral function, regardless of the state of the corresponding pullup enable register bit. The pullup device is also disabled if the pin is controlled by an analog function.

The KBI module and IRQ function when enabled for rising edge detection causes an enabled internal pull device to be configured as a pulldown.

Chapter 4 Memory Map and Register Definition

# 4.2 Reset and Interrupt Vector Assignments

Table 4-1 shows address assignments for reset and interrupt vectors. The vector names shown in this table are the labels used in the Freescale Semiconductor-provided equate file for the MC9S08QD4 series.

| Address<br>(High/Low) | Vector                                              | Vector Name |

|-----------------------|-----------------------------------------------------|-------------|

| 0xFFC0:FFC1           | Unused Vector Space<br>(available for user program) |             |

| 0xFFCE:FFCF           |                                                     |             |

| 0xFFD0:FFD1           | RTI                                                 | Vrti        |

| 0xFFD2:FFD3           | Reserved                                            | _           |

| 0xFFD4:FFD5           | Reserved                                            | _           |

| 0xFFD6:FFD7           | Reserved                                            | _           |

| 0xFFD8:FFD9           | ADC1 Conversion                                     | Vadc1       |

| 0xFFDA:FFDB           | KBI Interrupt                                       | Vkeyboard1  |

| 0xFFDC:FFDD           | Reserved                                            | _           |

| 0xFFDE:FFDF           | Reserved                                            | _           |

| 0xFFE0:FFE1           | Reserved                                            | _           |

| 0xFFE2:FFE3           | Reserved                                            | _           |

| 0xFFE4:FFE5           | Reserved                                            | _           |

| 0xFFE6:FFE7           | Reserved                                            | _           |

| 0xFFE8:FFE9           | Reserved                                            | _           |

| 0xFFEA:FFEB           | TPM2 Overflow                                       | Vtpm2ovf    |

| 0xFFEC:FFED           | Reserved                                            | _           |

| 0xFFEE:FFEF           | TPM2 Channel 0                                      | Vtpm2ch0    |

| 0xFFF0:FFF1           | TPM1 Overflow                                       | Vtpm1ovf    |

| 0xFFF2:FFF3           | TPM1 Channel 1                                      | Vtpm1ch1    |

| 0xFFF4:FFF5           | TPM1 Channel 0                                      | Vtpm1ch0    |

| 0xFFF6:FFF7           | Reserved                                            | —           |

| 0xFFF8:FFF9           | IRQ                                                 | IRQ         |

| 0xFFFA:FFFB           | Low Voltage Detect                                  | Vlvd        |

| 0xFFFC:FFFD           | SWI                                                 | Vswi        |

| 0xFFFE:FFFF           | Reset                                               | Vreset      |

MC9S08QD4 Series MCU Data Sheet, Rev. 6

#### **Chapter 4 Memory Map and Register Definition**

is no way to disengage security without completely erasing all flash locations. If KEYEN is 1, a secure user program can temporarily disengage security by:

- 1. Writing 1 to KEYACC in the FCNFG register. This makes the flash module interpret writes to the backdoor comparison key locations (NVBACKKEY through NVBACKKEY+7) as values to be compared against the key rather than as the first step in a flash program or erase command.

- 2. Writing the user-entered key values to the NVBACKKEY through NVBACKKEY+7 locations. These writes must be performed in order starting with the value for NVBACKKEY and ending with NVBACKKEY+7. STHX must not be used for these writes because these writes cannot be performed on adjacent bus cycles. User software normally would get the key codes from outside the MCU system through a communication interface such as a serial I/O.

- 3. Writing 0 to KEYACC in the FCNFG register. If the 8-byte key that was written matches the key stored in the flash locations, SEC01:SEC00 are automatically changed to 1:0 and security will be disengaged until the next reset.

The security key can be written only from secure memory (either RAM or flash), so it cannot be entered through background commands without the cooperation of a secure user program.

The backdoor comparison key (NVBACKKEY through NVBACKKEY+7) is located in flash memory locations in the nonvolatile register space so users can program these locations exactly as they would program any other flash memory location. The nonvolatile registers are in the same 512-byte block of flash as the reset and interrupt vectors, so block protecting that space also block protects the backdoor comparison key. Block protects cannot be changed from user application programs, so if the vector space is block protected, the backdoor security key mechanism cannot permanently change the block protect, security settings, or the backdoor key.

Security can always be disengaged through the background debug interface by taking these steps:

- 1. Disable any block protections by writing FPROT. FPROT can be written only with background debug commands, not from application software.

- 2. Mass erase flash if necessary.

- 3. Blank check flash. Provided flash is completely erased, security is disengaged until the next reset. To avoid returning to secure mode after the next reset, program NVOPT so SEC01:SEC00 = 1:0.

# 4.7 Flash Registers and Control Bits

The flash module has nine 8-bit registers in the high-page register space, two locations (NVOPT, NVPROT) in the nonvolatile register space in flash memory are copied into corresponding high-page control registers (FOPT, FPROT) at reset. There is also an 8-byte comparison key in flash memory. Refer to Table 4-3 and Table 4-4 for the absolute address assignments for all flash registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

# 4.7.1 Flash Clock Divider Register (FCDIV)

Before any erase or programming operations are possible, write to this register to set the frequency of the clock for the nonvolatile memory system within acceptable limits.

Chapter 5 Resets, Interrupts, and General System Control

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COPE becomes set in SOPT1 enabling the COP watchdog (see Section 5.8.5, "System Options Register 2 (SOPT2)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPE. The COP counter is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP counter.

The COPCLKS bit in SOPT2 (see Section 5.8.5, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 32 kHz clock source. With each clock source, there is an associated short and long time-out controlled by COPT in SOPT1. Table 5-1 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the 32 kHz clock source and the associated long time-out ( $2^8$  cycles).

| Contro  | Control Bits |                                  | COP Overflow Count                           |

|---------|--------------|----------------------------------|----------------------------------------------|

| COPCLKS | COPT         | <ul> <li>Clock Source</li> </ul> |                                              |

| 0       | 0            | ~32 kHz                          | 2 <sup>10</sup> cycles (32 ms) <sup>1</sup>  |

| 0       | 1            | ~32 kHz                          | 2 <sup>13</sup> cycles (256 ms) <sup>1</sup> |

| 1       | 0            | Bus                              | 2 <sup>13</sup> cycles                       |

| 1       | 1            | Bus                              | 2 <sup>18</sup> cycles                       |

Table 5-1. COP Configuration Options

<sup>1</sup> Values are shown in this column based on  $t_{RTI} = 1$  ms. See  $t_{RTI}$  in the Section A.8.1, "Control Timing," for the tolerance of this value.

Even if the application will use the reset default settings of COPE, COPCLKS and COPT, the user must write to the write-once SOPT1 and SOPT2 registers during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost. The initial writes to SOPT1 and SOPT2 will reset the COP counter.

The write to SRS that services (clears) the COP counter must not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

In Background debug mode, the COP counter will not increment.

When the bus clock source is selected, the COP counter does not increment while the system is in stop mode. The COP counter resumes once the MCU exits stop mode.

When the 32 kHz clock source is selected, the COP counter is re-initialized to zero upon entry to stop mode. The COP counter begins from zero once the MCU exits stop mode.

## 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the  $V_{POR}$  level, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the  $V_{LVDL}$  level. Both the POR bit and the LVD bit in SRS are set following a POR.

## 5.6.2 LVD Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the level determined by LVDV. The LVD bit in the SRS register is set following either an LVD reset or POR.

## 5.6.3 LVD Interrupt Operation

When a low voltage condition is detected and the LVD circuit is configured using SPMSC1 for interrupt operation (LVDE set, LVDIE set, and LVDRE clear), then LVDF in SPMSC1 will be set and an LVD interrupt request will occur.

## 5.6.4 Low-Voltage Warning (LVW)

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching, but is above, the LVD voltage. The LVW does not have an interrupt associated with it. There are two user selectable trip voltages for the LVW, one high ( $V_{LVWH}$ ) and one low ( $V_{LVWL}$ ). The trip voltage is selected by LVWV in SPMSC2.

## 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts. The RTI can accept two sources of clocks, the 1 kHz internal clock or an 32 kHz ICS clock if available. The RTICLKS bit in SRTISC is used to select the RTI clock source.

Both clock source can be used when the MCU is in run, wait or stop3 mode. When using the 32 kHz ICS clock in stop3, it must be enabled in stop (EREFSTEN = 1) and configured for low frequency operation (RANGE = 0). Only the internal 1 kHz clock source can be selected to wake the MCU from stop1 or stop2 modes.

The SRTISC register includes a read-only status flag, a write-only acknowledge bit, and a 3-bit control value (RTIS) used to select one of seven wakeup periods. The RTI has a local interrupt enable, RTIE, to allow masking of the real-time interrupt. The RTI can be disabled by writing each bit of RTIS to zeroes, and no interrupts will be generated. See Section 5.8.7, "System Real-Time Interrupt Status and Control Register (SRTISC)," for detailed information about this register.

| Field      | Description                                                                                                                                                                                                                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>LVDIE | <ul> <li>Low-Voltage Detect Interrupt Enable — This bit enables hardware interrupt requests for LVDF.</li> <li>0 Hardware interrupt disabled (use polling).</li> <li>1 Request a hardware interrupt when LVDF = 1.</li> </ul>                                                                          |

| 4<br>LVDRE | <ul> <li>Low-Voltage Detect Reset Enable — This write-once bit enables LVDF events to generate a hardware reset (provided LVDE = 1).</li> <li>0 LVDF does not generate hardware resets.</li> <li>1 Force an MCU reset when LVDF = 1.</li> </ul>                                                        |

| 3<br>LVDSE | <ul> <li>Low-Voltage Detect Stop Enable — Provided LVDE = 1, this read/write bit determines whether the low-voltage detect function operates when the MCU is in stop mode.</li> <li>0 Low-voltage detect disabled during stop mode.</li> <li>1 Low-voltage detect enabled during stop mode.</li> </ul> |

| 2<br>LVDE  | <ul> <li>Low-Voltage Detect Enable — This write-once bit enables low-voltage detect logic and qualifies the operation of other bits in this register.</li> <li>0 LVD logic disabled.</li> <li>1 LVD logic enabled.</li> </ul>                                                                          |

| 0<br>BGBE  | <ul> <li>Bandgap Buffer Enable — This bit enables an internal buffer for the bandgap voltage reference for use by the ADC module on one of its internal channels.</li> <li>0 Bandgap buffer disabled.</li> <li>1 Bandgap buffer enabled.</li> </ul>                                                    |

# 5.8.9 System Power Management Status and Control 2 Register (SPMSC2)

This high-page register contains status and control bits to configure the stop mode behavior of the MCU. See Section 3.6, "Stop Modes," for more information on stop modes.

| _              | 7              | 6            | 5              | 4    | 3    | 2           | 1            | 0                 |

|----------------|----------------|--------------|----------------|------|------|-------------|--------------|-------------------|

| R              | LVWF           | 0            | LVDV           |      | PPDF | 0           |              | PPDC <sup>1</sup> |

| w              |                | LVWACK       | LVDV           | LVWV |      | PPDACK      |              | PPDC              |

| POR:           | 0 <sup>2</sup> | 0            | 0              | 0    | 0    | 0           | 0            | 0                 |

| LVDR:          | 0 <sup>2</sup> | 0            | U              | U    | 0    | 0           | 0            | 0                 |

| Other<br>Reset | 0 <sup>2</sup> | 0            | U              | U    | 0    | 0           | 0            | 0                 |

| [              |                | = Unimplemer | ted or Reserve | ed   |      | U = Unaffec | ted by reset |                   |

<sup>1</sup> This bit can be written only one time after reset. Additional writes are ignored.

$^2$  LVWF will be set in the case when V<sub>supply</sub> transitions below the trip point or after reset and V<sub>supply</sub> is already below V<sub>LVW</sub>.

#### Figure 5-11. System Power Management Status and Control 2 Register (SPMSC2)

#### **Chapter 6 Parallel Input/Output Control**

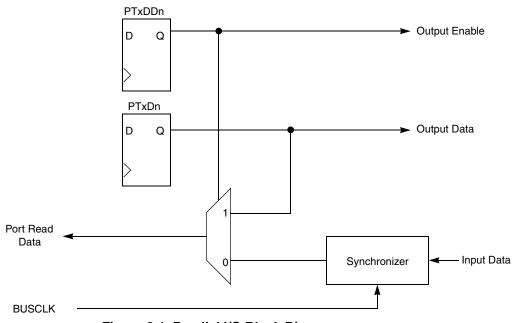

Figure 6-1. Parallel I/O Block Diagram

The data direction control bit (PTxDDn) determines whether the output buffer for the associated pin is enabled, and also controls the source for port data register reads. The input buffer for the associated pin is always enabled unless the pin is enabled as an analog function or is an output-only pin.

When a shared digital function is enabled for a pin, the output buffer is controlled by the shared function. However, the data direction register bit will continue to control the source for reads of the port data register.

When a shared analog function is enabled for a pin, both the input and output buffers are disabled. A value of 0 is read for any port data bit where the bit is an input (PTxDDn = 0) and the input buffer is disabled. In general, whenever a pin is shared with both an alternate digital function and an analog function, the analog function has priority such that if both the digital and analog functions are enabled, the analog function controls the pin.

It is a good programming practice to write to the port data register before changing the direction of a port pin to become an output. This ensures that the pin will not be driven momentarily with an old data value that happened to be in the port data register.

# 6.2 Pin Control — Pullup, Slew Rate and Drive Strength

Associated with the parallel I/O ports is a set of registers located in the high-page register space that operate independently of the parallel I/O registers. These registers are used to control pullups, slew rate and drive strength for the pins.

# 6.3 Pin Behavior in Stop Modes

Pin behavior following execution of a STOP instruction depends on the stop mode that is entered. An explanation of pin behavior for the various stop modes follows:

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

## 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

#### MC9S08QD4 Series MCU Data Sheet, Rev. 6

#### Internal Clock Source (S08ICSV1)

times the filter frequency, as selected by the RDIV bits, so that the ICSLCLK will be available for BDC communications, and the external reference clock is enabled.

## 9.4.1.6 FLL Bypassed External Low Power (FBELP)

The FLL bypassed external low power (FBELP) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is not active and LP bit is written to 1.

In FLL bypassed external low power mode, the ICSOUT clock is derived from the external reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications. The external reference clock is enabled.

### 9.4.1.7 Stop

Stop mode is entered whenever the MCU enters a STOP state. In this mode, all ICS clock signals are static except in the following cases:

ICSIRCLK will be active in stop mode when all the following conditions occur:

- IRCLKEN bit is written to 1

- IREFSTEN bit is written to 1

ICSERCLK will be active in stop mode when all the following conditions occur:

- ERCLKEN bit is written to 1

- EREFSTEN bit is written to 1

## 9.4.2 Mode Switching

When switching between FLL engaged internal (FEI) and FLL engaged external (FEE) modes the IREFS bit can be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. After a change in the IREFS value the FLL will begin locking again after a few full cycles of the resulting divided reference frequency.

The CLKS bits can also be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. The actual switch to the newly selected clock will not occur until after a few full cycles of the new clock. If the newly selected clock is not available, the previous clock will remain selected.

# 9.4.3 Bus Frequency Divider

The BDIV bits can be changed at anytime and the actual switch to the new frequency will occur immediately.

# 9.4.4 Low Power Bit Usage

The low power bit (LP) is provided to allow the FLL to be disabled and thus conserve power when it is not being used. However, in some applications it may be desirable to enable the FLL and allow it to lock for maximum accuracy before switching to an FLL engaged mode. Do this by writing the LP bit to 0.

## 9.4.5 Internal Reference Clock

When IRCLKEN is set the internal reference clock signal will be presented as ICSIRCLK, which can be used as an additional clock source. The ICSIRCLK frequency can be re-targeted by trimming the period of the internal reference clock. This can be done by writing a new value to the TRIM bits in the ICSTRM register. Writing a larger value will slow down the ICSIRCLK frequency, and writing a smaller value to the ICSTRM register will speed up the ICSIRCLK frequency. The TRIM bits will effect the ICSOUT frequency if the ICS is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or FLL bypassed internal low power (FBILP) mode. The TRIM and FTRIM value will not be affected by a reset.

Until ICSIRCLK is trimmed, programming low reference divider (RDIV) factors may result in ICSOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock timing specifications (see the Device Overview chapter).

If IREFSTEN is set and the IRCLKEN bit is written to 1, the internal reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

All MCU devices are factory programmed with a trim value in a reserved memory location. This value can be copied to the ICSTRM register during reset initialization. The factory trim value does not include the FTRIM bit. For finer precision, the user can trim the internal oscillator in the application and set the FTRIM bit accordingly.

## 9.4.6 Optional External Reference Clock

The ICS module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz in all modes. When the ERCLKEN is set, the external reference clock signal will be presented as ICSERCLK, which can be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by the FLL and will only be used as ICSERCLK. In these modes, the frequency can be equal to the maximum frequency the chip-level timing specifications will support (see the Device Overview chapter).

If EREFSTEN is set and the ERCLKEN bit is written to 1, the external reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

Internal Clock Source (S08ICSV1)

# 9.4.7 Fixed Frequency Clock

The ICS presents the divided FLL reference clock as ICSFFCLK for use as an additional clock source for peripheral modules. The ICS provides an output signal (ICSFFE) which indicates when the ICS is providing ICSOUT frequencies four times or greater than the divided FLL reference clock (ICSFFCLK). In FLL engaged mode (FEI and FEE) this is always true and ICSFFE is always high. In ICS bypass modes, ICSFFE will get asserted for the following combinations of BDIV and RDIV values:

- BDIV=00 (divide by 1), RDIV  $\ge$  010

- BDIV=01 (divide by 2), RDIV  $\ge$  011

- BDIV=10 (divide by 4), RDIV  $\geq$  100

- BDIV=11 (divide by 8), RDIV  $\geq$  101

# 9.5 Module Initialization

This section describes how to initialize and configure the ICS module. The following sections contain two initialization examples.

## 9.5.1 ICS Module Initialization Sequence

The ICS comes out of POR configured for FEI mode with the BDIV set for divide-by 2. The internal reference will stabilize in  $t_{IRST}$  microseconds before the FLL can acquire lock. As soon as the internal reference is stable, the FLL will acquire lock in  $t_{Acquire}$  milliseconds.

Upon POR, the internal reference will require trimming to guarantee an accurate clock. Freescale recommends using FLASH location 0xFFAE for storing the fine trim bit, FTRIM in the ICSSC register, and 0xFFAF for storing the 8-bit trim value for the ICSTRM register. The MCU will not automatically copy the values in these FLASH locations to the respective registers. Therefore, user code must copy these values from FLASH to the registers.

#### NOTE

The BDIV value must not be changed to divide-by 1 without first trimming the internal reference. Failure to do so could result in the MCU running out of specification.

## 9.5.1.1 Initialization Sequence, Internal Clock Mode to External Clock Mode

To change from FEI or FBI clock modes to FEE or FBE clock modes, follow this procedure:

- 1. Enable the external clock source by setting the appropriate bits in ICSC2.

- If FBE will be the selected mode, also set the LP bit at this time to minimize power consumption.

- 2. If necessary, wait for the external clock source to stabilize. Typical crystal startup times are given in Electrical Characteristics appendix. If EREFS is set in step 1, then the OSCINIT bit will set as soon as the oscillator has completed the initialization cycles.

- 3. Write to ICSC1 to select the clock mode.

Internal Clock Source (S08ICSV1)

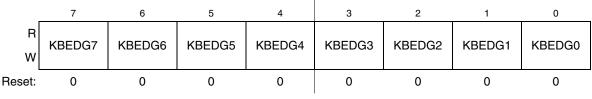

Keyboard Interrupts (S08KBIV2)

Figure 10-5. KBI Edge Select Register

Table 10-4. KBIES Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>KBEDGn | <ul> <li>Keyboard Edge Selects — Each of the KBEDGn bits selects the falling edge/low level or rising edge/high level function of the corresponding pin).</li> <li>Falling edge/low level.</li> <li>Rising edge/high level.</li> </ul> |

# **10.4 Functional Description**

This on-chip peripheral module is called a keyboard interrupt (KBI) module because originally it was designed to simplify the connection and use of row-column matrices of keyboard switches. However, these inputs are also useful as extra external interrupt inputs and as an external means of waking the MCU from stop or wait low-power modes.

The KBI module allows up to eight pins to act as additional interrupt sources. Writing to the KBIPEn bits in the keyboard interrupt pin enable register (KBIPE) independently enables or disables each KBI pin. Each KBI pin can be configured as edge sensitive or edge and level sensitive based on the KBMOD bit in the keyboard interrupt status and control register (KBISC). Edge sensitive can be software programmed to be either falling or rising; the level can be either low or high. The polarity of the edge or edge and level sensitivity is selected using the KBEDGn bits in the keyboard interrupt edge select register (KBISC).

# 10.4.1 Edge Only Sensitivity

Synchronous logic is used to detect edges. A falling edge is detected when an enabled keyboard interrupt (KBIPEn=1) input signal is seen as a logic 1 (the deasserted level) during one bus cycle and then a logic 0 (the asserted level) during the next cycle. A rising edge is detected when the input signal is seen as a logic 0 (the deasserted level) during one bus cycle and then a logic 1 (the asserted level) during the next cycle. Before the first edge is detected, all enabled keyboard interrupt input signals must be at the deasserted logic levels. After any edge is detected, all enabled keyboard interrupt input signals must return to the deasserted level before any new edge can be detected.

A valid edge on an enabled KBI pin will set KBF in KBISC. If KBIE in KBISC is set, an interrupt request will be presented to the CPU. Clearing of KBF is accomplished by writing a 1 to KBACK in KBISC.

# 10.4.2 Edge and Level Sensitivity

A valid edge or level on an enabled KBI pin will set KBF in KBISC. If KBIE in KBISC is set, an interrupt request will be presented to the CPU. Clearing of KBF is accomplished by writing a 1 to KBACK in

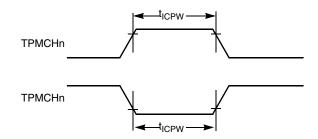

All TPM channels are programmable independently as input capture, output compare, or buffered edge-aligned PWM channels.

# 11.2 External Signal Description

When any pin associated with the timer is configured as a timer input, a passive pullup can be enabled. After reset, the TPM modules are disabled and all pins default to general-purpose inputs with the passive pullups disabled.

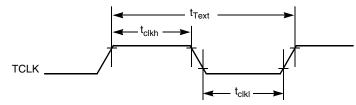

# 11.2.1 External TPM Clock Sources

When control bits CLKSB:CLKSA in the timer status and control register are set to 1:1, the prescaler and consequently the 16-bit counter for TPMx are driven by an external clock source, TPMxCLK, connected to an I/O pin. A synchronizer is needed between the external clock and the rest of the TPM. This synchronizer is clocked by the bus clock so the frequency of the external source must be less than one-half the frequency of the bus rate clock. The upper frequency limit for this external clock source is specified to be one-fourth the bus frequency to conservatively accommodate duty cycle and phase-locked loop (PLL) or frequency-locked loop (FLL) frequency jitter effects.

On some devices the external clock input is shared with one of the TPM channels. When a TPM channel is shared as the external clock input, the associated TPM channel cannot use the pin. (The channel can still be used in output compare mode as a software timer.) Also, if one of the TPM channels is used as the external clock input, the corresponding ELSnB:ELSnA control bits must be set to 0:0 so the channel is not trying to use the same pin.

# 11.2.2 TPMxCHn — TPMx Channel n I/O Pins

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the configuration of the channel. In some cases, no pin function is needed so the pin reverts to being controlled by general-purpose I/O controls. When a timer has control of a port pin, the port data and data direction registers do not affect the related pin(s). See the Pins and Connections chapter for additional information about shared pin functions.

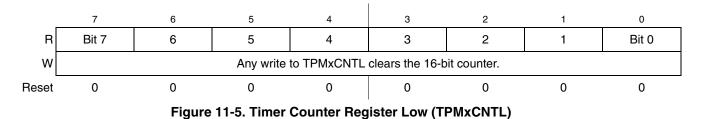

# 11.3 Register Definition

The TPM includes:

- An 8-bit status and control register (TPMxSC)

- A 16-bit counter (TPMxCNTH:TPMxCNTL)

- A 16-bit modulo register (TPMxMODH:TPMxMODL)

Each timer channel has:

- An 8-bit status and control register (TPMxCnSC)

- A 16-bit channel value register (TPMxCnVH:TPMxCnVL)

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all TPM registers. This section refers to registers and control bits only by their names. A

Timer/Pulse-Width Modulator (S08TPMV2)

When background mode is active, the timer counter and the coherency mechanism are frozen such that the buffer latches remain in the state they were in when the background mode became active even if one or both bytes of the counter are read while background mode is active.

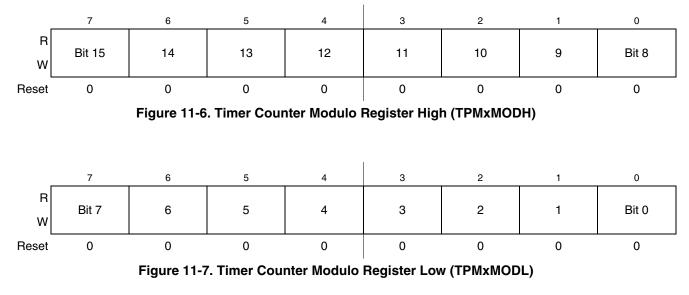

# 11.3.3 Timer Counter Modulo Registers (TPMxMODH:TPMxMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock (CPWMS = 0) or starts counting down (CPWMS = 1), and the overflow flag (TOF) becomes set. Writing to TPMxMODH or TPMxMODL inhibits TOF and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000, which results in a free-running timer counter (modulo disabled).

It is good practice to wait for an overflow interrupt so both bytes of the modulo register can be written well before a new overflow. An alternative approach is to reset the TPM counter before writing to the TPM modulo registers to avoid confusion about when the first counter overflow will occur.

#### Development Support

when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

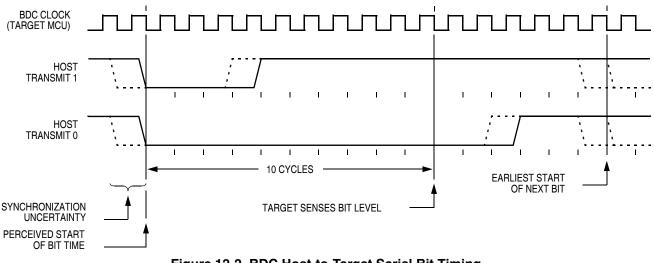

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.

Figure 12-2 shows an external host transmitting a logic 1 or 0 to the BKGD pin of a target HCS08 MCU. The host is asynchronous to the target so there is a 0-to-1 cycle delay from the host-generated falling edge to where the target perceives the beginning of the bit time. Ten target BDC clock cycles later, the target senses the bit level on the BKGD pin. Typically, the host actively drives the pseudo-open-drain BKGD pin during host-to-target transmissions to speed up rising edges. Because the target does not drive the BKGD pin during the host-to-target transmission period, there is no need to treat the line as an open-drain signal during this period.

Figure 12-2. BDC Host-to-Target Serial Bit Timing

Figure 12-3 shows the host receiving a logic 1 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the perceived start of the bit time in the target MCU. The host holds the BKGD pin low long enough for the target to recognize it (at least two target BDC cycles). The host must release the low drive before the target MCU drives a brief active-high speedup pulse seven cycles after the perceived start of the bit time. The host must sample the bit level about 10 cycles after it started the bit time.

**Appendix A Electrical Characteristics**

# A.8 AC Characteristics

This section describes AC timing characteristics for each peripheral system.

# A.8.1 Control Timing

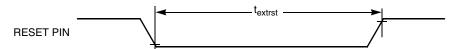

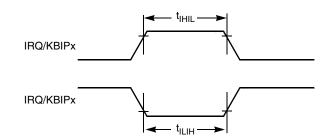

#### Table A-8. Control Timing

| Parameter                                                                                                                             | Symbol                                | Min                         | Typical <sup>1</sup> | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|----------------------|------|------|

| Bus frequency $(t_{cyc} = 1/f_{Bus})$                                                                                                 | f <sub>Bus</sub>                      | 1                           | _                    | 8    | MHz  |

| Real-time interrupt internal oscillator period                                                                                        | t <sub>RTI</sub>                      | 700                         | —                    | 1300 | μS   |

| External reset pulse width <sup>2</sup>                                                                                               | t <sub>extrst</sub>                   | 100                         | _                    | _    | ns   |

| IRQ pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>3</sup>                                                    | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 t <sub>cyc</sub> | _                    | _    | ns   |

| KBIPx pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>3</sup>                                                  | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 t <sub>cyc</sub> | _                    | _    | ns   |

| Port rise and fall time $(load = 50 \text{ pF})^4$<br>Slew rate control disabled (PTxSE = 0)<br>Slew rate control enabled (PTxSE = 1) | t <sub>Rise</sub> , t <sub>Fall</sub> |                             | 3<br>30              |      | ns   |

| BKGD/MS setup time after issuing background debug force reset to enter user or BDM modes                                              | t <sub>MSSU</sub>                     | 500                         | _                    | _    | ns   |

| BKGD/MS hold time after issuing background debug force reset to enter user or BDM modes $^{\rm 5}$                                    | t <sub>MSH</sub>                      | 100                         | —                    | —    | μs   |

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25°C.

<sup>2</sup> This is the shortest pulse that is guaranteed to be recognized.

<sup>3</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

$^4$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40°C to 125°C.

<sup>5</sup> To enter BDM mode following a POR, BKGD/MS must be held low during the power-up and for a hold time of t<sub>MSH</sub> after V<sub>DD</sub> rises above V<sub>LVD</sub>.

Figure A-12. Reset Timing

Figure A-13. IRQ/KBIPx Timing

## A.8.2 Timer/PWM (TPM) Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| Function                  | Symbol            | Min | Max                 | Unit             |

|---------------------------|-------------------|-----|---------------------|------------------|

| External clock frequency  | f <sub>TCLK</sub> | dc  | f <sub>Bus</sub> /4 | MHz              |

| External clock period     | t <sub>TCLK</sub> | 4   | —                   | t <sub>cyc</sub> |

| External clock high time  | t <sub>clkh</sub> | 1.5 | —                   | t <sub>cyc</sub> |

| External clock low time   | t <sub>clkl</sub> | 1.5 | —                   | t <sub>cyc</sub> |

| Input capture pulse width | t <sub>ICPW</sub> | 1.5 | —                   | t <sub>cyc</sub> |

Table A-9. TPM/MTIM Input Timing

Figure A-14. Timer External Clock

Figure A-15. Timer Input Capture Pulse

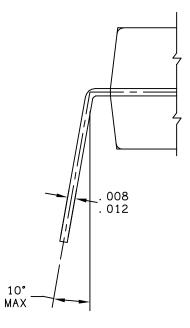

DETAIL "D"

| © FREESCALE SEMICONDUCTOR, INC.<br>All Rights reserved. |       | .INE PRINT VERSION N | NOT TO SCALE |

|---------------------------------------------------------|-------|----------------------|--------------|

| TITLE:                                                  | DOCUM | IENT NO: 98ASB42420B | REV: N       |

| 8 LD PDIP                                               | CASE  | NUMBER: 626-06       | 19 MAY 2005  |

|                                                         | STAND | ARD: NON-JEDEC       |              |

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- A DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- A. DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC.<br>All Rights reserved. |  | LOUTLINE                      | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--|-------------------------------|------------------|-------------|

| TITLE:                                                  |  | DOCUMENT NO                   | ): 98ASB42564B   | REV: U      |

| 8LD SOIC NARROW BODY                                    |  | CASE NUMBER: 751–07 07 APR 20 |                  | 07 APR 2005 |

|                                                         |  | STANDARD: JE                  | DEC MS-012AA     |             |