Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | - ·                                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 4                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 256 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 4x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                         |

| Supplier Device Package    | 8-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08qd4j1csc |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Chapter 2 External Signal Description

the CPU executes a STOP instruction, the MCU will not enter either of the stop modes and an illegal opcode reset is forced. The stop modes are selected by setting the appropriate bits in SPMSC2.

HCS08 devices that are designed for low voltage operation (1.8V to 3.6V) also include stop1 mode. The MC9S08QD4 series does not include stop1 mode.

| Mode  | PPDC | CPU, Digital<br>Peripherals,<br>Flash | RAM     | ICS              | ADC1          | Regulator | I/O Pins    | RTI           |

|-------|------|---------------------------------------|---------|------------------|---------------|-----------|-------------|---------------|

| Stop2 | 1    | Off                                   | Standby | Off              | Disabled      | Standby   | States held | Optionally on |

| Stop3 | 0    | Standby                               | Standby | Off <sup>1</sup> | Optionally on | Standby   | States held | Optionally on |

Table 3-1 summarizes the behavior of the MCU in each of the stop modes.

<sup>1</sup> ICS can be configured to run in stop3. Please see the ICS registers.

### 3.6.1 Stop2 Mode

The stop2 mode provides very low standby power consumption and maintains the contents of RAM and the current state of all of the I/O pins. To enter stop2, the user must execute a STOP instruction with stop2 selected (PPDC = 1) and stop mode enabled (STOPE = 1). In addition, the LVD must not be enabled to operate in stop (LVDSE = 0 or LVDE = 0). If the LVD is enabled in stop, then the MCU enters stop3 upon the execution of the STOP instruction regardless of the state of PPDC.

Before entering stop2 mode, the user must save the contents of the I/O port registers, as well as any other memory-mapped registers which they want to restore after exit of stop2, to locations in RAM. Upon exit of stop2, these values can be restored by user software before pin latches are opened.

When the MCU is in stop2 mode, all internal circuits that are powered from the voltage regulator are turned off, except for the RAM. The voltage regulator is in a low-power standby state, as is the ADC. Upon entry into stop2, the states of the I/O pins are latched. The states are held while in stop2 mode and after exiting stop2 mode until a logic 1 is written to PPDACK in SPMSC2.

Exit from stop2 is done by asserting either of the wake-up pins:  $\overline{\text{RESET}}$  or IRQ, or by an RTI interrupt. IRQ is always an active low input when the MCU is in stop2, regardless of how it was configured before entering stop2.

### NOTE

Although this IRQ pin is automatically configured as active low input, the pullup associated with the IRQ pin is not automatically enabled. Therefore, if an external pullup is not used, the internal pullup must be enabled by setting IRQPE in IRQSC.

Upon wake-up from stop2 mode, the MCU will start up as from a power-on reset (POR) except pin states remain latched. The CPU will take the reset vector. The system and all peripherals will be in their default reset states and must be initialized.

Aborting a command in this way sets the FACCERR access error flag which must be cleared before starting a new command.

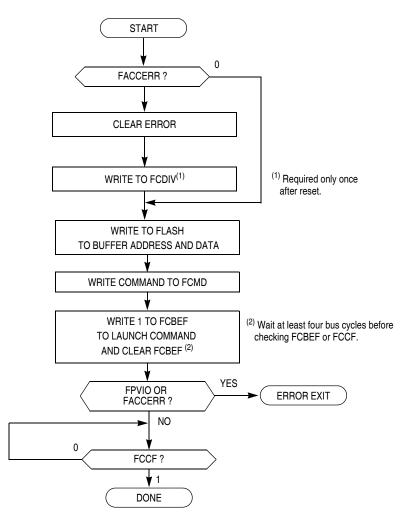

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the flash memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-2 is a flowchart for executing all of the commands except for burst programming. The FCDIV register must be initialized following any reset before using any flash commands.

Figure 4-2. Flash Program and Erase Flowchart

## 4.5.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the flash array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the flash memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst

### 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it was before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

If an event occurs in an enabled interrupt source, an associated read-only status flag will become set. The CPU will not respond until and unless the local interrupt enable is a 1 to enable the interrupt. The I bit in the CCR is 0 to allow interrupts. The global interrupt mask (I bit) in the CCR is initially set after reset which masks (prevents) all maskable interrupt sources. The user program initializes the stack pointer and performs other system setup before clearing the I bit to allow the CPU to respond to interrupts.

When the CPU receives a qualified interrupt request, it completes the current instruction before responding to the interrupt. The interrupt sequence obeys the same cycle-by-cycle sequence as the SWI instruction and consists of:

- Saving the CPU registers on the stack

- Setting the I bit in the CCR to mask further interrupts

- Fetching the interrupt vector for the highest-priority interrupt that is currently pending

- Filling the instruction queue with the first three bytes of program information starting from the address fetched from the interrupt vector locations

While the CPU is responding to the interrupt, the I bit is automatically set to avoid the possibility of another interrupt interrupting the ISR itself (this is called nesting of interrupts). Normally, the I bit is restored to 0 when the CCR is restored from the value stacked on entry to the ISR. In rare cases, the I bit can be cleared inside an ISR (after clearing the status flag that generated the interrupt) so that other interrupts can be serviced without waiting for the first service routine to finish. This practice is not recommended for anyone other than the most experienced programmers because it can lead to subtle program errors that are difficult to debug.

The interrupt service routine ends with a return-from-interrupt (RTI) instruction which restores the CCR, A, X, and PC registers to their pre-interrupt values by reading the previously saved information off the stack.

### NOTE

For compatibility with M68HC08 devices, the H register is not automatically saved and restored. It is good programming practice to push H onto the stack at the start of the interrupt service routine (ISR) and restore it immediately before the RTI that is used to return from the ISR.

When two or more interrupts are pending when the I bit is cleared, the highest priority source is serviced first (see Table 5-2).

Chapter 5 Resets, Interrupts, and General System Control

| Vector<br>Priority | Vector<br>Number    | Address<br>(High:Low)                 | Vector Name                                         | Module            | Source                                                              | Enable                                | Description                                                                                                 |

|--------------------|---------------------|---------------------------------------|-----------------------------------------------------|-------------------|---------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Lower              | 31<br>through<br>24 | 0xFFC0:FFC1<br>through<br>0xFFCE:FFCF | Unused Vector Space<br>(available for user program) |                   |                                                                     |                                       |                                                                                                             |

|                    | 23                  | 0xFFD0:FFD1                           | Vrti                                                | System<br>control | RTIF                                                                | RTIE                                  | Real-time interrupt                                                                                         |

|                    | 22                  | 0xFFD2:FFD3                           | —                                                   |                   | —                                                                   |                                       | —                                                                                                           |

|                    | 21                  | 0xFFD4:FFD5                           | —                                                   | _                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 20                  | 0xFFD6:FFD7                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 19                  | 0xFFD8:FFD9                           | Vadc1                                               | ADC1              | COCO                                                                | AIEN                                  | ADC1                                                                                                        |

|                    | 18                  | 0xFFDA:FFDB                           | Vkeyboard1                                          | KBI1              | KBF                                                                 | KBIE                                  | Keyboard pins                                                                                               |

|                    | 17                  | 0xFFDC:FFDD                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 16                  | 0xFFDE:FFDF                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 15                  | 0xFFE0:FFE1                           | —                                                   | _                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 14                  | 0xFFE2:FFE3                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 13                  | 0xFFE4:FFE5                           | —                                                   | _                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 12                  | 0xFFE6:FFE7                           | —                                                   | _                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 11                  | 0xFFE8:FFE9                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 10                  | 0xFFEA:FFEB                           | Vtpm2ovf                                            | TPM2              | TOF                                                                 | TOIE                                  | TPM2 overflow                                                                                               |

|                    | 9                   | 0xFFEC:FFED                           | —                                                   |                   | —                                                                   | _                                     | —                                                                                                           |

|                    | 8                   | 0xFFEE:FFEF                           | Vtpm2ch0                                            | TPM2              | CH0F                                                                | CH0IE                                 | TPM2 channel 0                                                                                              |

|                    | 7                   | 0xFFF0:FFF1                           | Vtpm1ovf                                            | TPM1              | TOF                                                                 | TOIE                                  | TPM1 overflow                                                                                               |

|                    | 6                   | 0xFFF2:FFF3                           | Vtpm1ch1                                            | TPM1              | CH1F                                                                | CH1IE                                 | TPM1 channel 1                                                                                              |

|                    | 5                   | 0xFFF4:FFF5                           | Vtpm1ch0                                            | TPM1              | CH0F                                                                | CH0IE                                 | TPM1 channel 0                                                                                              |

|                    | 4                   | 0xFFF6:FFF7                           | —                                                   | —                 | —                                                                   | _                                     | —                                                                                                           |

|                    | 3                   | 0xFFF8:FFF9                           | Virq                                                | IRQ               | IRRQF                                                               | IRQIE                                 | IRQ pin                                                                                                     |

|                    | 2                   | 0xFFFA:FFFB                           | Vlvd                                                | System control    | LVDF                                                                | LVDIE                                 | Low voltage detect                                                                                          |

|                    | 1                   | 0xFFFC:FFFD                           | Vswi                                                | CPU               | SWI<br>Instruction                                                  | _                                     | Software interrupt                                                                                          |

| ▼<br>Higher        | 0                   | 0xFFFE:FFFF                           | Vreset                                              | System<br>control | COP<br>LVD<br>RESET pin<br>Illegal opcode<br>Illegal address<br>POR | COPE<br>LVDRE<br>RSTPE<br>—<br>—<br>— | Watchdog timer<br>Low-voltage detect<br>External pin<br>Illegal opcode<br>Illegal address<br>power-on-reset |

### Table 5-2. Vector Summary

# 5.6 Low-Voltage Detect (LVD) System

The MC9S08QD4 series includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and an LVD circuit with a user selectable trip voltage, either high ( $V_{LVDH}$ ) or low ( $V_{LVDL}$ ). The LVD circuit is enabled when LVDE in SPMSC1 is high and the trip voltage is selected by LVDV in SPMSC2. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop1 or stop2, and the current consumption in stop3 with the LVD enabled will be greater.

- In stop1 mode, all internal registers including parallel I/O control and data registers are powered off. Each of the pins assumes its default reset state (output buffer and internal pullup disabled). Upon exit from stop1, all pins must be re-configured the same as if the MCU had been reset.

- Stop2 mode is a partial power-down mode, whereby latches maintain the pin state as before the STOP instruction was executed. CPU register status and the state of I/O registers must be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user must examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, I/O data previously stored in RAM, before the STOP instruction was executed, peripherals previously enabled will require being initialized and restored to their pre-stop condition. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access of pins is now permitted again in the user's application program.

- In stop3 mode, all pin states are maintained because internal logic stays powered up. Upon recovery, all pin functions are the same as before entering stop3.

# 6.4 Parallel I/O Registers

## 6.4.1 Port A Registers

This section provides information about the registers associated with the parallel I/O ports.

Refer to tables in Chapter 4, "Memory Map and Register Definition," for the absolute address assignments for all parallel I/O. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

## 6.4.1.1 Port A Data (PTAD)

|        | 7 | 6 | 5                  | 4                  | 3      | 2     | 1     | 0     |

|--------|---|---|--------------------|--------------------|--------|-------|-------|-------|

| R      | 0 | 0 | PTAD5 <sup>1</sup> | PTAD4 <sup>2</sup> | PTAD3  | PTAD2 | PTAD1 | PTAD0 |

| w      |   |   | T IAD3             |                    | T IADO |       |       | TIADU |

| Reset: | 0 | 0 | 0                  | 0                  | 0      | 0     | 0     | 0     |

<sup>1</sup> Reads of bit PTAD5 always return the pin value of PTA5, regardless of the value stored in bit PTADD5.

<sup>2</sup> Reads of bit PTAD4 always return the contents of PTAD4, regardless of the value stored in bit PTADD4.

Figure 6-2. Port A Data Register (PTAD)

Chapter 6 Parallel Input/Output Control

### 6.4.2.3 Port A Drive Strength Select (PTADS)

An output pin can be selected to have high output drive strength by setting the corresponding bit in the drive strength select register (PTADSn). When high drive is selected a pin is capable of sourcing and sinking greater current. Even though every I/O pin can be selected as high drive, the user must ensure that the total current source and sink limits for the chip are not exceeded. Drive strength selection is intended to affect the DC behavior of I/O pins. However, the AC behavior is also affected. High drive allows a pin to drive a greater load with the same switching speed as a low drive enabled pin into a smaller load. Because of this the EMC emissions may be affected by enabling pins as high drive.

### 6.4.2.4 Port A Drive Strength Select (PTADS)

<sup>1</sup> PTADS5 has no effect on the input-only PTA5 pin.

### Figure 6-6. Drive Strength Selection for Port A Register (PTADS)

### Table 6-5. PTADS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0<br>PTADS[5:0] | <ul> <li>Output Drive Strength Selection for Port A Bits — Each of these control bits selects between low and high output drive for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port A bit n.</li> <li>1 High output drive strength selected for port A bit n.</li> </ul> |

### 7.3.6.7 SP-Relative, 16-Bit Offset (SP2)

This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus a 16-bit offset included in the instruction as the address of the operand needed to complete the instruction.

# 7.4 Special Operations

The CPU performs a few special operations that are similar to instructions but do not have opcodes like other CPU instructions. In addition, a few instructions such as STOP and WAIT directly affect other MCU circuitry. This section provides additional information about these operations.

## 7.4.1 Reset Sequence

Reset can be caused by a power-on-reset (POR) event, internal conditions such as the COP (computer operating properly) watchdog, or by assertion of an external active-low reset pin. When a reset event occurs, the CPU immediately stops whatever it is doing (the MCU does not wait for an instruction boundary before responding to a reset event). For a more detailed discussion about how the MCU recognizes resets and determines the source, refer to the Resets, Interrupts, and System Configuration chapter.

The reset event is considered concluded when the sequence to determine whether the reset came from an internal source is done and when the reset pin is no longer asserted. At the conclusion of a reset event, the CPU performs a 6-cycle sequence to fetch the reset vector from 0xFFFE and 0xFFFF and to fill the instruction queue in preparation for execution of the first program instruction.

## 7.4.2 Interrupt Sequence

When an interrupt is requested, the CPU completes the current instruction before responding to the interrupt. At this point, the program counter is pointing at the start of the next instruction, which is where the CPU should return after servicing the interrupt. The CPU responds to an interrupt by performing the same sequence of operations as for a software interrupt (SWI) instruction, except the address used for the vector fetch is determined by the highest priority interrupt that is pending when the interrupt sequence started.

The CPU sequence for an interrupt is:

- 1. Store the contents of PCL, PCH, X, A, and CCR on the stack, in that order.

- 2. Set the I bit in the CCR.

- 3. Fetch the high-order half of the interrupt vector.

- 4. Fetch the low-order half of the interrupt vector.

- 5. Delay for one free bus cycle.

- 6. Fetch three bytes of program information starting at the address indicated by the interrupt vector to fill the instruction queue in preparation for execution of the first instruction in the interrupt service routine.

After the CCR contents are pushed onto the stack, the I bit in the CCR is set to prevent other interrupts while in the interrupt service routine. Although it is possible to clear the I bit with an instruction in the

## 7.4.5 **BGND Instruction**

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

are too fast, then the clock must be divided to the appropriate frequency. This divider is specified by the ADIV bits and can be divide-by 1, 2, 4, or 8.

## 8.4.2 Input Select and Pin Control

The pin control registers (APCTL3, APCTL2, and APCTL1) are used to disable the I/O port control of the pins used as analog inputs. When a pin control register bit is set, the following conditions are forced for the associated MCU pin:

- The output buffer is forced to its high impedance state.

- The input buffer is disabled. A read of the I/O port returns a zero for any pin with its input buffer disabled.

- The pullup is disabled.

### 8.4.3 Hardware Trigger

The ADC module has a selectable asynchronous hardware conversion trigger, ADHWT, that is enabled when the ADTRG bit is set. This source is not available on all MCUs. Consult the module introduction for information on the ADHWT source specific to this MCU.

When ADHWT source is available and hardware trigger is enabled (ADTRG=1), a conversion is initiated on the rising edge of ADHWT. If a conversion is in progress when a rising edge occurs, the rising edge is ignored. In continuous convert configuration, only the initial rising edge to launch continuous conversions is observed. The hardware trigger function operates in conjunction with any of the conversion modes and configurations.

## 8.4.4 Conversion Control

Conversions can be performed in either 10-bit mode or 8-bit mode as determined by the MODE bits. Conversions can be initiated by either a software or hardware trigger. In addition, the ADC module can be configured for low power operation, long sample time, continuous conversion, and automatic compare of the conversion result to a software determined compare value.

### 8.4.4.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADCSC1 (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger (ADHWT) event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADCSC1 is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

#### Analog-to-Digital Converter (S08ADC10V1)

- 2. Update status and control register 2 (ADCSC2) to select the conversion trigger (hardware or software) and compare function options, if enabled.

- 3. Update status and control register 1 (ADCSC1) to select whether conversions will be continuous or completed only once, and to enable or disable conversion complete interrupts. The input channel on which conversions will be performed is also selected here.

### 8.5.1.2 Pseudo — Code Example

In this example, the ADC module will be set up with interrupts enabled to perform a single 10-bit conversion at low power with a long sample time on input channel 1, where the internal ADCK clock will be derived from the bus clock divided by 1.

### ADCCFG = 0x98 (%10011000)

| Bit 7   | ADLPC  | 1  | Configures for low power (lowers maximum clock speed) |

|---------|--------|----|-------------------------------------------------------|

| Bit 6:5 | ADIV   | 00 | Sets the ADCK to the input clock $\div$ 1             |

| Bit 4   | ADLSMP | 1  | Configures for long sample time                       |

| Bit 3:2 | MODE   | 10 | Sets mode at 10-bit conversions                       |

| Bit 1:0 | ADICLK | 00 | Selects bus clock as input clock source               |

|         |        |    |                                                       |

### ADCSC2 = 0x00 (%00000000)

| Bit 7   | ADACT | 0  | Flag indicates if a conversion is in progress            |

|---------|-------|----|----------------------------------------------------------|

| Bit 6   | ADTRG | 0  | Software trigger selected                                |

| Bit 5   | ACFE  | 0  | Compare function disabled                                |

| Bit 4   | ACFGT | 0  | Not used in this example                                 |

| Bit 3:2 |       | 00 | Unimplemented or reserved, always reads zero             |

| Bit 1:0 |       | 00 | Reserved for Freescale's internal use; always write zero |

|         |       |    |                                                          |

### ADCSC1 = 0x41 (%01000001)

| Bit 7   | COCO | 0     | Read-only flag which is set when a conversion completes |

|---------|------|-------|---------------------------------------------------------|

| Bit 6   | AIEN | 1     | Conversion complete interrupt enabled                   |

| Bit 5   | ADCO | 0     | One conversion only (continuous conversions disabled)   |

| Bit 4:0 | ADCH | 00001 | Input channel 1 selected as ADC input channel           |

### ADCRH/L = 0xxx

Holds results of conversion. Read high byte (ADCRH) before low byte (ADCRL) so that conversion data cannot be overwritten with data from the next conversion.

### ADCCVH/L = 0xxx

Holds compare value when compare function enabled

### APCTL1=0x02

AD1 pin I/O control disabled. All other AD pins remain general purpose I/O pins

### APCTL2=0x00

All other AD pins remain general purpose I/O pins

converter yields the lower code (and vice-versa). However, even very small amounts of system noise can cause the converter to be indeterminate (between two codes) for a range of input voltages around the transition voltage. This range is normally around  $\pm 1/2$  LSB and will increase with noise. This error may be reduced by repeatedly sampling the input and averaging the result. Additionally the techniques discussed in Section 8.6.2.3, "Noise-Induced Errors," will reduce this error.

Non-monotonicity is defined as when, except for code jitter, the converter converts to a lower code for a higher input voltage. Missing codes are those values which are never converted for any input value.

In 8-bit or 10-bit mode, the ADC is guaranteed to be monotonic and to have no missing codes.

# 9.2 External Signal Description

There are no ICS signals that connect off chip.

## 9.3 Register Definition

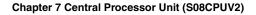

## 9.3.1 ICS Control Register 1 (ICSC1)

Figure 9-3. ICS Control Register 1 (ICSC1)

### Table 9-1. ICS Control Register 1 Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>CLKS   | <ul> <li>Clock Source Select — Selects the clock source that controls the bus frequency. The actual bus frequency depends on the value of the BDIV bits.</li> <li>O Output of FLL is selected.</li> <li>O1 Internal reference clock is selected.</li> <li>Internal reference clock is selected.</li> <li>External reference clock is selected.</li> <li>Reserved, defaults to 00.</li> </ul>                                                                                                                                                                                                                                                                                                                     |

| 5:3<br>RDIV   | <b>Reference Divider</b> — Selects the amount to divide down the FLL reference clock selected by the IREFS bits.         Resulting frequency must be in the range 31.25 kHz to 39.0625 kHz.         000       Encoding 0 — Divides reference clock by 1 (reset default)         001       Encoding 1 — Divides reference clock by 2         010       Encoding 2 — Divides reference clock by 4         011       Encoding 3 — Divides reference clock by 8         100       Encoding 4 — Divides reference clock by 16         101       Encoding 5 — Divides reference clock by 32         110       Encoding 6 — Divides reference clock by 64         111       Encoding 7 — Divides reference clock by 128 |

| 2<br>IREFS    | Internal Reference Select — The IREFS bit selects the reference clock source for the FLL.         1 Internal reference clock selected         0 External reference clock selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1<br>IRCLKEN  | Internal Reference Clock Enable — The IRCLKEN bit enables the internal reference clock for use as ICSIRCLK.<br>1 ICSIRCLK active<br>0 ICSIRCLK inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0<br>IREFSTEN | <ul> <li>Internal Reference Stop Enable — The IREFSTEN bit controls whether or not the internal reference clock remains enabled when the ICS enters stop mode.</li> <li>1 Internal reference clock stays enabled in stop if IRCLKEN is set or if ICS is in FEI, FBI, or FBILP mode before entering stop</li> <li>0 Internal reference clock is disabled in stop</li> </ul>                                                                                                                                                                                                                                                                                                                                       |

Internal Clock Source (S08ICSV1)

# 9.4 Functional Description

## 9.4.1 Operational Modes

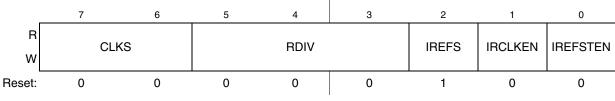

Figure 9-7. Clock Switching Modes

The seven states of the ICS are shown as a state diagram and are described below. The arrows indicate the allowed movements between the states.

### 9.4.1.1 FLL Engaged Internal (FEI)

FLL engaged internal (FEI) is the default mode of operation and is entered when all the following conditions occur:

- CLKS bits are written to 00

- IREFS bit is written to 1

- RDIV bits are written to divide trimmed reference clock to be within the range of 31.25 kHz to 39.0625 kHz.

In FLL engaged internal mode, the ICSOUT clock is derived from the FLL clock, which is controlled by the internal reference clock. The FLL loop will lock the frequency to 512 times the filter frequency, as selected by the RDIV bits. The ICSLCLK is available for BDC communications, and the internal reference clock is enabled.

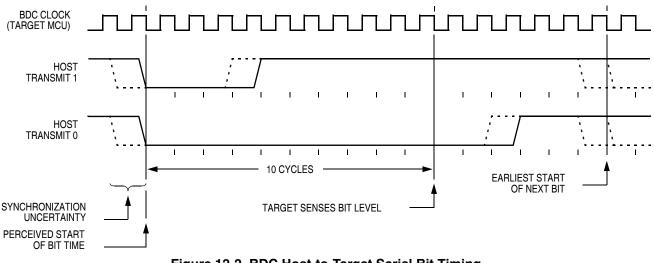

KBISC provided all enabled keyboard inputs are at their deasserted levels. KBF will remain set if any enabled KBI pin is asserted while attempting to clear by writing a 1 to KBACK.

## 10.4.3 KBI Pullup/Pulldown Resistors

The KBI pins can be configured to use an internal pullup/pulldown resistor using the associated I/O port pullup enable register. If an internal resistor is enabled, the KBIES register is used to select whether the resistor is a pullup (KBEDGn = 0) or a pulldown (KBEDGn = 1).

## 10.4.4 KBI Initialization

When a keyboard interrupt pin is first enabled it is possible to get a false keyboard interrupt flag. To prevent a false interrupt request during keyboard initialization, the user must do the following:

- 1. Mask keyboard interrupts by clearing KBIE in KBISC.

- 2. Enable the KBI polarity by setting the appropriate KBEDGn bits in KBIES.

- 3. If using internal pullup/pulldown device, configure the associated pullup enable bits in PTxPE.

- 4. Enable the KBI pins by setting the appropriate KBIPEn bits in KBIPE.

- 5. Write to KBACK in KBISC to clear any false interrupts.

- 6. Set KBIE in KBISC to enable interrupts.

Timer/Pulse-Width Modulator (S08TPMV2)

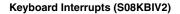

## 11.4.3 Center-Aligned PWM Mode

This type of PWM output uses the up-/down-counting mode of the timer counter (CPWMS = 1). The output compare value in TPMxCnVH:TPMxCnVL determines the pulse width (duty cycle) of the PWM signal and the period is determined by the value in TPMxMODH:TPMxMODL.

TPMxMODH:TPMxMODL must be kept in the range of 0x0001 to 0x7FFF because values outside this range can produce ambiguous results. ELSnA will determine the polarity of the CPWM output.

#### period = 2 x (TPMxMODH:TPMxMODL); for TPMxMODH:TPMxMODL = 0x0001–0x7FFF Eqn. 11-2

If the channel value register TPMxCnVH:TPMxCnVL is zero or negative (bit 15 set), the duty cycle will be 0%. If TPMxCnVH:TPMxCnVL is a positive value (bit 15 clear) and is greater than the (nonzero) modulus setting, the duty cycle will be 100% because the duty cycle compare will never occur. This implies the usable range of periods set by the modulus register is 0x0001 through 0x7FFE (0x7FFF if generation of 100% duty cycle is not necessary). This is not a significant limitation because the resulting period is much longer than required for normal applications.

TPMxMODH:TPMxMODL = 0x0000 is a special case that must not be used with center-aligned PWM mode. When CPWMS = 0, this case corresponds to the counter running free from 0x0000 through 0xFFFF, but when CPWMS = 1 the counter needs a valid match to the modulus register somewhere other than at 0x0000 in order to change directions from up-counting to down-counting.

Figure 11-12 shows the output compare value in the TPM channel registers (multiplied by 2), which determines the pulse width (duty cycle) of the CPWM signal. If ELSnA = 0, the compare match while counting up forces the CPWM output signal low and a compare match while counting down forces the output high. The counter counts up until it reaches the modulo setting in TPMxMODH:TPMxMODL, then counts down until it reaches zero. This sets the period equal to two times TPMxMODH:TPMxMODL.

Figure 11-12. CPWM Period and Pulse Width (ELSnA = 0)

Center-aligned PWM outputs typically produce less noise than edge-aligned PWMs because fewer I/O pin transitions are lined up at the same system clock edge. This type of PWM is also required for some types of motor drives.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers, TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers. Values are

#### Development Support

when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

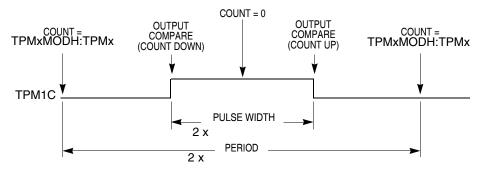

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.

Figure 12-2 shows an external host transmitting a logic 1 or 0 to the BKGD pin of a target HCS08 MCU. The host is asynchronous to the target so there is a 0-to-1 cycle delay from the host-generated falling edge to where the target perceives the beginning of the bit time. Ten target BDC clock cycles later, the target senses the bit level on the BKGD pin. Typically, the host actively drives the pseudo-open-drain BKGD pin during host-to-target transmissions to speed up rising edges. Because the target does not drive the BKGD pin during the host-to-target transmission period, there is no need to treat the line as an open-drain signal during this period.

Figure 12-2. BDC Host-to-Target Serial Bit Timing

Figure 12-3 shows the host receiving a logic 1 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the perceived start of the bit time in the target MCU. The host holds the BKGD pin low long enough for the target to recognize it (at least two target BDC cycles). The host must release the low drive before the target MCU drives a brief active-high speedup pulse seven cycles after the perceived start of the bit time. The host must sample the bit level about 10 cycles after it started the bit time.

#### Appendix A Electrical Characteristics

<sup>7</sup> Power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

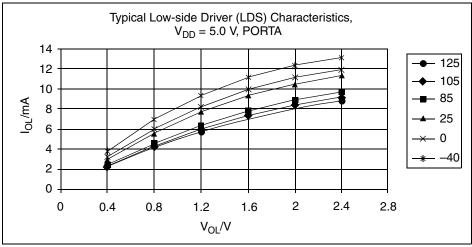

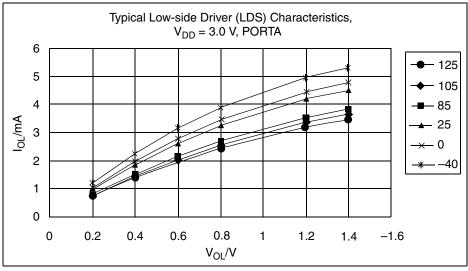

Figure A-1. Typical Low-Side Driver (Sink) Characteristics Low Drive (PTxDSn = 0), V<sub>DD</sub> = 5.0V, V<sub>OL</sub> vs. I<sub>OL</sub>

Figure A-2. Typical Low-Side Driver (Sink) Characteristics Low Drive (PTxDSn = 0),  $V_{DD}$  = 3.0 V,  $V_{OL}$  vs.  $I_{OL}$

Appendix A Electrical Characteristics