Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 4                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 4x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                          |

| Supplier Device Package    | 8-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08qd4j1cscr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

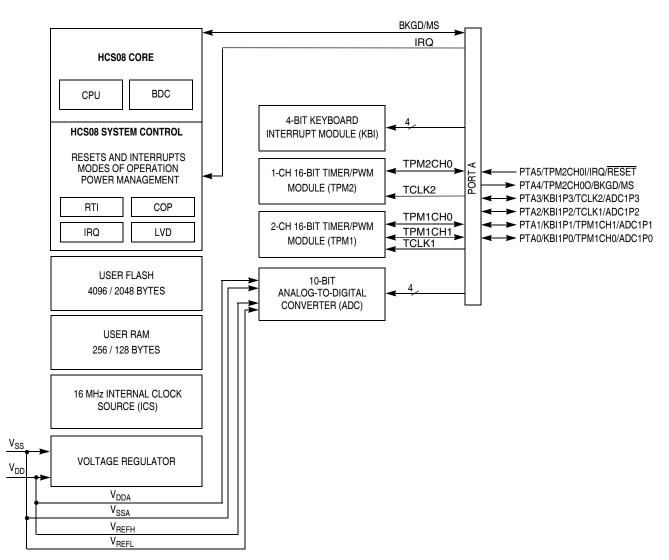

## 1.2.1 MCU Block Diagram

#### NOTES:

- <sup>1</sup> Port pins are software configurable with pullup device if input port.

- <sup>2</sup> Port pins are software configurable for output drive strength.

- <sup>3</sup> Port pins are software configurable for output slew rate control.

- <sup>4</sup> IRQ contains a software configurable (IRQPDD) pullup/pulldown device if PTA5 enabled as IRQ pin function (IRQPE = 1).

- <sup>5</sup>  $\overline{\text{RESET}}$  contains integrated pullup device if PTA5 enabled as reset pin function (RSTPE = 1).

- <sup>6</sup> PTA5 does not contain a clamp diode to  $V_{DD}$  and must not be driven above  $V_{DD}$ . The voltage measured on this pin when internal pullup is enabled may be as low as  $V_{DD} 0.7$  V. The internal gates connected to this pin are pulled to  $V_{DD}$ .

- <sup>7</sup> PTA4 contains integrated pullup device if BKGD enabled (BKGDPE = 1).

- <sup>8</sup> When pin functions as KBI (KBIPEn = 1) and associated pin is configured to enable the pullup device, KBEDGn can be used to reconfigure the pullup as a pulldown device.

#### Figure 1-1. MC9S08QD4 Series Block Diagram

Table 1-2 provides the functional versions of the on-chip modules.

#### MC9S08QD4 Series MCU Data Sheet, Rev. 6

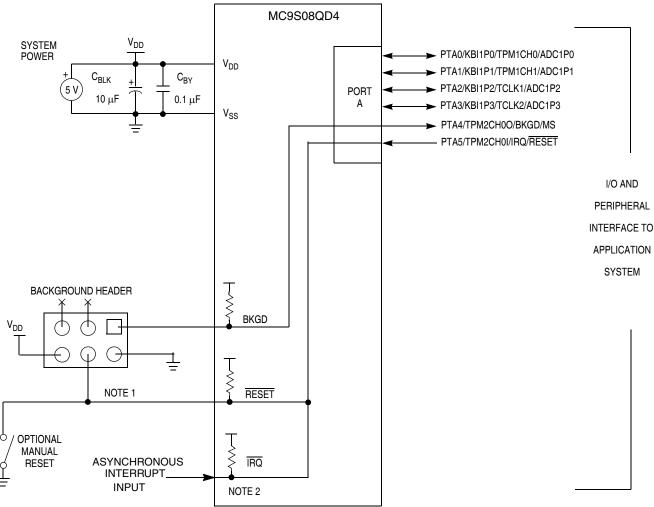

NOTES:

- 1. RESET pin can only be used to reset into user mode, you can not enter BDM using RESET pin. BDM can be entered by holding MS low during POR or writing a 1 to BDFR in SBDFR with MS low after issuing BDM command.

- 2. IRQ has optional internal pullup/pulldown device

#### Figure 2-2. Basic System Connections

#### 2.2.1 **Power**

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry, the ADC module, and to an internal voltage regulator. The internal voltage regulator provides regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins: a bulk electrolytic capacitor, such as a  $10\mu$ F tantalum capacitor, to provide bulk charge storage for the overall system, and a bypass capacitor, such as a  $0.1\mu$ F ceramic capacitor, located as near to the MCU power pins as practical to suppress high-frequency noise.

# Chapter 3 Modes of Operation

# 3.1 Introduction

The operating modes of the MC9S08QD4 series are described in this chapter. Entry into each mode, exit from each mode, and functionality while in each of the modes are described.

## 3.2 Features

- Active background mode for code development

- Wait mode:

- CPU shuts down to conserve power

- System clocks running

- Full voltage regulation maintained

- Stop modes:

- CPU and bus clocks stopped

- Stop2 Partial power down of internal circuits, RAM contents retained

- Stop3 All internal circuits powered for fast recovery

## 3.3 Run Mode

This is the normal operating mode for the MC9S08QD4 series. This mode is selected when the BKGD/MS pin is high at the rising edge of reset. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at 0xFFFE:0xFFFF after reset.

# 3.4 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in the HCS08 core. The BDC provides the means for analyzing MCU operation during software development.

Active background mode is entered in any of five ways:

- When the BKGD/MS pin is low at the rising edge of reset

- When a BACKGROUND command is received through the BKGD pin

- When a BGND instruction is executed

- When encountering a BDC breakpoint

MC9S08QD4 Series MCU Data Sheet, Rev. 6

Chapter 4 Memory Map and Register Definition

| Address            | Register Name                                                                           | Bit 7                 | 6      | 5    | 4    | 3     | 2    | 1     | Bit 0 |

|--------------------|-----------------------------------------------------------------------------------------|-----------------------|--------|------|------|-------|------|-------|-------|

| 0xFFAA –<br>0xFFAC | Reserved                                                                                | _                     | _      | _    | _    | _     | _    | _     | _     |

| 0xFFAD             | Reserved for<br>ADCRL of AD26<br>value during ICS<br>trim                               | ADR7                  | ADR6   | ADR5 | ADR4 | ADR3  | ADR2 | ADR1  | ADR0  |

| 0xFFAE             | Reserved for<br>ADCRH of AD26<br>value during ICS<br>trim and ICS Trim<br>value "FTRIM" | ADR9                  | ADR8   | _    | –    | –     | Ι    | Ι     | FTRIM |

| 0xFFAF             | Reserved for<br>ICS Trim value<br>"TRIM"                                                | TRIM                  |        |      |      |       |      |       |       |

| 0xFFB0 –<br>0xFFB7 | NVBACKKEY                                                                               | 8-Byte Comparison Key |        |      |      |       |      |       |       |

| 0xFFB8 –<br>0xFFBC | Reserved                                                                                | _                     | _      | _    | _    | _     | _    | _     | _     |

| 0xFFBD             | NVPROT                                                                                  | FPS F                 |        |      |      | FPDIS |      |       |       |

| 0xFFBE             | Unused                                                                                  | _                     | —      | —    |      | _     |      | _     |       |

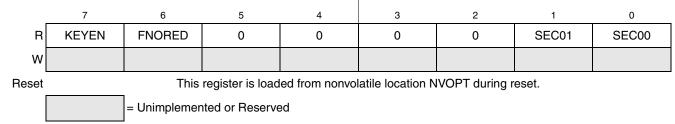

| 0xFFBF             | NVOPT                                                                                   | KEYEN                 | FNORED | 0    | 0    | 0     | 0    | SEC01 | SEC00 |

Table 4-4. Nonvolatile Register Summary

Provided the key enable (KEYEN) bit is 1, the 8-byte comparison key can be used to temporarily disengage memory security. This key mechanism can be accessed only through user code running in secure memory. (A security key cannot be entered directly through background debug commands.) This security key can be disabled completely by programming the KEYEN bit to 0. If the security key is disabled, the only way to disengage security is by mass erasing the flash if needed (normally through the background debug interface) and verifying that flash is blank. To avoid returning to secure mode after the next reset, program the security bits (SEC01:SEC00) to the unsecured state (1:0).

The ICS factory-trimmed value will be stored in 0xFFAE (bit-0) and 0xFFAF. Development tools, such as programmers can trim the ICS and the internal temperature sensor (via the ADC) and store the values in 0xFFAD–0xFFAF.

# 4.4 RAM

The MC9S08QD4 series includes static RAM. The locations in RAM below 0x0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait, stop2, or stop3 mode. At power-on or after wakeup from stop1, the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention ( $V_{RAM}$ ).

Chapter 4 Memory Map and Register Definition

# 4.7.2 Flash Options Register (FOPT and NVOPT)

During reset, the contents of the nonvolatile location NVOPT are copied from flash into FOPT. To change the value in this register, erase and reprogram the NVOPT location in flash memory as usual and then issue a new MCU reset.

#### Figure 4-6. Flash Options Register (FOPT)

#### Table 4-8. FOPT Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>KEYEN       | <ul> <li>Backdoor Key Mechanism Enable — When this bit is 0, the backdoor key mechanism cannot be used to disengage security. The backdoor key mechanism is accessible only from user (secured) firmware. BDM commands cannot be used to write key comparison values that would unlock the backdoor key. For more detailed information about the backdoor key mechanism, refer to Section 4.6, "Security."</li> <li>0 No backdoor key access allowed.</li> <li>1 If user firmware writes an 8-byte value that matches the nonvolatile backdoor key (NVBACKKEY through NVBACKKEY+7 in that order), security is temporarily disengaged until the next MCU reset.</li> </ul> |

| 6<br>FNORED      | <ul> <li>Vector Redirection Disable — When this bit is 1, then vector redirection is disabled.</li> <li>0 Vector redirection enabled.</li> <li>1 Vector redirection disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1:0<br>SEC0[1:0] | Security State Code — This 2-bit field determines the security state of the MCU as shown in Table 4-9. When the MCU is secure, the contents of RAM and flash memory cannot be accessed by instructions from any unsecured source including the background debug interface. SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of flash. For more detailed information about security, refer to Section 4.6, "Security."                                                                                                                                                                                                           |

#### Table 4-9. Security States<sup>1</sup>

| SEC01:SEC00 | Description |

|-------------|-------------|

| 0:0         | secure      |

| 0:1         | secure      |

| 1:0         | unsecured   |

| 1:1         | secure      |

<sup>1</sup> SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of flash.

Chapter 5 Resets, Interrupts, and General System Control

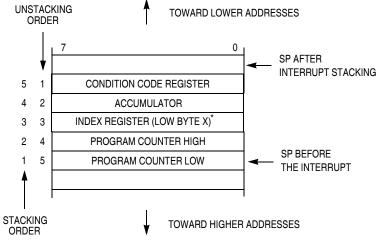

## 5.5.1 Interrupt Stack Frame

Figure 5-1 shows the contents and organization of a stack frame. Before the interrupt, the stack pointer (SP) points at the next available byte location on the stack. The current values of CPU registers are stored on the stack starting with the low-order byte of the program counter (PCL) and ending with the CCR. After stacking, the SP points at the next available location on the stack which is the address that is one less than the address where the CCR was saved. The PC value that is stacked is the address of the instruction in the main program that would have executed next if the interrupt had not occurred.

\* High byte (H) of index register is not automatically stacked.

Figure 5-1. Interrupt Stack Frame

When an RTI instruction is executed, these values are recovered from the stack in reverse order. As part of the RTI sequence, the CPU fills the instruction pipeline by reading three bytes of program information, starting from the PC address recovered from the stack.

The status flag causing the interrupt must be acknowledged (cleared) before returning from the ISR. Typically, the flag is cleared at the beginning of the ISR so that if another interrupt is generated by this same source, it will be registered so it can be serviced after completion of the current ISR.

## 5.5.2 External Interrupt Request (IRQ) Pin

External interrupts are managed by the IRQ status and control register, IRQSC. When the IRQ function is enabled, synchronous logic monitors the pin for edge-only or edge-and-level events. When the MCU is in stop mode and system clocks are shut down, a separate asynchronous path is used so the IRQ (if enabled) can wake the MCU.

#### 5.5.2.1 Pin Configuration Options

The IRQ pin enable (IRQPE) control bit in IRQSC must be 1 in order for the IRQ pin to act as the interrupt request (IRQ) input. As an IRQ input, the user can choose the polarity of edges or levels detected (IRQEDG), whether the pin detects edges-only or edges and levels (IRQMOD), and whether an event causes an interrupt or only sets the IRQF flag which can be polled by software.

Chapter 5 Resets, Interrupts, and General System Control

| RTIS2:RTIS1:RTIS0 | Using Internal 1 kHz Clock Source <sup>1 2</sup> | Using 32 kHz ICS Clock Source<br>Period = t <sub>ext</sub> <sup>3</sup> |

|-------------------|--------------------------------------------------|-------------------------------------------------------------------------|

| 0:0:0             | Disable RTI Disable RTI                          |                                                                         |

| 0:0:1             | 8 ms t <sub>ext</sub> × 256                      |                                                                         |

| 0:1:0             | 32 ms t <sub>ext</sub> × 1024                    |                                                                         |

| 0:1:1             | 64 ms t <sub>ext</sub> × 2048                    |                                                                         |

| 1:0:0             | 128 ms t <sub>ext</sub> × 4096                   |                                                                         |

| 1:0:1             | 256 ms                                           | t <sub>ext</sub> × 8192                                                 |

| 1:1:0             | 1:1:0 512 ms t <sub>ext</sub> × 16384            |                                                                         |

| 1:1:1             | 1.024 s                                          | $t_{ext} 	imes 32768$                                                   |

#### Table 5-11. Real-Time Interrupt Period

<sup>1</sup> Values are shown in this column based on t<sub>RTI</sub> = 1 ms. See t<sub>RTI</sub> in the Section A.8.1, "Control Timing," for the tolerance of this value.

<sup>2</sup> The initial RTI timeout period will be up to one 1 kHz clock period less than the time specified.

$^{3}$  t<sub>ext</sub> is the period of the 32 kHz ICS frequency.

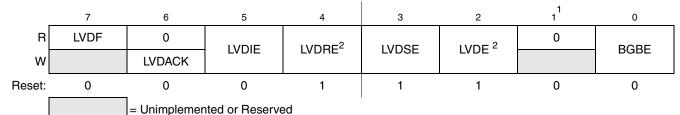

# 5.8.8 System Power Management Status and Control 1 Register (SPMSC1)

This high-page register contains status and control bits to support the low voltage detect function, and to enable the bandgap voltage reference for use by the ADC module. To configure the low voltage detect trip voltage, see Table 5-13 for the LVDV bit description in SPMSC2.

<sup>1</sup> Bit 1 is a reserved bit that must always be written to 0.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Figure 5-10. System Power Management Status and Control 1 Register (SPMSC1)

#### Table 5-12. SPMSC1 Register Field Descriptions

| Field       | Description                                                                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVDF   | Low-Voltage Detect Flag — Provided LVDE = 1, this read-only status bit indicates a low-voltage detect event.                                                    |

| 6<br>LVDACK | <b>Low-Voltage Detect Acknowledge</b> — This write-only bit is used to acknowledge low voltage detection errors (write 1 to clear LVDF). Reads always return 0. |

# 7.2.3 Stack Pointer (SP)

This 16-bit address pointer register points at the next available location on the automatic last-in-first-out (LIFO) stack. The stack may be located anywhere in the 64-Kbyte address space that has RAM and can be any size up to the amount of available RAM. The stack is used to automatically save the return address for subroutine calls, the return address and CPU registers during interrupts, and for local variables. The AIS (add immediate to stack pointer) instruction adds an 8-bit signed immediate value to SP. This is most often used to allocate or deallocate space for local variables on the stack.

SP is forced to 0x00FF at reset for compatibility with the earlier M68HC05 Family. HCS08 programs normally change the value in SP to the address of the last location (highest address) in on-chip RAM during reset initialization to free up direct page RAM (from the end of the on-chip registers to 0x00FF).

The RSP (reset stack pointer) instruction was included for compatibility with the M68HC05 Family and is seldom used in new HCS08 programs because it only affects the low-order half of the stack pointer.

# 7.2.4 Program Counter (PC)

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

During normal program execution, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, interrupt, and return operations load the program counter with an address other than that of the next sequential location. This is called a change-of-flow.

During reset, the program counter is loaded with the reset vector that is located at 0xFFFE and 0xFFFF. The vector stored there is the address of the first instruction that will be executed after exiting the reset state.

## 7.2.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask (I) and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code bits in general terms. For a more detailed explanation of how each instruction sets the CCR bits, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMv1.

| Source<br>Form                                                                                                  | Operation                                                                                                                                 | Address<br>Mode                                     | Object Code                                                                      | es                              | Cyc-by-Cyc<br>Details                            |     | Affect<br>n CCR |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|-----|-----------------|

|                                                                                                                 |                                                                                                                                           | Add<br>Mod                                          |                                                                                  | Cycles                          |                                                  | VH  | INZC            |

| MOV opr8a,opr8a<br>MOV opr8a,X+<br>MOV #opr8i,opr8a<br>MOV ,X+,opr8a                                            | Move<br>(M) <sub>destination</sub> $\leftarrow$ (M) <sub>source</sub><br>In IX+/DIR and DIR/IX+ Modes,<br>H:X $\leftarrow$ (H:X) + \$0001 | DIR/DIR<br>DIR/IX+<br>IMM/DIR<br>IX+/DIR            | 4E dd dd<br>5E dd<br>6E ii dd<br>7E dd                                           | 5<br>5<br>4<br>5                | rpwpp<br>rfwpp<br>pwpp<br>rfwpp                  | 0 — | - ↓ ↓ -         |

| MUL                                                                                                             | Unsigned multiply<br>X:A $\leftarrow$ (X) × (A)                                                                                           | INH                                                 | 42                                                                               | 5                               | ffffp                                            | - 0 | 0               |

| NEG opr8a<br>NEGA<br>NEGX<br>NEG oprx8,X<br>NEG ,X<br>NEG oprx8,SP                                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                      | IX                                                  | 30 dd<br>40<br>50<br>60 ff<br>70<br>9E 60 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp            | \$  | - ↓ ↓ ↓         |

| NOP                                                                                                             | No Operation — Uses 1 Bus Cycle                                                                                                           | INH                                                 | 9D                                                                               | 1                               | p                                                |     |                 |

| NSA                                                                                                             | Nibble Swap Accumulator $A \leftarrow (A[3:0]:A[7:4])$                                                                                    | INH                                                 | 62                                                                               | 1                               | q                                                |     |                 |

| ORA #opr8i<br>ORA opr8a<br>ORA opr16a<br>ORA oprx16,X<br>ORA oprx8,X<br>ORA ,X<br>ORA oprx16,SP<br>ORA oprx8,SP | Inclusive OR Accumulator and Memory $A \leftarrow (A) \mid (M)$                                                                           | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AA ii<br>BA dd<br>CA hh ll<br>DA ee ff<br>EA ff<br>FA<br>9E DA ee ff<br>9E EA ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | 0 — | -\$\$-          |

| PSHA                                                                                                            | Push Accumulator onto Stack<br>Push (A); SP $\leftarrow$ (SP) – \$0001                                                                    | INH                                                 | 87                                                                               | 2                               | sp                                               |     |                 |

| PSHH                                                                                                            | Push H (Index Register High) onto Stack<br>Push (H); SP $\leftarrow$ (SP) – \$0001                                                        | INH                                                 | 8B                                                                               | 2                               | sp                                               |     |                 |

| PSHX                                                                                                            | Push X (Index Register Low) onto Stack Push (X); SP $\leftarrow$ (SP) – \$0001                                                            | INH                                                 | 89                                                                               | 2                               | sp                                               |     |                 |

| PULA                                                                                                            | Pull Accumulator from Stack<br>SP $\leftarrow$ (SP + \$0001); Pull (A)                                                                    | INH                                                 | 86                                                                               | 3                               | ufp                                              |     |                 |

| PULH                                                                                                            | Pull H (Index Register High) from Stack SP $\leftarrow$ (SP + \$0001); Pull (H)                                                           | INH                                                 | 8A                                                                               | 3                               | ufp                                              |     |                 |

| PULX                                                                                                            | Pull X (Index Register Low) from Stack $SP \leftarrow (SP + \$0001)$ ; Pull (X)                                                           | INH                                                 | 88                                                                               | 3                               | ufp                                              |     |                 |

| ROL <i>opr8a</i><br>ROLA<br>ROLX<br>ROL <i>oprx8</i> ,X<br>ROL ,X<br>ROL <i>oprx8</i> ,SP                       | Rotate Left through Carry                                                                                                                 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39 dd<br>49<br>59<br>69 ff<br>79<br>9E 69 ff                                     | 5<br>1<br>5<br>4<br>6           | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp            | \$  | - ↓ ↓ ↓         |

| ROR opr8a<br>RORA<br>RORX<br>ROR oprx8,X<br>ROR ,X<br>ROR oprx8,SP                                              | Rotate Right through Carry                                                                                                                | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36 dd<br>46<br>56<br>66 ff<br>76<br>9E 66 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp            | \$  | - ↓ ↓ ↓         |

| Field      | Description                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC1 | <ul> <li>ADC Pin Control 1 — ADPC1 is used to control the pin associated with channel AD1.</li> <li>0 AD1 pin I/O control enabled</li> <li>1 AD1 pin I/O control disabled</li> </ul> |

| 0<br>ADPC0 | <ul> <li>ADC Pin Control 0 — ADPC0 is used to control the pin associated with channel AD0.</li> <li>0 AD0 pin I/O control enabled</li> <li>1 AD0 pin I/O control disabled</li> </ul> |

#### Table 8-9. APCTL1 Register Field Descriptions (continued)

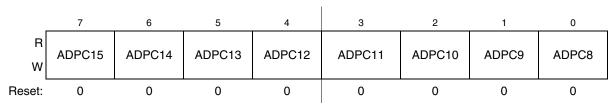

# 8.3.9 Pin Control 2 Register (APCTL2)

APCTL2 is used to control channels 8–15 of the ADC module.

Figure 8-12. Pin Control 2 Register (APCTL2)

#### Table 8-10. APCTL2 Register Field Descriptions

| Field       | Description                                                                                                                                                                               |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>ADPC15 | <ul> <li>ADC Pin Control 15 — ADPC15 is used to control the pin associated with channel AD15.</li> <li>0 AD15 pin I/O control enabled</li> <li>1 AD15 pin I/O control disabled</li> </ul> |  |

| 6<br>ADPC14 | <ul> <li>ADC Pin Control 14 — ADPC14 is used to control the pin associated with channel AD14.</li> <li>0 AD14 pin I/O control enabled</li> <li>1 AD14 pin I/O control disabled</li> </ul> |  |

| 5<br>ADPC13 | <ul> <li>ADC Pin Control 13 — ADPC13 is used to control the pin associated with channel AD13.</li> <li>0 AD13 pin I/O control enabled</li> <li>1 AD13 pin I/O control disabled</li> </ul> |  |

| 4<br>ADPC12 | <ul> <li>ADC Pin Control 12 — ADPC12 is used to control the pin associated with channel AD12.</li> <li>0 AD12 pin I/O control enabled</li> <li>1 AD12 pin I/O control disabled</li> </ul> |  |

| 3<br>ADPC11 | <ul> <li>ADC Pin Control 11 — ADPC11 is used to control the pin associated with channel AD11.</li> <li>0 AD11 pin I/O control enabled</li> <li>1 AD11 pin I/O control disabled</li> </ul> |  |

| 2<br>ADPC10 | <ul> <li>ADC Pin Control 10 — ADPC10 is used to control the pin associated with channel AD10.</li> <li>0 AD10 pin I/O control enabled</li> <li>1 AD10 pin I/O control disabled</li> </ul> |  |

are too fast, then the clock must be divided to the appropriate frequency. This divider is specified by the ADIV bits and can be divide-by 1, 2, 4, or 8.

## 8.4.2 Input Select and Pin Control

The pin control registers (APCTL3, APCTL2, and APCTL1) are used to disable the I/O port control of the pins used as analog inputs. When a pin control register bit is set, the following conditions are forced for the associated MCU pin:

- The output buffer is forced to its high impedance state.

- The input buffer is disabled. A read of the I/O port returns a zero for any pin with its input buffer disabled.

- The pullup is disabled.

#### 8.4.3 Hardware Trigger

The ADC module has a selectable asynchronous hardware conversion trigger, ADHWT, that is enabled when the ADTRG bit is set. This source is not available on all MCUs. Consult the module introduction for information on the ADHWT source specific to this MCU.

When ADHWT source is available and hardware trigger is enabled (ADTRG=1), a conversion is initiated on the rising edge of ADHWT. If a conversion is in progress when a rising edge occurs, the rising edge is ignored. In continuous convert configuration, only the initial rising edge to launch continuous conversions is observed. The hardware trigger function operates in conjunction with any of the conversion modes and configurations.

## 8.4.4 Conversion Control

Conversions can be performed in either 10-bit mode or 8-bit mode as determined by the MODE bits. Conversions can be initiated by either a software or hardware trigger. In addition, the ADC module can be configured for low power operation, long sample time, continuous conversion, and automatic compare of the conversion result to a software determined compare value.

#### 8.4.4.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADCSC1 (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger (ADHWT) event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADCSC1 is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

Internal Clock Source (S08ICSV1)

# 9.4 Functional Description

## 9.4.1 Operational Modes

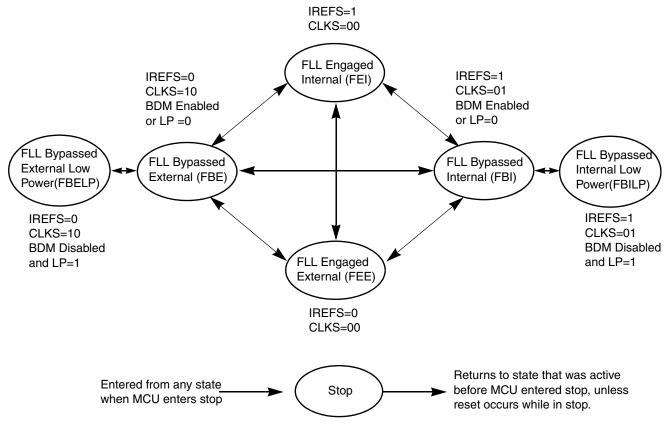

Figure 9-7. Clock Switching Modes

The seven states of the ICS are shown as a state diagram and are described below. The arrows indicate the allowed movements between the states.

#### 9.4.1.1 FLL Engaged Internal (FEI)

FLL engaged internal (FEI) is the default mode of operation and is entered when all the following conditions occur:

- CLKS bits are written to 00

- IREFS bit is written to 1

- RDIV bits are written to divide trimmed reference clock to be within the range of 31.25 kHz to 39.0625 kHz.

In FLL engaged internal mode, the ICSOUT clock is derived from the FLL clock, which is controlled by the internal reference clock. The FLL loop will lock the frequency to 512 times the filter frequency, as selected by the RDIV bits. The ICSLCLK is available for BDC communications, and the internal reference clock is enabled.

#### Internal Clock Source (S08ICSV1)

times the filter frequency, as selected by the RDIV bits, so that the ICSLCLK will be available for BDC communications, and the external reference clock is enabled.

#### 9.4.1.6 FLL Bypassed External Low Power (FBELP)

The FLL bypassed external low power (FBELP) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is not active and LP bit is written to 1.

In FLL bypassed external low power mode, the ICSOUT clock is derived from the external reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications. The external reference clock is enabled.

#### 9.4.1.7 Stop

Stop mode is entered whenever the MCU enters a STOP state. In this mode, all ICS clock signals are static except in the following cases:

ICSIRCLK will be active in stop mode when all the following conditions occur:

- IRCLKEN bit is written to 1

- IREFSTEN bit is written to 1

ICSERCLK will be active in stop mode when all the following conditions occur:

- ERCLKEN bit is written to 1

- EREFSTEN bit is written to 1

## 9.4.2 Mode Switching

When switching between FLL engaged internal (FEI) and FLL engaged external (FEE) modes the IREFS bit can be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. After a change in the IREFS value the FLL will begin locking again after a few full cycles of the resulting divided reference frequency.

The CLKS bits can also be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. The actual switch to the newly selected clock will not occur until after a few full cycles of the new clock. If the newly selected clock is not available, the previous clock will remain selected.

## 9.4.3 Bus Frequency Divider

The BDIV bits can be changed at anytime and the actual switch to the new frequency will occur immediately.

## 9.4.4 Low Power Bit Usage

The low power bit (LP) is provided to allow the FLL to be disabled and thus conserve power when it is not being used. However, in some applications it may be desirable to enable the FLL and allow it to lock for maximum accuracy before switching to an FLL engaged mode. Do this by writing the LP bit to 0.

#### 9.4.5 Internal Reference Clock

When IRCLKEN is set the internal reference clock signal will be presented as ICSIRCLK, which can be used as an additional clock source. The ICSIRCLK frequency can be re-targeted by trimming the period of the internal reference clock. This can be done by writing a new value to the TRIM bits in the ICSTRM register. Writing a larger value will slow down the ICSIRCLK frequency, and writing a smaller value to the ICSTRM register will speed up the ICSIRCLK frequency. The TRIM bits will effect the ICSOUT frequency if the ICS is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or FLL bypassed internal low power (FBILP) mode. The TRIM and FTRIM value will not be affected by a reset.

Until ICSIRCLK is trimmed, programming low reference divider (RDIV) factors may result in ICSOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock timing specifications (see the Device Overview chapter).

If IREFSTEN is set and the IRCLKEN bit is written to 1, the internal reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

All MCU devices are factory programmed with a trim value in a reserved memory location. This value can be copied to the ICSTRM register during reset initialization. The factory trim value does not include the FTRIM bit. For finer precision, the user can trim the internal oscillator in the application and set the FTRIM bit accordingly.

## 9.4.6 Optional External Reference Clock

The ICS module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz in all modes. When the ERCLKEN is set, the external reference clock signal will be presented as ICSERCLK, which can be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by the FLL and will only be used as ICSERCLK. In these modes, the frequency can be equal to the maximum frequency the chip-level timing specifications will support (see the Device Overview chapter).

If EREFSTEN is set and the ERCLKEN bit is written to 1, the external reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

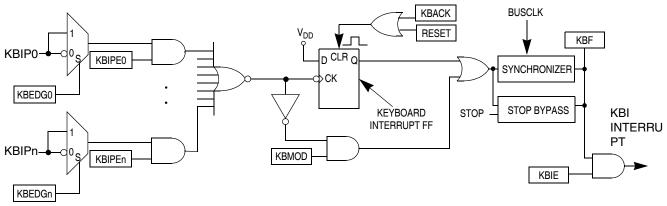

Keyboard Interrupts (S08KBIV2)

Figure 10-2. KBI Block Diagram

## **10.2 External Signal Description**

The KBI input pins can be used to detect either falling edges, or both falling edge and low level interrupt requests. The KBI input pins can also be used to detect either rising edges, or both rising edge and high level interrupt requests.

The signal properties of KBI are shown in Table 10-1.

Table 10-1. Signal Properties

| Signal | Function                | I/O |

|--------|-------------------------|-----|

| KBIPn  | Keyboard interrupt pins | I   |

## 10.3 Register Definition

The KBI includes three registers:

- An 8-bit pin status and control register.

- An 8-bit pin enable register.

- An 8-bit edge select register.

Refer to the direct-page register summary in the Memory chapter for the absolute address assignments for all KBI registers. This section refers to registers and control bits only by their names.

Some MCUs may have more than one KBI, so register names include placeholder characters to identify which KBI is being referenced.

## 10.3.1 KBI Status and Control Register (KBISC)

KBISC contains the status flag and control bits, which are used to configure the KBI.

MC9S08QD4 Series MCU Data Sheet, Rev. 6

Keyboard Interrupts (S08KBIV2)

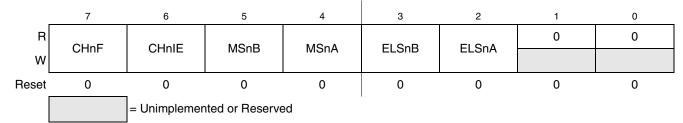

# 11.3.4 Timer Channel n Status and Control Register (TPMxCnSC)

TPMxCnSC contains the channel interrupt status flag and control bits that are used to configure the interrupt enable, channel configuration, and pin function.

#### Figure 11-8. Timer Channel n Status and Control Register (TPMxCnSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHnF        | <ul> <li>Channel n Flag — When channel n is configured for input capture, this flag bit is set when an active edge occurs on the channel n pin. When channel n is an output compare or edge-aligned PWM channel, CHnF is set when the value in the TPM counter registers matches the value in the TPM channel n value registers. This flag is seldom used with center-aligned PWMs because it is set every time the counter matches the channel value register, which correspond to both edges of the active duty cycle period.</li> <li>A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF by reading TPMxCnSC while CHnF is set and then writing a 0 to CHnF. If another interrupt request occurs before the clearing sequence is complete, the sequence is reset so CHnF would remain set after the clear sequence was completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost by clearing a previous CHnF. Reset clears CHnF. Writing a 1 to CHnF has no effect.</li> <li>No input capture or output compare event occurred on channel n</li> </ul> |

| 6<br>CHnIE       | <ul> <li>Channel n Interrupt Enable — This read/write bit enables interrupts from channel n. Reset clears CHnIE.</li> <li>O Channel n interrupt requests disabled (use software polling)</li> <li>1 Channel n interrupt requests enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5<br>MSnB        | <b>Mode Select B for TPM Channel n</b> — When CPWMS = 0, MSnB = 1 configures TPM channel n for edge-aligned PWM mode. For a summary of channel mode and setup controls, refer to Table 11-5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4<br>MSnA        | <b>Mode Select A for TPM Channel n</b> — When CPWMS = 0 and MSnB = 0, MSnA configures TPM channel n for input capture mode or output compare mode. Refer to Table 11-5 for a summary of channel mode and setup controls.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3:2<br>ELSn[B:A] | <b>Edge/Level Select Bits</b> — Depending on the operating mode for the timer channel as set by CPWMS:MSnB:MSnA and shown in Table 11-5, these bits select the polarity of the input edge that triggers an input capture event, select the level that will be driven in response to an output compare match, or select the polarity of the PWM output. Setting ELSnB:ELSnA to 0:0 configures the related timer pin as a general-purpose I/O pin unrelated to any timer channel functions. This function is typically used to temporarily disable an input capture channel or to make the timer pin available as a general-purpose I/O pin when the associated timer channel is set up as a software timer that does not require the use of a pin.                                                                                                                                                                                                                                                                                                                                                                                               |

#### Table 11-4. TPMxCnSC Register Field Descriptions

# Chapter 12 Development Support

# 12.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip flash and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

# 12.1.1 Forcing Active Background

The method for forcing active background mode depends on the specific HCS08 derivative. For the MC9S08QD4 series, you can force active background mode by holding the BKGD pin low as the MCU exits the reset condition independent of what caused the reset. If no debug pod is connected to the BKGD pin, the MCU will always reset into normal operating mode.

## 12.1.2 Module Configuration

The alternative BDC clock source for MC9S08QD4 series is the ICGCLK. See Chapter 9, "Internal Clock Source (S08ICSV1)," for more information about ICGCLK and how to select clock sources.

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

## 12.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

## 12.3 Register Definition

This section contains the descriptions of the BDC registers and control bits.

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- 2. ALL DIMENSIONS ARE IN INCHES.

- 3. 626-03 TO 626-06 OBSOLETE. NEW STANDARD 626-07.

- $\triangle$  DIMENSION TO CENTER OF LEAD WHEN FORMED PARALLEL.

- A PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CONERS). STYLE 1:

| PIN | 1. | AC I | Ν  |  |

|-----|----|------|----|--|

|     | 2. | DC + | ΙN |  |

|     | 3. | DC - | ΙN |  |

|     | 4. | AC I | N  |  |

- 5. GROUND

- OUTPUT

AUXILIARY

- 8. VCC

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICAL OUTLINE |                     | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------|---------------------|----------------------------|-------------|

| TITLE:                                                  |                    | DOCUMENT NO         | ): 98ASB42420B             | REV: N      |

| 8 LD PDIP                                               |                    | CASE NUMBER: 626-06 |                            | 19 MAY 2005 |

|                                                         |                    | STANDARD: NON-JEDEC |                            |             |