Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                          |

|----------------------------|-------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                |

| Core Size                  | 32-Bit Single-Core                              |

| Speed                      | 32MHz                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT      |

| Number of I/O              | 23                                              |

| Program Memory Size        | 32KB (32K x 8)                                  |

| Program Memory Type        | FLASH                                           |

| EEPROM Size                | 1K x 8                                          |

| RAM Size                   | 8K x 8                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                     |

| Data Converters            | A/D 10x12b                                      |

| Oscillator Type            | Internal                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                               |

| Mounting Type              | Surface Mount                                   |

| Package / Case             | 28-UFQFN                                        |

|                            |                                                 |

| Supplier Device Package    | 28-UFQFPN (4x4)                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The access line ultra-low-power STM32L041x4/6 family incorporates the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit RISC core operating at a 32 MHz frequency, high-speed embedded memories (up to 32 Kbytes of Flash program memory, 1 Kbytes of data EEPROM and 8 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L041x4/6 devices provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L041x4/6 devices offer several analog features, one 12-bit ADC with hardware oversampling, two ultra-low-power comparators, AES, several timers, one low-power timer (LPTIM), three general-purpose 16-bit timers, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L041x4/6 devices embed standard and advanced communication interfaces: one I2C, one SPI, one USART, and a low-power UART (LPUART).

The STM32L041x4/6 also include a real-time clock and a set of backup registers that remain powered in Standby mode.

The ultra-low-power STM32L041x4/6 devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

(if internal reference voltage is on), it can be the RTC alarm/tamper/timestamp/wakeup events, the USART/I2C/LPUART/LPTIMER wakeup events.

#### Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USART/I2C/LPUART/LPTIMER wakeup events.

#### • Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

#### • Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

| Operating power supply                         | Functionalities depending on the operating power supply range |                                  |                            |  |

|------------------------------------------------|---------------------------------------------------------------|----------------------------------|----------------------------|--|

| range                                          | ADC operation                                                 | Dynamic voltage<br>scaling range | I/O operation              |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | Conversion time up<br>to 570 ksps                             | Range 2 or<br>range 3            | Degraded speed performance |  |

| V <sub>DD</sub> = 1.71 to 2.0 V <sup>(1)</sup> | Conversion time up<br>to 1.14 Msps                            | Range 1, range 2 or range 3      | Degraded speed performance |  |

| V <sub>DD</sub> = 2.0 to 2.4 V                 | Conversion time up<br>to 1.14 Msps                            | Range 1, range 2 or<br>range 3   | Full speed operation       |  |

| V <sub>DD</sub> = 2.4 to 3.6 V                 | Conversion time up<br>to 1.14 Msps                            | Range 1, range 2 or range 3      | Full speed operation       |  |

CPU frequency changes from initial to final must respect the condition: f<sub>CPU initial</sub> <4f<sub>CPU initial</sub>. It must also respect 5 µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2 MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.

Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

# Table 5. Functionalities depending on the working mode(from Run/active down to standby) <sup>(1)</sup>

|                                           |            |       | Low-         | Low-           |   | Stop                 | S | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|---|----------------------|---|----------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |   | Wakeup<br>capability |   | Wakeup<br>capability |

| CPU                                       | Y          |       | Y            |                |   |                      |   |                      |

| Flash memory                              | 0          | 0     | 0            | 0              |   |                      |   |                      |

| RAM                                       | Y          | Y     | Y            | Y              | Y |                      |   |                      |

| Backup registers                          | Y          | Y     | Y            | Y              | Y |                      | Y |                      |

| EEPROM                                    | 0          | 0     | 0            | 0              |   |                      |   |                      |

| Brown-out reset<br>(BOR)                  | 0          | 0     | 0            | 0              | 0 | 0                    | 0 | 0                    |

| DMA                                       | 0          | 0     | 0            | 0              |   |                      |   |                      |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | 0     | 0            | 0              | 0 | 0                    | - |                      |

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

## 3.4.4 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1 (PA4, PA5, PA6, PA7), USART2 (PA2, PA3) or USART2 (PA9, PA10). See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

The ADC can be served by the DMA controller. It can operate from a supply voltage down to 1.65 V.

The ADC features a hardware oversampler up to 256 samples, this improves the resolution to 16 bits (see AN2668).

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers.

## 3.11 Temperature sensor

The temperature sensor ( $T_{SENSE}$ ) generates a voltage  $V_{SENSE}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                               | Memory address            |

|------------------------|---------------------------------------------------------------------------|---------------------------|

| TSENSE_CAL1            | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V  | 0x1FF8 007A - 0x1FF8 007B |

| TSENSE_CAL2            | TS ADC raw data acquired at temperature of 130 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |

Table 7. Temperature sensor calibration values

## 3.11.1 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (since no external voltage,  $V_{REF+}$ , is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

#### Table 8. Internal voltage reference measured values

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

## 3.16.2 Universal synchronous/asynchronous receiver transmitter (USART)

The USART interface (USART2) is able to communicate at speeds of up to 4 Mbit/s.

it provides hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART2 also supports Smartcard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability, auto baud rate feature and has a clock domain independent from the CPU clock that allows to wake up the MCU from Stop mode using baudrates up to 42 Kbaud.

USART2 interface can be served by the DMA controller.

Table 12 for the supported modes and features of USART interface.

| USART modes/features <sup>(1)</sup>         | USART2 |

|---------------------------------------------|--------|

| Hardware flow control for modem             | Х      |

| Continuous communication using DMA          | Х      |

| Multiprocessor communication                | Х      |

| Synchronous mode <sup>(2)</sup>             | Х      |

| Smartcard mode                              | Х      |

| Single-wire half-duplex communication       | Х      |

| IrDA SIR ENDEC block                        | Х      |

| LIN mode                                    | Х      |

| Dual clock domain and wakeup from Stop mode | Х      |

| Receiver timeout interrupt                  | Х      |

| Modbus communication                        | Х      |

| Auto baud rate detection (4 modes)          | Х      |

| Driver Enable                               | Х      |

1. X = supported.

2. This mode allows using the USART as an SPI master.

## 3.16.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock, and can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while

having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

#### 3.16.4 Serial peripheral interface (SPI)

The SPI is able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The USARTs with synchronous capability can also be used as SPI master.

The SPI can be served by the DMA controller.

Refer to *Table 13* for the supported modes and features of SPI interface.

| SPI features <sup>(1)</sup> | SPI1 |

|-----------------------------|------|

| Hardware CRC calculation    | Х    |

| I2S mode                    | -    |

| TI mode                     | Х    |

1. X = supported.

## 3.17 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

## 3.18 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

| Table 15. Pin definition | S |

|--------------------------|---|

|--------------------------|---|

|         |         | Pir      | ח num                          | ber    |                         |        |                                       | J. F III (  |               |      |                                                                   |                                            |

|---------|---------|----------|--------------------------------|--------|-------------------------|--------|---------------------------------------|-------------|---------------|------|-------------------------------------------------------------------|--------------------------------------------|

| TSSOP20 | WLCSP25 | UFQFPN28 | UFQFPN28 (STM32L041GxUxS only) | LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | Pin name<br>(function<br>after reset) | Pin<br>type | I/O structure | Note | Alternate<br>functions                                            | Additional functions                       |

| -       | -       | -        | -                              | -      | -                       | 2      | PC13-<br>ANTI_TAMP                    | I/O         | FT            | -    | -                                                                 | TAMP1/WKUP2                                |

| 2       | B5      | 2        | 2                              | 2      | 2                       | 3      | PC14-<br>OSC32_IN                     | I/O         | тс            | -    | -                                                                 | OSC32_IN                                   |

| 3       | C5      | 3        | 3                              | 3      | 3                       | 4      | PC15-<br>OSC32_OUT                    | I/O         | тс            | -    | -                                                                 | OSC32_OUT                                  |

| -       | -       | -        | -                              | -      | -                       | 5      | PH0-OSC_IN                            | I/O         | тс            | -    | -                                                                 | -                                          |

| -       | -       | -        | -                              | -      | -                       | 6      | PH1-<br>OSC_OUT                       | I/O         | тс            | -    | -                                                                 | -                                          |

| 4       | D5      | 4        | 4                              | 4      | 4                       | 7      | NRST                                  | I/O         | -             | -    | -                                                                 | -                                          |

| -       | -       | -        | -                              | -      | -                       | 1      | PC0                                   | I/O         | FT            | -    | LPTIM1_IN1,<br>EVENTOUT,<br>LPUART1_RX                            | -                                          |

| -       | E1      | -        | -                              | -      | "0"                     | 8      | VSSA                                  | S           | -             | -    | -                                                                 | -                                          |

| 5       | C4      | 5        | 5                              | 5      | 5                       | 9      | VDDA                                  | S           | -             | -    | -                                                                 | -                                          |

| 6       | E5      | 6        | 6                              | 6      | 6                       | -      | PA0-CK_IN                             | I/O         | тс            | -    | LPTIM1_IN1,<br>TIM2_CH1,<br>USART2_CTS,<br>TIM2_ETR,<br>COMP1_OUT | COMP1_INM6,<br>ADC_IN0,<br>RTC_TAMP2/WKUP1 |

| -       | -       | -        | -                              | -      | -                       | 10     | PA0                                   | I/O         | тс            | -    | LPTIM1_IN1,<br>TIM2_CH1,<br>USART2_CTS,<br>TIM2_ETR,<br>COMP1_OUT | COMP1_INM6,<br>ADC_IN0,<br>RTC_TAMP2/WKUP1 |

|        |      |                                                     |                     | Table                              | 16. Alternate fu  | unctions                                       |            |                      |           |

|--------|------|-----------------------------------------------------|---------------------|------------------------------------|-------------------|------------------------------------------------|------------|----------------------|-----------|

|        |      | AF0                                                 | AF1                 | AF2                                | AF3               | AF4                                            | AF5        | AF6                  | AF7       |

| Ports  |      | SPI1/USART2<br>/LPTIM/TIM21<br>/EVENTOUT/<br>SYS_AF | SPI1/I2C1/<br>LPTIM | LPTIM/TIM2/<br>EVENTOUT/<br>SYS_AF | I2C1/<br>EVENTOUT | I2C1/USART2/<br>LPUART1/<br>TIM22/<br>EVENTOUT | TIM2/21/22 | LPUART1/<br>EVENTOUT | COMP1/2   |

|        | PA0  | -                                                   | LPTIM1_IN1          | TIM2_CH1                           | -                 | USART2_CTS                                     | TIM2_ETR   | -                    | COMP1_OUT |

|        | PA1  | EVENTOUT                                            | LPTIM1_IN2          | TIM2_CH2                           | I2C1_SMBA         | USART2_RTS                                     | TIM21_ETR  | -                    | -         |

|        | PA2  | TIM21_CH1                                           | -                   | TIM2_CH3                           | -                 | USART2_TX                                      | -          | LPUART1_TX           | COMP2_OUT |

|        | PA3  | TIM21_CH2                                           | -                   | TIM2_CH4                           | -                 | USART2_RX                                      | -          | LPUART1_RX           |           |

|        | PA4  | SPI1_NSS                                            | LPTIM1_IN1          | -                                  | -                 | USART2_CK                                      | TIM22_ETR  | -                    | -         |

|        | PA5  | SPI1_SCK                                            | LPTIM1_IN2          | TIM2_ETR                           | -                 | -                                              | TIM2_CH1   | -                    | -         |

|        | PA6  | SPI1_MISO                                           | LPTIM1_ETR          | -                                  | -                 | LPUART1_CTS                                    | TIM22_CH1  | EVENTOUT             | COMP1_OUT |

| Port A | PA7  | SPI1_MOSI                                           | LPTIM1_OUT          | -                                  | -                 | USART2_CTS                                     | TIM22_CH2  | EVENTOUT             | COMP2_OUT |

| FULA   | PA8  | MCO                                                 | -                   | LPTIM1_IN1                         | EVENTOUT          | USART2_CK                                      | TIM2_CH1   | -                    | -         |

|        | PA9  | MCO                                                 | I2C1_SCL            | -                                  | -                 | USART2_TX                                      | TIM22_CH1  | -                    | -         |

|        | PA10 | -                                                   | I2C1_SDA            | -                                  | -                 | USART2_RX                                      | TIM22_CH2  | -                    | -         |

|        | PA11 | SPI1_MISO                                           | -                   | EVENTOUT                           | -                 | USART2_CTS                                     | TIM21_CH2  | -                    | COMP1_OUT |

|        | PA12 | SPI1_MOSI                                           | -                   | EVENTOUT                           | -                 | USART2_RTS                                     | -          | -                    | COMP2_OUT |

|        | PA13 | SWDIO                                               | LPTIM1_ETR          | -                                  | -                 | -                                              | -          | LPUART1_RX           | -         |

|        | PA14 | SWCLK                                               | LPTIM1_OUT          | -                                  | I2C1_SMBA         | USART2_TX                                      | -          | LPUART1_TX           | -         |

|        | PA15 | SPI1_NSS                                            | -                   | TIM2_ETR                           | EVENTOUT          | USART2_RX                                      | TIM2_CH1   | -                    | -         |

DocID027301 Rev 4

44/119

STM32L041x4/6

5

|        |      |                                                     |                     | Table 16. Alt                      | ternate functio   | ns (continued)                                 |            |                      |         |

|--------|------|-----------------------------------------------------|---------------------|------------------------------------|-------------------|------------------------------------------------|------------|----------------------|---------|

|        |      | AF0                                                 | AF1                 | AF2                                | AF3               | AF4                                            | AF5        | AF6                  | AF7     |

| Ро     | orts | SPI1/USART2<br>/LPTIM/TIM21<br>/EVENTOUT/<br>SYS_AF | SPI1/I2C1/<br>LPTIM | LPTIM/TIM2/<br>EVENTOUT/<br>SYS_AF | I2C1/<br>EVENTOUT | I2C1/USART2/<br>LPUART1/<br>TIM22/<br>EVENTOUT | TIM2/21/22 | LPUART1/<br>EVENTOUT | COMP1/2 |

|        | PB0  | EVENTOUT                                            | SPI1_MISO           | -                                  | -                 | USART2_RTS                                     | TIM2_CH3   | -                    | -       |

|        | PB1  | USART2_CK                                           | SPI1_MOSI           | -                                  | -                 | LPUART1_RTS                                    | TIM2_CH4   | -                    | -       |

|        | PB2  | -                                                   | -                   | LPTIM1_OUT                         | -                 | -                                              | -          | -                    | -       |

|        | PB3  | SPI1_SCK                                            | -                   | TIM2_CH2                           | -                 | EVENTOUT                                       | -          | -                    | -       |

|        | PB4  | SPI1_MISO                                           | -                   | EVENTOUT                           | -                 | TIM22_CH1                                      | -          | -                    | -       |

|        | PB5  | SPI1_MOSI                                           | -                   | LPTIM1_IN1                         | I2C1_SMBA         | TIM22_CH2                                      | -          | -                    | -       |

|        | PB6  | USART2_TX                                           | I2C1_SCL            | LPTIM1_ETR                         | -                 | -                                              | TIM21_CH1  | -                    | -       |

| Port B | PB7  | USART2_RX                                           | I2C1_SDA            | LPTIM1_IN2                         | -                 | -                                              | -          | -                    | -       |

| FUILD  | PB8  | -                                                   | -                   | -                                  | -                 | I2C1_SCL                                       | -          | -                    | -       |

|        | PB9  | -                                                   | -                   | EVENTOUT                           | -                 | I2C1_SDA                                       | -          | -                    | -       |

|        | PB10 | -                                                   | -                   | TIM2_CH3                           | -                 | -                                              | -          | LPUART1_TX           | -       |

|        | PB11 | EVENTOUT                                            | -                   | TIM2_CH4                           | -                 | -                                              | -          | LPUART1_RX           | -       |

|        | PB12 | SPI1_NSS                                            | -                   | -                                  | -                 | -                                              | -          | EVENTOUT             | -       |

|        | PB13 | SPI1_SCK                                            | -                   | МСО                                | -                 | -                                              | TIM21_CH1  | LPUART1_CTS          | -       |

|        | PB14 | SPI1_MISO                                           | -                   | RTC_OUT                            | -                 | -                                              | TIM21_CH2  | LPUART1_RTS          | -       |

|        | PB15 | SPI1_MOSI                                           | -                   | RTC_REFIN                          | -                 | -                                              | -          | -                    | -       |

| Port C | PC0  | LPTIM1_IN1                                          | -                   | EVENTOUT                           | -                 | -                                              | -          | LPUART1_RX           | -       |

| Dort L | PH0  | -                                                   | -                   | -                                  | -                 | -                                              | -          | -                    | -       |

| Port H | PH1  | -                                                   | -                   | -                                  | -                 | -                                              | -          | -                    | -       |

DocID027301 Rev 4

5

45/119

STM32L041x4/6

Pin descriptions

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.6 V (for the 1.65 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

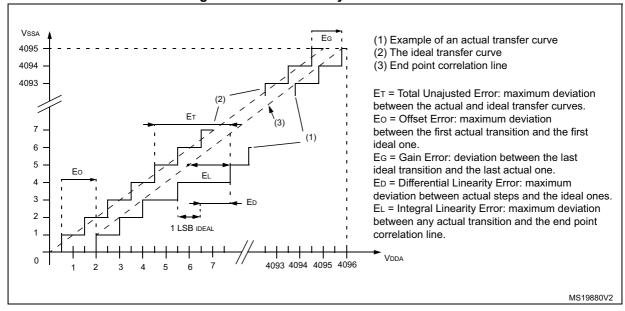

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

## 6.1.3 Typical curves

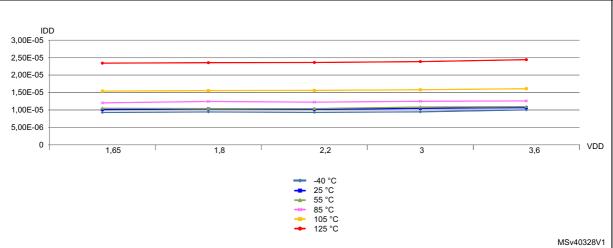

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 6.1.4 Loading capacitor

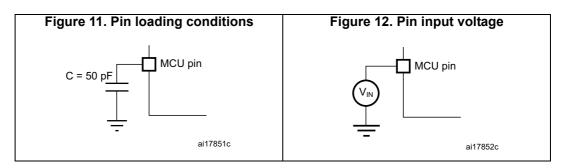

The loading conditions used for pin parameter measurement are shown in *Figure 11*.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 12*.

| Symbol            | Parameter                     | Conditions                                | Min  | Тур  | Мах  | Unit |  |

|-------------------|-------------------------------|-------------------------------------------|------|------|------|------|--|

| N/                | Brown-out reset threshold 3   | Falling edge                              | 2.45 | 2.55 | 2.6  |      |  |

| V <sub>BOR3</sub> | Brown-out reset threshold 5   | Rising edge                               | 2.54 | 2.66 | 2.7  |      |  |

| M.                | Brown-out reset threshold 4   | Falling edge                              | 2.68 | 2.8  | 2.85 |      |  |

| V <sub>BOR4</sub> |                               | Rising edge                               | 2.78 | 2.9  | 2.95 |      |  |

| V <sub>PVD0</sub> | Programmable voltage detector | Falling edge                              | 1.8  | 1.85 | 1.88 |      |  |

|                   | threshold 0                   | Rising edge                               | 1.88 | 1.94 | 1.99 |      |  |

| V <sub>PVD1</sub> | PVD threshold 1               | Falling edge                              | 1.98 | 2.04 | 2.09 |      |  |

|                   |                               | Rising edge                               | 2.08 | 2.14 | 2.18 |      |  |

| V <sub>PVD2</sub> | PVD threshold 2               | Falling edge                              | 2.20 | 2.24 | 2.28 | v    |  |

|                   |                               | Rising edge                               | 2.28 | 2.34 | 2.38 | v    |  |

| V                 | DVD threshold 2               | Falling edge                              | 2.39 | 2.44 | 2.48 |      |  |

| V <sub>PVD3</sub> | PVD threshold 3               | Rising edge                               | 2.47 | 2.54 | 2.58 |      |  |

| V                 | PVD threshold 4               | Falling edge                              | 2.57 | 2.64 | 2.69 |      |  |

| V <sub>PVD4</sub> |                               | Rising edge                               | 2.68 | 2.74 | 2.79 |      |  |

| V                 | PVD threshold 5               | Falling edge                              | 2.77 | 2.83 | 2.88 |      |  |

| V <sub>PVD5</sub> |                               | Rising edge                               | 2.87 | 2.94 | 2.99 |      |  |

| V                 | PVD threshold 6               | Falling edge                              | 2.97 | 3.05 | 3.09 |      |  |

| V <sub>PVD6</sub> |                               | Rising edge                               | 3.08 | 3.15 | 3.20 | .20  |  |

|                   |                               | BOR0 threshold                            | -    | 40   | -    |      |  |

| V <sub>hyst</sub> | Hysteresis voltage            | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |  |

Table 21. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

## 6.3.3 Embedded internal reference voltage

The parameters given in *Table 23* are based on characterization results, unless otherwise specified.

| Calibration value name | Description                                                       | Memory address            |

|------------------------|-------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at temperature of 25 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                             | Conditions                                                     | Min   | Тур   | Max   | Unit                     |  |  |

|------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|--------------------------|--|--|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                            | – 40 °C < T <sub>J</sub> < +125 °C                             | 1.202 | 1.224 | 1.242 | V                        |  |  |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                       | -                                                              | -     | 2     | 3     | ms                       |  |  |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> voltage during V <sub>REFINT</sub> factory measure   | -                                                              | 2.99  | 3     | 3.01  | V                        |  |  |

| Avref_meas                               | Accuracy of factory-measured V <sub>REFINT</sub> value <sup>(3)</sup> | Including uncertainties due to ADC and $V_{\text{DDA}}$ values | -     | -     | ±5    | mV                       |  |  |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                               | –40 °C < T <sub>J</sub> < +125 °C                              | -     | 25    | 100   | ppm/°C                   |  |  |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                   | 1000 hours, T= 25 °C                                           | -     | -     | 1000  | ppm                      |  |  |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                   | 3.0 V < V <sub>DDA</sub> < 3.6 V                               | -     | -     | 2000  | ppm/V                    |  |  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage   | -                                                              | 5     | 10    | -     | μs                       |  |  |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                      | -                                                              | -     | -     | 10    | μs                       |  |  |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                       | -                                                              | -     | 13.5  | 25    | μA                       |  |  |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                                | -                                                              | -     | -     | 1     | μA                       |  |  |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                  | -                                                              | -     | -     | 50    | pF                       |  |  |

| I <sub>LPBUF</sub> <sup>(4)</sup>        | Consumption of reference<br>voltage buffer for VREF_OUT<br>and COMP   | -                                                              | -     | 730   | 1200  | nA                       |  |  |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup>  | 1/4 reference voltage                                                 | -                                                              | 24    | 25    | 26    |                          |  |  |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup>  | 1/2 reference voltage                                                 | -                                                              | 49    | 50    | 51    | %<br>V <sub>REFINT</sub> |  |  |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup>  | 3/4 reference voltage                                                 | -                                                              | 74    | 75    | 76    | KEFINI                   |  |  |

#### Table 23. Embedded internal reference voltage<sup>(1)</sup>

1. Refer to *Table 35: Peripheral current consumption in Stop and Standby mode* for the value of the internal reference current consumption (I<sub>REFINT</sub>).

2. Guaranteed by test in production.

3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

4. Guaranteed by design.

5. Shortest sampling time can be determined in the application by multiple iterations.

6. To guarantee less than 1% VREF\_OUT deviation.

DocID027301 Rev 4

| Symbol                        | Parameter               |                                              | Conditions                                                          |                                         | Тур                | Max <sup>(1)</sup> | Unit |

|-------------------------------|-------------------------|----------------------------------------------|---------------------------------------------------------------------|-----------------------------------------|--------------------|--------------------|------|

|                               |                         |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz<br>Flash memory OFF | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 3.2 <sup>(2)</sup> | -                  |      |

|                               |                         |                                              |                                                                     | $T_A$ = -40 °C to 25 °C                 | 13                 | 19                 |      |

|                               |                         |                                              | MSI clock, 65 kHz                                                   | T <sub>A</sub> = 85 °C                  | 16                 | 21                 |      |

|                               |                         |                                              |                                                                     | T <sub>A</sub> = 105 °C                 | 18.5               | 24                 | μA   |

|                               |                         | All peripherals<br>off, V <sub>DD</sub> from |                                                                     | T <sub>A</sub> = 125 °C                 | 23.5               | 32                 |      |

|                               | Supply                  |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz,<br>Flash memory ON | $T_A$ = -40 °C to 25 °C                 | 13.5               | 19                 |      |

| I <sub>DD</sub><br>(LP Sleep) | current in<br>Low-power |                                              |                                                                     | T <sub>A</sub> = 85 °C                  | 16.5               | 21                 |      |

|                               | sleep mode              | 1.65 V to 3.6 V                              |                                                                     | T <sub>A</sub> = 105 °C                 | 18.5               | 24                 |      |

|                               |                         |                                              |                                                                     | T <sub>A</sub> = 125 °C                 | 24                 | 33                 |      |

|                               |                         |                                              |                                                                     | $T_A$ = -40 °C to 25 °C                 | 15.5               | 21                 |      |

|                               |                         |                                              | MSI clock, 131 kHz                                                  | T <sub>A</sub> = 55 °C                  | 17.5               | 22                 |      |

|                               |                         |                                              | f <sub>HCLK</sub> = 131 kHz,                                        | T <sub>A</sub> = 85 °C                  | 18.5               | 23                 |      |

|                               |                         |                                              | Flash memory ON                                                     | T <sub>A</sub> = 105 °C                 | 21                 | 26                 |      |

|                               |                         |                                              |                                                                     | T <sub>A</sub> = 125 °C                 | 26                 | 35                 |      |

#### Table 30. Current consumption in Low-power Sleep mode

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

As the CPU is in Sleep mode, the difference between the current consumption with Flash memory ON and OFF (nearly 12 μA) is the same whatever the clock frequency.

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125 \text{ °C conforming to JESD78A}$ | II level A |

| Table 51 | Electrical | sensitivities |

|----------|------------|---------------|

|          |            | ••••••        |

## 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 52.

|                  |                                                              | Functional s       |                    |      |

|------------------|--------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                  | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                    | -0                 | NA                 |      |

|                  | Injected current on PA0, PA2, PA4, PA5,<br>PC15, PH0 and PH1 | -5                 | 0                  | mA   |

| I <sub>INJ</sub> | Injected current on any other FT and FTf pin                 | -5 <sup>(1)</sup>  | NA                 | ma   |

|                  | Injected current on any other pin                            | -5 <sup>(1)</sup>  | +5                 |      |

#### Table 52. I/O current injection susceptibility

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

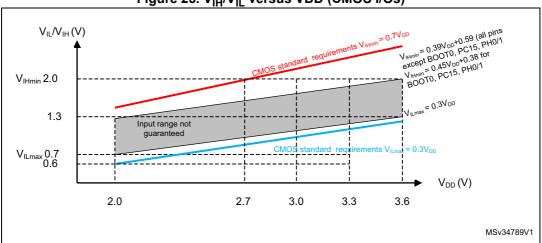

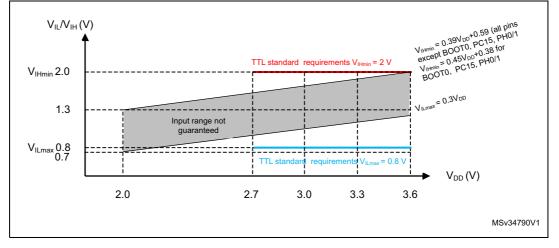

Figure 25. V<sub>IH</sub>/V<sub>IL</sub> versus VDD (CMOS I/Os)

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 15$  mA with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 54*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD(Σ)</sub> (see *Table 18*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS(Σ)</sub> (see *Table 18*).

| Symbol                                                                                                                 | Parameter                        | Conditions                                     | Min                                               | Тур   | Мах                                               | Unit                       |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------|---------------------------------------------------|-------|---------------------------------------------------|----------------------------|

| <b>•</b> (3)                                                                                                           | Colibration time                 | f <sub>ADC</sub> = 16 MHz                      |                                                   | 5.2   |                                                   | μs                         |

| <sup>I</sup> CAL <sup>(*)</sup>                                                                                        | Calibration time                 |                                                |                                                   | 83    |                                                   | 1/f <sub>ADC</sub>         |

|                                                                                                                        |                                  | ADC clock = HSI16                              | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles | -     | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

| W <sub>LATENCY</sub>                                                                                                   | ADC_DR register write<br>latency | ADC clock = PCLK/2                             | -                                                 | 4.5   | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                                                                                                        |                                  | ADC clock = PCLK/4                             | -                                                 | 8.5   | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                                                                                                        |                                  | $f_{ADC} = f_{PCLK}/2 = 16 \text{ MHz}$        |                                                   | 0.266 |                                                   | μs                         |

|                                                                                                                        |                                  | $f_{ADC} = f_{PCLK}/2$                         | 8.5                                               |       |                                                   | 1/f <sub>PCLK</sub>        |

| t <sub>latr</sub> (3)                                                                                                  | Trigger conversion latency       | $f_{ADC} = f_{PCLK}/4 = 8 \text{ MHz}$         | 0.516                                             |       | μs                                                |                            |

|                                                                                                                        |                                  | f <sub>ADC</sub> = f <sub>PCLK</sub> /4        |                                                   | 16.5  |                                                   | 1/f <sub>PCLK</sub>        |

| $W_{LATENCY} \begin{cases} A \\ Iz \end{cases}$ $t_{latr}^{(3)} T$ $Jitter_{ADC} c$ $t_{S}^{(3)} S$ $t_{STAB}^{(3)} F$ |                                  | f <sub>ADC</sub> = f <sub>HSI16</sub> = 16 MHz | 0.252                                             | -     | 0.260                                             | μs                         |

| Jitter <sub>ADC</sub>                                                                                                  | ADC jitter on trigger conversion | f <sub>ADC</sub> = f <sub>HSI16</sub>          | -                                                 | 1     | -                                                 | 1/f <sub>HSI16</sub>       |

| + (3)                                                                                                                  | Sampling time                    | f <sub>ADC</sub> = 16 MHz                      | 0.093                                             | -     | 10.03                                             | μs                         |

| ls(*)                                                                                                                  |                                  |                                                | 1.5                                               | -     | 239.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>STAB</sub> <sup>(3)</sup>                                                                                       | Power-up time                    |                                                | 0                                                 | 0     | 1                                                 | μs                         |

|                                                                                                                        | Total conversion time            | f <sub>ADC</sub> = 16 MHz                      | 0.875                                             |       | 10.81                                             | μs                         |

| t <sub>ConV</sub> <sup>(3)</sup>                                                                                       | (including sampling time)        |                                                | 14 to 173 (t <sub>S</sub> fo<br>successive app    |       |                                                   | 1/f <sub>ADC</sub>         |

#### Table 57. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value can be decreased in specific temperature conditions. Refer to *Table 58: RAIN max for fADC* = 16 *MHz*.

2. A current consumption proportional to the APB clock frequency has to be added (see *Table 34: Peripheral current consumption in Run or Sleep mode*).

3. Guaranteed by design.

Standard channels have an extra protection resistance which depends on supply voltage. Refer to Table 58: RAIN max for fADC = 16 MHz.

#### Equation 1: $R_{AIN} max$ formula

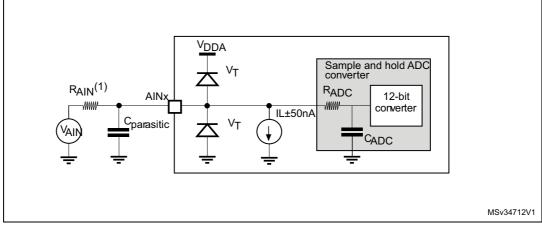

$$R_{AIN} < \frac{r_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

#### Figure 29. ADC accuracy characteristics

<sup>1.</sup> Refer to Table 57: ADC characteristics for the values of RAIN, RADC and CADC.

C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

#### 6.3.16 Temperature sensor characteristics

#### Table 60. Temperature sensor calibration values

| Calibration value name | Description                                                                    | Memory address            |  |

|------------------------|--------------------------------------------------------------------------------|---------------------------|--|

| TS_CAL1                | TS ADC raw data acquired at<br>temperature of 30 °C,<br>V <sub>DDA</sub> = 3 V | 0x1FF8 007A - 0x1FF8 007B |  |

| TS_CAL2                | TS ADC raw data acquired at<br>temperature of 130 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |

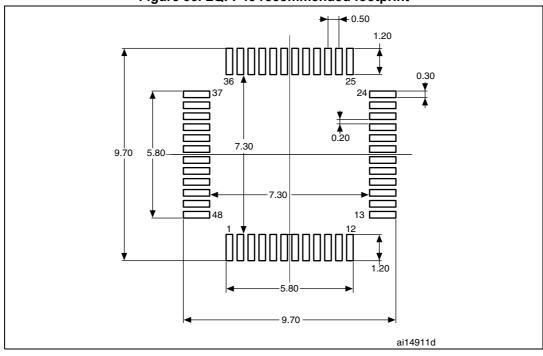

|        |             |       | echanical ua |                       | (4)    |        |

|--------|-------------|-------|--------------|-----------------------|--------|--------|

| Symbol | millimeters |       |              | inches <sup>(1)</sup> |        |        |

|        | Min         | Тур   | Max          | Min                   | Тур    | Max    |

| А      | -           | -     | 1.600        | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150        | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450        | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270        | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -     | 0.200        | 0.0035                | -      | 0.0079 |

| D      | 8.800       | 9.000 | 9.200        | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800       | 7.000 | 7.200        | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.500 | -            | -                     | 0.2165 | -      |

| Е      | 8.800       | 9.000 | 9.200        | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800       | 7.000 | 7.200        | 0.2677                | 0.2756 | 0.2835 |

| E3     | -           | 5.500 | -            | -                     | 0.2165 | -      |

| е      | -           | 0.500 | -            | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600 | 0.750        | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -            | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°  | 7°           | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -     | 0.080        | -                     | -      | 0.0031 |

| Table 70. LQFP48 - 48-pin low-profile quad flat package, 7 x 7 mm, package |

|----------------------------------------------------------------------------|

| mechanical data                                                            |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.