Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 25                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 1K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l041k6u6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The access line ultra-low-power STM32L041x4/6 family incorporates the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit RISC core operating at a 32 MHz frequency, high-speed embedded memories (up to 32 Kbytes of Flash program memory, 1 Kbytes of data EEPROM and 8 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L041x4/6 devices provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L041x4/6 devices offer several analog features, one 12-bit ADC with hardware oversampling, two ultra-low-power comparators, AES, several timers, one low-power timer (LPTIM), three general-purpose 16-bit timers, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L041x4/6 devices embed standard and advanced communication interfaces: one I2C, one SPI, one USART, and a low-power UART (LPUART).

The STM32L041x4/6 also include a real-time clock and a set of backup registers that remain powered in Standby mode.

The ultra-low-power STM32L041x4/6 devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

# 3.12 Ultra-low-power comparators and reference voltage

The STM32L041x4/6 embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with ultra low consumption

- One comparator with rail-to-rail inputs, fast or slow mode.

- The threshold can be one of the following:

- External I/O pins

- Internal reference voltage (V<sub>REFINT</sub>)

- submultiple of Internal reference voltage(1/4, 1/2, 3/4) for the rail to rail comparator.

Both comparators can wake up the devices from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

# 3.13 System configuration controller

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM21, TIM22 and LPTIM timer input captures. It also controls the routing of internal analog signals to the ADC, COMP1 and COMP2 and the internal reference voltage  $V_{\sf REFINT}$ .

# 3.14 AES

The AES Hardware Accelerator can be used to encrypt and decrypt data using the AES algorithm (compatible with FIPS PUB 197, 2001 Nov 26):

- Key scheduler

- Key derivation for decryption

- 128-bit data block processed

- 128-bit key length

- 213 clock cycles to encrypt/decrypt one 128-bit block

- Electronic codebook (ECB), cypher block chaining (CBC), and counter mode (CTR) supported by hardware.

The AES can be served by the DMA controller.

# 3.16.2 Universal synchronous/asynchronous receiver transmitter (USART)

The USART interface (USART2) is able to communicate at speeds of up to 4 Mbit/s.

it provides hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART2 also supports Smartcard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability, auto baud rate feature and has a clock domain independent from the CPU clock that allows to wake up the MCU from Stop mode using baudrates up to 42 Kbaud.

USART2 interface can be served by the DMA controller.

Table 12 for the supported modes and features of USART interface.

| USART modes/features <sup>(1)</sup>         | USART2 |

|---------------------------------------------|--------|

| Hardware flow control for modem             | Х      |

| Continuous communication using DMA          | Х      |

| Multiprocessor communication                | Х      |

| Synchronous mode <sup>(2)</sup>             | Х      |

| Smartcard mode                              | Х      |

| Single-wire half-duplex communication       | Х      |

| IrDA SIR ENDEC block                        | Х      |

| LIN mode                                    | Х      |

| Dual clock domain and wakeup from Stop mode | Х      |

| Receiver timeout interrupt                  | Х      |

| Modbus communication                        | Х      |

| Auto baud rate detection (4 modes)          | Х      |

| Driver Enable                               | Х      |

1. X = supported.

2. This mode allows using the USART as an SPI master.

# 3.16.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock, and can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while

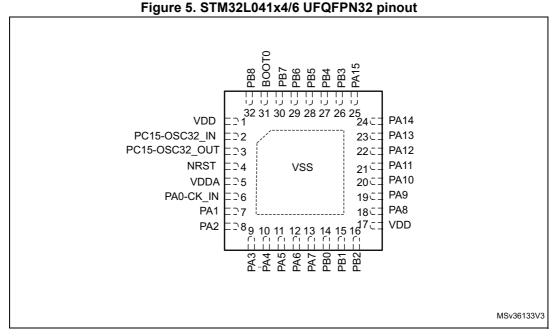

1. The above figure shows the package top view.

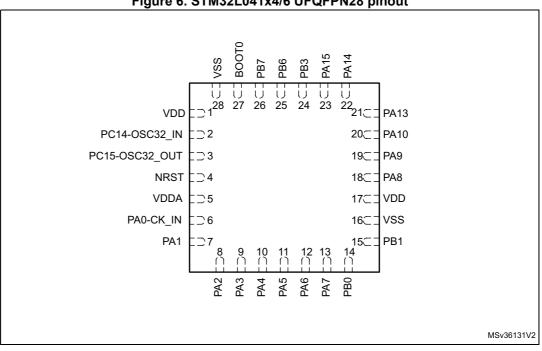

Figure 6. STM32L041x4/6 UFQFPN28 pinout

1. The above figure shows the package top view.

2. This pinout applies to all part numbers except for STM32L041GxUxS.

| Table 15. | Pin definitions | (continued) |

|-----------|-----------------|-------------|

|           |                 |             |

|         |         | Pir      | n num                          | ber    |                         |        |                                       |             |               |      | ,                                                               |                           |

|---------|---------|----------|--------------------------------|--------|-------------------------|--------|---------------------------------------|-------------|---------------|------|-----------------------------------------------------------------|---------------------------|

| TSSOP20 | WLCSP25 | UFQFPN28 | UFQFPN28 (STM32L041GxUxS only) | LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | Pin name<br>(function<br>after reset) | Pin<br>type | I/O structure | Note | Alternate<br>functions                                          | Additional functions      |

| -       | -       | -        | -                              | -      | -                       | 35     | VSS                                   | S           | -             | -    | -                                                               | -                         |

| -       | D1      | -        | -                              | -      | -                       | 36     | VDD                                   | S           | -             | -    | -                                                               | -                         |

| 20      | A2      | 22       | 22                             | 24     | 24                      | 37     | PA14                                  | I/O         | FT            | -    | SWCLK,<br>LPTIM1_OUT,<br>I2C1_SMBA,<br>USART2_TX,<br>LPUART1_TX | -                         |

| -       | -       | 23       | 23                             | 25     | 25                      | 38     | PA15                                  | I/O         | FT            | -    | SPI1_NSS,<br>TIM2_ETR,<br>EVENTOUT,<br>USART2_RX,<br>TIM2_CH1   |                           |

| -       | B2      | 24       | 24                             | 26     | 26                      | 39     | PB3                                   | I/O         | FT            | -    | SPI1_SCK,<br>TIM2_CH2,<br>EVENTOUT                              | COMP2_INN                 |

| -       | -       | -        | 25                             | 27     | 27                      | 40     | PB4                                   | I/O         | FT            | -    | SPI1_MISO,<br>EVENTOUT,<br>TIM22_CH1                            | COMP2_INP                 |

| -       | -       | -        | 26                             | 28     | 28                      | 41     | PB5                                   | I/O         | FT            | -    | SPI1_MOSI,<br>LPTIM1_IN1,<br>I2C1_SMBA,<br>TIM22_CH2            | COMP2_INP                 |

| -       | A3      | 25       | 27                             | 29     | 29                      | 42     | PB6                                   | I/O         | FTf           | -    | USART2_TX,<br>I2C1_SCL,<br>LPTIM1_ETR,<br>TIM21_CH1             | COMP2_INP                 |

| -       | A4      | 26       | 28                             | 30     | 30                      | 43     | PB7                                   | I/O         | FTf           | -    | USART2_RX,<br>I2C1_SDA,<br>LPTIM1_IN2                           | COMP2_INP,<br>VREF_PVD_IN |

|         | -       | Pir      | num                            | ber    |                         |        |                                       |             |               |      |                        |                      |  |

|---------|---------|----------|--------------------------------|--------|-------------------------|--------|---------------------------------------|-------------|---------------|------|------------------------|----------------------|--|

| TSSOP20 | WLCSP25 | UFQFPN28 | UFQFPN28 (STM32L041GxUxS only) | LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | Pin name<br>(function<br>after reset) | Pin<br>type | I/O structure | Note | Alternate<br>functions | Additional functions |  |

| 1       | A5      | 27       | 1                              | 31     | 31                      | 44     | BOOT0                                 | I           | -             | -    | -                      | -                    |  |

| -       | -       | -        | -                              | -      | 32                      | 45     | PB8                                   | I/O         | FTf           | -    | I2C1_SCL               | -                    |  |

| -       | -       | -        | -                              | -      | -                       | 46     | PB9                                   | I/O         | FTf           | -    | EVENTOUT,<br>I2C1_SDA  | -                    |  |

| -       | -       | 28       | -                              | 32     | -                       | 47     | VSS                                   | S           | -             | -    | -                      | -                    |  |

| -       | -       | 1        | -                              | 1      | 1                       | 48     | VDD                                   | S           | -             | -    | -                      | -                    |  |

Table 15. Pin definitions (continued)

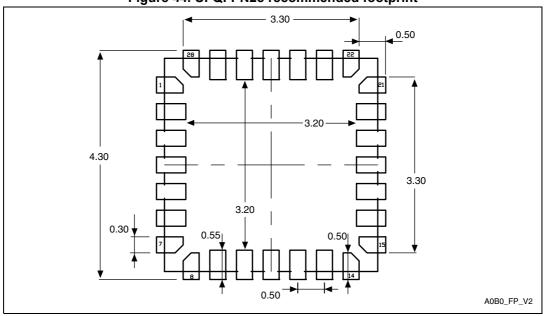

1. VSS pins are connected to the exposed pad (see Figure 40: UFQFPN32, 5 x 5 mm, 32-pin package outline).

|        |      |                                                     |                     | Table 16. Alt                      | ternate functio   | ns (continued)                                 |            |                      |         |

|--------|------|-----------------------------------------------------|---------------------|------------------------------------|-------------------|------------------------------------------------|------------|----------------------|---------|

|        |      | AF0                                                 | AF1                 | AF2                                | AF3               | AF4                                            | AF5        | AF6                  | AF7     |

| Po     | orts | SPI1/USART2<br>/LPTIM/TIM21<br>/EVENTOUT/<br>SYS_AF | SPI1/I2C1/<br>LPTIM | LPTIM/TIM2/<br>EVENTOUT/<br>SYS_AF | I2C1/<br>EVENTOUT | I2C1/USART2/<br>LPUART1/<br>TIM22/<br>EVENTOUT | TIM2/21/22 | LPUART1/<br>EVENTOUT | COMP1/2 |

|        | PB0  | EVENTOUT                                            | SPI1_MISO           | -                                  | -                 | USART2_RTS                                     | TIM2_CH3   | -                    | -       |

|        | PB1  | USART2_CK                                           | SPI1_MOSI           | -                                  | -                 | LPUART1_RTS                                    | TIM2_CH4   | -                    | -       |

|        | PB2  | -                                                   | -                   | LPTIM1_OUT                         | -                 | -                                              | -          | -                    | -       |

|        | PB3  | SPI1_SCK                                            | -                   | TIM2_CH2                           | -                 | EVENTOUT                                       | -          | -                    | -       |

|        | PB4  | SPI1_MISO                                           | -                   | EVENTOUT                           | -                 | TIM22_CH1                                      | -          | -                    | -       |

|        | PB5  | SPI1_MOSI                                           | -                   | LPTIM1_IN1                         | I2C1_SMBA         | TIM22_CH2                                      | -          | -                    | -       |

|        | PB6  | USART2_TX                                           | I2C1_SCL            | LPTIM1_ETR                         | -                 | -                                              | TIM21_CH1  | -                    | -       |

| Port B | PB7  | USART2_RX                                           | I2C1_SDA            | LPTIM1_IN2                         | -                 | -                                              | -          | -                    | -       |

| FUILD  | PB8  | -                                                   | -                   | -                                  | -                 | I2C1_SCL                                       | -          | -                    | -       |

|        | PB9  | -                                                   | -                   | EVENTOUT                           | -                 | I2C1_SDA                                       | -          | -                    | -       |

|        | PB10 | -                                                   | -                   | TIM2_CH3                           | -                 | -                                              | -          | LPUART1_TX           | -       |

|        | PB11 | EVENTOUT                                            | -                   | TIM2_CH4                           | -                 | -                                              | -          | LPUART1_RX           | -       |

|        | PB12 | SPI1_NSS                                            | -                   | -                                  | -                 | -                                              | -          | EVENTOUT             | -       |

|        | PB13 | SPI1_SCK                                            | -                   | МСО                                | -                 | -                                              | TIM21_CH1  | LPUART1_CTS          | -       |

|        | PB14 | SPI1_MISO                                           | -                   | RTC_OUT                            | -                 | -                                              | TIM21_CH2  | LPUART1_RTS          | -       |

|        | PB15 | SPI1_MOSI                                           | -                   | RTC_REFIN                          | -                 | -                                              | -          | -                    | -       |

| Port C | PC0  | LPTIM1_IN1                                          | -                   | EVENTOUT                           | -                 | -                                              | -          | LPUART1_RX           | -       |

| Dort L | PH0  | -                                                   | -                   | -                                  | -                 | -                                              | -          | -                    | -       |

| Port H | PH1  | -                                                   | -                   | -                                  | -                 | -                                              | -          | -                    | -       |

DocID027301 Rev 4

5

45/119

STM32L041x4/6

Pin descriptions

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 17: Voltage characteristics*, *Table 18: Current characteristics*, and *Table 19: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                                                        | Min                  | Мах                  | Unit |

|------------------------------------|------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>   | External main supply voltage<br>(including V <sub>DDA</sub> , V <sub>DD</sub> ) <sup>(1)</sup> | -0.3                 | 4.0                  |      |

|                                    | Input voltage on FT and FTf pins                                                               | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub> <sup>(2)</sup>     | Input voltage on TC pins                                                                       | V <sub>SS</sub> –0.3 | 4.0                  | V    |

| VIN' /                             | Input voltage on BOOT0                                                                         | V <sub>SS</sub>      | V <sub>DD</sub> +4.0 |      |

|                                    | Input voltage on any other pin                                                                 | V <sub>SS</sub> –0.3 | 4.0                  |      |

| $ \Delta V_{DD} $                  | Variations between different $V_{DDx}$ power pins                                              | -                    | 50                   |      |

| V <sub>DDA</sub> -V <sub>DDx</sub> | Variations between any $V_{DDx}$ and $V_{DDA}$ power $\mbox{pins}^{(3)}$                       | -                    | 300                  | mV   |

| $ \Delta V_{SS} $                  | Variations between all different ground pins                                                   | -                    | 50                   |      |

| V <sub>ESD(HBM)</sub>              | Electrostatic discharge voltage<br>(human body model)                                          | see Section 6.3.11   |                      |      |

| Table 17 | Voltage | characteristics |

|----------|---------|-----------------|

|----------|---------|-----------------|

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 18* for maximum allowed injected current values.

3. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and device operation.

- 2. HSI oscillator is off for this measure.

- 3. Current consumption is negligible and close to 0  $\mu$ A.

| Sumhal                     | Devinhevel                   | Typical consum         | ption, T <sub>A</sub> = 25 °C | Unit |

|----------------------------|------------------------------|------------------------|-------------------------------|------|

| Symbol                     | Peripheral                   | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V        | Unit |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                    | 1.2                           |      |

| I <sub>REFINT</sub>        | -                            | 1.3                    | 1.4                           | -    |

| -                          | LSE Low drive <sup>(2)</sup> | 0.1                    | 0.1                           |      |

| -                          | LSI                          | 0.27                   | 0.31                          |      |

| -                          | IWDG                         | 0.2                    | 0.3                           |      |

| -                          | LPTIM1, Input 100 Hz         | 0.01                   | 0.01                          | μΑ   |

| -                          | LPTIM1, Input 1 MHz          | 6                      | 6                             |      |

| -                          | LPUART1                      | 0.2                    | 0.2                           |      |

| -                          | RTC (LSE in Bypass<br>mode)  | 0.2                    | 0.2                           | ]    |

| Table 35. Perip | oheral current   | consumption | in Sto | n and Stan | dby mode <sup>(1)</sup> |

|-----------------|------------------|-------------|--------|------------|-------------------------|

|                 | Jileiai cuiteili | consumption |        | p and Stan | uby mode                |

1. LPTIM, LPUART peripherals can operate in Stop mode but not in Standby mode

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

# 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 20*.

|                                 |                                                                                |                                           | Value              |         |

|---------------------------------|--------------------------------------------------------------------------------|-------------------------------------------|--------------------|---------|

| Symbol                          | Parameter                                                                      | Conditions                                | Min <sup>(1)</sup> | Unit    |

|                                 | Cycling (erase / write)<br>Program memory                                      | −T <sub>A</sub> = -40°C to 105 °C         | 10                 |         |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>EEPROM data memory                                  | $T_{A} = -40 \text{ C to } 105 \text{ C}$ | 100                | kovoles |

| INCYC (                         | Cycling (erase / write)<br>Program memory                                      | -T <sub>A</sub> = -40°C to 125 °C         | 0.2                | kcycles |

|                                 | Cycling (erase / write)<br>EEPROM data memory                                  | TA+0 C 10 125 C                           | 2                  |         |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C  | -Т <sub>вет</sub> = +85 °С                | 30                 | years   |

|                                 | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$ | 1 RET = 105 0                             | 30                 |         |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C | - T <sub>RFT</sub> = +105 °C              |                    |         |

| 'RET`                           | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 105$ °C        | TRET - +103 C                             | 10                 |         |

|                                 | Data retention (program memory) after<br>200 cycles at T <sub>A</sub> = 125 °C | - T <sub>RET</sub> = +125 °C              | 10                 |         |

|                                 | Data retention (EEPROM data memory) after 2 kcycles at $T_A = 125 \ ^{\circ}C$ | RET - 123 C                               |                    |         |

| Table 47. Flash memory | y and data EEPROM endurance and retention |

|------------------------|-------------------------------------------|

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                           | Monitored<br>frequency band | Max vs.<br>f <sub>OSC</sub> /f <sub>CPU</sub><br>8 MHz/32 MHz | Unit |

|------------------|------------|------------------------------------------------------|-----------------------------|---------------------------------------------------------------|------|

|                  |            | V                                                    | 0.1 to 30 MHz               | -10                                                           |      |

| 6                | Peak level | $V_{DD} = 3.6 \text{ V},$<br>T <sub>A</sub> = 25 °C, | 30 to 130 MHz               | 5                                                             | dBµV |

| S <sub>EMI</sub> | reak level | LQFP48 package                                       | 130 MHz to 1GHz             | -5                                                            |      |

|                  |            | conforming to IEC61967-2                             | EMI Level                   | 1.5                                                           | -    |

#### Table 49. EMI characteristics

# 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                               | Conditions                                                     | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/JEDEC JS-001  | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/ESD STM5.3.1. | C4    | 500                             | V    |

Table 50. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125 \text{ °C conforming to JESD78A}$ | II level A |

| Table 51 | Electrical | sensitivities |

|----------|------------|---------------|

|          |            | ••••••        |

# 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 52.

|                  |                                                              | Functional s       |                    |      |

|------------------|--------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                  | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                    | -0                 | NA                 |      |

|                  | Injected current on PA0, PA2, PA4, PA5,<br>PC15, PH0 and PH1 | -5                 | 0                  | mA   |

| I <sub>INJ</sub> | Injected current on any other FT and FTf pin                 | -5 <sup>(1)</sup>  | NA                 | ma   |

|                  | Injected current on any other pin                            | -5 <sup>(1)</sup>  | +5                 |      |

#### Table 52. I/O current injection susceptibility

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

## **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 54* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 20*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                                                                                         | Min                   | Max  | Unit |

|-----------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup> ,<br>I <sub>IO</sub> = +8 mA                                              | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin | $1_{O} = +0.11$ A<br>2.7 V $\leq V_{DD} \leq 3.6$ V                                                | V <sub>DD</sub> -0.4  | -    |      |

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin  | TTL port <sup>(2)</sup> ,<br>$I_{IO}$ =+ 8 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V         | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | TTL port <sup>(2)</sup> ,<br>$I_{IO} = -6 \text{ mA}$<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | $I_{IO}$ = +15 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                     | -                     | 1.3  | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> = -15 mA<br>2.7 V ≤V <sub>DD</sub> ≤ 3.6 V                                         | V <sub>DD</sub> -1.3  | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +4 mA<br>1.65 V ≤V <sub>DD</sub> < 3.6 V                                         | -                     | 0.45 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> = -4 mA<br>1.65 V ≤V <sub>DD</sub> ≤ 3.6 V                                         | V <sub>DD</sub> -0.45 | -    |      |

| V (1)(4)                          | Output low level voltage for an FTf      | $I_{IO} = 20 \text{ mA}$ $2.7 \text{ V} \leq V_{DD} \leq 3.6 \text{ V}$                            | -                     | 0.4  |      |

| VOLFM+ I/O pin in Fm+ mode        |                                          | $I_{IO}$ = 10 mA<br>1.65 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                     | -                     | 0.4  |      |

The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 18*. The sum of the currents sunk by all the I/Os (I/O ports and control pins) must always be respected and must not exceed ΣI<sub>IO(PIN)</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 18. The sum of the currents sourced by all the I/Os (I/O ports and control pins) must always be respected and must not exceed  $\Sigma I_{IO(PIN)}$ .

4. Guaranteed by characterization results.

| Symbol              | Parameter                                     | Conditions                                                                                                                  | Min  | Тур | Max <sup>(1)</sup> | Unit       |

|---------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                           | 1.65 | -   | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                           | 0    | -   | V <sub>DDA</sub>   | V          |

| +.                  | Comparator startup time                       | Fast mode                                                                                                                   | -    | 15  | 20                 |            |

| t <sub>start</sub>  |                                               | Slow mode                                                                                                                   | -    | 20  | 25                 |            |

| +                   | Propagation delay <sup>(2)</sup> in slow mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                             | -    | 1.8 | 3.5                |            |

| t <sub>d slow</sub> |                                               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                              | -    | 2.5 | 6                  | μs         |

| +                   | Propagation delay <sup>(2)</sup> in fast mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                             | -    | 0.8 | 2                  |            |

| t <sub>d fast</sub> | Fropagation delay in last mode                | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                              | -    | 1.2 | 4                  |            |

| V <sub>offset</sub> | Comparator offset error                       |                                                                                                                             | -    | ±4  | ±20                | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V$ $T_{A} = 0 \text{ to } 50 \circ C$ $V = V_{REFINT},$ $3/4 V_{REFINT},$ $1/2 V_{REFINT},$ $1/4 V_{REFINT}.$ | -    | 15  | 30                 | ppm<br>/°C |

| 1                   | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                   | -    | 3.5 | 5                  |            |

| I <sub>COMP2</sub>  |                                               | Slow mode                                                                                                                   | -    | 0.5 | 2                  | μA         |

Table 63. Comparator 2 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (necessary for comparator operation) is not included.

# 6.3.18 Timer characteristics

#### **TIM timer characteristics**

The parameters given in the *Table 64* are guaranteed by design.

Refer to *Section 6.3.13: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                | Parameter               | Conditions                    | Min   | Мах                     | Unit                 |

|-----------------------|-------------------------|-------------------------------|-------|-------------------------|----------------------|

| t                     | Timer resolution time   |                               | 1     | -                       | t <sub>TIMxCLK</sub> |

| <sup>(</sup> res(TIM) |                         | f <sub>TIMxCLK</sub> = 32 MHz | 31.25 | -                       | ns                   |

| f                     | Timer external clock    |                               | 0     | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>      | frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 32 MHz | 0     | 16                      | MHz                  |

| Res <sub>TIM</sub>    | Timer resolution        | -                             |       | 16                      | bit                  |

Table 64. TIMx<sup>(1)</sup> characteristics

#### **SPI characteristics**

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 20*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                            | Conditions                                               | Min     | Тур   | Max               | Unit |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------|---------|-------|-------------------|------|

|                                              |                                      | Master mode                                              |         |       | 16                |      |

|                                              |                                      | Slave mode receiver                                      | 1 -     | -     | 16                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 12 <sup>(2)</sup> | MHz  |

|                                              |                                      | Slave mode Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                               | 30      | 50    | 70                | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                | 4*Tpclk | -     | -                 |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                | 2*Tpclk | -     | -                 |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2           |      |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                              | 8.5     | -     | -                 |      |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                                               | 8.5     | -     | -                 |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                              | 6       | -     | -                 |      |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                               | 1       | -     | -                 | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                               | 15      | -     | 36                |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                               | 10      | -     | 30                |      |

| +                                            |                                      | Slave mode 1.71 <v<sub>DD&lt;3.6V</v<sub>                | -       | 29    | 41                |      |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode 2.7 <v<sub>DD&lt;3.6V</v<sub>                 | -       | 22    | 28                |      |

| t <sub>v(MO)</sub>                           |                                      | Master mode                                              | -       | 10    | 17                |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                                               | 9       | -     | -                 |      |

| t <sub>h(MO)</sub>                           |                                      | Master mode                                              | 3       | -     | -                 |      |

| Table 67. SPI characteristics | cs in voltage Range 1 <sup>(1)</sup> |

|-------------------------------|--------------------------------------|

|-------------------------------|--------------------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{y(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур   | Max   | Min                   | Тур    | Max    |  |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| Е      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| E3     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

| Table 70. LQFP48 - 48-pin low-profile quad flat package, 7 x 7 mm, package |

|----------------------------------------------------------------------------|

| mechanical data                                                            |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

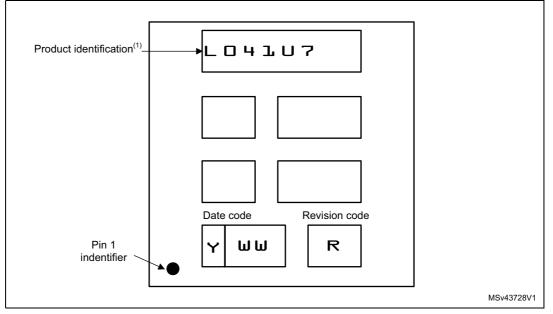

## **UFQFPN28** device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Figure 45. Example of UFQFPN28 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

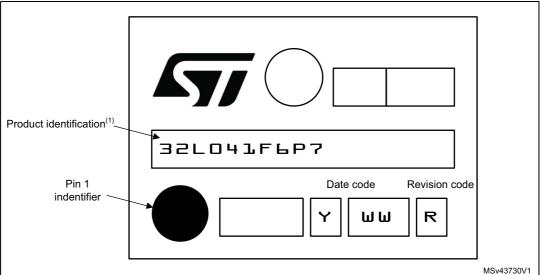

#### **TSSOP20** device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

Other optional marking or inset/upset marks, which depends assembly location, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10-Nov-2015 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 14-Mar-2016 | 2        | Updated number of SPI interfaces on cover page and in <i>Table 2:</i><br><i>Ultra-low-power STM32L041x4/x6 device features and peripheral</i><br><i>counts.</i><br>Updated number of GPIOs for devices in UFQFPN28 in <i>Table 2:</i><br><i>Ultra-low-power STM32L041x4/x6 device features and peripheral</i><br><i>counts.</i><br>Updated Section 3.4.4: Boot modes.<br>Updated Section 3.16.2: Universal synchronous/asynchronous<br><i>receiver transmitter (USART)</i> and Section 3.16.4: Serial<br><i>peripheral interface (SPI)</i> to mention the fact that USARTs with<br>synchronous mode feature can be used as SPI master interfaces.<br>Modified pin 2 in <i>Figure 5: STM32L041x4/6 UFQFPN32 pinout.</i><br>Added <i>Figure 7: STM32L041GxUxS UFQFPN28 pinout.</i><br><i>Table 15: Pin definitions:</i><br>– Added UFQFPN28 for STM32L041GxUxS part number.<br>– Renamed PA0-WKUP-CK_IN into PA0-CK_IN<br>– Renamed PA0-WKUP into PA0<br>Updated <i>Table 18: Current characteristics</i> to add the total output<br><i>current for STM32L031GxUxS.</i><br>Added one power pair option in <i>Table 78: STM32L041x4/6 order-<br/>ing information scheme.</i> |  |

#### Table 79. Document revision history