# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST10                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | CANbus, EBI/EMI, SSC, UART/USART                                       |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 111                                                                    |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | ROMIess                                                                |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 144-BQFP                                                               |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st10r167-q3-tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# II - PIN DATA (continued)

Table 1 : Pin list

| Symbol                       | Pin                              | Туре                 | Function                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|------------------------------|----------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P6.0 - P6.7                  | 1 - 8                            | I/O                  | 8-bit bidirectional I/O port, bit-wise programmable for input or output via direction bits. Programming an I/O pin as input forces the corresponding output driver to high impedance state. Port 6 outputs can be configured as push/pull or open drain drivers. The following Port 6 pins have alternate functions:                                                               |  |  |

|                              | 1                                | 0                    | P6.0 CS0 Chip Select 0 Output                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                              | 5<br>6<br>7<br>8                 | <br>0<br>1<br>0<br>0 | P6.4 CS4 Chip Select 4 Output   P6.5 HOLD External Master Hold Request Input   P6.6 HLDA Hold Acknowledge Output   P6.7 BREQ Bus Request Output                                                                                                                                                                                                                                    |  |  |

| P8.0 - P8.7                  | 9 - 16                           | I/O                  | 8-bit bidirectional I/O port, bit-wise programmable for input or output via direction bits. Programming an I/O pin as input forces the corresponding output driver to high impedance state. Port 8 outputs can be configured as push/pull or open drain drivers. The input threshold of Port 8 is selectable (TTL or special). The following Port 8 pins have alternate functions: |  |  |

|                              | 9                                | I/O                  | P8.0 CC16IO CAPCOM2: CC16 Capture Input/Compare Output                                                                                                                                                                                                                                                                                                                             |  |  |

|                              | <br>16                           | <br>I/O              | P8.7 CC23IO CAPCOM2: CC23 Capture Input/Compare Output                                                                                                                                                                                                                                                                                                                             |  |  |

| P7.0 - P7.7                  | 19 - 26                          | I/O                  | 8-bit bidirectional I/O port, bit-wise programmable for input or output via direction bits. Programming an I/O pin as input forces the corresponding output driver to high impedance state. Port 7 outputs can be configured as push/pull or open drain drivers. The input threshold of Port 7 is selectable (TTL or special). The following Port 7 pins have alternate functions: |  |  |

|                              | 19                               | 0                    | P7.0 POUT0 PWM Channel 0 Output                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                              | <br>22<br>23                     | <br>O<br>I/O         | P7.3 POUT3 PWM Channel 3 Output<br>P7.4 CC28IO CAPCOM2: CC28 Capture Input/Compare Output                                                                                                                                                                                                                                                                                          |  |  |

|                              | <br>26                           | <br>I/O              | P7.7 CC31IO CAPCOM2: CC31 Capture Input/Compare Output                                                                                                                                                                                                                                                                                                                             |  |  |

| P5.0 - P5.9<br>P5.10 - P5.15 | 27 - 36<br>39 - 44               | 1                    | Port 5 is a 16-bit input-only port with Schmitt-Trigger characteristics. The pins of Port 5 also serve as the (up to 16) analog input channels for the A/ D converter, where P5.x equals ANx (Analog input channel x), or they serve as timer inputs:                                                                                                                              |  |  |

|                              | 39<br>40<br>41<br>42<br>43<br>44 |                      | P5.10T6EUDGPT2 Timer T6 External Up/Down Control InputP5.11T5EUDGPT2 Timer T5 External Up/Down Control InputP5.12T6INGPT2 Timer T6 Count InputP5.13T5INGPT2 Timer T5 Count InputP5.14T4EUDGPT1 Timer T4 External Up/Down Control InputP5.15T2EUDGPT1 Timer T2 External Up/Down Control Input                                                                                       |  |  |

## **IV - MEMORY ORGANIZATION**

The memory space of the ST10R167 is configured in a Von-Neumann architecture. Code memory, data memory, registers and I/O ports are organized within the same linear address space of 16M Byte.

The entire memory space can be accessed Bytewise or Wordwise. Particular portions of the on-chip memory have additionally been made directly bit addressable.

**ROM**: 32K Byte of on-chip ROM.

**RAM** : 2K Byte of on-chip internal RAM (dual-port) is provided as a storage for data, system stack, general purpose register banks and code. The register bank can consist of up to 16 wordwide (R0 to R15) and/or Bytewide (RL0, RH0, ..., RL7, RH7) general purpose registers.

**XRAM :** 2K Byte of on-chip extension RAM (single port XRAM) is provided as a storage for data, user stack and code.

The XRAM is connected to the internal XBUS and is accessed like an external memory in 16-bit demultiplexed bus-mode without waitstate or read/write delay (80ns access at 25MHz CPU clock). Byte and Word access is allowed.

The XRAM address range is 00'E000h -00'E7FFh if the XRAM is enabled (XPEN bit 2 of SYSCON register). As the XRAM appears like external memory, it cannot be used for the ST10R167's system stack or register banks. The

XRAM is not provided for single bit storage and therefore is not bit addressable. If bit XRAMEN is cleared, then any access in the address range 00'E000h - 00'E7FFh will be directed to external memory interface, using the BUSCONx register corresponding to address matching ADDRSELx register.

**SFR/ESFR** : 1024 Byte (2 \* 512 Byte) of address space is reserved for the special function register areas. SFRs are wordwide registers which are used for controlling and monitoring functions of the different on-chip units.

**CAN** : Address range 00'EF00h - 00'EFFFh is reserved for the CAN Module access. The CAN is enabled by setting XPEN bit 2 of the SYSCON register. Accesses to the CAN Module use demultiplexed addresses and a 16-bit data bus (Byte accesses are possible). Two wait states give an access time of 160ns at 25MHz CPU clock. No tristate waitstate is used.

Note If the CAN module is used, Port 4 can not be programmed to output all 8 segment address lines. Thus, only 4 segment address lines can be used, reducing the external memory space to 5M Byte (1M Byte per CS line).

In order to meet the needs of designs where more memory is required than is provided on chip, up to 16M Byte of external RAM and/or ROM can be connected to the microcontroller.

## VII - INTERRUPT SYSTEM

The interrupt response time for internal program execution is from 200ns to 480ns.

The ST10R167 architecture supports several mechanisms for fast and flexible response to service requests that can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is suspended and a branch to the interrupt vector table is performed. just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single Byte or Word data transfer between any two memory locations with an additional increment of either the PEC source or the destination pointer. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source related vector location. PEC services are very well suited, for example, for supporting the transmission or reception of blocks of data. The ST10R167 has 8 PEC channels each of which offers such fast interrupt-driven data transfer capabilities.

A interrupt control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield is dedicated to each existing interrupt source. Thanks to its related register, each source can be programmed to one of sixteen interrupt priority levels. Once starting to be processed by the CPU, an interrupt service can only be interrupted by a higher prioritized service request. For the standard interrupt processing, each of the possible interrupt sources has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

Table 2 shows all the available ST10R167 interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers :

<u>ل ۲</u>۸

| Source of Interrupt or PEC<br>Service Request | Request<br>Flag | Enable<br>Flag | Interrupt<br>Vector | Vector<br>Location | Trap<br>Number |

|-----------------------------------------------|-----------------|----------------|---------------------|--------------------|----------------|

| CAPCOM Register 0                             | CC0IR           | CC0IE          | CC0INT              | 00'0040h           | 10h            |

| CAPCOM Register 1                             | CC1IR           | CC1IE          | CC1INT              | 00'0044h           | 11h            |

| CAPCOM Register 2                             | CC2IR           | CC2IE          | CC2INT              | 00'0048h           | 12h            |

| CAPCOM Register 3                             | CC3IR           | CC3IE          | CC3INT              | 00'004Ch           | 13h            |

| CAPCOM Register 4                             | CC4IR           | CC4IE          | CC4INT              | 00'0050h           | 14h            |

| CAPCOM Register 5                             | CC5IR           | CC5IE          | CC5INT              | 00'0054h           | 15h            |

| CAPCOM Register 6                             | CC6IR           | CC6IE          | CC6INT              | 00'0058h           | 16h            |

| CAPCOM Register 7                             | CC7IR           | CC7IE          | CC7INT              | 00'005Ch           | 17h            |

| CAPCOM Register 8                             | CC8IR           | CC8IE          | CC8INT              | 00'0060h           | 18h            |

| CAPCOM Register 9                             | CC9IR           | CC9IE          | CC9INT              | 00'0064h           | 19h            |

| CAPCOM Register 10                            | CC10IR          | CC10IE         | CC10INT             | 00'0068h           | 1Ah            |

| CAPCOM Register 11                            | CC11IR          | CC11IE         | CC11INT             | 00'006Ch           | 1Bh            |

| CAPCOM Register 12                            | CC12IR          | CC12IE         | CC12INT             | 00'0070h           | 1Ch            |

| CAPCOM Register 13                            | CC13IR          | CC13IE         | CC13INT             | 00'0074h           | 1Dh            |

| CAPCOM Register 14                            | CC14IR          | CC14IE         | CC14INT             | 00'0078h           | 1Eh            |

| CAPCOM Register 15                            | CC15IR          | CC15IE         | CC15INT             | 00'007Ch           | 1Fh            |

| CAPCOM Register 16                            | CC16IR          | CC16IE         | CC16INT             | 00'00C0h           | 30h            |

| CAPCOM Register 17                            | CC17IR          | CC17IE         | CC17INT             | 00'00C4h           | 31h            |

Table 2 : Interrupt sources

## IX - GENERAL PURPOSE TIMER UNIT (continued)

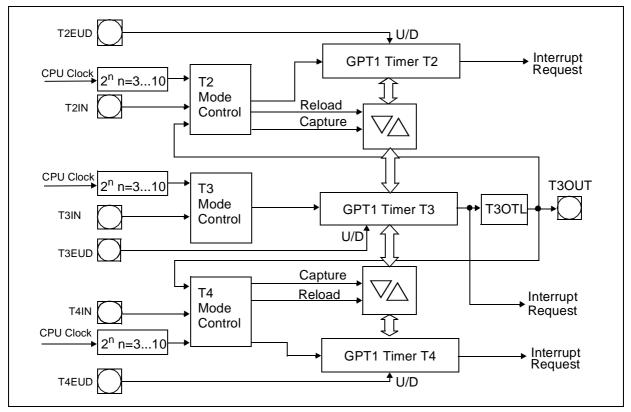

Figure 5 : Block diagram of GPT1

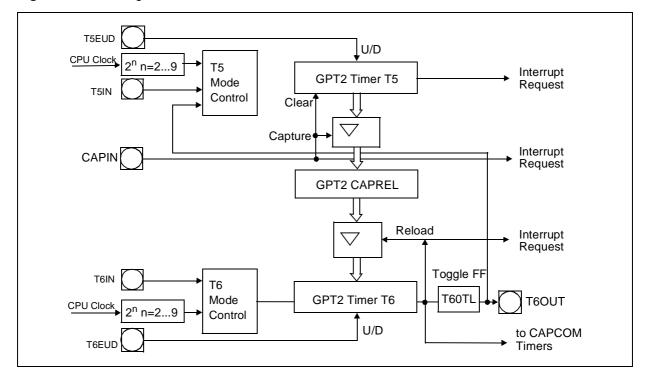

## IX.2 - GPT2

The GPT2 module provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD). Concatenation of the timers is supported via the output toggle latch (T6OTL) of timer T6 which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, or it may be output on a port pin (T6OUT). The overflows/underflows of timer T6 can additionally be used to clock the CAPCOM timers T0 or T1, and to cause a reload from the CAPREL register.

The CAPREL register may capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN), and timer T5 may optionally be cleared after the capture procedure. This allows absolute time differences to be measured or pulse multiplication to be performed without software overhead.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer T3 inputs T3IN and/or T3EUD. This is advantageous when T3 operates in Incremental Interface Mode.

Table 7 lists the timer input frequencies, resolution and periods for each pre-scaler option at 25MHz CPU clock.

This also applies to the Gated Timer Mode of T6 and to the auxiliary timer T5 in Timer and Gated Timer Mode.

# IX - GENERAL PURPOSE TIMER UNIT (continued)

Table 7 : GPT2 timer input frequencies, resolution and periods

| f <sub>CPU</sub> = 25MHz | Timer Input Selection T5I / T6I |          |          |          |          |          |          |          |  |  |

|--------------------------|---------------------------------|----------|----------|----------|----------|----------|----------|----------|--|--|

| 1CPU <b>- 201112</b>     | 000B                            | 001B     | 010B     | 011B     | 100B     | 101B     | 110B     | 111B     |  |  |

| Pre-scaler factor        | 4                               | 8        | 16       | 32       | 64       | 128      | 256      | 512      |  |  |

| Input Frequency          | 6.25MHz                         | 3.125MHz | 1.563MHz | 781.3KHz | 390.6KHz | 195.3KHz | 97.66KHz | 48.83KHz |  |  |

| Resolution               | 160ns                           | 320ns    | 640ns    | 1.28µs   | 2.56µs   | 5.12µs   | 10.24µs  | 20.48µs  |  |  |

| Period                   | 10.49ms                         | 21.0ms   | 41.9ms   | 83.9ms   | 167ms    | 336ms    | 671ms    | 1.34s    |  |  |

Figure 6 : Block diagram of GPT2

# **X - PWM MODULE**

57

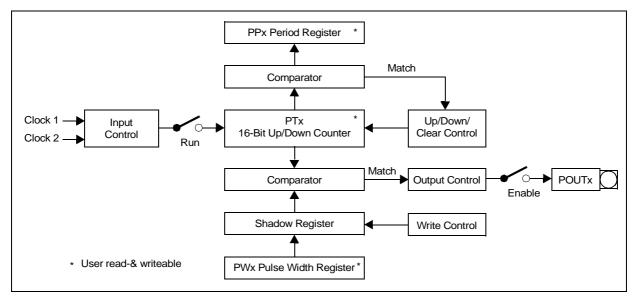

The pulse width modulation module can generate up to four PWM output signals using edge-aligned or centre-aligned PWM. In addition, the PWM module can generate PWM burst signals and single shot outputs. Table 8 shows the PWM frequencies for different resolutions. The level of the output signals is selectable and the PWM module can generate interrupt requests.

| Table 8 : PWM unit freq | uencies and resolution at 25MHz clock |

|-------------------------|---------------------------------------|

|-------------------------|---------------------------------------|

| Mode 0       | Resolution | 8-bit    | 10-bit   | 12-bit   | 14-bit   | 16-bit   |

|--------------|------------|----------|----------|----------|----------|----------|

| CPU Clock/1  | 40ns       | 97.66KHz | 24.41KHz | 6.104KHz | 1.526KHz | 0.381KHz |

| CPU Clock/64 | 2.56ns     | 1.526KHz | 381.5Hz  | 95.37Hz  | 23.84Hz  | 5.96Hz   |

| Mode 1       | Resolution | 8-bit    | 10-bit   | 12-bit   | 14-bit   | 16-bit   |

| CPU Clock/1  | 40ns       | 48.82KHz | 12.20KHz | 3.05KHz  | 762.9Hz  | 190.7Hz  |

| CPU Clock/64 | 2.56ns     | 762.9Hz  | 190.7 Hz | 47.68Hz  | 11.92Hz  | 2.98Hz   |

Figure 7 : Block diagram of PWM module

## **XI - PARALLEL PORTS**

The ST10R167 provides up to 111 I/O lines organized into eight input/output ports and one input port.

All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as input or output via direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs.

The output drivers of five I/O ports can be configured (pin by pin) for push/pull operation or open-drain operation via control registers. During the internal reset, all port pins are configured as inputs.

The input threshold of Port 2, Port 3, Port 7 and Port 8 is selectable (TTL-or CMOS-like), where the special CMOS-like input threshold reduces noise sensitivity due to the input hysteresis.

The input thresholds are selected with bit of PICON register dedicated to blocks of 8 input pins (2-bit for port2, 2-bit for port3, 1-bit for port7, 1-bit for port8).

All pins of I/O ports also support an alternate programmable function:

- Port0 and Port1 may be used as address and data lines when accessing external memory.

- Port 2, Port 7 and Port 8 are associated with the capture inputs or with the compare outputs of the CAPCOM units and/or with the outputs of the PWM module.

- Port 3 includes the alternate functions of timers, serial interfaces, the optional bus control signal BHE and the system clock output (CLKOUT).

- Port 4 outputs the additional segment address bits A16 to A23 in systems where segmentation is enabled to access more than 64K Byte of memory.

- Port 5 is used as analog input channels of the A/D converter or as timer control signals.

- Port 6 provides optional bus arbitration signals (BREQ, HLDA, HOLD) and chip select signals.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

Ĺ₹/

## **XII - A/D CONVERTER**

A10-bit A/D converter with 16 multiplexed input channels and a sample and hold circuit is integrated on-chip. The sample time (for loading the capacitors) and the conversion time is programmable and can be adjusted to the external circuitry. Overrun error detection/protection is controlled by the ADDAT register. Either an interrupt request is generated when the result of a previous conversion has not been read from the result register at the time the next conversion is complete, or the next conversion is suspended until the previous result has been read. For applications which require less than 16 analog input channels, the remaining channel inputs can be used as digital input port pins. The AD converter of the ST10F168 supports different conversion modes :

- Single channel single conversion : the analog level of the selected channel is sampled once and converted. The result of the conversion is stored in the ADDAT register.

- Single channel continuous conversion : the analog level of the selected channel is repeatedly sampled and converted. The result of the conversion is stored in the ADDAT register.

- Auto scan single conversion : the analog level of the selected channels are sampled once and converted. After each conversion the result is stored in the ADDAT register. The data can be transfered to the RAM by interrupt software management or using the powerfull Peripheral Event Controller data transfert.

- Auto scan continuous conversion : the analog level of the selected channels are repeatedly sampled and converted. The result of the conversion is stored in the ADDAT register. The data can be transfered to the RAM by interrupt software management or using the powerfull Peripheral Event Controller data transfert.

- Wait for ADDAT read mode : when using continuous modes, in order to avoid to overwrite the result of the current conversion by the next one, the ADWR bit of ADCON control register

must be activated. Then, until the ADDAT register is read, the new result is stored in a temporary buffer and the conversion is on hold.

- Channel injection mode : when using continuous modes, a selected channel can be converted in between without changing the current operating mode. The 10 bit data of the conversion are stored in ADRES field of ADDAT2. The current continuous mode remains active after the single conversion is completed.

The Table : 9 ADC sample clock and conversion time shows the ADC unit conversion clock, sample clock.

A complete conversion will take  $14t_{CC} + 2 t_{SC} + 4$  TCL. This time includes the conversion it-self, the sampling time and the time required to transfer the digital value to the result register. For example, at 25MHz of CPU clock, minimum complete conversion time is 7.76 $\mu$ s.

The A/D converter provides automatic offset and linearity self calibration. The calibration operation is performed in two ways:

- A full calibration sequence is performed after a reset and lasts 1.6ms minimum (at 25MHz CPU clock). During this time, the ADBSY flag is set to indicate the operation. Normal conversion can be performed during this time. The duration of the calibration sequence is then extended by the time consumed by the conversions.

Note : After a power-on reset, the total unadjusted error (TUE) of the ADC might be worse than  $\pm 2LSB$  (max.  $\pm 4LSB$ ). During the full calibration sequence, the TUE is constantly improved until at the end of the cycle, TUE is within the specified limits of  $\pm 2LSB$ .

One calibration cycle is performed after each conversion : each calibration cycle takes 4 ADC clock cycles. These operation cycles ensure constant updating of the ADC accuracy, compensating changing operating conditions.

| ADOTO | Conversion C                  | Clock t <sub>CC</sub>       | ADSTO | Sample Clock t <sub>SC</sub> |                             |  |

|-------|-------------------------------|-----------------------------|-------|------------------------------|-----------------------------|--|

| ADCTC | $TCL^1 = 1/2 \times f_{XTAL}$ | At f <sub>CPU</sub> = 25MHz | ADSTC | -                            | At f <sub>CPU</sub> = 25MHz |  |

| 00    | TCL x 24                      | 0.48µs                      | 00    | t <sub>CC</sub>              | 0.48µs <sup>2</sup>         |  |

| 01    | Reserved, do not use          | -                           | 01    | t <sub>CC</sub> x 2          | 0.96µs <sup>2</sup>         |  |

| 10    | TCL x 96                      | 1.92µs                      | 10    | t <sub>CC</sub> x 4          | 1.92µs <sup>2</sup>         |  |

| 11    | TCL x 48                      | 0.96µs                      | 11    | t <sub>CC</sub> x 8          | 3.84µs <sup>2</sup>         |  |

Note 1. See chapter XX. 2.  $t_{CC} = TCL \times 24$ .

# XIX - SPECIAL FUNCTION REGISTER OVERVIEW (continued)

| Table 14 : Special function registers listed by name ( | (continued) |

|--------------------------------------------------------|-------------|

|                                                        |             |

| Nan    | Name Physical<br>address |       | Name |     | 8-bit<br>address                              | Description | Reset value |

|--------|--------------------------|-------|------|-----|-----------------------------------------------|-------------|-------------|

| CC8IC  | b                        | FF88h |      | C4h | CAPCOM Register 8 Interrupt Control Register  | 0000h       |             |

| CC9    |                          | FE92h |      | 49h | CAPCOM Register 9                             | 0000h       |             |

| CC9IC  | b                        | FF8Ah |      | C5h | CAPCOM Register 9 Interrupt Control Register  | 0000h       |             |

| CC10   |                          | FE94h |      | 4Ah | CAPCOM Register 10                            | 0000h       |             |

| CC10IC | b                        | FF8Ch |      | C6h | CAPCOM Register 10 Interrupt Control Register | 0000h       |             |

| CC11   |                          | FE96h |      | 4Bh | CAPCOM Register 11                            | 0000h       |             |

| CC11IC | b                        | FF8Eh |      | C7h | CAPCOM Register 11 Interrupt Control Register | 0000h       |             |

| CC12   |                          | FE98h |      | 4Ch | CAPCOM Register 12                            | 0000h       |             |

| CC12IC | b                        | FF90h |      | C8h | CAPCOM Register 12 Interrupt Control Register | 0000h       |             |

| CC13   |                          | FE9Ah |      | 4Dh | CAPCOM Register 13                            | 0000h       |             |

| CC13IC | b                        | FF92h |      | C9h | CAPCOM Register 13 Interrupt Control Register | 0000h       |             |

| CC14   |                          | FE9Ch |      | 4Eh | CAPCOM Register 14                            | 0000h       |             |

| CC14IC | b                        | FF94h |      | CAh | CAPCOM Register 14 Interrupt Control Register | 0000h       |             |

| CC15   |                          | FE9Eh |      | 4Fh | CAPCOM Register 15                            | 0000h       |             |

| CC15IC | b                        | FF96h |      | CBh | CAPCOM Register 15 Interrupt Control Register | 0000h       |             |

| CC16   |                          | FE60h |      | 30h | CAPCOM Register 16                            | 0000h       |             |

| CC16IC | b                        | F160h | Е    | B0h | CAPCOM Register 16 Interrupt Control Register | 0000h       |             |

| CC17   |                          | FE62h |      | 31h | CAPCOM Register 17                            | 0000h       |             |

| CC17IC | b                        | F162h | Е    | B1h | CAPCOM Register 17 Interrupt Control Register | 0000h       |             |

| CC18   |                          | FE64h |      | 32h | CAPCOM Register 18                            | 0000h       |             |

| CC18IC | b                        | F164h | Е    | B2h | CAPCOM Register 18 Interrupt Control Register | 0000h       |             |

| CC19   |                          | FE66h |      | 33h | CAPCOM Register 19                            | 0000h       |             |

| CC19IC | b                        | F166h | Е    | B3h | CAPCOM Register 19 Interrupt Control Register | 0000h       |             |

| CC20   |                          | FE68h |      | 34h | CAPCOM Register 20                            | 0000h       |             |

| CC20IC | b                        | F168h | Е    | B4h | CAPCOM Register 20 Interrupt Control Register | 0000h       |             |

| CC21   |                          | FE6Ah |      | 35h | CAPCOM Register 21                            | 0000h       |             |

| CC21IC | b                        | F16Ah | Е    | B5h | CAPCOM Register 21 Interrupt Control Register | 0000h       |             |

| CC22   |                          | FE6Ch |      | 36h | CAPCOM Register 22                            | 0000h       |             |

| CC22IC | b                        | F16Ch | Е    | B6h | CAPCOM Register 22 Interrupt Control Register | 0000h       |             |

| CC23   |                          | FE6Eh |      | 37h | CAPCOM Register 23                            | 0000h       |             |

| CC23IC | b                        | F16Eh | Е    | B7h | CAPCOM Register 23 Interrupt Control Register | 0000h       |             |

| CC24   |                          | FE70h |      | 38h | CAPCOM Register 24                            | 0000h       |             |

| CC24IC | b                        | F170h | Е    | B8h | CAPCOM Register 24 Interrupt Control Register | 0000h       |             |

| CC25   |                          | FE72h |      | 39h | CAPCOM Register 25                            | 0000h       |             |

| CC25IC | b                        | F172h | Е    | B9h | CAPCOM Register 25 Interrupt Control Register | 0000h       |             |

| CC26   |                          | FE74h |      | 3Ah | CAPCOM Register 26                            | 0000h       |             |

| CC26IC | b                        | F174h | Е    | BAh | CAPCOM Register 26 Interrupt Control Register | 0000h       |             |

| CC27   |                          | FE76h |      | 3Bh | CAPCOM Register 27                            | 0000h       |             |

## **XX - ELECTRICAL CHARACTERISTICS**

#### XX.1 - Absolute maximum ratings

| Symbol           | Parameter                                                    | Value                        | Unit |

|------------------|--------------------------------------------------------------|------------------------------|------|

| V <sub>SS</sub>  | Voltage on $V_{DD}$ pins with respect to ground              | -0.5, +6.5                   | V    |

| V <sub>SS</sub>  | Voltage on any pin with respect to ground                    | -0.3 to V <sub>DD</sub> +0.3 | V    |

|                  | Input current on any pin during overload condition           | -10, +10                     | mA   |

|                  | Absolute sum of all input currents during overload condition | 100                          | mA   |

| P <sub>tot</sub> | Power Dissipation                                            | 1.5                          | W    |

| T <sub>amb</sub> | Ambient Temperature under bias                               | -40, +125                    | °C   |

| T <sub>stg</sub> | Storage Temperature                                          | -65, +150                    | °C   |

Note Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions ( $V_{IN}$ > $V_{DD}$  or  $V_{IN}$ < $V_{SS}$ ) the voltage on pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the Absolute Maximum Ratings.

## XX.2 - Parameter interpretation

The parameters listed in the following tables represent the characteristics of the ST10C167 and its demands on the system. Where the ST10C167 logic provides signals with their respective timing characteristics, the symbol "CC"

for Controller Characteristics is included in the "Symbol" column.

Where the external system must provide signals with their respective timing characteristics to the ST10C167, the symbol "SR" for System Requirement is included in the "Symbol" column.

**لر ج**لاً

Notes 1. VAIN may exceed VAGND or VAREF up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

2. During the sample time the input capacitance  $C_1$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within ts. After the end of the sample time ts, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>SC</sub> depend on programming and can be taken from the table above.

3. This parameter includes the sample time  $t_{s}$ , the time for determining the digital result and the time to load the result register with the conversion result. Values for the conversion clock t<sub>CC</sub> depend on programming and can be taken from the table above.

4. This parameter is fixed by ADC control logic.

5. TUE is tested at V<sub>AREF</sub> = 5.0V, V<sub>AGND</sub> = 0V, V<sub>CC</sub> = 4.9V. It is guaranteed by design characterization for all other voltages within the defined voltage range. The specified TUE is guaranteed only if an overload condition (see I<sub>OV</sub> specification) occurs on maximum of 2 not selected analog input pins and the absolute sum of input overload currents on all analog input pins does not exceed 10mA. During the reset calibration sequence the maximum TUE may be ±4 LSB.

6. During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference voltage source must allow the capacitance to reach its respective voltage level within t<sub>CC</sub>. The maximum internal resistance results from the programmed conversion timing.

7. Partially tested, guaranteed by design characterization.

Sample time and conversion time of the ST10C167's ADC are programmable. The table below should be used to calculate the above timings.

| ADCON.15 14 (ADCTC) | Conversion clock $t_{CC}$ | ADCON.13 12 (ADSTC) | Sample clock $t_{SC}$          |

|---------------------|---------------------------|---------------------|--------------------------------|

| 00                  | TCL * 24                  | 00                  | tcc                            |

| 01                  | Reserved, do not use      | 01                  | t <sub>CC</sub> * 2            |

| 10                  | TCL * 96                  | 10                  | <sup>t</sup> CC <sup>* 4</sup> |

| 11                  | TCL * 48                  | 11                  | t <sub>CC</sub> * 8            |

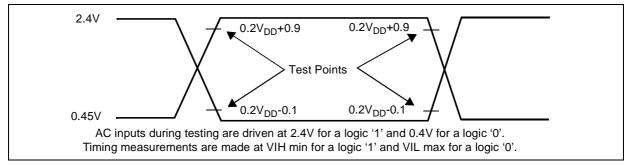

#### XX.4 - AC characteristics

#### Test waveforms

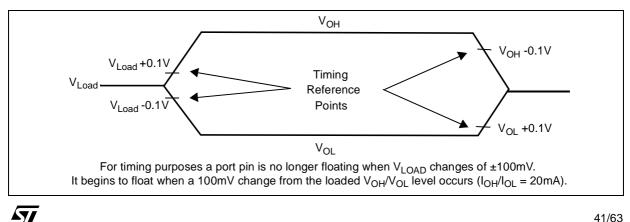

#### Figure 9 : Input output waveforms

## Figure 10 : Float waveforms

# Table 18 : Multiplexed bus characteristics (continued)

| Symbol            |    | Parameter                                                                                        |                     | CPU Clock<br>25MHz    | Variable CPU Clock<br>1/2TCL = 1 to 25MHz |                                                 | Unit |

|-------------------|----|--------------------------------------------------------------------------------------------------|---------------------|-----------------------|-------------------------------------------|-------------------------------------------------|------|

|                   |    |                                                                                                  | Min.                | Max.                  | Min.                                      | Max.                                            |      |

| t <sub>10</sub> 1 | CC | Address float after RD, WR<br>(with RW-delay)                                                    | _                   | 6                     | _                                         | 6                                               | ns   |

| t <sub>11</sub> 1 | СС | Address float after RD, WR (no RW-delay)                                                         | _                   | 26                    | _                                         | TCL + 6                                         | ns   |

| t <sub>12</sub>   | CC | RD, WR low time (with RW-delay)                                                                  | 30 + t <sub>C</sub> | _                     | 2TCL - 10 + t <sub>C</sub>                | _                                               | ns   |

| t <sub>13</sub>   | CC | RD, WR low time (no RW-delay)                                                                    | 50 + t <sub>C</sub> | -                     | 3TCL - 10 + t <sub>C</sub>                | -                                               | ns   |

| t <sub>14</sub>   | SR | RD to valid data in (with<br>RW-delay)                                                           | _                   | 20 + t <sub>C</sub>   | _                                         | 2TCL - 20+ t <sub>C</sub>                       | ns   |

| t <sub>15</sub>   | SR | RD to valid data in (no RW-delay)                                                                | -                   | 40 + t <sub>C</sub>   | _                                         | 3TCL - 20+ t <sub>C</sub>                       | ns   |

| t <sub>16</sub>   | SR | ALE low to valid data in                                                                         | -                   | $40 + t_{A} + t_{C}$  | _                                         | 3TCL - 20<br>+ t <sub>A</sub> + t <sub>C</sub>  | ns   |

| t <sub>17</sub>   | SR | Address/Unlatched CS to valid data in                                                            | _                   | $50 + 2t_A + t_C$     | _                                         | 4TCL - 30<br>+ 2t <sub>A</sub> + t <sub>C</sub> | ns   |

| t <sub>18</sub>   | SR | Data hold after RD rising edge                                                                   | 0                   | -                     | 0                                         | -                                               | ns   |

| t <sub>19</sub> 1 | SR | Data float after RD                                                                              | -                   | 26 + t <sub>F</sub>   | -                                         | 2TCL - 14 + t <sub>F</sub>                      | ns   |

| t <sub>22</sub>   | СС | Data valid to WR                                                                                 | 20 + t <sub>C</sub> | _                     | 2TCL - 20 + t <sub>C</sub>                | _                                               | ns   |

| t <sub>23</sub>   | СС | Data hold after WR                                                                               | 26 + t <sub>F</sub> | -                     | 2TCL - 14 + t <sub>F</sub>                | -                                               | ns   |

| t <sub>25</sub>   | СС | ALE rising edge after $\overline{RD}$ , $\overline{WR}$                                          | 26 + t <sub>F</sub> | -                     | 2TCL - 14 + t <sub>F</sub>                | -                                               | ns   |

| t <sub>27</sub>   | СС | $\frac{\text{Address/Unlatched }\overline{\text{CS}} \text{ hold after }}{\text{RD}, \text{WR}}$ | 26 + t <sub>F</sub> | _                     | 2TCL - 14 + t <sub>F</sub>                | _                                               | ns   |

| t <sub>38</sub>   | СС | ALE falling edge to Latched $\overline{CS}$                                                      | -4 - t <sub>A</sub> | 10 - t <sub>A</sub>   | -4 - t <sub>A</sub>                       | 10 - t <sub>A</sub>                             | ns   |

| t <sub>39</sub>   | SR | Latched $\overline{CS}$ low to valid data in                                                     | -                   | $40 + t_{C} + 2t_{A}$ | -                                         | 3TCL - 20<br>+ t <sub>C</sub> + 2t <sub>A</sub> | ns   |

| t <sub>40</sub>   | СС | Latched $\overline{CS}$ hold after $\overline{RD}$ , $\overline{WR}$                             | 46 + t <sub>F</sub> | _                     | 3TCL - 14 + t <sub>F</sub>                | _                                               | ns   |

| t <sub>42</sub>   | СС | ALE fall. edge to $\overline{RdCS}$ , $\overline{WrCS}$ (with RW delay)                          | 16 + t <sub>A</sub> | _                     | TCL - 4 + t <sub>A</sub>                  | _                                               | ns   |

| t <sub>43</sub>   | СС | ALE fall. edge to $\overline{RdCS}$ , $\overline{WrCS}$ (no RW delay)                            | -4 + t <sub>A</sub> | _                     | -4 + t <sub>A</sub>                       | _                                               | ns   |

| t <sub>44</sub> 1 | СС | Address float after RdCS, WrCS (with RW delay)                                                   | Ι                   | 0                     | -                                         | 0                                               | ns   |

| t <sub>45</sub> 1 | СС | Address float after RdCS, WrCS<br>(no RW delay)                                                  | _                   | 20                    | -                                         | TCL                                             | ns   |

| t <sub>46</sub>   | SR | RdCS to Valid Data In (with RW delay)                                                            | -                   | 16 + t <sub>C</sub>   | _                                         | 2TCL - 24 + t <sub>C</sub>                      | ns   |

| t <sub>47</sub>   | SR | RdCS to Valid Data In (no RW delay)                                                              | _                   | 36 + t <sub>C</sub>   | -                                         | 3TCL - 24 + t <sub>C</sub>                      | ns   |

| Symbol            |    | Parameter                           |                     | CPU Clock<br>25MHz  | Variable CPU Clock<br>1/2TCL = 1 to 25MHz |                            | Unit |

|-------------------|----|-------------------------------------|---------------------|---------------------|-------------------------------------------|----------------------------|------|

|                   |    |                                     | Min.                | Max.                | Min.                                      | Max.                       |      |

| t <sub>48</sub>   | СС | RdCS, WrCS Low Time (with RW delay) | 30 + t <sub>C</sub> | _                   | 2TCL - 10 + t <sub>C</sub>                | -                          | ns   |

| t <sub>49</sub>   | CC | RdCS, WrCS Low Time (no RW delay)   | 50 + t <sub>C</sub> | -                   | 3TCL - 10 + t <sub>C</sub>                | -                          | ns   |

| t <sub>50</sub>   | СС | Data valid to WrCS                  | 26 + t <sub>C</sub> | _                   | 2TCL - 14+ t <sub>C</sub>                 | -                          | ns   |

| t <sub>51</sub>   | SR | Data hold after RdCS                | 0                   | _                   | 0                                         | -                          | ns   |

| t <sub>52</sub> 1 | SR | Data float after RdCS               | -                   | 20 + t <sub>F</sub> | -                                         | 2TCL - 20 + t <sub>F</sub> | ns   |

| t <sub>54</sub>   | СС | Address hold after RdCS, WrCS       | 20 + t <sub>F</sub> | _                   | 2TCL - 20 + t <sub>F</sub>                | -                          | ns   |

| t <sub>56</sub>   | СС | Data hold after WrCS                | 20 + t <sub>F</sub> | _                   | 2TCL - 20 + t <sub>F</sub>                | _                          | ns   |

Table 18 : Multiplexed bus characteristics (continued)

Note 1. Guaranteed by design characterization.

51

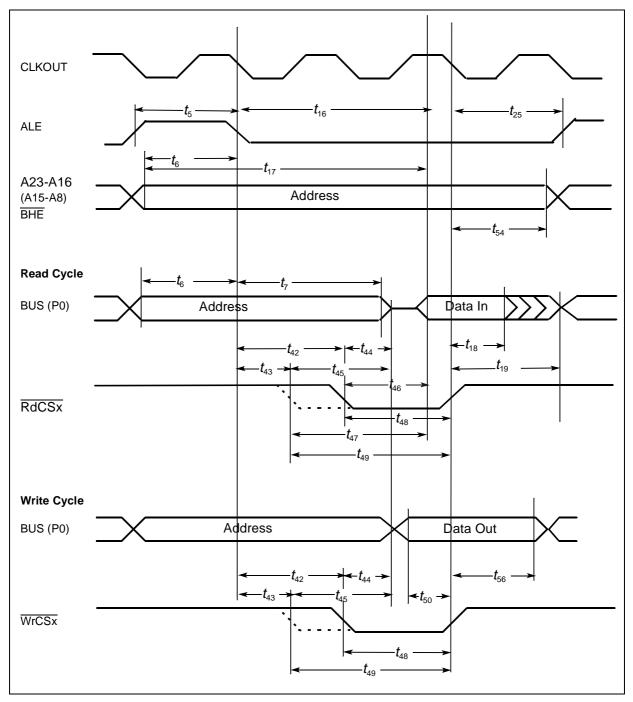

Figure 17 : External Memory Cycle: multiplexed bus, with/without read/write delay, extended ALE, read/ write chip select

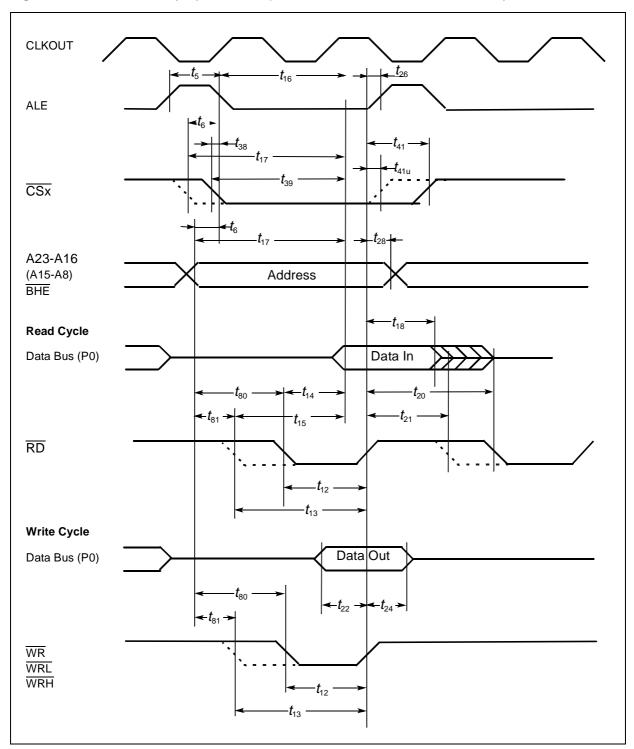

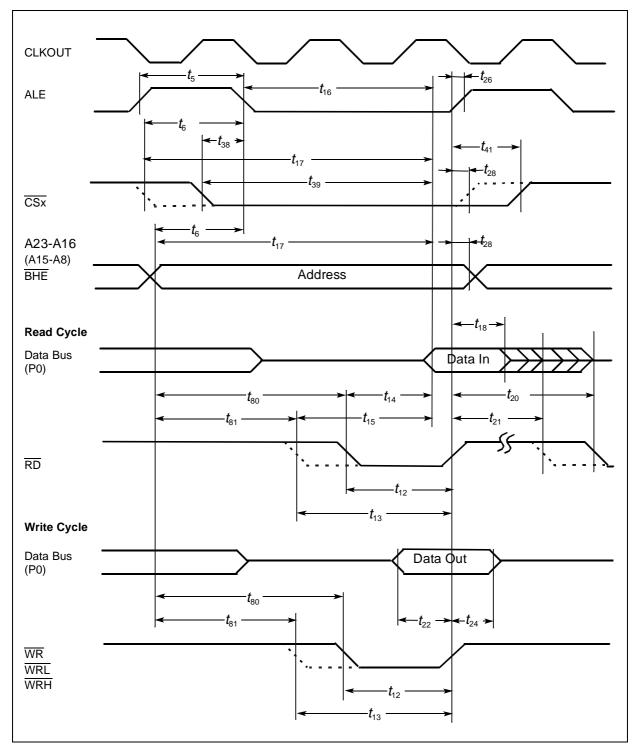

Figure 18 : External Memory Cycle: demultiplexed bus, with/without read/write delay, normal ALE

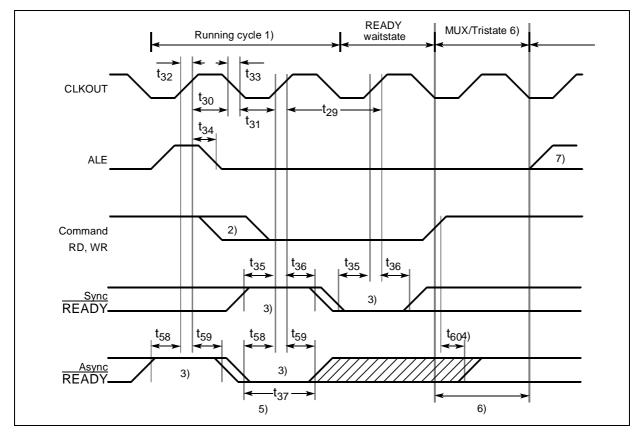

## XX.4.11 - CLKOUT and READY

$\begin{array}{l} V_{DD} = 5V \pm 10\%, \, V_{SS} = 0V, \, T_A = \underline{-40} \ \underline{to} \ \underline{+125^{\circ}C} \\ C_L \ (for \ Port0, \ \underline{Port1}, \ Port \ 4, \ ALE, \ \overline{RD}, \ \overline{WR}, \ \overline{BHE}, \ CLKOUT) = 100 pF \\ C_L \ (for \ Port \ 6, \ \overline{CS}) = 100 pF \end{array}$

# Table 20 : CLKOUT and READY characteristics

| Symbol          |    | Parameter                                                                                                                              | Max. CPU Clock<br>= 25MHz |                          | Variable CPU Clock<br>1/2TCL = 1 to 25MHz |                                                         | Unit |

|-----------------|----|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|-------------------------------------------|---------------------------------------------------------|------|

|                 |    |                                                                                                                                        | Min.                      | Max.                     | Min.                                      | Max.                                                    |      |

| t <sub>29</sub> | СС | CLKOUT cycle time                                                                                                                      | 40                        | 40                       | 2TCL                                      | 2TCL                                                    | ns   |

| t <sub>30</sub> | СС | CLKOUT high time                                                                                                                       | 14                        | _                        | TCL – 6                                   | -                                                       | ns   |

| t <sub>31</sub> | СС | CLKOUT low time                                                                                                                        | 10                        | _                        | TCL – 10                                  | _                                                       | ns   |

| t <sub>32</sub> | СС | CLKOUT rise time                                                                                                                       | Ι                         | 4                        | -                                         | 4                                                       | ns   |

| t <sub>33</sub> | CC | CLKOUT fall time                                                                                                                       | -                         | 4                        | -                                         | 4                                                       | ns   |

| t <sub>34</sub> | СС | CLKOUT rising edge to ALE falling edge                                                                                                 | 0 + t <sub>A</sub>        | 10 + t <sub>A</sub>      | $0 + t_A$                                 | 10 + t <sub>A</sub>                                     | ns   |

| t <sub>35</sub> | SR | Synchronous READY setup time to CLKOUT                                                                                                 | 14                        | _                        | 14                                        | _                                                       | ns   |

| t <sub>36</sub> | SR | Synchronous READY hold time<br>after CLKOUT                                                                                            | 4                         | _                        | 4                                         | -                                                       | ns   |

| t <sub>37</sub> | SR | Asynchronous READY low time                                                                                                            | 54                        | _                        | 2TCL + 14                                 | _                                                       | ns   |

| t <sub>58</sub> | SR | Asynchronous READY setup time <sup>1</sup>                                                                                             | 14                        | _                        | 14                                        | _                                                       | ns   |

| t <sub>59</sub> | SR | Asynchronous READY hold time <sup>1</sup>                                                                                              | 4                         | _                        | 4                                         | _                                                       | ns   |

| t <sub>60</sub> | SR | Async. $\overline{\text{READY}}$ hold time after $\overline{\text{RD}}$ , $\overline{\text{WR}}$ high (Demultiplexed Bus) <sup>2</sup> | 0                         | $0 + 2t_A + t_C + t_F^2$ | 0                                         | TCL - 20<br>+ $2t_{A}$ + $t_{C}$ + $t_{F}$ <sup>2</sup> | ns   |

Notes 1. These timings are given for test purposes only, in order to assure recognition at a specific clock edge.

2. Demultiplexed bus is the worst case. For multiplexed bus 2TCL are to be added to the maximum values. This adds even more time for deactivating READY. The  $2t_A$  and  $t_C$  refer to the next following bus cycle,  $t_F$  refers to the current bus cycle.

#### Figure 22 : CLKOUT and READY

Notes 1. Cycle as programmed, including MCTC waitstates (Example shows 0 MCTC WS).

2. The leading edge of the respective command depends on RW-delay.

3. READY sampled HIGH at this sampling point generates a READY controlled wait state, READY sampled LOW at this sampling point terminates the currently running bus cycle.

4. READY may be deactivated in response to the trailing (rising) edge of the corresponding command (RD or WR).

5. If the Asynchronous READY signal does not fulfill the indicated setup and hold times with respect to CLKOUT (e.g. because CLKOUT is not enabled), it must fulfill t 37 in order to be safely synchronized. This is guaranteed, if READY is removed in response to the command (see Note 4)).

6. Multiplexed bus modes have a MUX waitstate added after a bus cycle, and an additional MTTC waitstate may be inserted here. For a multiplexed bus with MTTC waitstate this delay is 2 CLKOUT cycles, for a demultiplexed bus without MTTC waitstate this delay is zero.

7. The next external bus cycle may start here.

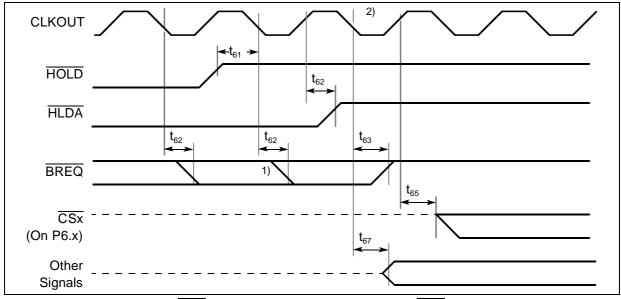

Figure 24 : External bus arbitration, (regaining the bus)

Notes 1. This is the last opportunity for BREQ to trigger the indicated regain-sequence. Even if BREQ is activated earlier, the regain-sequence is initiated by HOLD going high. Please note that HOLD may also be deactivated without the ST10C167 requesting the bus. 2. The next ST10C167 driven bus cycle may start here.

**/**

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 1999 STMicroelectronics - All Rights Reserved STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A. http://www.st.com