Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M0+                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 15MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                              |

| Data Converters            | A/D 12x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 20-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc802m001jdh20fp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**LPC802**

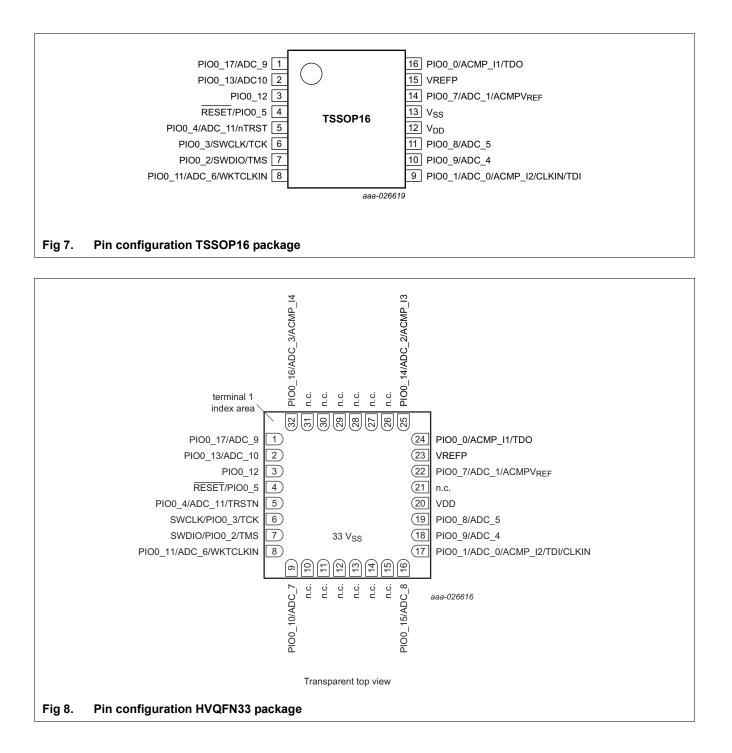

## 7.2 Pin description

<u>Table 4</u> shows the pin functions that are fixed to specific pins on each package. These fixed-pin functions are selectable through the switch matrix between GPIO and the comparator, ADC, SWD, and RESET pins. By default, the GPIO function is selected except on pins PIO0\_2, PIO0\_3, and PIO0\_5. JTAG functions are available in boundary scan mode only.

Movable functions for the I2C, USART, SPI, CTimer pins and other peripherals can be assigned through the switch matrix to any pin that is not power or ground in place of the pin's fixed functions.

The following exceptions apply:

Do not assign more than one output to any pin. However, an output and/or one or more inputs can be assigned to a pin. Once any function is assigned to a pin, the pin's GPIO functionality is disabled.

Eight GPIO pins trigger a wake-up from deep power-down mode. If the part must wake up from deep power-down mode via an external pin, do not assign any movable function to this pin. The GPIO pins should be pulled HIGH externally before entering deep power-down mode. A LOW-going pulse as short as 50 ns causes the chip to exit deep power-down mode and wakes up the part.

The JTAG functions TDO, TDI, TCK, TMS, and TRST are selected on pins PIO0\_0 to PIO0\_4 by hardware when the part is in boundary scan mode.

PIO0\_2, PIO0\_3, and PIO0\_12 are the high drive output pins. <u>PIO0\_4</u>, PIO0\_8, PIO0\_9, PIO0\_10, PIO0\_11, PIO0\_13, PIO0\_15, and PIO0\_17 are the WAKEUP pins.

# 8. Movable functions

Movable functions for the I2C, USART, SPI, CTimer pins and other peripherals can be assigned through the switch matrix to any pin that is not power or ground in place of the fixed functions of the pin.

| Table 5. | Movable functions (assign to pins PIO0_0 to PIO0_5, PIO0_7 to PIO0_17 through |

|----------|-------------------------------------------------------------------------------|

|          | switch matrix)                                                                |

|               | maun | 7                                                                   |

|---------------|------|---------------------------------------------------------------------|

| Function name | Туре | Description                                                         |

| Ux_TXD        | 0    | Transmitter output for USART0 to USART1.                            |

| Ux_RXD        | I    | Receiver input for USART0 to USART1.                                |

| Ux_RTS        | 0    | Request To Send output for USART0.                                  |

| Ux_CTS        | I    | Clear To Send input for USART0.                                     |

| Ux_SCLK       | I/O  | Serial clock input/output for USART0 to USART1 in synchronous mode. |

| SPIx_SCK      | I/O  | Serial clock for SPI0.                                              |

| SPIx_MOSI     | I/O  | Master Out Slave In for SPI0.                                       |

| SPIx_MISO     | I/O  | Master In Slave Out for SPI0.                                       |

| SPIx_SSEL0    | I/O  | Slave select 0 for SPI0.                                            |

| SPIx_SSEL1    | I/O  | Slave select 1 for SPI0.                                            |

| I2Cx_SDA      | I/O  | I <sup>2</sup> C0 bus data input/output.                            |

| I2Cx_SCL      | I/O  | I <sup>2</sup> C0 bus clock input/output.                           |

| ACMP_O        | 0    | Analog comparator output.                                           |

| CLKOUT        | 0    | Clock output.                                                       |

| GPIO_INT_BMAT | 0    | Output of the pattern match engine.                                 |

| T0_MAT0       | 0    | Timer Match channel 0.                                              |

| T0_MAT1       | 0    | Timer Match channel 1.                                              |

| T0_MAT2       | 0    | Timer Match channel 2.                                              |

| T0_MAT3       | 0    | Timer Match channel 3.                                              |

| T0_CAP0       | I    | Timer Capture channel 0.                                            |

| T0_CAP1       | I    | Timer Capture channel 1.                                            |

| T0_CAP2       | I    | Timer Capture channel 2.                                            |

| LVLSHFT_IN0   | I    | Level shift input 0.                                                |

| LVLSHFT_IN1   | I    | Level shift input 1.                                                |

| LVLSHFT_OUT0  | 0    | Level shift output 0.                                               |

| LVLSHFT_OUT1  | 0    | Level shift output 1.                                               |

## 9. Functional description

## 9.1 ARM Cortex-M0+ core

The ARM Cortex-M0+ core runs at an operating frequency of up to 15 MHz using a two-stage pipeline. The core revision is r0p1.

Integrated in the core are the NVIC and Serial Wire Debug with four breakpoints and two watchpoints. The ARM Cortex-M0+ core supports a single-cycle I/O enabled port for fast GPIO access.

The core includes a single-cycle multiplier and a system tick timer.

## 9.2 On-chip flash program memory

The LPC802 contain up to 16 KB of on-chip EEPROM based flash program memory.

## 9.3 On-chip SRAM

The LPC802 contain a total of 2 KB on-chip static RAM data memory.

## 9.4 On-chip ROM

The on-chip ROM contains the bootloader:

- Boot loader.

- Supports Flash In-Application Programming (IAP).

- Supports In-System Programming (ISP) through USART.

- On-chip ROM APIs for integer divide.

- Free Running Oscillator (FRO) API.

### 9.5 Memory map

The LPC802 incorporates several distinct memory regions. <u>Figure 9</u> shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The ARM private peripheral bus includes the ARM core registers for controlling the NVIC, the system tick timer (SysTick), and the reduced power modes.

- Counter or timer operation.

- Up to three 32-bit captures can take a snapshot of the timer value when an input signal transitions. A capture event may also optionally generate an interrupt. The number of capture inputs for each timer that are actually available on device pins can vary by device.

- Four 32-bit match registers that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Shadow registers are added for glitch-free PWM output.

- For each timer, up to 4 external outputs corresponding to match registers with the following capabilities (the number of match outputs for each timer that are actually available on device pins can vary by device):

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- The timer and prescaler may be configured to be cleared on a designated capture event. This feature permits easy pulse width measurement by clearing the timer on the leading edge of an input pulse and capturing the timer value on the trailing edge.

- Up to 4 match registers can be configured for PWM operation, allowing up to 3 single edged controlled PWM outputs. (The number of match outputs for each timer that are actually available on device pins can vary by device.)

## 9.16 Multi-Rate Timer (MRT)

The Multi-Rate Timer (MRT) provides a repetitive interrupt timer with two channels. Each channel can be programmed with an independent time interval, and each channel operates independently from the other channels.

## 9.16.1 Features

- 31-bit interrupt timer

- Two channels independently counting down from individually set values

- Bus stall, repeat and one-shot interrupt modes

## 9.17 Windowed WatchDog Timer (WWDT)

The watchdog timer resets the controller if software fails to service the watchdog timer periodically within a programmable time window.

### 9.17.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The WatchDog Clock (WDCLK) is generated by the dedicated watchdog oscillator (WDOSC).

## 9.18 Self-Wake-up Timer (WKT)

The self-wake-up timer is a 32-bit, loadable down counter. Writing any non-zero value to this timer automatically enables the counter and launches a count-down sequence. When the counter is used as a wake-up timer, this write can occur prior to entering a reduced power mode.

## 9.18.1 Features

- 32-bit loadable down counter. Counter starts automatically when a count value is loaded. Time-out generates an interrupt/wake up request.

- The WKT supports three clock sources: an external clock on the WKTCLKIN pin, the low-power oscillator, and the FRO. The low-power oscillator can be used as the clock source in sleep, deep-sleep, and power-down modes.

- The WKT can be used for waking up the part from any reduced power mode or for general-purpose timing.

## 9.19 Analog comparator (ACMP)

The analog comparator with selectable hysteresis can compare voltage levels on external pins and internal voltages.

After power-up and after switching the input channels of the comparator, the output of the voltage ladder must be allowed to settle to its stable value before it can be used as a comparator reference input. Settling times are given in <u>Table 27</u>.

The analog comparator output is a movable function and is assigned to a pin through the switch matrix. The comparator inputs and the voltage reference are enabled through the switch matrix.

**LPC802**

## 9.22 Clocking and power control

### 9.22.4 Power control

The LPC802 supports the ARM Cortex-M0+ sleep mode. The CPU clock rate may also be controlled as needed by changing clock sources, and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, a register is provided for shutting down the clocks to individual on-chip peripherals, allowing to fine-tune power consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Selected peripherals have their own clock divider which provides even better power control.

#### 9.22.4.1 Sleep mode

When sleep mode is entered, the clock to the core is stopped. Resumption from the sleep mode does not need any special sequence but re-enabling the clock to the ARM core.

In sleep mode, execution of instructions is suspended until either a reset or interrupt occurs. Peripheral functions continue operation during sleep mode and may generate interrupts to cause the processor to resume execution. sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses.

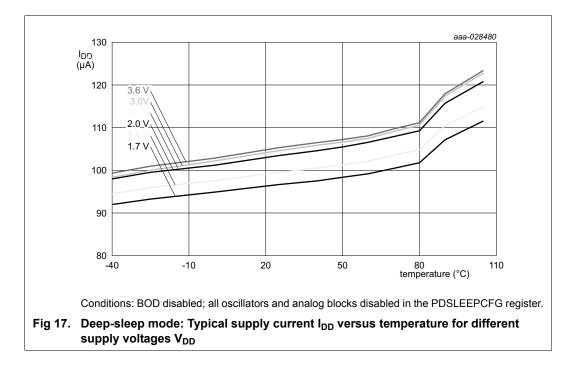

### 9.22.4.2 Deep-sleep mode

In deep-sleep mode, the LPC802 core is in sleep mode and all peripheral clocks and all clock sources are off except for the FRO or low-power oscillator if selected. The FRO output is disabled. In addition, all analog blocks are shut down and the flash is in standby mode. In deep-sleep mode, the application can keep the low power oscillator and the BOD circuit running for self-timed wakeup and BOD protection.

The LPC802 can wake up from deep-sleep mode via a reset, digital pins selected as inputs to the pin interrupt block, a watchdog timer interrupt, or an interrupt from the USART (if the USART is configured in synchronous slave mode), the SPI (in slave mode), or the I2C blocks (in slave mode).

Any interrupt used for waking up from deep-sleep mode must be enabled in one of the SYSCON wake-up enable registers and the NVIC.

Deep-sleep mode saves power and allows for short wake-up times.

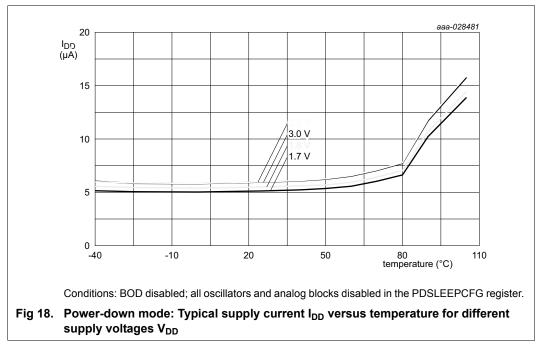

### 9.22.4.3 Power-down mode

In power-down mode, the LPC802 is in sleep mode and all peripheral clocks and all clock sources are off except for low-power oscillator if selected. In addition, all analog blocks and the flash are shut down. In power-down mode, the application can keep the low-power oscillator and the BOD circuit running for self-timed wake up and BOD protection.

The LPC802 can wake up from power-down mode via a reset, digital pins selected as inputs to the pin interrupt block, a watchdog timer interrupt, or an interrupt from the USART (if the USART is configured in synchronous slave mode), the SPI (in slave mode), or the I2C blocks (in slave mode).

Any interrupt used for waking up from power-down mode must be enabled in one of the SYSCON wake-up enable registers and the NVIC.

# 10. Limiting values

#### Table 9. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol              | Parameter                               | Conditions                                        |               | Min  | Max             | Unit |

|---------------------|-----------------------------------------|---------------------------------------------------|---------------|------|-----------------|------|

| V <sub>DD</sub>     | supply voltage (core and external rail) |                                                   | [2]           | -0.5 | +4.6            | V    |

| V <sub>ref</sub>    | reference voltage                       | on pin VREFP                                      |               | -0.5 | V <sub>DD</sub> | V    |

| VI                  | input voltage                           | 5 V tolerant I/O pins; $V_{DD} \ge$ 1.71 V        | <u>[3][4]</u> | -0.5 | +5.4            | V    |

|                     |                                         | 3 V tolerant I/O pin ACMPV <sub>REF</sub>         | [5]           | -0.5 | +3.6            | V    |

| V <sub>IA</sub>     | analog input voltage                    | on digital pins configured for an analog function | [6][7]<br>[8] | -0.5 | +4.6            | V    |

| I <sub>DD</sub>     | supply current                          | per supply pin (TSSOP20)                          |               | -    | 40              | mA   |

|                     |                                         | per supply pin (TSSOP16)                          |               | -    | 30              |      |

|                     |                                         | per supply pin (HVQFN33)                          |               | -    | 50              |      |

|                     |                                         | per supply pin (WLCSP16)                          |               | -    | 30              |      |

| I <sub>SS</sub>     | ground current                          | per ground pin (TSSOP20)                          |               | -    | 40              | mA   |

|                     |                                         | per ground pin (TSSOP16)                          |               | -    | 30              |      |

|                     |                                         | per ground pin (HVQFN33)                          |               | -    | 50              |      |

|                     |                                         | per supply pin (WLCSP16)                          |               | -    | 30              |      |

| l <sub>latch</sub>  | I/O latch-up current                    | $-(0.5V_{DD}) < V_{I} < (1.5V_{DD});$             |               | -    | 100             | mA   |

| <b>T</b> .          | storago tomporaturo                     | T <sub>j</sub> < 125 °C                           | [9]           | -65  | +150            | °C   |

| T <sub>stg</sub>    | storage temperature                     |                                                   | <u>[0]</u>    | -co- |                 | -    |

| T <sub>j(max)</sub> | maximum junction temperature            |                                                   |               | -    | 150             | °C   |

## 12.2.1 Peripheral power consumption

The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled in the SYSAHBCLKCFG. and PDRUNCFG (for analog blocks) registers. All other blocks are disabled in both registers and no code accessing the peripheral is executed. Measured on a typical sample at  $T_{amb}$  = 25 °C.

The supply currents are shown for system clock frequencies of 12 MHz and 15 MHz.

Table 13. Power consumption for individual analog and digital blocks

| Peripheral           | Typical s | upply current in | μA     | Notes                                                                                                                                                        |  |  |

|----------------------|-----------|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                      | System of | clock frequency  | =      |                                                                                                                                                              |  |  |

|                      | n/a       | 12 MHz           | 15 MHz |                                                                                                                                                              |  |  |

| FRO                  | 74        | -                | -      | FRO = 12MHz. FRO output disabled.                                                                                                                            |  |  |

| BOD                  | 39        | -                | -      | Independent of main clock frequency.                                                                                                                         |  |  |

| Flash                | 80        | -                | -      | -                                                                                                                                                            |  |  |

| LPOsc                | 1         | -                | -      | FRO; independent of main clock frequency.                                                                                                                    |  |  |

| GPIO + pin interrupt | -         | 40               | 54     | GPIO pins configured as outputs and set to<br>LOW. Direction and pin state are maintained if<br>the GPIO is disabled in the SYSAHBCLKCFG<br>register.        |  |  |

| SWM                  | -         | 24               | 30     | -                                                                                                                                                            |  |  |

| IOCON                | -         | 28               | 36     | -                                                                                                                                                            |  |  |

| CTimer               | -         | 28               | 37     | -                                                                                                                                                            |  |  |

| MRT                  | -         | 45               | 56     | -                                                                                                                                                            |  |  |

| WWDT                 | -         | 31               | 41     | -                                                                                                                                                            |  |  |

| I2C0                 | -         | 44               | 58     | -                                                                                                                                                            |  |  |

| SPI0                 | -         | 33               | 42     | -                                                                                                                                                            |  |  |

| USART0               | -         | 39               | 46     | -                                                                                                                                                            |  |  |

| USART1               | -         | 40               | 50     | -                                                                                                                                                            |  |  |

| Comparator ACMP      | -         | 36               | 46     | -                                                                                                                                                            |  |  |

| ADC                  | -         | 61               | 78     | Digital controller only. Analog portion of the ADC disabled in the PDRUNCFG register.                                                                        |  |  |

|                      | -         | 61               | 78     | Combined analog and digital logic. ADC<br>enabled in the PDRUNCFG register and<br>LPWRMODE bit set to 1 in the ADC CTRL<br>register (ADC in low-power mode). |  |  |

|                      | -         | 61               | 78     | Combined analog and digital logic. ADC<br>enabled in the PDRUNCFG register and<br>LPWRMODE bit set to 0 in the ADC CTRL<br>register (ADC powered).           |  |  |

| CRC                  | -         | 37               | 50     | -                                                                                                                                                            |  |  |

## 13.6 SPI interfaces

The actual SPI bit rate depends on the delays introduced by the external trace, the external device, system clock (CCLK), and capacitive loading. Excluding delays introduced by external device and PCB, the maximum supported bit rate for SPI master mode is 15 Mbit/s, and the maximum supported bit rate for SPI slave mode is  $1/(2 \times 28 \text{ ns}) = 17.8 \text{ Mbit/s}$  at  $3.0v \le \text{VDD} \le 3.6v$  and  $1/(2 \times 32 \text{ ns}) = 15.6 \text{ Mbit/s}$  at  $1.7v \le \text{VDD} \le 3.0v$ .

**Remark:** SPI functions can be assigned to all digital pins. The characteristics are valid for all digital pins.

#### Table 21. SPI dynamic characteristics

$T_{amb} = -40$  °C to 105 °C;  $C_L = 20$  pF; input slew = 1 ns. Simulated parameters sampled at the 30 % and 70 % level of the rising or falling edge; values guaranteed by design. Delays introduced by the external trace or external device are not considered.

| Symbol            | Parameter              | Conditions                         | Min | Max | Unit |

|-------------------|------------------------|------------------------------------|-----|-----|------|

| SPI maste         | er                     |                                    |     |     |      |

| t <sub>DS</sub>   | data set-up time       | 1.71 V <= V <sub>DD</sub> <= 3.6 V | 10  | -   | ns   |

| t <sub>DH</sub>   | data hold time         | 1.71 V <= V <sub>DD</sub> <= 3.6 V | 7   | -   | ns   |

| t <sub>v(Q)</sub> | data output valid time | 1.71 V <= V <sub>DD</sub> <= 3.6 V | 0   | 2   | ns   |

| SPI slave         |                        |                                    |     |     |      |

| t <sub>DS</sub>   | data set-up time       | 1.71 V <= V <sub>DD</sub> <= 3.6 V | 10  | -   | ns   |

| t <sub>DH</sub>   | data hold time         | 1.71 V <= V <sub>DD</sub> <= 3.6 V | 7   | -   | ns   |

| t <sub>v(Q)</sub> | data output valid time | 3.0 V <= V <sub>DD</sub> <= 3.6 V  | 0   | 28  | ns   |

|                   |                        | 1.71 V <= V <sub>DD</sub> < 3.0 V  | 0   | 32  | ns   |

# **15. Application information**

## 15.1 Start-up behavior

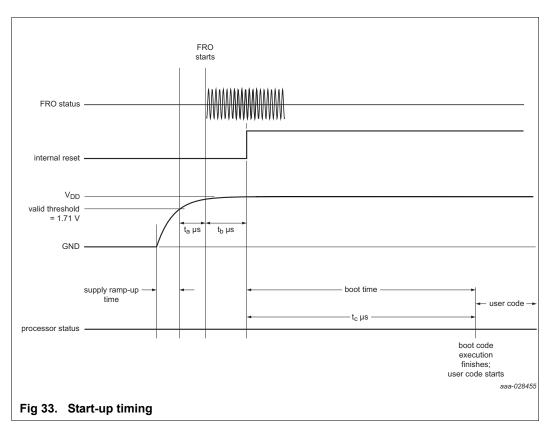

<u>Figure 33</u> shows the start-up timing after reset. The FRO 12 MHz oscillator provides the default clock at Reset and provides a clean system clock shortly after the supply pins reach operating voltage.

Table 30.

Typical start-up timing parameters

| Parameter      | Description                | Value   |

|----------------|----------------------------|---------|

| t <sub>a</sub> | FRO start time             | ≤ 26 μs |

| t <sub>b</sub> | Internal reset de-asserted | 101 μs  |

| t <sub>c</sub> | Boot time                  | 36 μs   |

## 15.2 Connecting power, clocks, and debug functions

Figure 34 shows the basic board connections used to power the LPC802 and provide debug capabilities via the serial wire port.

## 15.4 Termination of unused pins

Table 31 shows how to terminate pins that are **not** used in the application. In many cases, unused pins may should be connected externally or configured correctly by software to minimize the overall power consumption of the part.

Unused pins with GPIO function should be configured as outputs set to LOW with their internal pull-up disabled. To configure a GPIO pin as output and drive it LOW, select the GPIO function in the IOCON register, select output in the GPIO DIR register, and write a 0 to the GPIO PORT register for that pin. Disable the pull-up in the pin's IOCON register.

In addition, it is recommended to configure all GPIO pins that are not bonded out on smaller packages as outputs driven LOW with their internal pull-up disabled.

Table 31.

Termination of unused pins

|            | Default<br>state <sup>[1]</sup> | Recommended termination of unused pins                                                                 |

|------------|---------------------------------|--------------------------------------------------------------------------------------------------------|

| all PIOn_m |                                 | Can be left unconnected if driven LOW and configured as GPIO output with pull-up disabled by software. |

| VREFP      | -                               | Tie to VDD.                                                                                            |

[1] I = Input, O = Output, IA = Inactive (no pull-up/pull-down enabled), F = floating, PU = Pull-Up.

## 15.5 Pin states in different power modes

#### Table 32. Pin states in different power modes

| Pin         | Active                         | Sleep                    | Deep-sleep/power-<br>down | Deep power-down                                                            |

|-------------|--------------------------------|--------------------------|---------------------------|----------------------------------------------------------------------------|

| PIOn_m pins | As configured in th enabled.   | e IOCON <u>⊡</u> . Defau | lt: internal pull-up      | Floating.                                                                  |

| RESET       | Reset function ena<br>enabled. | ıbled. Default: inpu     | t, internal pull-up       | Reset function disabled; floating; if the part is in deep power-down mode. |

[1] Default and programmed pin states are retained in sleep, deep-sleep, and power-down modes.

**LPC802**

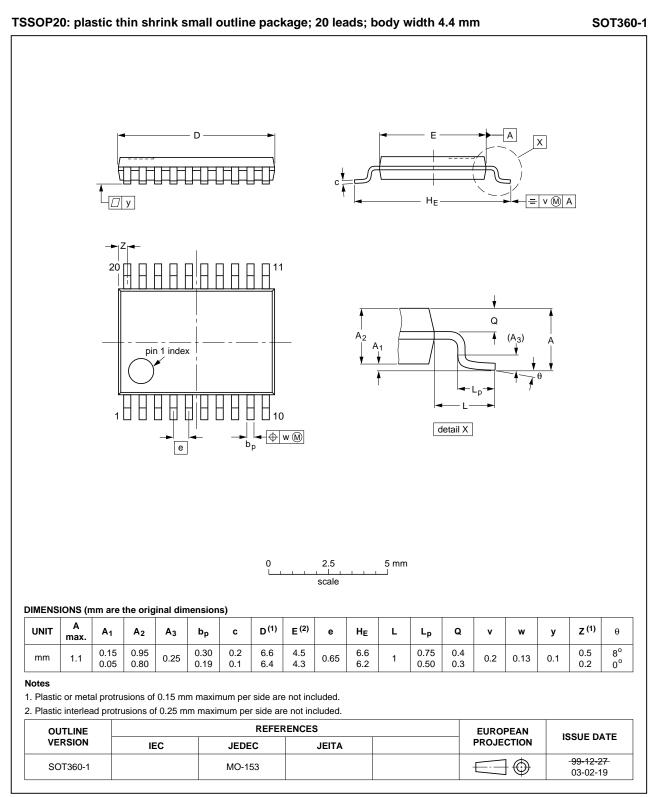

# 16. Package outline

### Fig 35. Package outline SOT360-1 (TSSOP20)

**LPC802**

Product data sheet

# 20. Revision history

## Table 34.Revision history

| Document ID    | Release date                                               | Data sheet status                                                                                                                        | Change notice                            | Supersedes                                                                           |  |  |

|----------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| LPC802 v.1.6   | 20180427                                                   | Product data sheet                                                                                                                       | -                                        | LPC802 v.1.5                                                                         |  |  |

| Modifications: | registers ar<br>• Updated <u>Se</u><br>• Updated <u>Se</u> | to <u>Section 9.22.4.4 "Dec</u><br>e available to store infor<br>ection 9.22.1 "Internal of                                              | mation during dee<br>scillators". Change |                                                                                      |  |  |

| LPC802 v.1.5   | 20180312                                                   | Product data sheet                                                                                                                       | -                                        | LPC802 v.1.4                                                                         |  |  |

| Modifications: | Updated Ta                                                 | able 3 "Device revision ta                                                                                                               | able".                                   |                                                                                      |  |  |

| LPC802 v.1.4   | 20180227                                                   | Product data sheet                                                                                                                       | -                                        | LPC802 v.1.3                                                                         |  |  |

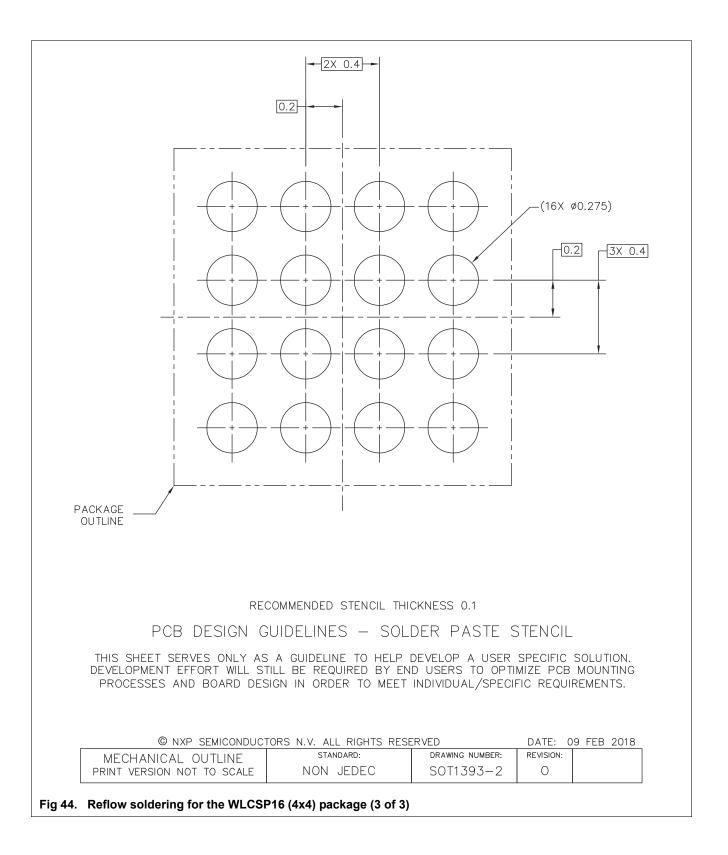

| Modifications: | <ul> <li>Added Figu</li> </ul>                             | Ire 38 "Package outline                                                                                                                  | WLCSP16 (1.86 '1                         | .86 ´ 0.3 mm)".                                                                      |  |  |

|                | 43 "Reflow                                                 |                                                                                                                                          | P16 (4x4) package                        | (4x4) package (1 of 3)", Figure (2 of 3)", and Figure 44 "Reflow                     |  |  |

|                | <ul> <li>Updated tit</li> </ul>                            | le of Section 13.1 "Flash                                                                                                                | memory (EEPRO                            | M based)".                                                                           |  |  |

|                |                                                            | <ul> <li>Updated Table 12 "Static characteristics, supply pins": Added condition: system clock</li> <li>= 1 MHz, VDD = 3.3 V.</li> </ul> |                                          |                                                                                      |  |  |

|                |                                                            |                                                                                                                                          |                                          | k values: FRO clock frequency; uency; Condition: $-40 \text{ °C} \le T_{amb}$        |  |  |

| LPC802 v.1.3   | 20180209                                                   | Product data sheet                                                                                                                       | -                                        | LPC802 v.1.2                                                                         |  |  |

| Modifications: | Updated Se                                                 | ection 2 "Features and b                                                                                                                 | enefits".                                |                                                                                      |  |  |

|                |                                                            | able 5 "Movable function<br>rough switch matrix)".                                                                                       | s (assign to pins P                      | IO0_0 to PIO0_5, PIO0_7 to                                                           |  |  |

|                | Added leve                                                 | I shifter functionality to S                                                                                                             | Section 9.8 "I/O cor                     | nfiguration".                                                                        |  |  |

|                |                                                            | 5 MHz. Added Conditio                                                                                                                    |                                          | anged frequencies to 9 MHz, 12 $_{\odot}$ 70 °C and Condition: –40 $~^{\circ}C \leq$ |  |  |

| LPC802 v.1.2   | 20171222                                                   | Product data sheet                                                                                                                       | -                                        | LPC802 v.1.1                                                                         |  |  |

| Modifications: | Updated Fi                                                 | gure 4 "LPC802 block d                                                                                                                   | iagram".                                 |                                                                                      |  |  |

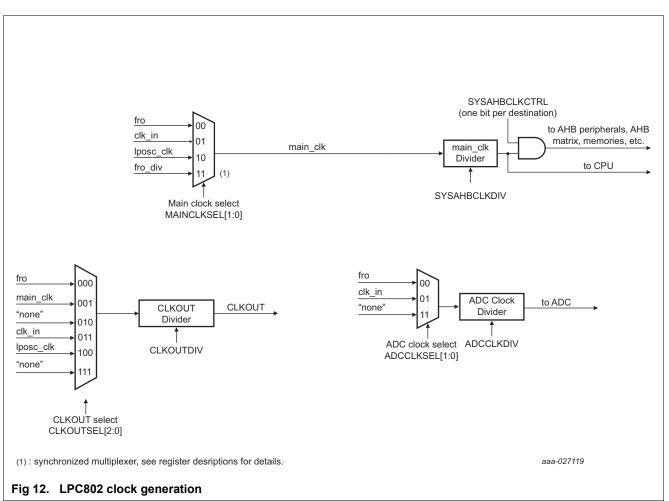

|                | <ul> <li>Updated Fi</li> </ul>                             | gure 12 "LPC802 clock                                                                                                                    | generation".                             |                                                                                      |  |  |

|                |                                                            | able 7 "Peripheral config<br>is on standby.                                                                                              | uration in reduced                       | power modes": In deep-sleep                                                          |  |  |

| LPC802 v.1.1   | 20171222                                                   | Product data sheet                                                                                                                       | -                                        | LPC802 v.1                                                                           |  |  |

| Modifications: |                                                            | gure 21 "High-drive outp<br>output current IOH" at 1                                                                                     |                                          | evel output voltage VOH versus                                                       |  |  |

| LPC802 v.1     | 20171218                                                   | Product data sheet                                                                                                                       |                                          |                                                                                      |  |  |

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Non-automotive qualified products** — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b)

# 22. Contact information

whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

## 21.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

# 23. Contents

| 1              | General description 1                                             |

|----------------|-------------------------------------------------------------------|

| 2              | Features and benefits 1                                           |

| 3              | Applications 4                                                    |

| 4              | Ordering information 4                                            |

| 4.1            | Ordering options 4                                                |

| 5              | Marking 5                                                         |

| 6              | Block diagram 7                                                   |

| 7              | Pinning information                                               |

| 7.1            | Pinning 8                                                         |

| 7.2            | Pin description 10                                                |

| 8              | Movable functions 14                                              |

| 9              | Functional description 15                                         |

| 9.1            | ARM Cortex-M0+ core 15                                            |

| 9.2            | On-chip flash program memory                                      |

| 9.3            | On-chip SRAM 15                                                   |

| 9.4            | On-chip ROM                                                       |

| 9.5            | Memory map                                                        |

| 9.6<br>9.6.1   | Nested Vectored Interrupt Controller (NVIC) . 17<br>Features      |

| 9.6.2          | Interrupt sources                                                 |

| 9.7            | System tick timer                                                 |

| 9.8            | I/O configuration                                                 |

| 9.8.1          | Standard I/O pad configuration                                    |

| 9.9            | Switch Matrix (SWM)                                               |

| 9.10           | Fast General-Purpose parallel I/O (GPIO) 19                       |

| 9.10.1         | Features                                                          |

| 9.11           | Pin interrupt 19                                                  |

| 9.11.1         | Features                                                          |

| 9.12<br>9.12.1 | USART0/1                                                          |

| 9.12.1         | Features         20           SPI0         20                     |

| 9.13.1         | Features                                                          |

| 9.14           | I2C-bus interface (I2C0)                                          |

| 9.14.1         | Features                                                          |

| 9.15           | CTimer 21                                                         |

| 9.15.1         | General-purpose 32-bit timers/external event                      |

|                | counter                                                           |

| 9.15.1.1       | Features                                                          |

| 9.16           | Multi-Rate Timer (MRT) 22                                         |

| 9.16.1<br>9.17 | Features                                                          |

| 9.17           | Windowed WatchDog Timer (WWDT)       22         Features       22 |

| 9.17.1         | Self-Wake-up Timer (WKT)                                          |

| 9.18.1         | Features                                                          |

| 9.19           | Analog comparator (ACMP)                                          |

| 9.19.1         | Features                                                          |

|                |                                                                   |

| 9.20                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                 | Analog-to-Digital Converter (ADC)                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25                                                                                                               |

| 9.20.1                                                                                                                                          | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                               |

| 9.21                                                                                                                                            | CRC engine                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26                                                                                                               |

| 9.21.1                                                                                                                                          | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26                                                                                                               |

| 9.22                                                                                                                                            | Clocking and power control                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                                               |

| 9.22.1                                                                                                                                          | Internal oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30                                                                                                               |

| 9.22.1.1                                                                                                                                        | Free Running Oscillator (FRO)                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30                                                                                                               |

| 9.22.1.2                                                                                                                                        | Low Power Oscillator (LPOsc)                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30                                                                                                               |

| 9.22.2                                                                                                                                          | Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30                                                                                                               |

| 9.22.3                                                                                                                                          | Clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30                                                                                                               |

| 9.22.4                                                                                                                                          | Power control                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                               |

| 9.22.4.1                                                                                                                                        | Sleep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                                                               |

| 9.22.4.2                                                                                                                                        | Deep-sleep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                               |

| 9.22.4.3                                                                                                                                        | Power-down mode                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                               |

| 9.22.4.4                                                                                                                                        | Deep power-down mode                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32                                                                                                               |

| 9.22.5                                                                                                                                          | Wake-up process                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                                               |

| 9.23                                                                                                                                            | System control                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33                                                                                                               |

| 9.23.1                                                                                                                                          | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33                                                                                                               |

| 9.23.2                                                                                                                                          | Brownout detection                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34                                                                                                               |

| 9.23.3                                                                                                                                          | Code security (Code Read Protection - CRP)                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                                                                               |

| 9.23.4                                                                                                                                          | APB interface                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35                                                                                                               |

| 9.23.5                                                                                                                                          | AHBLite                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                                                                               |

| 9.24                                                                                                                                            | Emulation and debugging                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                                                                               |

| 10                                                                                                                                              | Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                                                                               |

| 11                                                                                                                                              | Thermal characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39                                                                                                               |

| 12                                                                                                                                              | Static characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                                                                               |

| 12.1                                                                                                                                            | General operating conditions                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40                                                                                                               |

| 12.2                                                                                                                                            | Power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40                                                                                                               |

| 12.2.1                                                                                                                                          | Peripheral power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                  |

| 40.0                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44                                                                                                               |

| 12.3                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44<br>45                                                                                                         |

| 12.3                                                                                                                                            | Pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                  |

| 12.3.1                                                                                                                                          | Pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45<br>47                                                                                                         |

| 12.3.1<br><b>13</b>                                                                                                                             | Pin characteristics<br>Electrical pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                               | 45<br>47<br><b>50</b>                                                                                            |

| 12.3.1<br><b>13</b><br>13.1                                                                                                                     | Pin characteristics<br>Electrical pin characteristics<br>Dynamic characteristics<br>Flash memory (EEPROM based)                                                                                                                                                                                                                                                                                                                                                     | 45<br>47<br><b>50</b><br>50                                                                                      |

| 12.3.1<br><b>13</b><br>13.1<br>13.2                                                                                                             | Pin characteristics<br>Electrical pin characteristics<br>Dynamic characteristics<br>Flash memory (EEPROM based)<br>FRO                                                                                                                                                                                                                                                                                                                                              | 45<br>47<br><b>50</b><br>50<br>50                                                                                |

| 12.3.1<br><b>13</b><br>13.1<br>13.2<br>13.3                                                                                                     | Pin characteristics<br>Electrical pin characteristics<br><b>Dynamic characteristics</b><br>Flash memory (EEPROM based)<br>FRO<br>I/O pins.                                                                                                                                                                                                                                                                                                                          | 45<br>47<br><b>50</b><br>50<br>50<br>51                                                                          |

| 12.3.1<br><b>13</b><br>13.1<br>13.2<br>13.3<br>13.4                                                                                             | Pin characteristics<br>Electrical pin characteristics<br><b>Dynamic characteristics</b><br>Flash memory (EEPROM based)<br>FRO<br>I/O pins<br>WKTCLKIN pin (wake-up clock input)                                                                                                                                                                                                                                                                                     | 45<br>47<br><b>50</b><br>50<br>50<br>51<br>51                                                                    |

| 12.3.1<br><b>13</b><br>13.1<br>13.2<br>13.3<br>13.4<br>13.5                                                                                     | Pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45<br>47<br><b>50</b><br>50<br>51<br>51<br>51                                                                    |

| 12.3.1<br><b>13</b><br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6                                                                             | Pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45<br>47<br><b>50</b><br>50<br>51<br>51<br>51<br>53                                                              |

| 12.3.1<br><b>13</b><br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6<br>13.7                                                                     | Pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45<br>47<br><b>50</b><br>50<br>51<br>51<br>51<br>53<br>56                                                        |

| 12.3.1<br><b>13</b><br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6<br>13.7<br>13.8                                                             | Pin characteristics .<br>Electrical pin characteristics.<br><b>Dynamic characteristics</b> .<br>Flash memory (EEPROM based)<br>FRO<br>I/O pins.<br>WKTCLKIN pin (wake-up clock input) .<br>I <sup>2</sup> C-bus.<br>SPI interfaces.<br>USART interface<br>Wake-up process.                                                                                                                                                                                          | 45<br>47<br>50<br>50<br>51<br>51<br>51<br>51<br>53<br>56<br>57                                                   |

| 12.3.1<br><b>13</b><br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.6<br>13.7<br>13.8<br><b>14</b>                                                | Pin characteristics<br>Electrical pin characteristics<br><b>Dynamic characteristics</b><br>Flash memory (EEPROM based)<br>FRO<br>I/O pins.<br>WKTCLKIN pin (wake-up clock input)<br>I <sup>2</sup> C-bus.<br>SPI interfaces.<br>USART interface<br>Wake-up process.<br><b>Characteristics of analog peripherals</b>                                                                                                                                                 | 45<br>47<br>50<br>50<br>51<br>51<br>51<br>51<br>53<br>56<br>57<br>57                                             |