Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | USB                                                                  |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                              |

| Number of I/O              | 11                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 384 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                            |

| Data Converters            | A/D 3x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                      |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f623f2b1 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIN DESCRIPTION (Cont'd)

### Legend / Abbreviations:

| Туре:        | I = Input, O = Output, S = Supply                                                                                                 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Input level: | A = Dedicated analog input                                                                                                        |

| Input level: | $\begin{array}{l} C = CMOS \; 0.3V_{DD}/0.7V_{DD}, \\ C_T = CMOS \; 0.3V_{DD}/0.7V_{DD} \; \text{with input trigger} \end{array}$ |

Output level: HS = High Sink (on N-buffer only)

Port configuration capabilities:

- Input:float = floating, wpu = weak pull-up, int = interrupt (\ =falling edge, / =rising edge), ana = analog

### **Table 1. Device Pin Description**

| _      | Ou    | Itpu | t: O  | D =  | оре   | en drain, T = true op                    | oen o | drair          | n (N              | buff  | er 8 | mA  | @0   | .4 V               | /), P | P = push-          | pull                                                                   |

|--------|-------|------|-------|------|-------|------------------------------------------|-------|----------------|-------------------|-------|------|-----|------|--------------------|-------|--------------------|------------------------------------------------------------------------|

| Tab    | le 1  | I. D | evio  | ce F | Pin I | Description                              |       |                |                   |       |      |     |      |                    |       |                    | de                                                                     |

|        |       | Pin  | n°    |      |       |                                          | Level |                | el Port / Control |       |      |     | Main | 200                |       |                    |                                                                        |

| 244    | 42    | 34   | 32    | 20   | 20    | Pin Name                                 | Type  | Ħ              | out               |       | Inp  | out |      | Out                | tput  | Function<br>(after | Alternate Function                                                     |

| LQFP44 | DIP42 | S034 | DIP32 | S020 | DIP20 |                                          | F     | Input          | Output            | float | wpu  | int | ana  | ОD                 | РР    | reset)             |                                                                        |

| 1      | 6     | 29   | 28    | 9    | 14    | V <sub>PP</sub>                          | S     |                |                   |       | x    |     | 6    | $\hat{\mathbf{O}}$ | 6     |                    | ogramming voltage<br>st be tied low in user                            |

| 2      | 7     | -    | -     | -    | -     | PD1                                      | I/O   | $C_T$          |                   |       | x    | X   | 2    |                    | х     | Port D1            |                                                                        |

| 3      | 8     | -    | -     | -    | -     | PD0                                      | I/O   | $C_{T}$        |                   |       | x    | )   |      |                    | х     | Port D0            |                                                                        |

| 4      | 9     | 31   | -     | -    | -     | PC7                                      | I/O   | C <sub>T</sub> | 1                 |       | х    |     |      |                    | х     | Port C7            |                                                                        |

| 5      | 10    | 32   | 30    | -    | -     | PC6/MOSI                                 | I/O   | с <sub>т</sub> | 5                 |       | x    |     |      |                    | x     | Port C6            | SPI Master Out /<br>Slave In <sup>1)</sup>                             |

| 6      | 11    | 33   | 31    | -    | -     | PC5/MISO/IT12                            | 1/0   | Ст             |                   |       | x    | x   |      |                    | x     | Port C5            | SPI Master In /<br>Slave Out <sup>1)</sup> /<br>Interrupt 12 input     |

| 7      | 12    | 34   | 32    | -    | -     | PC4/SS/IT11                              | I/O   | CT             |                   |       | x    | x   |      |                    | x     | Port C4            | SPI Slave Select<br>(active low) <sup>1)</sup> /<br>Interrupt 11 input |

| 8      | 13    | 1    | 1     | -(   | Q.    | PC3/SCK/IT10                             | I/O   | C <sub>T</sub> |                   |       | x    | x   |      |                    | x     | Port C3            | SPI Serial Clock <sup>1)</sup> /<br>Interrupt 10 input                 |

| 9      | 14    | 2    | 2     | )'   | -     | PC2/IT9                                  | I/O   | $C_T$          |                   |       | х    | х   |      |                    | x     | Port C2            | Interrupt 9 input                                                      |

| 10     | 15    | 3    | 3     | 11   | 16    | OSCIN                                    |       |                |                   |       |      |     |      |                    |       |                    | s are used connect an ock source to the on-                            |

| 11     | 16    | 4    | 4     | 12   | 17    | OSCOUT                                   |       |                |                   |       |      |     |      |                    |       | chip main          |                                                                        |

| 12     | 17    | 5    | 5     | 4    | 9     | V <sub>SS</sub>                          | S     |                |                   |       |      |     |      |                    |       | Digital Gro        | ound Voltage                                                           |

| 13     | 18    | 6    | 6     | 8    | 13    | V <sub>DD</sub>                          | S     |                |                   |       |      |     |      |                    |       | Digital Mai<br>age | in Power Supply Volt-                                                  |

| 14     | 19    | 7    | -     | -    | -     | PC1                                      | I/O   | $C_T$          |                   | х     |      |     |      | Т                  |       | Port C1            |                                                                        |

| 15     | 20    | -    | -     | -    | -     | PC0                                      | I/O   | $C_T$          |                   | х     |      |     |      | Т                  |       | Port C0            |                                                                        |

| 16     | 21    | 8    | 7     | 13   | 18    | PB7/PWM1/IT8/<br>RX_SEZ/DA-<br>TAOUT/DA9 | I/O   | CT             | HS                | x     |      | ١   |      |                    | x     | Port B7            | ART PWM output 1/<br>Interrupt 8 input                                 |

| 17     | -     | -    |       |      |       | N.C.                                     |       |                |                   |       |      |     |      |                    |       | Not Conne          | ected                                                                  |

## **5 CENTRAL PROCESSING UNIT**

## **5.1 INTRODUCTION**

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

## **5.2 MAIN FEATURES**

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- Low power HALT and WAIT modes

- Priority maskable hardware interrupts

- Non-maskable software/hardware interrupts

#### **5.3 CPU REGISTERS**

The 6 CPU registers shown in Figure 10 are not present in the memory mapping and are accessed by specific instructions.

#### Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

#### Index Registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

#### Program Counter (PC)

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

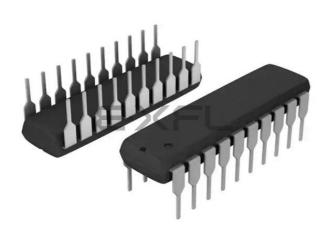

#### Figure 10. CPU Registers 0 7 ACCUMULATOR RESET VALUE = XXh 7 0 X INDEX REGISTER RESET VALUE = XXh 7 0 Y INDEX REGISTER RESET VALUE = XXh PCH PCL 15 8 7 0 **PROGRAM COUNTER** RESET VALUE = RESET VECTOR @ FFFEh-FFFFh 0 1 11 H 10 Ν Ζ С 1 CONDITION CODE REGISTER RESET VALUE = 1 1 Х хх 1 1 8 7 15 0 STACK POINTER RESET VALUE = STACK HIGHER ADDRESS X = Undefined Value

## CENTRAL PROCESSING UNIT (Cont'd)

#### Condition Code Register (CC)

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### Arithmetic Management Bits

#### Bit $4 = \mathbf{H}$ Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result  $7^{\text{th}}$  bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative (i.e. the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

Bit 1 = **Z** Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

0: The result of the last operation is different from zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = **C** Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation. 0: No overflow or underflow has occurred. 1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

#### Interrupt Management Bits

#### Bit 5,3 = **I1**, **I0** Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | 11 | 10 |

|-------------------------------|----|----|

| Level 0 (main)                | 1  | 0  |

| Level 1                       | 0  | 1  |

| Level 2                       | 0  | 0  |

| Level 3 (= interrupt disable) | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/ cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

## 6 CLOCKS AND RESET

#### 6.1 CLOCK SYSTEM

#### 6.1.1 General Description

The MCU accepts either a Crystal or Ceramic resonator, or an external clock signal to drive the internal oscillator. The internal clock ( $f_{CPU}$ ) is derived from the external oscillator frequency ( $f_{OSC}$ ), by dividing by 3 and multiplying by 2. By setting the OSC12/6 bit in the option byte, a 12 MHz external clock can be used giving an internal frequency of 8 MHz while maintaining a 6 MHz clock for USB (refer to Figure 14).

The internal clock signal (f<sub>CPU</sub>) consists of a square wave with a duty cycle of 50%.

It is further divided by 1, 2, 4 or 8 depending on the Slow Mode Selection bits in the Miscellaneous register (SMS[1:0])

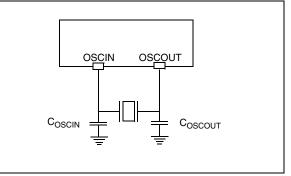

The internal oscillator is designed to operate with an AT-cut parallel resonant quartz or ceramic resonator in the frequency range specified for  $f_{osc}$ . The circuit shown in Figure 13 is recommended when using a crystal, and Table 4 lists the recommended capacitors. The crystal and associated components should be mounted as close as possible to the input pins in order to minimize output distortion and start-up stabilization time.

# Table 4. RecommendedValuesfor12MHzCrystal Resonator

| R <sub>SMAX</sub>   | <b>20</b> Ω | <b>25</b> Ω | <b>70</b> Ω |

|---------------------|-------------|-------------|-------------|

| C <sub>OSCIN</sub>  | 56pF        | 47pF        | 22pF        |

| C <sub>OSCOUT</sub> | 56pF        | 47pF        | 22pF        |

| R <sub>P</sub>      | 1-10 MΩ     | 1-10 MΩ     | 1-10 MΩ     |

**Note:** R<sub>SMAX</sub> is the equivalent serial resistor of the crystal (see crystal specification).

**Note:** When a crystal is used, and to not overstress the crystal, ST recommends to add a serial resistor on the OSCOUT pin to limit the drive level in accordance with the crystal manufacturer's specification. Please also refer to Section 12.5.4.

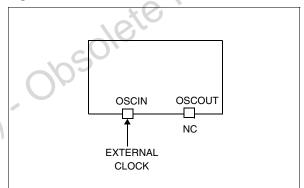

#### 6.1.2 External Clock input

An external clock may be applied to the OSCIN input with the OSCOUT pin not connected, as shown on Figure 12. The  $t_{OXOV}$  specifications does not apply when using an external clock input. The equivalent specification of the external clock source should be used instead of  $t_{OXOV}$  (see Electrical Characteristics).

#### 6.1.3 Clock Output Pin (MCO)

The internal clock (f<sub>CPU</sub>) can be output on Port B0 by setting the MCO bit in the Miscellaneous register.

#### Figure 12. External Clock Source Connections

Doc ID 6996 Rev 5

## 7 INTERRUPTS

## 7.1 INTRODUCTION

The CPU enhanced interrupt management provides the following features:

- Hardware interrupts

- Software interrupt (TRAP)

- Nested or concurrent interrupt management with flexible interrupt priority and level management:

- Up to 4 software programmable nesting levels

- Up to 16 interrupt vectors fixed by hardware

- 3 non maskable events: RESET, TRAP, TLI This interrupt management is based on:

- Bit 5 and bit 3 of the CPU CC register (I1:0),

- Interrupt software priority registers (ISPRx),

- Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nested) CPU interrupt controller.

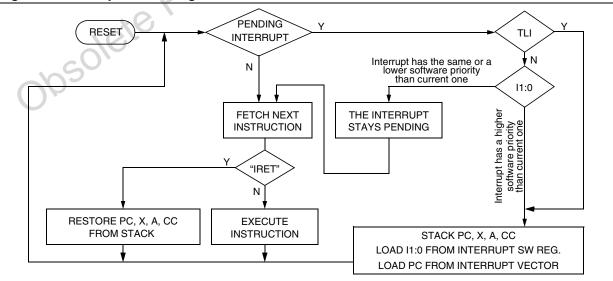

## 7.2 MASKING AND PROCESSING FLOW

The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of each interrupt vector (see Table 5). The processing flow is shown in Figure 20.

#### Figure 20. Interrupt Processing Flowchart

When an interrupt request has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to "Interrupt Mapping" table for vector addresses).

The interrupt service routine should end with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note**: As a consequence of the IRET instruction, the I1 and I0 bits will be restored from the stack and the program in the previous level will resume.

## Table 5. Interrupt Software Priority Levels

| Interrupt software priority   | Level | l1 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | ▼     | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

## 9 I/O PORTS

### 9.1 INTRODUCTION

The I/O ports offer different functional modes:

transfer of data through digital inputs and outputs and for specific pins:

- Analog signal input (ADC)

- Alternate signal input/output for the on-chip peripherals.

- External interrupt generation

An I/O port is composed of up to 8 pins. Each pin can be programmed independently as digital input or digital output.

#### 9.2 FUNCTIONAL DESCRIPTION

Each port is associated with 2 main registers:

- Data Register (DR)

- Data Direction Register (DDR)

Each I/O pin may be programmed using the corresponding register bits in DDR register: bit x corresponding to pin x of the port. The same correspondence is used for the DR register.

#### Table 8. I/O Pin Functions

| DDR | MODE   |

|-----|--------|

| 0   | Input  |

| 1   | Output |

#### 9.2.1 Input Modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

#### Notes:

- 1. All the inputs are triggered by a Schmitt trigger.

- When switching from input mode to output mode, the DR register should be written first to output the correct value as soon as the port is configured as an output.

#### Interrupt function

When an external interrupt function of an I/O pin, is enabled using the ITFRE registers, an event on this I/O can generate an external Interrupt request to the CPU. The interrupt sensitivity is programmable, the options are given in the description of the ITRFRE interrupt registers.

Each pin can independently generate an Interrupt request.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see Interrupts section). If more than one input pin is selected simultaneously as interrupt source, this is logically AN-Ded and inverted. For this reason, if an event occurs on one of the interrupt pins, it masks the other ones.

#### 9.2.2 Output Mode

The pin is configured in output mode by setting the corresponding DDR register bit (see Table 7).

In this mode, writing "0" or "1" to the DR register applies this digital value to the I/O pin through the latch. Then reading the DR register returns the previously stored value.

**Note**: In this mode, the interrupt function is disabled.

#### 9.2.3 Alternate Functions

#### **Digital Alternate Functions**

When an on-chip peripheral is configured to use a pin, the alternate function is automatically selected. This alternate function takes priority over standard I/O programming. When the signal is coming from an on-chip peripheral, the I/O pin is automatically configured in output mode (push-pull or open drain according to the peripheral).

When the signal is going to an on-chip peripheral, the I/O pin has to be configured in input mode. In this case, the pin state is also digitally readable by addressing the DR register.

#### Notes:

- 1. Input pull-up configuration can cause an unexpected value at the alternate peripheral input.

- When the on-chip peripheral uses a pin as input and output, this pin must be configured as an input (DDR = 0).

*Warning*: Alternate functions of peripherals must must not be activated when the external interrupts are enabled on the same pin, in order to avoid generating spurious interrupts.

### PWM AUTO-RELOAD TIMER (Cont'd)

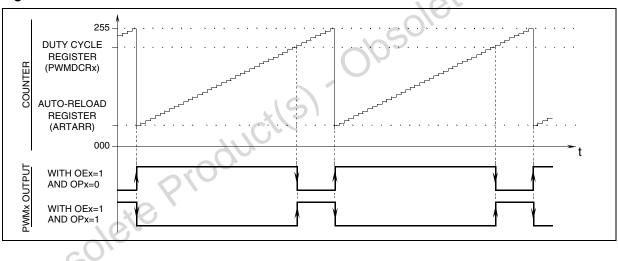

#### Independent PWM signal generation

This mode allows up to two Pulse Width Modulated signals to be generated on the PWMx output pins with minimum core processing overhead. This function is stopped during HALT mode.

Each PWMx output signal can be selected independently using the corresponding OEx bit in the PWM Control register (PWMCR). When this bit is set, the corresponding I/O pin is configured as output push-pull alternate function.

The PWM signals all have the same frequency which is controlled by the counter period and the ARTARR register value.

$f_{PWM} = f_{COUNTER} / (256 - ARTARR)$

When a counter overflow occurs, the PWMx pin level is changed depending on the corresponding OPx (output polarity) bit in the PWMCR register.

Figure 33. PWM Auto-reload Timer Function

57

When the counter reaches the value contained in one of the output compare register (OCRx) the corresponding PWMx pin level is restored.

It should be noted that the reload values will also affect the value and the resolution of the duty cycle of the PWM output signal. To obtain a signal on a PWMx pin, the contents of the OCRx register must be greater than the contents of the ARTARR register.

The maximum available resolution for the PWMx duty cycle is:

Resolution = 1 / (256 - ARTARR)

**Note**: To get the maximum resolution (1/256), the ARTARR register must be 0. With this maximum resolution, 0% and 100% can be obtained by changing the polarity.

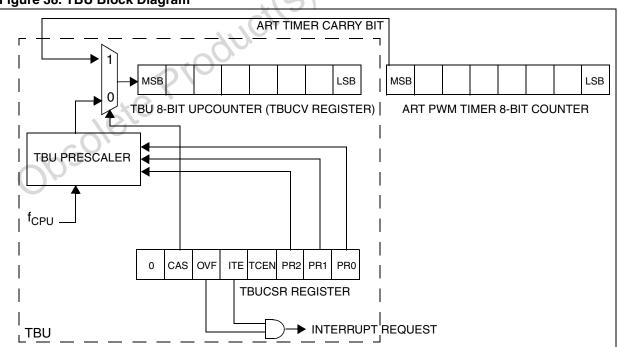

#### 10.3 TIMEBASE UNIT (TBU)

#### 10.3.1 Introduction

The Timebase unit (TBU) can be used to generate periodic interrupts.

#### 10.3.2 Main Features

- 8-bit upcounter

- Programmable prescaler

- Period between interrupts: max. 8.1ms (at 8) MHz f<sub>CPU</sub>)

- Maskable interrupt

- Cascadable with PWM/ART TImer

#### **10.3.3 Functional Description**

The TBU operates as a free-running upcounter.

When the TCEN bit in the TBUCSR register is set by software, counting starts at the current value of the TBUCV register. The TBUCV register is incremented at the clock rate output from the prescaler selected by programming the PR[2:0] bits in the TBUCSR register.

When the counter rolls over from FFh to 00h, the OVF bit is set and an interrupt request is generated if ITE is set.

The user can write a value at any time in the TBUCV register.

If the cascading option is selected (CAS bit=1 in the TBUCSR register), the TBU and the ART TImer counters act together as a 16-bit counter. In this case, the TBUCV register is the high order byte, the ART counter (ARTCAR register) is the low order byte. Counting is clocked by the ART timer clock (Refer to the description of the ART Timer ARTCSR register).

#### 10.3.4 Programming Example

In this example, timer is required to generate an interrupt after a delay of 1 ms.

Assuming that f<sub>CPU</sub> is 8 MHz and a prescaler division factor of 256 will be programmed using the PR[2:0] bits in the TBUCSR register, 1 ms = 32 TBU timer ticks.

In this case, the initial value to be loaded in the TBUCV must be (256-32) = 224 (E0h).

Prescaler factor = 256, interrupt enable, TBU enable

#### Figure 38. TBU Block Diagram

57/

### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.5.4.3 Receiver

The SCI can receive data words of either 8 or 9 bits. When the M bit is set, word length is 9 bits and the MSB is stored in the R8 bit in the SCICR1 register.

#### **Character reception**

During a SCI reception, data shifts in least significant bit first through the RDI pin. In this mode, the SCIDR register consists or a buffer (RDR) between the internal bus and the received shift register (see Figure 46).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIERPR registers.

- Set the RE bit, this enables the receiver which begins searching for a start bit.

When a character is received:

- The RDRF bit is set. It indicates that the content of the shift register is transferred to the RDR.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CC register.

- The error flags can be set if a frame error, noise or an overrun error has been detected during reception.

Clearing the RDRF bit is performed by the following software sequence done by:

- 1. An access to the SCISR register

- 2. A read to the SCIDR register.

The RDRF bit must be cleared before the end of the reception of the next character to avoid an overrun error.

#### **Break Character**

When a break character is received, the SCI handles it as a framing error.

#### **Idle Character**

When a idle frame is detected, there is the same procedure as a data received character plus an interrupt if the ILIE bit is set and the I bit is cleared in the CC register.

#### **Overrun Error**

An overrun error occurs when a character is received when RDRF has not been reset. Data can not be transferred from the shift register to the RDR register as long as the RDRF bit is not cleared.

When an overrun error occurs:

- The OR bit is set.

- The RDR content is not lost.

- The shift register is overwritten.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CC register.

The OR bit is reset by an access to the SCISR register followed by a SCIDR register read operation.

#### Noise Error

Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise. Normal data bits are considered valid if three consecutive samples (8th, 9th, 10th) have the same bit value, otherwise the NF flag is set. In the case of start bit detection, the NF flag is set on the basis of an algorithm combining both valid edge detection and three samples (8th, 9th, 10th). Therefore, to prevent the NF flag getting set during start bit reception, there should be a valid edge detection as well as three valid samples.

When noise is detected in a frame:

- The NF flag is set at the rising edge of the RDRF bit.

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The NF flag is reset by a SCISR register read operation followed by a SCIDR register read operation.

During reception, if a false start bit is detected (e.g. 8th, 9th, 10th samples are 011,101,110), the frame is discarded and the receiving sequence is not started for this frame. There is no RDRF bit set for this frame and the NF flag is set internally (not accessible to the user). This NF flag is accessible along with the RDRF bit when a next valid frame is received.

**Note:** If the application Start Bit is not long enough to match the above requirements, then the NF Flag may get set due to the short Start Bit. In this case, the NF flag may be ignored by the application software when the first valid byte is received.

See also Section 10.5.4.10.

## SERIAL COMMUNICATIONS INTERFACE (Cont'd) DATA REGISTER (SCIDR)

#### Read/Write

#### Reset Value: Undefined

Contains the Received or Transmitted data character, depending on whether it is read from or written to.

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

The Data register performs a double function (read and write) since it is composed of two registers, one for transmission (TDR) and one for reception (RDR).

The TDR register provides the parallel interface between the internal bus and the output shift register (see Figure 46).

The RDR register provides the parallel interface between the input shift register and the internal bus (see Figure 46).

## **BAUD RATE REGISTER (SCIBRR)**

Read/Write

Reset Value: 0000 0000 (00h)

| _ |  |

|---|--|

|   |  |

| 1 |  |

| SCP1 | SCDU | SCT2 | SCT1 | SCTO | SCBO  | SCP1 | SCBO  |

|------|------|------|------|------|-------|------|-------|

| 3011 | 3010 | 3012 | 3011 | 3010 | 30112 | Sonr | 30110 |

|      |      |      |      |      |       |      |       |

|      |      |      |      |      |       |      |       |

## Bits 7:6 = SCP[1:0] First SCI Prescaler

These 2 prescaling bits allow several standard clock division ranges:

| PR Prescaling factor | SCP1 | SCP0 |

|----------------------|------|------|

| cD'                  | 0    | 0    |

| -3                   | 0    | 1    |

| 4                    | 1    | 0    |

| 13                   | 1    | 1    |

Bits 5:3 = SCT[2:0] SCI Transmitter rate divisor These 3 bits, in conjunction with the SCP1 & SCP0 bits define the total division applied to the bus clock to yield the transmit rate clock in conventional Baud Rate Generator mode.

| TR dividing factor | SCT2 | SCT1 | SCT0 |   |

|--------------------|------|------|------|---|

| 1                  | 0    | 0    | 0    |   |

| 2                  | 0    | 0    | 1    |   |

| 4                  | 0    | 1    | 0    |   |

| 8                  | 0    | 1    | 1    |   |

| 16                 | 1    | 0    | 0    | 5 |

| 32                 | 1    | 0    |      |   |

| 64                 | 1    | 1    | 0    |   |

| 128                | 1    | 0    | 1    |   |

Bits 2:0 = **SCR[2:0]** *SCI Receiver rate divisor.* These 3 bits, in conjunction with the SCP[1:0] bits define the total division applied to the bus clock to yield the receive rate clock in conventional Baud Rate Generator mode.

| RR Dividing factor | SCR2 | SCR1 | SCR0 |

|--------------------|------|------|------|

|                    | 0    | 0    | 0    |

| 2                  | 0    | 0    | 1    |

| 4                  | 0    | 1    | 0    |

| 8                  | 0    | 1    | 1    |

| 16                 | 1    | 0    | 0    |

| 32                 | 1    | 0    | 1    |

| 64                 | 1    | 1    | 0    |

| 128                | 1    | 1    | 1    |

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### Address Register 7 5 6 4 3 2 1 0 Name (Hex.) SCIERPR ERPR7 ERPR6 ERPR5 ERPR4 ERPR3 ERPR2 ERPR1 ERPR0 1D **Reset Value** 0 0 0 0 0 0 0 0 ETPR6 ETPR3 ETPR2 SCIETPR ETPR7 ETPR5 ETPR4 ETPR1 ETPR0 1E **Reset Value** 0 0 0 0 0 0 0 0 TDRE тс RDRF IDLE OR NF FE ΡE SCISR 20 **Reset Value** 0 0 0 0 0 0 1 1 SCIDR DR7 DR6 DR5 DR4 DR3 DR2 DR1 DRO 21 **Reset Value** х х х х х х х x SCIBRR SCP1 SCP0 SCT2 SCT1 SCT0 SCR2 SCR1 SCR0 22 **Reset Value** 0 0 0 0 0 0 0 0 SCICR1 R8 Τ8 SCID Μ WAKE PCE PS PIE 23 **Reset Value** 0 0 0 0 0 х 0 0 obsolete Producils) SCICR2 TIE TCIE RIE ILIE ΤE RE RWU SBK 24 0 0 0

#### Table 22. SCI Register Map and Reset Values

## USB INTERFACE (Cont'd) PID REGISTER (PIDR)

Read only

Reset Value: xx00 0000 (x0h)

| 7   |     |   |   |   |            |     | 0 |

|-----|-----|---|---|---|------------|-----|---|

| TP3 | TP2 | 0 | 0 | 0 | RX_<br>SEZ | RXD | 0 |

Bits 7:6 = **TP[3:2]** *Token PID bits 3 & 2*. USB token PIDs are encoded in four bits. **TP[3:2]** correspond to the variable token PID bits 3 & 2. **Note:** PID bits 1 & 0 have a fixed value of 01. When a CTR interrupt occurs (see register ISTR) the software should read the TP3 and TP2 bits to retrieve the PID name of the token received. The USB standard defines TP bits as:

| TP3 | TP2 | PID Name |

|-----|-----|----------|

| 0   | 0   | OUT      |

| 1   | 0   | IN       |

| 1   | 1   | SETUP    |

Bits 5:3 Reserved. Forced by hardware to 0.

Bit 2 = **RX\_SEZ** Received single-ended zero This bit indicates the status of the RX\_SEZ transceiver output.

- 0: No SEO (single-ended zero) state

- 1: USB lines are in SE0 (single-ended zero) state

Bit 1 = **RXD** Received data

0: No K-state

1: USB lines are in K-state

This bit indicates the status of the RXD transceiver output (differential receiver output).

**Note:** If the environment is noisy, the RX\_SEZ and RXD bits can be used to secure the application. By interpreting the status, software can distinguish a valid End Suspend event from a spurious wake-up due to noise on the external USB line. A valid End Suspend is followed by a Resume or Reset sequence. A Resume is indicated by RXD=1, a Reset is indicated by RX\_SEZ=1.

Bit 0 = Reserved. Forced by hardware to 0.

#### **INTERRUPT STATUS REGISTER (ISTR)**

Read / Write Reset Value: 0000 0000 (00h)

| 7    |      |     |     |      |       |       | 0   |  |

|------|------|-----|-----|------|-------|-------|-----|--|

| SUSP | DOVR | CTR | ERR | IOVR | ESUSP | RESET | SOF |  |

When an interrupt occurs these bits are set by hardware. Software must read them to determine the interrupt type and clear them after servicing. **Note:** These bits cannot be set by software.

#### Bit 7 = **SUSP** Suspend mode request.

This bit is set by hardware when a constant idle state is present on the bus line for more than 3 ms, indicating a suspend mode request from the USB bus. The suspend request check is active immediately after each USB reset event and its disabled by hardware when suspend mode is forced (FSUSP bit of CTLR register) until the end of resume sequence.

#### Bit 6 = **DOVR** DMA over/underrun.

This bit is set by hardware if the ST7 processor can't answer a DMA request in time. 0: No over/underrun detected 1: Over/underrun detected

Bit 5 = CTR Correct Transfer. This bit is set by hardware when a correct transfer operation is performed. The type of transfer can be determined by looking at bits TP3-TP2 in register PIDR. The Endpoint on which the transfer was made is identified by bits EP1-EP0 in register IDR.

0: No Correct Transfer detected

1: Correct Transfer detected

**Note:** A transfer where the device sent a NAK or STALL handshake is considered not correct (the host only sends ACK handshakes). A transfer is considered correct if there are no errors in the PID and CRC fields, if the DATA0/DATA1 PID is sent as expected, if there were no data overruns, bit stuffing or framing errors.

#### Bit 4 = **ERR** Error.

This bit is set by hardware whenever one of the errors listed below has occurred:

- 0: No error detected

- 1: Timeout, CRC, bit stuffing or nonstandard framing error detected

## 10.7 10-BIT A/D CONVERTER (ADC)

#### 10.7.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 8 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 8 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

#### 10.7.2 Main Features

- 10-bit conversion

- Up to 8 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

- Conversion complete status flag

- Continuous or One-Shot mode

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 52.

#### **10.7.3 Functional Description**

#### 10.7.3.1 Analog Power Supply

Depending on the MCU pin count, the package may feature separate  $V_{DDA}$  and  $V_{SSA}$  analog power supply pins. These pins supply power to the A/D converter cell and function as the high and low reference voltages for the conversion. In smaller packages  $V_{DDA}$  and  $V_{SSA}$  pins are not available and the analog supply and reference pads are internally bonded to the  $V_{DD}$  and  $V_{SS}$  pins.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines.

#### 10.7.3.2 PCB Design Guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB. The analog power plane should be connected to the digital power plane via an RC network.

- Filter power to the analog power planes. The best solution is to connect a  $0.1\mu$ F capacitor, with good high frequency characteristics, between  $V_{DDA}$  and  $V_{SSA}$  and place it as close as possible to the  $V_{DDA}$  and  $V_{SSA}$  pins and connect the analog and digital power supplies in a star network. Do not use a resistor, as  $V_{DDA}$  is used as a reference voltage by the A/D converter and resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signal from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs on the same I/O port as the A/D input being converted.

## 10.7.3.3 Digital A/D Conversion Result

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than  $V_{DDA}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRMSB register and 03h in the ADCDRLSB register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRMSB and ADCDRLSB registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRMSB and ADCDRLSB registers. The accuracy of the conversion is described in the Electrical Characteristics Section.

$R_{AIN}$  is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the allotted time.

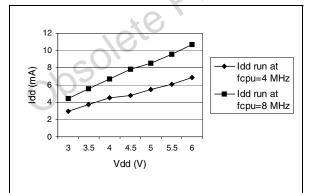

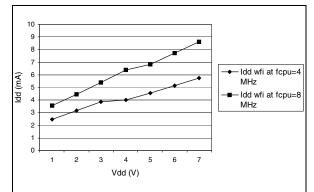

## **12.4 SUPPLY CURRENT CHARACTERISTICS**

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for HALT mode for which the clock is stopped).

| Symbol                     | Parameter                                | Conditio                                                   | <b>Typ</b> <sup>1)</sup> | Max                | Unit |    |

|----------------------------|------------------------------------------|------------------------------------------------------------|--------------------------|--------------------|------|----|

| $\Delta I_{DD(\Delta Ta)}$ | Supply current variation vs. temperature | Constant V <sub>DD</sub> and f <sub>CPU</sub>              |                          |                    | 10   | %  |

|                            |                                          | I/Os in input mode.                                        | f <sub>CPU</sub> = 4 MHz | 6                  | 8    | _  |

|                            | CPU RUN mode                             | USB transceiver and LVD disabled                           | f <sub>CPU</sub> = 8 MHz | 8                  | 14   | mA |

|                            |                                          | LVD enabled. USB in                                        | f <sub>CPU</sub> = 4 MHz | 13                 | 18   | mA |

|                            |                                          | Transmission <sup>2)</sup>                                 | f <sub>CPU</sub> = 8 MHz | 15                 | 24   | mA |

| I <sub>DD</sub>            | CPU WAIT mode <sup>2)</sup>              | I/Os in input mode.<br>USB transceiver and<br>LVD disabled | f <sub>CPU</sub> = 8 MHz | 7                  | 12   | mA |

|                            |                                          | LVD enabled. USB in<br>Transmission                        | f <sub>CPU</sub> = 8 MHz | 14                 | 22   | mA |

|                            | CPU HALT mode <sup>3)</sup>              | with LVD                                                   | 20                       | 130                | 200  | μA |

|                            | of officer mode                          | without LVD                                                | 0                        | 30                 | 50   | μΛ |

|                            | USB Suspend mode <sup>4)</sup>           |                                                            |                          | 130                | 200  | μA |

| I <sub>DD(ADC)</sub>       | ADC supply current when converting       | f <sub>ADC</sub> =4M                                       | Hz                       | 1000 <sup>2)</sup> |      | μA |

- Note 1: Typical data are based on T<sub>A</sub>=25°C and not tested in production

- Note 2: Data based on design simulation, not tested in production.

- Note 3: USB Transceiver and ADC are powered down.

- Note 4: Low voltage reset function enabled. CPU in HALT mode. Current consumption of external pull-up (1.5Kohms to USBVCC) and pull-down (15Kohms to V<sub>SSA</sub>) not included.

## Figure 56. Typ. I<sub>DD</sub> in RUN at 4 and 8 MHz f<sub>CPU</sub>

## Figure 57. Typ. I<sub>DD</sub> in WAIT at 4 and 8 MHz f<sub>CPU</sub>

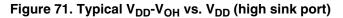

## I/O PORT PIN CHARACTERISTICS (Cont'd)

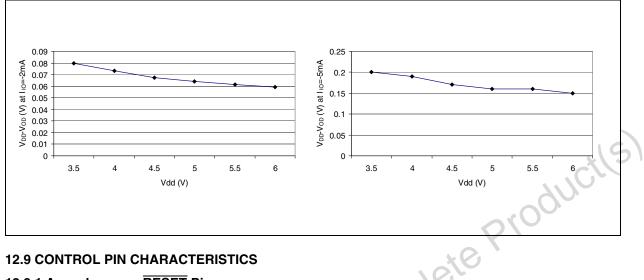

## **12.9 CONTROL PIN CHARACTERISTICS**

## 12.9.1 Asynchronous RESET Pin

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                  | Parameter                             | Conditions                       |                      | Min                 | <b>Typ</b> <sup>1)</sup> | Max                 | Unit                 |

|-------------------------|---------------------------------------|----------------------------------|----------------------|---------------------|--------------------------|---------------------|----------------------|

| V <sub>IH</sub>         | Input High Level Voltage              |                                  |                      | 0.7xV <sub>DD</sub> |                          | V <sub>DD</sub>     | V                    |

| V <sub>IL</sub>         | Input Low Voltage                     |                                  |                      | V <sub>SS</sub>     |                          | 0.3xV <sub>DD</sub> | V                    |

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis 3) | 191                              |                      |                     | 400                      |                     | mV                   |

| V                       | Output low level voltage 4)           | V <sub>DD</sub> =5V              | I <sub>IO</sub> =5mA |                     |                          | 1 <sup>2)</sup>     | v                    |

| V <sub>OL</sub>         | (see Figure 73, Figure 74)            | v <sub>DD</sub> =3v              | I <sub>IO</sub> =2mA |                     |                          | 0.4 <sup>2)</sup>   | v                    |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor 5)   | V <sub>IN</sub> =V <sub>SS</sub> |                      |                     | 60                       |                     | kΩ                   |

| t (= ===)               | Generated reset pulse duration        | External p                       |                      |                     | 6                        |                     | 1/f <sub>SFOSC</sub> |

| t <sub>w(RSTL)out</sub> | denerated reset pulse duration        | internal re                      | eset sources         |                     | 30                       |                     | μs                   |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time 6)     |                                  |                      | 10                  |                          |                     | μS                   |

#### Notes:

1. Unless otherwise specified, typical data are based on T<sub>A</sub>=25°C and V<sub>DD</sub>=5V, not tested in production.

2. Data guaranteed by design.

3. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

4. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2 and the sum of I<sub>IO</sub> (I/ O ports and control pins) must not exceed I<sub>VSS</sub>.

5. The R<sub>ON</sub> pull-up equivalent resistor is based on a resistive transistor (corresponding I<sub>ON</sub> current characteristics described in Figure 72). This data is based on characterization results, not tested in production.

To guarantee the reset of the device, a minimum pulse has to be applied to RESET pin. All short pulses applied on RESET pin with a duration below th(RSTL)in can be ignored.

## CONTROL PIN CHARACTERISTICS (Cont'd)

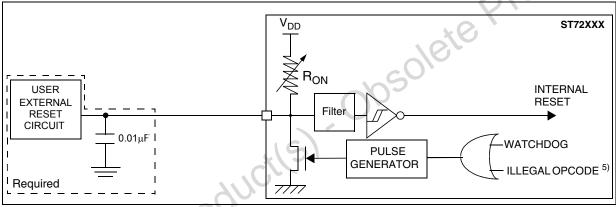

## Figure 75. RESET pin protection when LVD is enabled.<sup>1)2)3)4)</sup>

#### Note 1:

- The reset network protects the device against parasitic resets.

- The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

- Whatever the reset source is (internal or external), the user must ensure that the level on the RESET pin can go below the V<sub>IL</sub> max. level specified in section 12.9.1 on page 113. Otherwise the reset will not be taken into account internally.

- Because the reset circuit is designed to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin is less than the absolute maximum value specified for I<sub>INJ(RESET)</sub> in section 12.2.2 on page 102.

**Note 2:** When the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

**Note 3:** In case a capacitive power supply is used, it is recommended to connect a 1M $\Omega$  pull-down resistor to the RESET pin to discharge any residual voltage induced by the capacitive effect of the power supply (this will add 5µA to the power consumption of the MCU).

Note 4: Tips when using the LVD:

- 1. Check that all recommendations related to the reset circuit have been applied (see notes above).

- 2. Check that the power supply is properly decoupled (100nF + 10 $\mu$ F close to the MCU). Refer to AN1709 and AN2017. If this cannot be done, it is recommended to put a 100nF + 1M $\Omega$  pull-down on the RESET pin.

- 3. The capacitors connected on the RESET pin and also the power supply are key to avoid any start-up marginality. <u>In most</u> cases, steps 1 and 2 above are sufficient for a robust solution. Otherwise: replace 10nF pull-down on the RESET pin with a 5µF to 20µF capacitor."

## **12.10 TIMER PERIPHERAL CHARACTERISTICS**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output...).

### 12.10.1 8-Bit PWM-ART Auto-Reload Timer

| Symbol                | Parameter                    | Conditions                      | Min | Тур | Max                 | Unit             |

|-----------------------|------------------------------|---------------------------------|-----|-----|---------------------|------------------|

| +                     | PWM resolution time          |                                 | 1   |     |                     | t <sub>CPU</sub> |

| t <sub>res(PWM)</sub> | P wiw resolution time        | f <sub>CPU</sub> =8MHz          | 125 |     |                     | ns               |

| f <sub>EXT</sub>      | ART external clock frequency |                                 | 0   |     | f <sub>CPU</sub> /2 | MHz              |

| f <sub>PWM</sub>      | PWM repetition rate          |                                 | 0   |     | f <sub>CPU</sub> /2 |                  |

| Res <sub>PWM</sub>    | PWM resolution               |                                 |     |     | 8                   | bit              |

| V <sub>OS</sub>       | PWM/DAC output step voltage  | V <sub>DD</sub> =5V, Res=8 bits |     | 20  | 21                  | mV               |

|                       |                              |                                 |     |     |                     |                  |

## ADC CHARACTERISTICS (Cont'd)

## 12.12.0.1 Analog Power Supply and Reference Pins

Depending on the MCU pin count, the package may feature separate  $V_{DDA}$  and  $V_{SSA}$  analog power supply pins. These pins supply power to the A/D converter cell and function as the high and low reference voltages for the conversion. In some packages  $V_{DDA}$  and  $V_{SSA}$  pins are not available (refer to Table 1, "Device Pin Description," on page 8). In this case the analog supply and reference pads are internally bonded to the  $V_{DD}$  and  $V_{SS}$  pins.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines (see Section 10.7.3.2 PCB Design Guidelines).

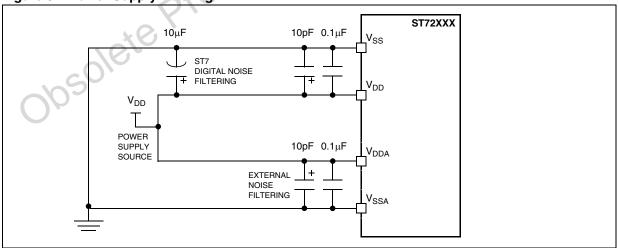

#### 12.12.0.2 General PCB Design Guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

- Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB.

- Filter power to the analog power planes. The best solution is to connect capacitors, with good

high frequency characteristics, between the power and ground lines, placing  $0.1\mu$ F and  $10\mu$ F capacitors as close as possible to the ST7 power supply pins and a  $10\mu$ F capacitor close to the power source (see Figure 84).

- The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>DDA</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs on the same I/O port as the A/D input being converted.

# 12.12.0.3 Specific Application Design Guidelines

- When a USB transmission is taking place during A/D conversion, the noise caused on the analog power supply by the USB transmission may result in a loss of ADC accuracy.

- If the USB is used to supply power to the application, this causes noise which may result in a loss of ADC accuracy.

#### Figure 84. Power Supply Filtering

## ADC CHARACTERISTICS (Cont'd)

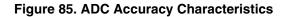

#### 12.12.1 ADC Accuracy

## Table 27. f<sub>CPU</sub>=8 MHz, f<sub>ADC</sub>=4 MHz R<sub>AIN</sub>< 10k $\Omega^{(2)}$

| Parameter                    | Conditions                                                                           | Тур                                                                               | Max <sup>1)</sup>                                                                             | Unit                                                                             |

|------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Total unadjusted error       |                                                                                      | 3                                                                                 |                                                                                               |                                                                                  |

| Offset error                 |                                                                                      | 1                                                                                 | 2                                                                                             | 1                                                                                |

| Gain Error                   | V <sub>DD</sub> = 4V-5.5V                                                            | 0.7                                                                               | 2                                                                                             | LSB                                                                              |

| Differential linearity error |                                                                                      | 1.3                                                                               | 2                                                                                             | 1                                                                                |

| Integral linearity error     |                                                                                      | 2.9                                                                               | 5                                                                                             | ]                                                                                |

|                              | Total unadjusted error<br>Offset error<br>Gain Error<br>Differential linearity error | Total unadjusted error   Offset error   Gain Error   Differential linearity error | Total unadjusted error 3   Offset error 1   Gain Error 0.7   Differential linearity error 1.3 | Total unadjusted error3Offset error1Gain Error0.7Differential linearity error1.3 |

Notes:

1. Not tested in production, guaranteed by characterization. All accuracy measurements are taken with the MCU in WAIT mode (no I/O switching) and when adequate low-pass filtering is present (0.1  $\mu$ F capacitor between V<sub>DD</sub>/V<sub>DDA</sub> and V<sub>SS</sub>/V<sub>SSA</sub>). Outside these conditions, a degree of microcontroller noise may result, causing accuracy errors which will vary based on board layout and the type of CPU activity.

2. ADC Accuracy vs. Negative Injection Current:

Injecting negative current on any of the analog input pins significantly reduces the accuracy of the conversion being performed on another analog input.

For I<sub>INJ</sub>=0.8mA, the typical leakage induced inside the die is 1.6µA and the effect on the ADC accuracy is a loss of 4 LSB for each 10KΩ increase of the external analog source impedance. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ</sub>(PIN) and ΣI<sub>INJ</sub>(PIN) in Section 12.8 does not affect the ADC accuracy.

122/139