#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                               |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 79                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 28x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560b50l3b4e0x |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

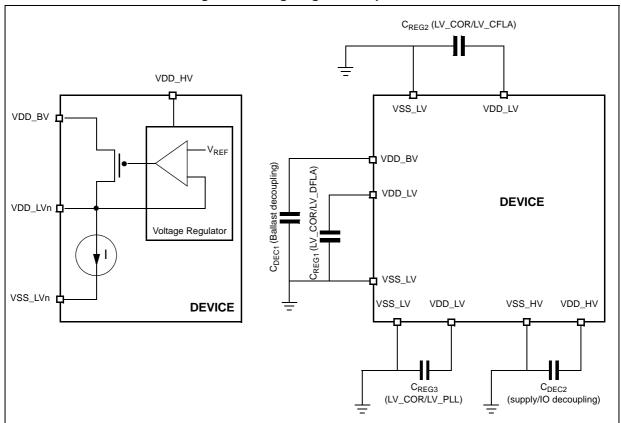

# 3.3 Voltage supply pins

Voltage supply pins are used to provide power to the device. Three dedicated VDD\_LV/VSS\_LV supply pairs are used for 1.2 V regulator stabilization.

| Bort nin   | Function                                                                                                                        | Pin number   |                       |                     |                                                                                       |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|---------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Port pin   | Function                                                                                                                        | LQFP64       | LQFP100               | LQFP144             | LBGA208 <sup>(1)</sup>                                                                |  |  |  |  |

| VDD_HV     | Digital supply voltage                                                                                                          | 7, 28, 56    | 15, 37, 70,<br>84     | 19, 51, 100,<br>123 | C2, D9, E16,<br>G13, H3, N9,<br>R5                                                    |  |  |  |  |

| VSS_HV     | Digital ground                                                                                                                  | 6, 8, 26, 55 | 14, 16, 35,<br>69, 83 |                     | G7, G8, G9,<br>G10, H1, H7,<br>H8, H9, H10,<br>J7, J8, J9,<br>J10, K7, K8,<br>K9, K10 |  |  |  |  |

| VDD_LV     | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest $V_{SS_LV}$ pin. <sup>(2)</sup> | 11, 23, 57   | 19, 32, 85            | 23, 46, 124         | D8, K4, P7                                                                            |  |  |  |  |

| VSS_LV     | 1.2V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest $V_{DD_LV}$ pin. <sup>(2)</sup> | 10, 24, 58   | 18, 33, 86            | 22, 47, 125         | C8, J2, N7                                                                            |  |  |  |  |

| VDD_BV     | Internal regulator supply voltage                                                                                               | 12           | 20                    | 24                  | K3                                                                                    |  |  |  |  |

| VSS_HV_ADC | Reference ground and analog ground for the ADC                                                                                  | 33           | 51                    | 73                  | R15                                                                                   |  |  |  |  |

| VDD_HV_ADC | Reference voltage and analog supply for the ADC                                                                                 | 34           | 52                    | 74                  | P14                                                                                   |  |  |  |  |

1. LBGA208 available only as development package for Nexus2+

2. A decoupling capacitor must be placed between each of the three VDD\_LV/VSS\_LV supply pairs to ensure stable voltage (see the recommended operating conditions in the device datasheet for details).

# 3.4 Pad types

In the device the following types of pads are available for system pins and functional port pins:

- $S = Slow^{(b)}$

- $M = Medium^{(b) (c)}$

- $F = Fast^{(b)}(c)$

- I = Input only with analog feature<sup>(b)</sup>

- J = Input/Output ('S' pad) with analog feature

- X = Oscillator

b. See the I/O pad electrical characteristics in the device datasheet for details.

|          |                                                                       |                                                          |                                                        |                                                  |                        | Pin number             |                        |         |         |                        |     |

|----------|-----------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------|------------------------|------------------------|------------------------|---------|---------|------------------------|-----|

| Port pin | PCR<br>Alternate<br>function <sup>(1)</sup><br>Function<br>Peripheral |                                                          | Peripheral                                             | I/O direction <sup>(2)</sup>                     | Pad type               | RESET<br>configuration | LQFP64                 | LQFP100 | LQFP144 | LBGA208 <sup>(3)</sup> |     |

| PA[7]    | PCR[7]                                                                | AF0<br>AF1<br>AF2<br>AF3<br>—                            | GPIO[7]<br>E0UC[7]<br>LIN3TX<br>—<br>EIRQ[2]           | SIUL<br>eMIOS_0<br>LINFlex_3<br>—<br>SIUL        | I/O<br>I/O<br>O<br>I   | S                      | Tristate               | 44      | 71      | 104                    | D16 |

| PA[8]    | PCR[8]                                                                | AF0<br>AF1<br>AF2<br>AF3<br>—<br>N/A <sup>(6)</sup><br>— | GPIO[8]<br>E0UC[8]<br>—<br>EIRQ[3]<br>ABS[0]<br>LIN3RX | SIUL<br>eMIOS_0<br>—<br>SIUL<br>BAM<br>LINFlex_3 |                        | S                      | Input, weak<br>pull-up | 45      | 72      | 105                    | C16 |

| PA[9]    | PCR[9]                                                                | AF0<br>AF1<br>AF2<br>AF3<br>N/A <sup>(6)</sup>           | GPIO[9]<br>E0UC[9]<br>—<br>FAB                         | SIUL<br>eMIOS_0<br>—<br>BAM                      | I/O<br>I/O<br>—<br>I   | S                      | Pull-down              | 46      | 73      | 106                    | C15 |

| PA[10]   | PCR[10]                                                               | AF0<br>AF1<br>AF2<br>AF3                                 | GPIO[10]<br>E0UC[10]<br>SDA<br>—                       | SIUL<br>eMIOS_0<br>I2C_0<br>—                    | I/O<br>I/O<br>I/O<br>— | S                      | Tristate               | 47      | 74      | 107                    | B16 |

| PA[11]   | PCR[11]                                                               | AF0<br>AF1<br>AF2<br>AF3                                 | GPIO[11]<br>E0UC[11]<br>SCL<br>—                       | SIUL<br>eMIOS_0<br>I2C_0<br>—                    | I/O<br>I/O<br>I/O      | S                      | Tristate               | 48      | 75      | 108                    | B15 |

| PA[12]   | PCR[12]                                                               | AF0<br>AF1<br>AF2<br>AF3<br>—                            | GPIO[12]<br>—<br>—<br>SIN_0                            | SIUL<br>—<br>—<br>DSPI0                          | I/O<br><br>I           | S                      | Tristate               | 22      | 31      | 45                     | Τ7  |

| PA[13]   | PCR[13]                                                               | AF0<br>AF1<br>AF2<br>AF3                                 | GPIO[13]<br>SOUT_0<br>—                                | SIUL<br>DSPI_0<br>—                              | I/O<br>O<br>—          | М                      | Tristate               | 21      | 30      | 44                     | R7  |

Table 6. Functional port pin descriptions (continued)

|          |                                             |                               |                                                                     |                                               | Pin number                   |          |                        |        |         |         |                        |

|----------|---------------------------------------------|-------------------------------|---------------------------------------------------------------------|-----------------------------------------------|------------------------------|----------|------------------------|--------|---------|---------|------------------------|

| Port pin | PCR<br>Alternate<br>function <sup>(1)</sup> |                               | Function                                                            | Peripheral                                    | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration | LQFP64 | LQFP100 | LQFP144 | LBGA208 <sup>(3)</sup> |

| PE[11]   | PCR[75]                                     | AF0<br>AF1<br>AF2<br>AF3<br>  | GPIO[75]<br>—<br>CS4_1<br>—<br>LIN3RX<br>WKPU[14] <sup>(4)</sup>    | SIUL<br>—<br>DSPI_1<br>—<br>LINFlex_3<br>WKPU | /O<br><br>0<br><br>1<br>     | S        | Tristate               |        | 13      | 17      | H2                     |

| PE[12]   | PCR[76]                                     | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[76]<br>—<br>E1UC[19] <sup>(13)</sup><br>—<br>SIN_2<br>EIRQ[11] | SIUL<br><br>eMIOS_1<br><br>DSPI_2<br>SIUL     | /O<br><br> /O<br><br> <br>   | S        | Tristate               | _      | 76      | 109     | C14                    |

| PE[13]   | PCR[77]                                     | AF0<br>AF1<br>AF2<br>AF3      | GPIO[77]<br>SOUT2<br>E1UC[20]<br>—                                  | SIUL<br>DSPI_2<br>eMIOS_1<br>—                | I/O<br>O<br>I/O<br>—         | S        | Tristate               | _      |         | 103     | D15                    |

| PE[14]   | PCR[78]                                     | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[78]<br>SCK_2<br>E1UC[21]<br>—<br>EIRQ[12]                      | SIUL<br>DSPI_2<br>eMIOS_1<br>—<br>SIUL        | I/O<br>I/O<br>I/O<br>I       | S        | Tristate               | _      |         | 112     | C13                    |

| PE[15]   | PCR[79]                                     | AF0<br>AF1<br>AF2<br>AF3      | GPIO[79]<br>CS0_2<br>E1UC[22]<br>—                                  | SIUL<br>DSPI_2<br>eMIOS_1<br>—                | I/O<br>I/O<br>I/O<br>—       | М        | Tristate               |        | _       | 113     | A13                    |

| PF[0]    | PCR[80]                                     | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[80]<br>E0UC[10]<br>CS3_1<br>—<br>ANS[8]                        | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>ADC         | I/O<br>I/O<br>O<br>I         | J        | Tristate               | _      | _       | 55      | N10                    |

| PF[1]    | PCR[81]                                     | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[81]<br>E0UC[11]<br>CS4_1<br>—<br>ANS[9]                        | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>I           | I/O<br>I/O<br>O<br>I         | J        | Tristate               | _      | _       | 56      | P10                    |

|          |         |                                      |                                                                                 |                                                  |                              |          |                        | Pin number |         |         |                        |  |

|----------|---------|--------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|----------|------------------------|------------|---------|---------|------------------------|--|

| Port pin | PCR     | Alternate<br>function <sup>(1)</sup> | Function                                                                        | Peripheral                                       | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration | LQFP64     | LQFP100 | LQFP144 | LBGA208 <sup>(3)</sup> |  |

| PF[9]    | PCR[89] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[89]<br>—<br>CS5_0<br>—<br>CAN2RX <sup>(15)</sup><br>CAN3RX <sup>(14)</sup> | SIUL<br><br>DSPI_0<br><br>FlexCAN_2<br>FlexCAN_3 | I/O<br>- O<br>- I<br>- I     | S        | Tristate               | _          | _       | 33      | N2                     |  |

| PF[10]   | PCR[90] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[90]<br>—<br>—<br>—                                                         | SIUL<br>—<br>—<br>—                              | I/O<br>                      | М        | Tristate               | _          |         | 38      | R3                     |  |

| PF[11]   | PCR[91] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[91]<br>—<br>—<br>—<br>WKPU[15] <sup>(4)</sup>                              | SIUL<br>—<br>—<br>—<br>WKPU                      | I/O<br><br>                  | S        | Tristate               |            |         | 39      | R4                     |  |

| PF[12]   | PCR[92] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[92]<br>E1UC[25]<br>—                                                       | SIUL<br>eMIOS_1<br>—                             | I/O<br>I/O<br>               | М        | Tristate               |            | _       | 35      | R1                     |  |

| PF[13]   | PCR[93] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[93]<br>E1UC[26]<br>—<br>—<br>WKPU[16] <sup>(4)</sup>                       | SIUL<br>eMIOS_1<br>—<br>WKPU                     | I/O<br>I/O<br>—<br>I         | S        | Tristate               | _          | _       | 41      | Т6                     |  |

| PF[14]   | PCR[94] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[94]<br>CAN4TX <sup>(11)</sup><br>E1UC[27]<br>CAN1TX                        | SIUL<br>FlexCAN_4<br>eMIOS_1<br>FlexCAN_4        | I/O<br>O<br>I/O<br>O         | М        | Tristate               | _          | _       | 102     | D14                    |  |

| PF[15]   | PCR[95] | AF0<br>AF1<br>AF2<br>AF3<br><br>     | GPIO[95]<br>—<br>—<br>CAN1RX<br>CAN4RX <sup>(11)</sup><br>EIRQ[13]              | SIUL<br>—<br>—<br>FlexCAN_1<br>FlexCAN_4<br>SIUL | /O<br><br><br> <br> <br>     | S        | Tristate               |            |         | 101     | E15                    |  |

|          |                                                                       |                               |                                                                      |                                                |                        | -      |          | Pin number |                        |    |     |  |

|----------|-----------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------|------------------------------------------------|------------------------|--------|----------|------------|------------------------|----|-----|--|

| Port pin | PCR<br>Alternate<br>function <sup>(1)</sup><br>Function<br>Peripheral |                               | I/O direction <sup>(2)</sup>                                         | Pad type                                       | RESET<br>configuration | LQFP64 | LQFP100  | LQFP144    | LBGA208 <sup>(3)</sup> |    |     |  |

| PG[0]    | PCR[96]                                                               | AF0<br>AF1<br>AF2<br>AF3      | GPIO[96]<br>CAN5TX <sup>(11)</sup><br>E1UC[23]<br>—                  | SIUL<br>FlexCAN_5<br>eMIOS_1<br>—              | I/O<br>O<br>I/O<br>—   | М      | Tristate |            |                        | 98 | E14 |  |

| PG[1]    | PCR[97]                                                               | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[97]<br>—<br>E1UC[24]<br>—<br>CAN5RX <sup>(11)</sup><br>EIRQ[14] | SIUL<br>—<br>eMIOS_1<br>—<br>FlexCAN_5<br>SIUL | I/O<br>I/O<br>I<br>I   | S      | Tristate | _          | _                      | 97 | E13 |  |

| PG[2]    | PCR[98]                                                               | AF0<br>AF1<br>AF2<br>AF3      | GPIO[98]<br>E1UC[11]<br>—                                            | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>         | Μ      | Tristate |            | _                      | 8  | E4  |  |

| PG[3]    | PCR[99]                                                               | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[99]<br>E1UC[12]<br>—<br>—<br>WKPU[17] <sup>(4)</sup>            | SIUL<br>eMIOS_1<br>—<br>WKPU                   | I/O<br>I/O<br> <br>    | S      | Tristate | _          | _                      | 7  | E3  |  |

| PG[4]    | PCR[100]                                                              | AF0<br>AF1<br>AF2<br>AF3      | GPIO[100]<br>E1UC[13]<br>—                                           | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>         | М      | Tristate | _          | _                      | 6  | E1  |  |

| PG[5]    | PCR[101]                                                              | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[101]<br>E1UC[14]<br>—<br>WKPU[18] <sup>(4)</sup>                | SIUL<br>eMIOS_1<br>—<br>WKPU                   | I/O<br>I/O<br>—<br>I   | S      | Tristate | _          |                        | 5  | E2  |  |

| PG[6]    | PCR[102]                                                              | AF0<br>AF1<br>AF2<br>AF3      | GPIO[102]<br>E1UC[15]<br>—                                           | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>         | М      | Tristate |            | _                      | 30 | M2  |  |

| Table 6. Functional port pin descriptions (continued) |

|-------------------------------------------------------|

|-------------------------------------------------------|

Most of the time for the applications,  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant, if the device is configured to continuously drive external modules and/or memories.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

#### Equation 2 $P_D = K / (T_J + 273 °C)$

Therefore, solving equations *Equation 1* and *Equation 2*:

#### Equation 3 K = $P_D x (T_A + 273 °C) + R_{\theta JA} x P_D^2$

Where:

K is a constant for the particular part, which may be determined from *Equation 3* by measuring P<sub>D</sub> (at equilibrium) for a known T<sub>A</sub>. Using this value of K, the values of P<sub>D</sub> and T<sub>J</sub> may be obtained by solving equations *Equation 1* and *Equation 2* iteratively for any value of T<sub>A</sub>.

## 3.15 I/O pad electrical characteristics

## 3.15.1 I/O pad types

The device provides four main I/O pad types depending on the associated alternate functions:

- Slow pads—These pads are the most common pads, providing a good compromise between transition time and low electromagnetic emission.

- Medium pads—These pads provide transition fast enough for the serial communication channels with controlled current to reduce electromagnetic emission.

- Fast pads—These pads provide maximum speed. There are used for improved Nexus debugging capability.

- Input only pads—These pads are associated to ADC channels and the external 32 kHz crystal oscillator (SXOSC) providing low input leakage.

Medium and Fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance.

## 3.15.2 I/O input DC characteristics

Table 16 provides input DC electrical characteristics as described in Figure 6.

|             |             |            |        |                           | LQFP144/ | LQFP100 | (0011111 |         | LQFI    | P64 <sup>(2)</sup> |         |  |

|-------------|-------------|------------|--------|---------------------------|----------|---------|----------|---------|---------|--------------------|---------|--|

| Sup         | ply seg     | ment       | Pad    | Weigh                     | nt 5 V   | Weigh   | t 3.3 V  | Weig    | ht 5 V  | Weight 3.3 V       |         |  |

| LQFP<br>144 | LQFP<br>100 | LQFP<br>64 |        | SRC <sup>(3)</sup> =<br>0 | SRC = 1  | SRC = 0 | SRC = 1  | SRC = 0 | SRC = 1 | SRC = 0            | SRC = 1 |  |

|             |             |            | PA[5]  | 5%                        | 7%       | 6%      | 6%       | 6%      | 8%      | 7%                 | 7%      |  |

| 2           | 3 3         | 2          | PA[6]  | 5%                        | —        | 6%      | _        | 5%      |         | 6%                 | _       |  |

| 3           | 3           | 2          | PH[10] | 4%                        | 6%       | 5%      | 5%       | 5%      | 7%      | 6%                 | 6%      |  |

|             |             |            | PC[1]  | 5%                        | —        | 5%      | _        | 5%      | _       | 5%                 | _       |  |

|             |             | 3          | PC[0]  | 6%                        | 9%       | 7%      | 8%       | 6%      | 9%      | 7%                 | 8%      |  |

|             |             | 3          | PH[9]  | 7                         | 7        | 8       | 8        | 7       | 7       | 8                  | 8       |  |

|             |             | _          | PE[2]  | 7%                        | 10%      | 9%      | 9%       | _       | _       | —                  | _       |  |

|             | 4           | _          | PE[3]  | 8%                        | 11%      | 9%      | 9%       |         |         | —                  |         |  |

|             | 4           | 3          | PC[5]  | 8%                        | 11%      | 9%      | 10%      | 8%      | 11%     | 9%                 | 10%     |  |

|             |             | 3          | PC[4]  | 8%                        | 12%      | 10%     | 10%      | 8%      | 12%     | 10%                | 10%     |  |

|             |             | _          | PE[4]  | 8%                        | 12%      | 10%     | 11%      | _       | _       | _                  | _       |  |

|             |             | _          | PE[5]  | 9%                        | 12%      | 10%     | 11%      | _       | _       | _                  | _       |  |

|             |             | _          | PH[4]  | 9%                        | 13%      | 11%     | 11%      |         |         | —                  |         |  |

| 4           |             | _          | PH[5]  | 9%                        | —        | 11%     |          |         |         | —                  |         |  |

|             |             | _          | PH[6]  | 9%                        | 13%      | 11%     | 12%      | _       | _       | _                  | _       |  |

|             |             |            | PH[7]  | 9%                        | 13%      | 11%     | 12%      | _       |         | _                  | _       |  |

|             |             |            | PH[8]  | 10%                       | 14%      | 11%     | 12%      | _       |         | _                  | _       |  |

|             |             | —          | PE[6]  | 10%                       | 14%      | 12%     | 12%      | —       | _       |                    | —       |  |

|             |             | _          | PE[7]  | 10%                       | 14%      | 12%     | 12%      |         |         | —                  |         |  |

|             |             | _          | PC[12] | 10%                       | 14%      | 12%     | 13%      | _       | _       | —                  | —       |  |

|             | 4           | —          | PC[13] | 10%                       | —        | 12%     |          |         |         | —                  |         |  |

|             |             |            | PC[8]  | 10%                       | —        | 12%     |          | 10%     |         | 12%                | —       |  |

|             |             | 3          | PB[2]  | 10%                       | 15%      | 12%     | 13%      | 10%     | 15%     | 12%                | 13%     |  |

## Table 24. I/O weight<sup>(1)</sup> (continued)

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to125 °C, unless otherwise specified

2. All LQFP64 information is indicative and must be confirmed during silicon validation.

3. SRC: "Slew Rate Control" bit in SIU\_PCR

# 3.16 **RESET** electrical characteristics

The device implements a dedicated bidirectional  $\overline{\text{RESET}}$  pin.

Figure 9. Voltage regulator capacitance connection

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device in order to provide a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the board to less than 5 nH.

Each decoupling capacitor must be placed between each of the three V<sub>DD\_LV</sub>/V<sub>SS\_LV</sub> supply pairs to ensure stable voltage (see *Section 3.13: Recommended operating conditions*).

The internal voltage regulator requires a controlled slew rate of both  $V_{DD_HV}$  and  $V_{DD_BV}$  as described in *Figure 10*.

released as soon as internal reset sequence is completed regardless of LVDHV5H threshold.

| Symbol                 |    | с | Parameter                                   | Conditions <sup>(1)</sup>                 |      | Unit |      |      |

|------------------------|----|---|---------------------------------------------|-------------------------------------------|------|------|------|------|

| Symbol                 |    | C | Falantelei                                  | Conditions                                | Min  | Тур  | Мах  | Unit |

| V <sub>PORUP</sub>     | SR | Ρ | Supply for functional POR module            | —                                         | 1.0  |      | 5.5  |      |

| V <sub>PORH</sub>      | сс | Ρ | Power-on reset threshold                    | T <sub>A</sub> = 25 °C,<br>after trimming | 1.5  | _    | 2.6  |      |

|                        |    | Т |                                             | —                                         | 1.5  | _    | 2.6  |      |

| V <sub>LVDHV3H</sub>   | СС | Т | LVDHV3 low voltage detector high threshold  |                                           | _    | _    | 2.95 |      |

| V <sub>LVDHV3L</sub>   | СС | Ρ | LVDHV3 low voltage detector low threshold   |                                           | 2.6  | _    | 2.9  | V    |

| V <sub>LVDHV5H</sub>   | СС | Т | LVDHV5 low voltage detector high threshold  |                                           |      |      | 4.5  |      |

| V <sub>LVDHV5L</sub>   | СС | Ρ | LVDHV5 low voltage detector low threshold   |                                           | 3.8  | _    | 4.4  |      |

| V <sub>LVDLVCORL</sub> | СС | Ρ | LVDLVCOR low voltage detector low threshold | ]                                         | 1.08 | _    | 1.16 |      |

| V <sub>LVDLVBKPL</sub> | СС | Ρ | LVDLVBKP low voltage detector low threshold |                                           | 1.08 | _    | 1.16 |      |

Table 27. Low voltage detector electrical characteristics

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified

# 3.18 Power consumption

*Table 28* provides DC electrical characteristics for significant application modes. These values are indicative values; actual consumption depends on the application.

| Symbol                            |    | с | Parameter                                       | Conditions <sup>(1)</sup>   |                         |     | Value |                           |    |   |    |     |  |

|-----------------------------------|----|---|-------------------------------------------------|-----------------------------|-------------------------|-----|-------|---------------------------|----|---|----|-----|--|

| Symbol                            |    | 0 | rarameter                                       | Conditions                  | Min                     | Тур | Max   | Unit                      |    |   |    |     |  |

| I <sub>DDMAX</sub> <sup>(2)</sup> | сс | D | RUN mode maximum<br>average current             | _                           |                         | _   | 115   | 140 <sup>(3)</sup>        | mA |   |    |     |  |

|                                   |    | Т |                                                 | f <sub>CPU</sub> = 8 MHz    |                         | _   | 7     |                           |    |   |    |     |  |

|                                   |    | Т |                                                 | f <sub>CPU</sub> = 16 MHz   |                         | _   | 18    |                           |    |   |    |     |  |

| I <sub>DDRUN</sub> <sup>(4)</sup> | сс | Т | RUN mode typical average current <sup>(5)</sup> | f <sub>CPU</sub> = 32 MHz   |                         | _   | 29    |                           | mA |   |    |     |  |

|                                   |    |   | -                                               |                             |                         | Ρ   |       | f <sub>CPU</sub> = 48 MHz |    | _ | 40 | 100 |  |

|                                   |    | Ρ |                                                 | f <sub>CPU</sub> = 64 MHz   |                         | _   | 51    | 125                       |    |   |    |     |  |

|                                   | сс | С | HALT mode current <sup>(6)</sup>                | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _   | 8     | 15                        | mA |   |    |     |  |

| IDDHALT                           | 00 |   |                                                 | (128 kHz) running           | T <sub>A</sub> = 125 °C |     | 14    | 25                        |    |   |    |     |  |

Table 28. Power consumption on VDD\_BV and VDD\_HV

## 3.19.3 Start-up/Switch-off timings

| Symbol                  |     | С | Parameter                                 | Conditions <sup>(1)</sup> |     | Unit |     |      |

|-------------------------|-----|---|-------------------------------------------|---------------------------|-----|------|-----|------|

| Symbol                  |     | C | Farameter                                 | Conditions                | Min | Тур  | Max | Unit |

| т                       | сс  | Т | Delay for Flash module to exit reset mode | Code Flash                | _   | —    | 125 |      |

| T <sub>FLARSTEXIT</sub> | 00  | Т | Delay for Flash module to exit reset mode | Data Flash                | —   | —    | 125 |      |

| т                       | сс  | Т | Delay for Flash module to exit low-power  | Code Flash                | _   | —    | 0.5 |      |

| T <sub>FLALPEXIT</sub>  |     | Т | mode                                      | Data Flash                | _   |      | 0.5 |      |

| <b>т</b>                | ~~  | Т | Delay for Flash module to exit power-down | Code Flash                | _   | _    | 30  |      |

| T <sub>FLAPDEXIT</sub>  | СС  | Т | mode                                      | Data Flash                | _   | _    | 30  | μs   |

| т                       | сс  | Т | Delay for Flash module to enter low-power | Code Flash                | —   | _    | 0.5 |      |

| T <sub>FLALPENTRY</sub> |     | Т | mode                                      | Data Flash                | _   | _    | 0.5 | 1    |

| <b>т</b>                | ~~~ | Т | Delay for Flash module to enter power-    | Code Flash                | _   | —    | 1.5 | 1    |

| T <sub>FLAPDENTRY</sub> | СС  | Т | down mode                                 | Data Flash                | _   | —    | 1.5 | 1    |

Table 33. Start-up time/Switch-off time

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified

# 3.20 Electromagnetic compatibility (EMC) characteristics

Susceptibility tests are performed on a sample basis during product characterization.

## 3.20.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user apply EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

- Software recommendations: The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

- Prequalification trials: Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the reset pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note *Software Techniques For Improving Microcontroller EMC Performance* (AN1015)).

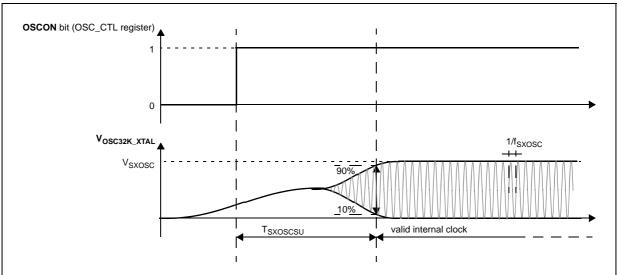

Figure 17. Slow external crystal oscillator (32 kHz) timing diagram

Table 40. Slow external crystal oscillator (32 kHz) electrical characteristics

| Symbol                 |    | с | Parameter                                      | Conditions <sup>(1)</sup> |     | Unit   |                  |      |

|------------------------|----|---|------------------------------------------------|---------------------------|-----|--------|------------------|------|

| Symbol                 |    | C | Falameter                                      | Conditions                | Min | Тур    | Max              | Unit |

| f <sub>sxosc</sub>     | SR |   | Slow external crystal oscillator frequency     | —                         | 32  | 32.768 | 40               | kHz  |

| V <sub>SXOSC</sub>     | СС | Т | Oscillation amplitude                          | _                         | _   | 2.1    | _                | V    |

| I <sub>SXOSCBIAS</sub> | СС | Т | Oscillation bias current                       | —                         | _   | 2.5    | _                | μΑ   |

| I <sub>SXOSC</sub>     | СС | Т | Slow external crystal oscillator consumption   | _                         | _   | —      | 8                | μΑ   |

| T <sub>SXOSCSU</sub>   | СС | Т | Slow external crystal oscillator start-up time |                           |     |        | 2 <sup>(2)</sup> | s    |

1.  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40$  to 125 °C, unless otherwise specified. Values are specified for no neighbor GPIO pin activity. If oscillator is enabled (OSC32K\_XTAL and OSC32K\_EXTAL pins), neighboring pins should not toggle.

2. Start-up time has been measured with EPSON TOYOCOM MC306 crystal. Variation may be seen with other crystal.

## 3.23 FMPLL electrical characteristics

The device provides a frequency-modulated phase-locked loop (FMPLL) module to generate a fast system clock from the main oscillator driver.

| Symbo               |        | с | Parameter                                       | Conditions <sup>(1)</sup> |     | Unit |     |      |

|---------------------|--------|---|-------------------------------------------------|---------------------------|-----|------|-----|------|

| Symbo               | Symbol |   | rarameter                                       | Conditions                | Min | Тур  | Max | Unit |

| f <sub>PLLIN</sub>  | SR     |   | FMPLL reference clock <sup>(2)</sup>            | _                         | 4   | —    | 64  | MHz  |

| $\Delta_{PLLIN}$    | SR     | _ | FMPLL reference clock duty cycle <sup>(2)</sup> | _                         | 40  | -    | 60  | %    |

| f <sub>PLLOUT</sub> | СС     | D | FMPLL output clock frequency                    | _                         | 16  | _    | 64  | MHz  |

| Symbo                           | a.l | с | Parameter                                     | Conditions <sup>(1)</sup>                                                             |     |     | Unit |      |

|---------------------------------|-----|---|-----------------------------------------------|---------------------------------------------------------------------------------------|-----|-----|------|------|

| Symbo                           |     | U | Parameter                                     | Conditions                                                                            | Min | Тур | Max  | Unit |

| f (3)                           | сс  |   | VCO frequency without<br>frequency modulation | —                                                                                     | 256 |     | 512  | MHz  |

| f <sub>VCO</sub> <sup>(3)</sup> | 00  | С | VCO frequency with frequency modulation       | —                                                                                     | 245 | _   | 533  |      |

| f <sub>CPU</sub>                | SR  |   | System clock frequency                        | —                                                                                     | _   | _   | 64   | MHz  |

| f <sub>FREE</sub>               | СС  | Ρ | Free-running frequency                        | —                                                                                     | 20  | —   | 150  | MHz  |

| t <sub>LOCK</sub>               | СС  | Ρ | FMPLL lock time                               | Stable oscillator (f <sub>PLLIN</sub> = 16 MHz)                                       | _   | 40  | 100  | μs   |

| $\Delta t_{STJIT}$              | СС  |   | FMPLL short term jitter <sup>(4)</sup>        | f <sub>sys</sub> maximum                                                              | -4  | _   | 4    | %    |

| $\Delta t_{LTJIT}$              | сс  | _ | FMPLL long term jitter                        | f <sub>PLLIN</sub> = 16 MHz (resonator),<br>f <sub>PLLCLK</sub> @ 64 MHz, 4000 cycles |     | _   | 10   | ns   |

| I <sub>PLL</sub>                | СС  | С | FMPLL consumption                             | T <sub>A</sub> = 25 °C                                                                | _   | _   | 4    | mA   |

Table 41. FMPLL electrical characteristics (continued)

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified.

2. PLLIN clock retrieved directly from FXOSC clock. Input characteristics are granted when oscillator is used in functional mode. When bypass mode is used, oscillator input clock should verify  $f_{PLLIN}$  and  $\Delta_{PLLIN}$ .

3. Frequency modulation is considered ±4%

4. Short term jitter is measured on the clock rising edge at cycle n and n+4.

# 3.24 Fast internal RC oscillator (16 MHz) electrical characteristics

The device provides a 16 MHz fast internal RC oscillator. This is used as the default clock at the power-up of the device.

| Symbo                 |    | С | Parameter                                                                   | Con                                                        | ditions <sup>(1)</sup> | Value |                |     | Unit         |   |     |   |  |

|-----------------------|----|---|-----------------------------------------------------------------------------|------------------------------------------------------------|------------------------|-------|----------------|-----|--------------|---|-----|---|--|

| Symbo                 | 1  | 0 | Falainetei                                                                  | Conditions                                                 |                        | Min   | Тур            | Max | Unit         |   |     |   |  |

| f                     | CC | Ρ | Fast internal RC oscillator high                                            | cillator high $T_A = 25 \text{ °C}$ , tr                   |                        | _     | 16             | _   | MHz          |   |     |   |  |

| <sup>†</sup> FIRC     | SR | _ | frequency                                                                   |                                                            |                        | 12    |                | 20  |              |   |     |   |  |

| I <sub>FIRCRUN</sub>  | сс | т | Fast internal RC oscillator high<br>frequency current in running mode       | T <sub>A</sub> = 25 °C, trimmed<br>T <sub>A</sub> = 125 °C |                        | _     | _              | 200 | μA           |   |     |   |  |

| I <sub>FIRCPWD</sub>  | сс | D | Fast internal RC oscillator high<br>frequency current in power down<br>mode |                                                            |                        | _     | _              | 10  | μA           |   |     |   |  |

|                       |    |   |                                                                             |                                                            |                        |       |                |     | sysclk = off | _ | 500 | _ |  |

|                       |    |   | Fast internal RC oscillator high                                            |                                                            | sysclk = 2 MHz         | _     | 600            | _   |              |   |     |   |  |

| I <sub>FIRCSTOP</sub> | СС | т | frequency and system clock current                                          | T <sub>A</sub> = 25 °C                                     | sysclk = 4 MHz         |       | 700            |     | μA           |   |     |   |  |

|                       |    |   |                                                                             |                                                            | in stop mode           |       | sysclk = 8 MHz |     | 900          | _ |     |   |  |

|                       |    |   |                                                                             |                                                            | sysclk = 16 MHz        | _     | 1250           | _   |              |   |     |   |  |

Table 42. Fast internal RC oscillator (16 MHz) electrical characteristics

| Sumbo                  | Symbol C Parameter |   | Parameter                                                                                                                                                 | Conditions <sup>(1)</sup>     |     |     | Unit |      |

|------------------------|--------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|------|------|

| Symbo                  | 1                  | C | Parameter                                                                                                                                                 | Conditions                    | Min | Тур | Max  | Unit |

| t <sub>FIRCSU</sub>    | сс                 | С | Fast internal RC oscillator start-up time                                                                                                                 | V <sub>DD</sub> = 5.0 V ± 10% | —   | 1.1 | 2.0  | μs   |

| $\Delta_{FIRCPRE}$     | сс                 |   | Fast internal RC oscillator precision after software trimming of f <sub>FIRC</sub>                                                                        | T <sub>A</sub> = 25 °C        | -1  | _   | +1   | %    |

|                        | сс                 | т | Fast internal RC oscillator trimming step                                                                                                                 | T <sub>A</sub> = 25 °C        | _   | 1.6 |      | %    |

| $\Delta_{\sf FIRCVAR}$ | сс                 | Ρ | Fast internal RC oscillator variation<br>in over temperature and supply with<br>respect to $f_{FIRC}$ at $T_A = 25$ °C in<br>high-frequency configuration | _                             | -5  |     | +5   | %    |

Table 42. Fast internal RC oscillator (16 MHz) electrical characteristics (continued)

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

# 3.25 Slow internal RC oscillator (128 kHz) electrical characteristics

The device provides a 128 kHz slow internal RC oscillator. This can be used as the reference clock for the RTC module.

| Symbol                           |    | С | Parameter                                                                                                                                            | Conditions <sup>(1)</sup>                                |     |     | Unit |      |

|----------------------------------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----|-----|------|------|

| Symbol                           |    | C | Farameter                                                                                                                                            | Conditions                                               | Min | Тур | Max  | Unit |

| f                                | СС | Ρ | Slow internal RC oscillator low                                                                                                                      | T <sub>A</sub> = 25 °C, trimmed                          | —   | 128 |      | kHz  |

| f <sub>SIRC</sub>                | SR |   | frequency                                                                                                                                            | —                                                        | 100 | —   | 150  | KIIZ |

| I <sub>SIRC</sub> <sup>(2)</sup> | сс | С | Slow internal RC oscillator low<br>frequency current                                                                                                 | T <sub>A</sub> = 25 °C, trimmed                          | —   | _   | 5    | μA   |

| tsircsu                          | сс | Ρ | Slow internal RC oscillator start-up time                                                                                                            | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 5.0 V ±<br>10% | _   | 8   | 12   | μs   |

|                                  | сс | с | Slow internal RC oscillator precision after software trimming of <sup>f</sup> sIRC                                                                   | T <sub>A</sub> = 25 °C                                   | -2  | _   | +2   | %    |

|                                  | сс | С | Slow internal RC oscillator trimming step                                                                                                            | _                                                        | —   | 2.7 | _    |      |

|                                  | сс | С | Slow internal RC oscillator variation<br>in temperature and supply with<br>respect to $f_{SIRC}$ at $T_A = 55$ °C in<br>high frequency configuration | High frequency configuration                             | -10 | _   | +10  | %    |

Table 43. Slow internal RC oscillator (128 kHz) electrical characteristics

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

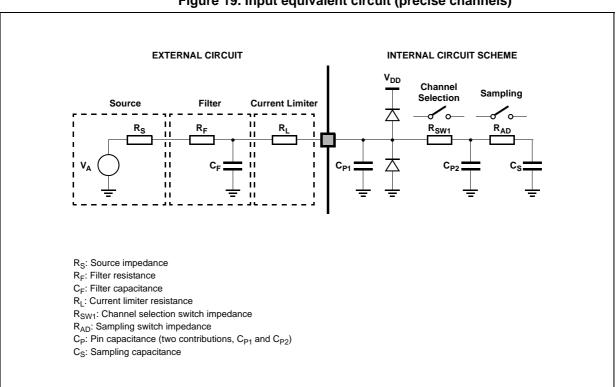

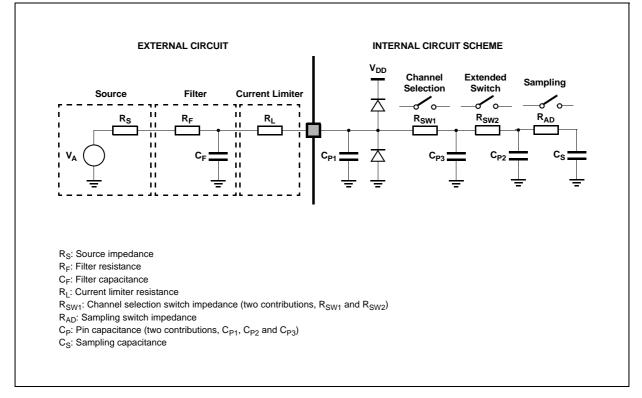

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; furthermore, it sources charge during the sampling phase, when the analog signal source is a high-impedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance: being  $C_S$  and  $C_{p2}$  substantially two switched capacitances, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S+C_{p2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (f_c \times (C_S+C_{p2}))$ ), where  $f_c$  represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S+C_{p2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the *Equation 4*:

#### **Equation 4**

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

*Equation 4* generates a constraint for external network design, in particular on a resistive path.

#### Figure 19. Input equivalent circuit (precise channels)

SPC560B40x/50x, SPC560C40x/50x

DocID14619 Rev 13

During the conversion, the total current consumption is given from the sum of the static and dynamic consumption, i.e., (41 + 5) \* f<sub>periph.</sub>

| ĺ | /06 |

|---|-----|

|   | 116 |

|   | 0,  |

DocID14619 Rev 13

5

| NI - | Cumple of                          |    | ~ | Denemation                                                                                                              |                           | DSPI0/DSPI1             |                    |                          | DSPI2                   |                    |                           |        |   |  |                          |    |   |   |     |   |

|------|------------------------------------|----|---|-------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------|--------------------|--------------------------|-------------------------|--------------------|---------------------------|--------|---|--|--------------------------|----|---|---|-----|---|

| No.  | Symbo                              | DI | С | Parameter                                                                                                               |                           | Min                     | Тур                | Max                      | Min                     | Тур                | Max                       | - Unit |   |  |                          |    |   |   |     |   |

|      |                                    |    | D |                                                                                                                         | Master mode<br>(MTFE = 0) | 125                     | _                  | —                        | 333                     | _                  | _                         |        |   |  |                          |    |   |   |     |   |

| 1    | 1 t <sub>SCK</sub>                 | SR | D | SCK cycle time                                                                                                          | Slave mode<br>(MTFE = 0)  | 125                     | _                  | _                        | 333                     | _                  | _                         | ns     |   |  |                          |    |   |   |     |   |

| I    |                                    |    | D |                                                                                                                         | Master mode<br>(MTFE = 1) | 83                      | _                  | _                        | 125                     | _                  | _                         |        |   |  |                          |    |   |   |     |   |

|      |                                    |    |   |                                                                                                                         | D                         | D                       | D                  | D                        |                         |                    |                           | D      | D |  | Slave mode<br>(MTFE = 1) | 83 | _ | _ | 125 | _ |

| _    | f <sub>DSPI</sub>                  | SR | D | DSPI digital controller freque                                                                                          | ncy                       | —                       | _                  | f <sub>CPU</sub>         | _                       | —                  | f <sub>CPU</sub>          | MHz    |   |  |                          |    |   |   |     |   |

| _    | ∆t <sub>CSC</sub>                  | СС | D | Internal delay between pad<br>associated to SCK and pad<br>associated to CSn in master<br>mode for CSn1 $\rightarrow$ 0 | Master mode               | _                       | _                  | 130 <sup>(2)</sup>       | _                       | _                  | 15 <sup>(3)</sup>         | ns     |   |  |                          |    |   |   |     |   |

|      | ∆t <sub>ASC</sub>                  | СС | D | Internal delay between pad<br>associated to SCK and pad<br>associated to CSn in master<br>mode for CSn1 $\rightarrow$ 1 | Master mode               | _                       | _                  | 130 <sup>(3)</sup>       | _                       | _                  | 130 <sup>(3)</sup>        | ns     |   |  |                          |    |   |   |     |   |

| 2    | t <sub>CSCext</sub> <sup>(4)</sup> | SR | D | CS to SCK delay                                                                                                         | Slave mode                | 32                      | —                  |                          | 32                      | _                  | _                         | ns     |   |  |                          |    |   |   |     |   |

| 3    | t <sub>ASCext</sub> <sup>(5)</sup> | SR | D | After SCK delay                                                                                                         | Slave mode                | 1/f <sub>DSPI</sub> + 5 | —                  | —                        | 1/f <sub>DSPI</sub> + 5 | —                  | _                         | ns     |   |  |                          |    |   |   |     |   |

| 4    | tana                               | CC | D | SCK duty cycle                                                                                                          | Master mode               | —                       | t <sub>SCK/2</sub> | —                        |                         | t <sub>SCK/2</sub> | _                         | ns     |   |  |                          |    |   |   |     |   |

| 4    | t <sub>SDC</sub>                   | SR | D |                                                                                                                         | Slave mode                | t <sub>SCK/2</sub>      | —                  | _                        | t <sub>SCK/2</sub>      | _                  |                           | 115    |   |  |                          |    |   |   |     |   |

| 5    | t <sub>A</sub>                     | SR | D | Slave access time                                                                                                       | Slave mode                |                         | —                  | 1/f <sub>DSPI</sub> + 70 |                         | —                  | 1/f <sub>DSPI</sub> + 130 | ns     |   |  |                          |    |   |   |     |   |

| 6    | t <sub>DI</sub>                    | SR | D | Slave SOUT disable time                                                                                                 | Slave mode                | 7                       | —                  | —                        | 7                       | —                  |                           | ns     |   |  |                          |    |   |   |     |   |

| 7    | t <sub>PCSC</sub>                  | SR |   | PCSx to PCSS time                                                                                                       |                           | 0                       | —                  | —                        | 0                       | —                  | —                         | ns     |   |  |                          |    |   |   |     |   |

| 8    | t <sub>PASC</sub>                  | SR | D | PCSS to PCSx time                                                                                                       |                           | 0                       | -                  | —                        | 0                       |                    | —                         | ns     |   |  |                          |    |   |   |     |   |

Package pinouts and signal descriptions

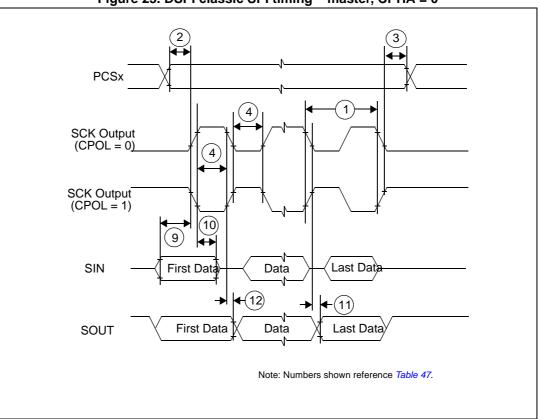

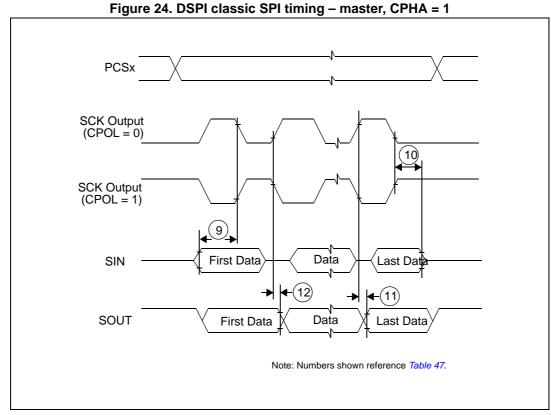

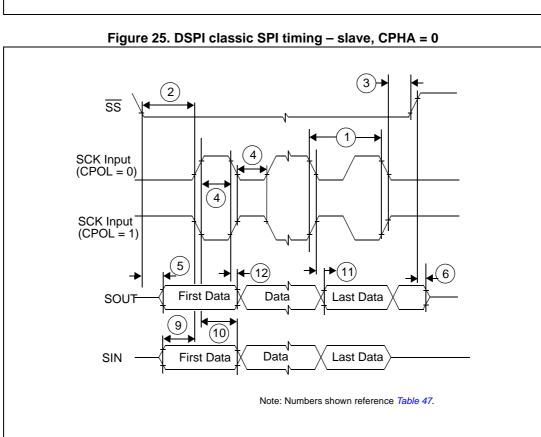

Figure 23. DSPI classic SPI timing – master, CPHA = 0

DocID14619 Rev 13

| Table 55. | Document | revision | history | (continued) | ) |

|-----------|----------|----------|---------|-------------|---|

|           | Document | 10131011 | matory  | Commuca     | , |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01-Oct-2011 | 9        | Formatting and minor editorial changes throughout<br>Harmonized oscillator nomenclature<br>Devices comparison table: removed 384 KB code flash device versions<br>Device comparison table: changed temperature value in footnote 2 from 105 °C to<br>125 °C; removed 384 KB code flash device versions<br>LQFP 64-pin configuration: renamed pin 6 from VPP_TEST to VSS_HV<br>Removed "Pin Muxing" section; added sections "Pad configuration during reset<br>phases", "Voltage supply pins", "Pad types", "System pins," "Functional ports", and<br>"Nexus 2+ pins"<br>Section "NVUSRO register": edited content to separate configuration into electrical<br>parameters and digital functionality: updated footnote describing defaulti value of 1'1<br>in field descriptions NVUSRO[PAD3/SV] and NVUSRO[OSCILLATOR_MARGIN]<br>Added section "NVUSRO[PAD3/SV] and NVUSRO[OSCILLATOR_MARGIN]<br>Added section "NVUSRO[PAD3/SV] and Recommended operating conditions<br>(5.0 V): updated conditions for ambient and junction temperature characteristics<br>Section "I/O pad current specification": removed content referencing the I <sub>DYNSEG</sub><br>maximum value<br>I/O consumption: replaced instances of "Root medium square" with "Root mean<br>square"<br>I/O weight: replaced instances of bit "SRE" with "SRC"; added pads PH[9] and PH[10];<br>added supply segments; removed weight values in 64-pin LQFP for pads that do not<br>exist in that package<br>Reset electrical characteristics: updated parameter classification for  I <sub>WPU</sub>  <br>Updated Voltage regulator electrical characteristics": changed title (was "Voltage<br>monitor electrical characteristics"); added event status flag names found in RGM<br>chapter of device reference manual to POR module and LVD descriptions; replaced<br>instances of "Low voltage monitor" with "LvoLVGBKP" with "LVDLVBKP" in note<br>Updated section "Power consumption"<br>Fast external crystal oscillator (32 kHz) electrical characteristics: updated<br>parameter classification for V <sub>FXOSCOP</sub><br>Crystal oscillator and resonator connection scheme: added footnote about possibility<br>of adding a series resistor<br>Slo |

| 17-Jan-2013 | 10       | Internal review.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17-Jan-2013 | 10       | Internal review.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |