#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                               |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 79                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 48K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 28x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560c50l3b4e0x |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.16 | RESET   | ۲ electrical characteristics 5                                        | 7 |

|------|---------|-----------------------------------------------------------------------|---|

| 3.17 | Power   | management electrical characteristics                                 | 0 |

|      | 3.17.1  | Voltage regulator electrical characteristics                          | 0 |

|      | 3.17.2  | Low voltage detector electrical characteristics                       | 5 |

| 3.18 | Power   | consumption                                                           | 6 |

| 3.19 | Flash r | nemory electrical characteristics6                                    | 8 |

|      | 3.19.1  | Program/Erase characteristics 6                                       | 8 |

|      | 3.19.2  | Flash power supply DC characteristics6                                | 9 |

|      | 3.19.3  | Start-up/Switch-off timings7                                          | 0 |

| 3.20 | Electro | magnetic compatibility (EMC) characteristics                          | 0 |

|      | 3.20.1  | Designing hardened software to avoid noise problems7                  | 0 |

|      | 3.20.2  | Electromagnetic interference (EMI)7                                   | 1 |

|      | 3.20.3  | Absolute maximum ratings (electrical sensitivity)7                    | 1 |

| 3.21 | Fast ex | cternal crystal oscillator (4 to 16 MHz) electrical characteristics 7 | 2 |

| 3.22 | Slow e  | xternal crystal oscillator (32 kHz) electrical characteristics 7      | 5 |

| 3.23 | FMPLL   | electrical characteristics                                            | 7 |

| 3.24 | Fast in | ternal RC oscillator (16 MHz) electrical characteristics              | 8 |

| 3.25 | Slow in | nternal RC oscillator (128 kHz) electrical characteristics            | 9 |

| 3.26 | ADC el  | lectrical characteristics                                             | 0 |

|      | 3.26.1  | Introduction                                                          | 0 |

|      | 3.26.2  | Input impedance and ADC accuracy8                                     | 0 |

|      | 3.26.3  | ADC electrical characteristics                                        | 5 |

| 3.27 | On-chi  | p peripherals                                                         | 7 |

|      | 3.27.1  | Current consumption                                                   | 7 |

|      | 3.27.2  | DSPI characteristics8                                                 | 8 |

|      | 3.27.3  | Nexus characteristics9                                                | 6 |

|      | 3.27.4  | JTAG characteristics9                                                 | 8 |

| Pack | age cha | aracteristics                                                         | 9 |

| 4.1  | ECOP    | ACK®                                                                  | 9 |

| 4.2  | Packag  | ge mechanical data                                                    | 9 |

|      | 4.2.1   |                                                                       |   |

|      | 4.2.2   | LQFP100                                                               | 1 |

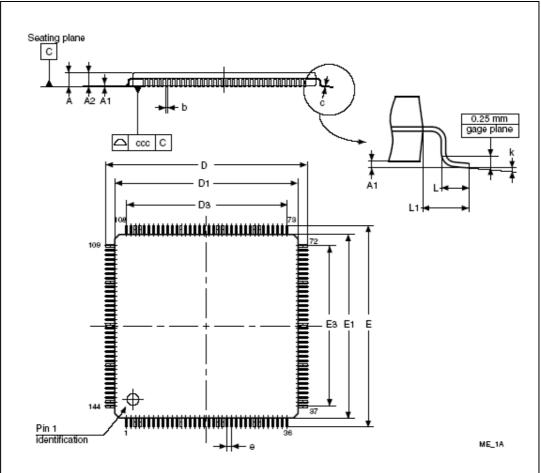

|      | 4.2.3   | LQFP144                                                               | 2 |

|      | 4.2.4   | LBGA208                                                               | 4 |

4

DocID14619 Rev 13

## 1 Introduction

## 1.1 Document overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device. To ensure a complete understanding of the device functionality, refer also to the device reference manual and errata sheet.

## 1.2 Description

The SPC560B40x/50x and SPC560C40x/50x is a family of next generation microcontrollers built on the Power Architecture embedded category.

The SPC560B40x/50x and SPC560C40x/50x family of 32-bit microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding family of automotive-focused products designed to address the next wave of body electronics applications within the vehicle. The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category and only implements the VLE (variable-length encoding) APU, providing improved code density. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

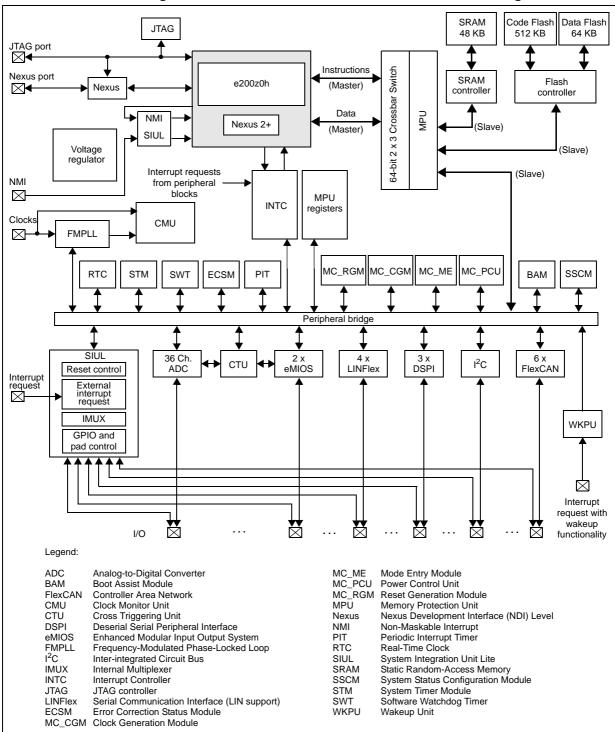

Figure 1. SPC560B40x/50x and SPC560C40x/50x block diagram

*Table 3* summarizes the functions of all blocks present in the SPC560B40x/50x and SPC560C40x/50x series of microcontrollers. Please note that the presence and number of blocks vary by device and package.

| Block                                             | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                 | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                          | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock monitor unit (CMU)                          | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                       | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Deserial serial peripheral interface (DSPI)       | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Error Correction Status Module<br>(ECSM)          | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Enhanced Direct Memory Access<br>(eDMA)           | Performs complex data transfers with minimal intervention from a host processor via "n" programmable channels.                                                                                                                                                                                                    |

| Enhanced modular input output system (eMIOS)      | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Flash memory                                      | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)                 | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Frequency-modulated phase-<br>locked loop (FMPLL) | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Internal multiplexer (IMUX) SIU subblock          | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Inter-integrated circuit (I <sup>2</sup> C™) bus  | A two wire bidirectional serial bus that provides a simple and efficient method of data exchange between devices                                                                                                                                                                                                  |

| Interrupt controller (INTC)                       | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                   | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Clock generation module<br>(MC_CGM)               | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Mode entry module (MC_ME)                         | Provides a mechanism for controlling the device operational mode and mode<br>transition sequences in all functional states; also manages the power control<br>unit, reset generation module and clock generation module, and holds the<br>configuration, control and status registers accessible for applications |

| Power control unit (MC_PCU)                       | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU                                                                           |

| Reset generation module<br>(MC_RGM)               | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                                     |

# 3 Package pinouts and signal descriptions

## 3.1 Package pinouts

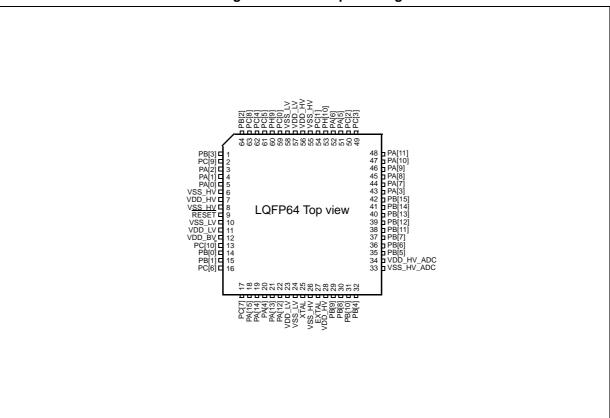

The available LQFP pinouts and the LBGA208 ballmap are provided in the following figures. For pin signal descriptions, please refer to the device reference manual (RM0017).

Figure 2. LQFP 64-pin configuration<sup>(a)</sup>

a. All LQFP64 information is indicative and must be confirmed during silicon validation.

|          |         |                                      |                                    |                                |                              | -        |                        | _      | Pin nu  | umber   |                        |

|----------|---------|--------------------------------------|------------------------------------|--------------------------------|------------------------------|----------|------------------------|--------|---------|---------|------------------------|

| Port pin | PCR     | Alternate<br>function <sup>(1)</sup> | Function                           | Peripheral                     | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration | LQFP64 | LQFP100 | LQFP144 | LBGA208 <sup>(3)</sup> |

| PC[15]   | PCR[47] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[47]<br>E0UC[15]<br>CS0_2<br>— | SIUL<br>eMIOS_0<br>DSPI_2<br>— | I/O<br>I/O<br>I/O<br>—       | М        | Tristate               | _      | 4       | 4       | D3                     |

| PD[0]    | PCR[48] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[48]<br>—<br>—<br>—<br>GPI[4]  | SIUL<br> -<br> <br>ADC         | <br> -<br>                   | I        | Tristate               |        | 41      | 63      | P12                    |

| PD[1]    | PCR[49] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[49]<br>—<br>—<br>—<br>GPI[5]  | SIUL<br>—<br>—<br>ADC          | <br><br><br>                 | I        | Tristate               |        | 42      | 64      | T12                    |

| PD[2]    | PCR[50] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[50]<br>—<br>—<br>—<br>GPI[6]  | SIUL<br>—<br>—<br>ADC          | <br>                         | I        | Tristate               | _      | 43      | 65      | R12                    |

| PD[3]    | PCR[51] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[51]<br>—<br>—<br>—<br>GPI[7]  | SIUL<br>—<br>—<br>ADC          | <br> -<br> <br>              | I        | Tristate               | _      | 44      | 66      | P13                    |

| PD[4]    | PCR[52] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[52]<br>—<br>—<br>—<br>GPI[8]  | SIUL<br><br>ADC                | <br><br>                     | I        | Tristate               | _      | 45      | 67      | R13                    |

| PD[5]    | PCR[53] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[53]<br>—<br>—<br>—<br>GPI[9]  | SIUL<br><br><br>ADC            | <br>                         | I        | Tristate               | _      | 46      | 68      | T13                    |

Table 6. Functional port pin descriptions (continued)

|          |          |                                      |                                                                      |                                                |                              | -        |                        |        | Pin nu  | umber   |                        |

|----------|----------|--------------------------------------|----------------------------------------------------------------------|------------------------------------------------|------------------------------|----------|------------------------|--------|---------|---------|------------------------|

| Port pin | PCR      | Alternate<br>function <sup>(1)</sup> | Function                                                             | Peripheral                                     | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration | LQFP64 | LQFP100 | LQFP144 | LBGA208 <sup>(3)</sup> |

| PG[0]    | PCR[96]  | AF0<br>AF1<br>AF2<br>AF3             | GPIO[96]<br>CAN5TX <sup>(11)</sup><br>E1UC[23]<br>—                  | SIUL<br>FlexCAN_5<br>eMIOS_1<br>—              | I/O<br>O<br>I/O<br>—         | М        | Tristate               |        |         | 98      | E14                    |

| PG[1]    | PCR[97]  | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[97]<br>—<br>E1UC[24]<br>—<br>CAN5RX <sup>(11)</sup><br>EIRQ[14] | SIUL<br>—<br>eMIOS_1<br>—<br>FlexCAN_5<br>SIUL | I/O<br>I/O<br>I<br>I         | S        | Tristate               | _      | _       | 97      | E13                    |

| PG[2]    | PCR[98]  | AF0<br>AF1<br>AF2<br>AF3             | GPIO[98]<br>E1UC[11]<br>—                                            | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>               | М        | Tristate               |        | _       | 8       | E4                     |

| PG[3]    | PCR[99]  | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[99]<br>E1UC[12]<br>—<br>—<br>WKPU[17] <sup>(4)</sup>            | SIUL<br>eMIOS_1<br>—<br>WKPU                   | I/O<br>I/O<br> <br>          | S        | Tristate               | _      | _       | 7       | E3                     |

| PG[4]    | PCR[100] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[100]<br>E1UC[13]<br>—                                           | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>               | М        | Tristate               | _      | _       | 6       | E1                     |

| PG[5]    | PCR[101] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[101]<br>E1UC[14]<br>—<br>WKPU[18] <sup>(4)</sup>                | SIUL<br>eMIOS_1<br>—<br>WKPU                   | I/O<br>I/O<br>—<br>I         | S        | Tristate               | _      |         | 5       | E2                     |

| PG[6]    | PCR[102] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[102]<br>E1UC[15]<br>—                                           | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>               | М        | Tristate               |        | _       | 30      | M2                     |

| Table 6. Functional port pin descriptions (continued) |

|-------------------------------------------------------|

|-------------------------------------------------------|

|          |          |                                      |                                                |                                        |                              | -        |                        |        | Pin nu  | umber   |                        |

|----------|----------|--------------------------------------|------------------------------------------------|----------------------------------------|------------------------------|----------|------------------------|--------|---------|---------|------------------------|

| Port pin | PCR      | Alternate<br>function <sup>(1)</sup> | Function                                       | Peripheral                             | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration | LQFP64 | LQFP100 | LQFP144 | LBGA208 <sup>(3)</sup> |

| PG[7]    | PCR[103] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[103]<br>E1UC[16]<br>—                     | SIUL<br>eMIOS_1<br>—                   | I/O<br>I/O<br>—              | М        | Tristate               | _      | _       | 29      | M1                     |

| PG[8]    | PCR[104] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[104]<br>E1UC[17]<br><br>CS0_2<br>EIRQ[15] | SIUL<br>eMIOS_1<br>—<br>DSPI_2<br>SIUL | I/O<br>I/O<br>I/O<br>I       | S        | Tristate               | _      | _       | 26      | L2                     |

| PG[9]    | PCR[105] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[105]<br>E1UC[18]<br>—<br>SCK_2            | SIUL<br>eMIOS_1<br>—<br>DSPI_2         | I/O<br>I/O<br><br>I/O        | S        | Tristate               | _      | _       | 25      | L1                     |

| PG[10]   | PCR[106] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[106]<br>E0UC[24]<br>—                     | SIUL<br>eMIOS_0<br>—                   | I/O<br>I/O<br>               | S        | Tristate               | _      | _       | 114     | D13                    |

| PG[11]   | PCR[107] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[107]<br>E0UC[25]<br>—                     | SIUL<br>eMIOS_0<br>—                   | I/O<br>I/O<br>               | М        | Tristate               | _      | _       | 115     | B12                    |

| PG[12]   | PCR[108] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[108]<br>E0UC[26]<br>—<br>—                | SIUL<br>eMIOS_0<br>—<br>—              | I/O<br>I/O<br>               | М        | Tristate               | _      | _       | 92      | K14                    |

| PG[13]   | PCR[109] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[109]<br>E0UC[27]<br>—                     | SIUL<br>eMIOS_0<br>—<br>—              | I/O<br>I/O<br>—              | М        | Tristate               |        | —       | 91      | K16                    |

| PG[14]   | PCR[110] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[110]<br>E1UC[0]<br>—                      | SIUL<br>eMIOS_1<br>—                   | I/O<br>I/O<br>               | S        | Tristate               | _      | _       | 110     | B14                    |

Table 6. Functional port pin descriptions (continued)

|                           |          |                                      |                                         |                                  |                              |          |                        |        | Pin nı  | umber   |                        |

|---------------------------|----------|--------------------------------------|-----------------------------------------|----------------------------------|------------------------------|----------|------------------------|--------|---------|---------|------------------------|

| Port pin                  | PCR      | Alternate<br>function <sup>(1)</sup> | Function                                | Peripheral                       | I/O direction <sup>(2)</sup> | Pad type | RESET<br>configuration | LQFP64 | LQFP100 | LQFP144 | LBGA208 <sup>(3)</sup> |

| PH[7]                     | PCR[119] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[119]<br>E1UC[9]<br>CS3_2<br>MA[1]  | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC | I/O<br>I/O<br>O              | М        | Tristate               | _      | _       | 137     | C5                     |

| PH[8]                     | PCR[120] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[120]<br>E1UC[10]<br>CS2_2<br>MA[0] | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC | I/O<br>I/O<br>O<br>O         | М        | Tristate               | _      | _       | 138     | A5                     |

| PH[9] <sup>(9)</sup>      | PCR[121] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[121]<br>—<br>TCK<br>—              | SIUL<br>—<br>JTAGC<br>—          | I/O<br>—<br>I<br>—           | S        | Input, weak<br>pull-up | 60     | 88      | 127     | B8                     |

| PH[10] <sup>(</sup><br>9) | PCR[122] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[122]<br>—<br>TMS<br>—              | SIUL<br>—<br>JTAGC<br>—          | I/O<br>—<br>I<br>—           | S        | Input, weak<br>pull-up | 53     | 81      | 120     | В9                     |

Table 6. Functional port pin descriptions (continued)

Alternate functions are chosen by setting the values of the PCR.PA bitfields inside the SIUL module. PCR.PA = 00 → AF0; PCR.PA = 01 → AF1; PCR.PA = 10 → AF2; PCR.PA = 11 → AF3. This is intended to select the output functions; to use one of the input functions, the PCR.IBE bit must be written to '1', regardless of the values selected in the PCR.PA bitfields. For this reason, the value corresponding to an input only function is reported as "—".

2. Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMIO.PADSELx bitfields inside the SIUL module.

3. LBGA208 available only as development package for Nexus2+

4. All WKPU pins also support external interrupt capability. See wakeup unit chapter for further details.

5. NMI has higher priority than alternate function. When NMI is selected, the PCR.AF field is ignored.

- 6. "Not applicable" because these functions are available only while the device is booting. Refer to BAM chapter of the reference manual for details.

- 7. Value of PCR.IBE bit must be 0

- Be aware that this pad is used on the SPC560B64L3 and SPC560B64L5 to provide VDD\_HV\_ADC and VSS\_HV\_ADC1. Therefore, you should be careful in ensuring compatibility between SPC560B40x/50x and SPC560C40x/50x and SPC560B64.

- Out of reset all the functional pins except PC[0:1] and PH[9:10] are available to the user as GPIO. PC[0:1] are available as JTAG pins (TDI and TDO respectively). PH[9:10] are available as JTAG pins (TCK and TMS respectively). If the user configures these JTAG pins in GPIO mode the device is no longer compliant with IEEE 1149.1-2001.

- 10. The TDO pad has been moved into the STANDBY domain in order to allow low-power debug handshaking in STANDBY mode. However, no pull-resistor is active on the TDO pad while in STANDBY mode. At this time the pad is configured as an input. When no debugger is connected the TDO pad is floating causing additional current consumption. To avoid the extra consumption TDO must be connected. An external pull-up resistor in the range of 47–100 kΩ should be added between the TDO pin and VDD\_HV. Only in case the TDO pin is used as application pin and a pull-up cannot be used then a pull-down resistor with the same value should be used between TDO pin and GND instead.

| Symbo                |    | Doromotor                                                                | Conditions                                    | v    | linit                |      |

|----------------------|----|--------------------------------------------------------------------------|-----------------------------------------------|------|----------------------|------|

| Symbo                | 1  | Parameter Conditions                                                     |                                               | Min  | Max                  | Unit |

| V                    | SR | Voltage on any GPIO pin with respect to                                  | —                                             | -0.3 | 6.0                  | V    |

| V <sub>IN</sub>      | 31 |                                                                          | Relative to V <sub>DD</sub>                   | —    | V <sub>DD</sub> +0.3 | v    |

| I <sub>INJPAD</sub>  | SR | Injected input current on any pin during overload condition              | _                                             | -10  | 10                   | mA   |

| I <sub>INJSUM</sub>  | SR | Absolute sum of all injected input<br>currents during overload condition | —                                             | -50  | 50                   |      |

| 1                    | SR | Sum of all the static I/O current within a                               | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _    | 70                   | mA   |

| IAVGSEG              | SK | supply segment                                                           | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _    | 64                   |      |

| I <sub>CORELV</sub>  | SR | Low voltage static current sink through VDD_BV                           | _                                             | _    | 150                  | mA   |

| T <sub>STORAGE</sub> | SR | Storage temperature                                                      | —                                             | -55  | 150                  | °C   |

Table 12. Absolute maximum ratings (continued)

Note: Stresses exceeding the recommended absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ), the voltage on pins with respect to ground ( $V_{SS}$ ) must not exceed the recommended values.

## 3.13 Recommended operating conditions

| Symbol                             |    | Parameter                                                                                     | Conditions                  | Va                   | lue                  | Unit |

|------------------------------------|----|-----------------------------------------------------------------------------------------------|-----------------------------|----------------------|----------------------|------|

| Symbol                             |    | Falameter                                                                                     | Conditions                  | Min                  | Max                  | Unit |

| V <sub>SS</sub>                    | SR | Digital ground on VSS_HV pins                                                                 | —                           | 0                    | 0                    | V    |

| V <sub>DD</sub> <sup>(1)</sup>     | SR | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                              | _                           | 3.0                  | 3.6                  | V    |

| V <sub>SS_LV</sub> <sup>(2)</sup>  | SR | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | _                           | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD BV</sub> <sup>(3)</sup>  | SR | Voltage on VDD_BV pin (regulator supply) with                                                 | _                           | 3.0                  | 3.6                  | v    |

| VDD_BV                             | SK | respect to ground (V <sub>SS</sub> )                                                          | Relative to $V_{\text{DD}}$ | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 | v    |

| V <sub>SS_ADC</sub>                | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> )           | _                           | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_ADC</sub> <sup>(4)</sup> | SR | Voltage on VDD_HV_ADC pin (ADC reference)                                                     | —                           | 3.0 <sup>(5)</sup>   | 3.6                  | v    |

| ▼DD_ADC`´                          | JK | with respect to ground $(V_{SS})$                                                             | Relative to $V_{DD}$        | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 | v    |

Table 13. Recommended operating conditions (3.3 V)

| Symbol              |    | Parameter                                                                | Conditions                  | Va                   | Unit                                      |      |

|---------------------|----|--------------------------------------------------------------------------|-----------------------------|----------------------|-------------------------------------------|------|

| Symbol              |    | Farameter                                                                | Conditions                  | Min                  | Max                                       | Unit |

| V S                 |    | Voltage on any GPIO pin with respect to ground                           | —                           | V <sub>SS</sub> -0.1 | —                                         | v    |

| V <sub>IN</sub>     | SR | (V <sub>SS</sub> )                                                       | Relative to $V_{\text{DD}}$ |                      | V <sub>DD</sub> +0.1                      | v    |

| I <sub>INJPAD</sub> | SR | Injected input current on any pin during overload condition              | _                           | -5                   | 5                                         | mA   |

| I <sub>INJSUM</sub> | SR | Absolute sum of all injected input currents<br>during overload condition | _                           | -50                  | 50                                        | IIIA |

| TV <sub>DD</sub>    | SR | V <sub>DD</sub> slope to ensure correct power up <sup>(6)</sup>          | _                           | 3.0 <sup>(7)</sup>   | 250 x 10 <sup>3</sup><br>(0.25<br>[V/µs]) | V/s  |

#### Table 13. Recommended operating conditions (3.3 V) (continued)

1. 100 nF capacitance needs to be provided between each  $V_{\text{DD}}/V_{\text{SS}}$  pair

2. 330 nF capacitance needs to be provided between each  $V_{DD_LLV}/V_{SS_LV}$  supply pair.

3. 400 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics).

4. 100 nF capacitance needs to be provided between  $V_{\text{DD}\_\text{ADC}}/V_{\text{SS}\_\text{ADC}}$  pair.

Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

6. Guaranteed by device validation.

7. Minimum value of TV<sub>DD</sub> must be guaranteed until V<sub>DD</sub> reaches 2.6 V (maximum value of V<sub>PORH</sub>).

| Symbol                             |    | Parameter                                                                                     | Conditions                  | Va                   | lue                  | Unit |  |

|------------------------------------|----|-----------------------------------------------------------------------------------------------|-----------------------------|----------------------|----------------------|------|--|

| Symbol                             |    | Farameter                                                                                     | Conditions                  | Min                  | Max                  | Unit |  |

| V <sub>SS</sub>                    | SR | Digital ground on VSS_HV pins                                                                 | —                           | 0                    | 0                    | V    |  |

| V <sub>DD</sub> <sup>(1)</sup>     | SR | Voltage on VDD_HV pins with respect to                                                        | —                           | 4.5                  | 5.5                  | v    |  |

| V DD` ´                            | JK | ground (V <sub>SS</sub> )                                                                     | Voltage drop <sup>(2)</sup> | 3.0                  | 5.5                  | v    |  |

| V <sub>SS_LV</sub> <sup>(3)</sup>  | SR | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | _                           | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |  |

|                                    |    | with respect to ground (v <sub>SS</sub> )                                                     | —                           | 4.5                  | 5.5                  |      |  |

| V <sub>DD_BV</sub> <sup>(4)</sup>  | SR |                                                                                               | Voltage drop <sup>(2)</sup> | 3.0                  | 5.5                  | V    |  |

|                                    |    |                                                                                               | Relative to V <sub>DD</sub> | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |  |

| V <sub>SS_ADC</sub>                | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub>             | _                           | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |  |

|                                    |    |                                                                                               | —                           | 4.5                  | 5.5                  |      |  |

| V <sub>DD_ADC</sub> <sup>(5)</sup> | SR | Voltage on VDD_HV_ADC pin (ADC reference) with respect to ground (V <sub>SS</sub> )           | Voltage drop <sup>(2)</sup> | 3.0                  | 5.5                  | V    |  |

|                                    |    |                                                                                               | Relative to V <sub>DD</sub> | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |  |

| V                                  | SR | Voltage on any GPIO pin with respect to                                                       | —                           | V <sub>SS</sub> -0.1 | —                    | V    |  |

| V <sub>IN</sub>                    | JR | ground (V <sub>SS</sub> )                                                                     | Relative to V <sub>DD</sub> | —                    | V <sub>DD</sub> +0.1 |      |  |

#### Table 14. Recommended operating conditions (5.0 V)

#### 3.15.3 I/O output DC characteristics

The following tables provide DC characteristics for bidirectional pads:

- Table 17 provides weak pull figures. Both pull-up and pull-down resistances are supported.

- *Table 18* provides output driver characteristics for I/O pads when in SLOW configuration.

- *Table 19* provides output driver characteristics for I/O pads when in MEDIUM configuration.

- Table 20 provides output driver characteristics for I/O pads when in FAST configuration.

| Symbol           |                         | с                                     | Parameter                                              | Conditions <sup>(1)</sup>                                         |                            | Unit |     |     |      |

|------------------|-------------------------|---------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------|----------------------------|------|-----|-----|------|

| Synib            | Symbol                  |                                       | Farameter                                              | Conditions                                                        |                            | Min  | Тур | Max | Unit |

|                  | P                       |                                       |                                                        |                                                                   | PAD3V5V = 0                | 10   | _   | 150 |      |

| I <sub>WPU</sub> | I <sub>WPU</sub> C<br>C | С                                     | Weak pull-up current<br>absolute value                 | $V_{IN} = V_{IL}, V_{DD} = 5.0 V \pm 10\%$                        | PAD3V5V = 1 <sup>(2)</sup> | 10   | _   | 250 | μA   |

|                  |                         | Ρ                                     |                                                        | $V_{IN} = V_{IL}, V_{DD} = 3.3 \text{ V} \pm 10\%$                | PAD3V5V = 1                | 10   | —   | 150 |      |

|                  | _                       | Ρ                                     |                                                        | V <sub>IN</sub> = V <sub>IH</sub> , V <sub>DD</sub> = 5.0 V ± 10% | PAD3V5V = 0                | 10   | —   | 150 |      |

|                  | С                       | Weak pull-down current absolute value | $v_{\rm IN} = v_{\rm IH}, v_{\rm DD} = 5.0 v \pm 10.0$ | PAD3V5V = 1                                                       | 10                         | —    | 250 | μA  |      |

|                  |                         | Ρ                                     |                                                        | $V_{IN} = V_{IH}, V_{DD} = 3.3 \text{ V} \pm 10\%$                | PAD3V5V = 1                | 10   | _   | 150 |      |

#### Table 17. I/O pull-up/pull-down DC electrical characteristics

1. V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified.

The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

#### Table 18. SLOW configuration output buffer electrical characteristics

| Sum             | Symbol C Parameter |   | Paramotor                            |            | Conditions <sup>(1)</sup>                                                                            |                      | Unit |       |   |

|-----------------|--------------------|---|--------------------------------------|------------|------------------------------------------------------------------------------------------------------|----------------------|------|-------|---|

| Sym             |                    |   |                                      | Conditions |                                                                                                      | Тур                  | Max  | U.III |   |

|                 |                    | Ρ |                                      |            | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended) | 0.8V <sub>DD</sub>   | _    | _     |   |

| V <sub>OH</sub> | сс                 | С | Output high level SLOW configuration | Push Pull  | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^{(2)}$            | 0.8V <sub>DD</sub>   |      | _     | v |

|                 |                    | С |                                      |            | $I_{OH} = -1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$<br>(recommended) | V <sub>DD</sub> -0.8 |      |       |   |

| <b>S</b> 14     | mhal | ~ | Deremeter                                             |                            | Conditions <sup>(1)</sup>                              |                            | Value | )   | Unit |    |    |

|-----------------|------|---|-------------------------------------------------------|----------------------------|--------------------------------------------------------|----------------------------|-------|-----|------|----|----|

| Зу              | mbol | C | Parameter                                             |                            | Conditions                                             | Min                        | Тур   | Max | Unit |    |    |

|                 |      | D |                                                       | C <sub>L</sub> = 25 pF     |                                                        | —                          | —     | 10  |      |    |    |

|                 |      | Т |                                                       | C <sub>L</sub> = 50 pF     |                                                        | —                          | —     | 20  |      |    |    |

|                 |      | D | Output transition time output 1<br>pin <sup>(2)</sup> | C <sub>L</sub> =<br>100 pF | SIUL.PCRx.SRC = 1                                      | _                          | _     | 40  |      |    |    |

| ۲tr             |      | D |                                                       | C <sub>L</sub> = 25 pF     |                                                        | —                          | —     | 12  | ns   |    |    |

|                 |      | Т |                                                       | C <sub>L</sub> = 50 pF     |                                                        | _                          | —     | 25  |      |    |    |

|                 |      | D |                                                       | C <sub>L</sub> =<br>100 pF | SIUL.PCRx.SRC = 1                                      | _                          | _     | 40  |      |    |    |

|                 |      |   |                                                       | C <sub>L</sub> = 25 pF     | -                                                      | —                          | —     | 4   |      |    |    |

|                 |      |   |                                                       | C <sub>L</sub> = 50 pF     |                                                        | _                          | —     | 6   |      |    |    |

| +               | сс   |   |                                                       |                            | Output transition time output pin <sup>(2)</sup>       | C <sub>L</sub> =<br>100 pF |       | _   | _    | 12 | 20 |

| t <sub>tr</sub> |      |   | FAST configuration                                    | C <sub>L</sub> = 25 pF     |                                                        | —                          | —     | 4   | ns   |    |    |

|                 |      |   |                                                       | C <sub>L</sub> = 50 pF     | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1             | _                          | —     | 7   |      |    |    |

|                 |      |   |                                                       | C <sub>L</sub> =<br>100 pF | $1000 - 0.5 \text{ v} \pm 10\%, 1 \text{ AD} 3000 = 1$ |                            | _     | 12  |      |    |    |

| Table 21. | Output     | pin transition | times ( | (continued) |

|-----------|------------|----------------|---------|-------------|

|           | e aip ai j |                |         |             |

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified

2. C<sub>L</sub> includes device and package capacitances (C<sub>PKG</sub> < 5 pF).

## 3.15.5 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in *Table 22*.

| Package                | Supply segment |                |               |               |           |   |  |  |  |  |

|------------------------|----------------|----------------|---------------|---------------|-----------|---|--|--|--|--|

|                        | 1              | 2              | 3             | 4             | 5         | 6 |  |  |  |  |

| LBGA208 <sup>(1)</sup> | Equival        | ent to LQFP144 | tribution     | МСКО          | MDOn/MSEO |   |  |  |  |  |

| LQFP144                | pin20–pin49    | pin51–pin99    | pin100-pin122 | pin 123–pin19 | —         | — |  |  |  |  |

| LQFP100                | pin16–pin35    | pin37–pin69    | pin70–pin83   | pin 84–pin15  | —         | — |  |  |  |  |

| LQFP64 <sup>(2)</sup>  | pin8–pin26     | pin28–pin55    | pin56–pin7    | —             | _         | — |  |  |  |  |

Table 22. I/O supply segment

1. LBGA208 available only as development package for Nexus2+

2. All LQFP64 information is indicative and must be confirmed during silicon validation.

Table 23 provides I/O consumption figures.

In order to ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{\rm AVGSEG}$  maximum value.

| Symbol              |    | с | Parameter                                                                       | Conditions <sup>(1)</sup>                             |     |     | Unit       |      |  |

|---------------------|----|---|---------------------------------------------------------------------------------|-------------------------------------------------------|-----|-----|------------|------|--|

| Symbol              |    | J | Faiameter                                                                       | Conditions                                            | Min | Тур | Max        | onic |  |

| I <sub>ULPREG</sub> | SR |   | Ultra low power regulator current provided to V <sub>DD_LV</sub> domain         | _                                                     | _   |     | 5          | mA   |  |

|                     | сс |   | Ultra low power regulator module                                                | I <sub>ULPREG</sub> = 5 mA;<br>T <sub>A</sub> = 55 °C |     | _   | 100        |      |  |

| IULPREGINT          |    | D |                                                                                 | I <sub>ULPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C |     | 2   | _          | μA   |  |

| I <sub>DD_BV</sub>  | сс | D | In-rush average current on<br>V <sub>DD_BV</sub> during power-up <sup>(5)</sup> | _                                                     | _   | _   | 300<br>(6) | mA   |  |

| Table 26. Voltage regulator electrical characteristic | s (continued) |

|-------------------------------------------------------|---------------|

|-------------------------------------------------------|---------------|

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified

This capacitance value is driven by the constraints of the external voltage regulator supplying the V<sub>DD\_BV</sub> voltage. A typical value is in the range of 470 nF.

3. This value is acceptable to guarantee operation from 4.5 V to 5.5 V  $\,$

4. External regulator and capacitance circuitry must be capable of providing  $I_{DD_BV}$  while maintaining supply  $V_{DD_BV}$  in operating range.

5. In-rush average current is seen only for short time (maximum 20  $\mu$ s) during power-up and on standby exit. It is dependent on the sum of the C<sub>REGn</sub> capacitances.

The duration of the in-rush current depends on the capacitance placed on LV pins. BV decoupling capacitors must be sized accordingly. Refer to I<sub>MREG</sub> value for minimum amount of current to be provided in cc.

The  $|\Delta_{VDD(STDBY)}|$  and dVDD(STDBY)/dt system requirement can be used to define the component used for the V<sub>DD</sub> supply generation. The following two examples describe how to calculate capacitance size:

#### Example 1 No regulator (worst case)

The  $|\Delta_{VDD(STDBY)}|$  parameter can be seen as the  $V_{DD}$  voltage drop through the ESR resistance of the regulator stability capacitor when the  $I_{DD_BV}$  current required to load  $V_{DD_LV}$  domain during the standby exit. It is thus possible to define the maximum equivalent resistance ESR<sub>STDBY</sub>(MAX) of the total capacitance on the  $V_{DD}$  supply:

$ESR_{STDBY}(MAX) = |\Delta_{VDD(STDBY)}|/I_{DD BV} = (30 \text{ mV})/(300 \text{ mA}) = 0.1\Omega^{(d)}$

The dVDD(STDBY)/dt parameter can be seen as the V<sub>DD</sub> voltage drop at the capacitance pin (excluding ESR drop) while providing the  $I_{DD_BV}$  supply required to load  $V_{DD_LV}$  domain during the standby exit. It is thus possible to define the minimum equivalent capacitance  $C_{STDBY}$ (MIN) of the total capacitance on the V<sub>DD</sub> supply:

$C_{STDBY}(MIN) = I_{DD BV}/dVDD(STDBY)/dt = (300 mA)/(15 mV/\mu s) = 20 \mu F$

This configuration is a worst case, with the assumption no regulator is available.

#### Example 2 Simplified regulator

The regulator should be able to provide significant amount of the current during the standby exit process. For example, in case of an ideal voltage regulator providing 200 mA current, it is possible to recalculate the equivalent ESR<sub>STDBY</sub>(MAX) and C<sub>STDBY</sub>(MIN) as follows:

d. Based on typical time for standby exit sequence of 20 µs, ESR(MIN) can actually be considered at ~50 kHz.

## 3.19.3 Start-up/Switch-off timings

| Symbol                     |          | с                                         | Parameter                                 | Conditions <sup>(1)</sup> |     |     | Unit |      |   |                                           |            |   |  |     |  |

|----------------------------|----------|-------------------------------------------|-------------------------------------------|---------------------------|-----|-----|------|------|---|-------------------------------------------|------------|---|--|-----|--|

| Symbol                     |          | C                                         | Parameter                                 | Conditions ?              | Min | Тур | Max  | onne |   |                                           |            |   |  |     |  |

| т                          | сс       | Т                                         |                                           | Code Flash                | _   | —   | 125  |      |   |                                           |            |   |  |     |  |

| T <sub>FLARSTEXIT</sub> CC | Т        | Delay for Flash module to exit reset mode | Data Flash                                | —                         | —   | 125 |      |      |   |                                           |            |   |  |     |  |

| т                          | сс       | Т                                         | Delay for Flash module to exit low-power  | Code Flash                | —   | —   | 0.5  |      |   |                                           |            |   |  |     |  |

| T <sub>FLALPEXIT</sub>     |          | Т                                         | mode                                      | Data Flash                | —   | _   | 0.5  |      |   |                                           |            |   |  |     |  |

| -                          | ~~       | Т                                         | Delay for Flash module to exit power-down | Code Flash                | _   | _   | 30   |      |   |                                           |            |   |  |     |  |

| T <sub>FLAPDEXIT</sub>     | СС       |                                           | mode                                      | Data Flash                | _   | _   | 30   | μs   |   |                                           |            |   |  |     |  |

| -                          | <u> </u> | <u> </u>                                  | ~~                                        | сс                        | Т   | T   | Т    | Т    | Т | Delay for Flash module to enter low-power | Code Flash | _ |  | 0.5 |  |

| T <sub>FLALPENTRY</sub> (  |          |                                           | in a da                                   | Data Flash                | _   | _   | 0.5  | 1    |   |                                           |            |   |  |     |  |

| -                          | ~~       |                                           | Delay for Flash module to enter power-    | Code Flash                | —   |     | 1.5  | 1    |   |                                           |            |   |  |     |  |

| T <sub>FLAPDENTRY</sub>    |          |                                           | down mode                                 | Data Flash                | —   | —   | 1.5  |      |   |                                           |            |   |  |     |  |

| Table 33. | Start-up | time/Switch-off | time |

|-----------|----------|-----------------|------|

|           | otart ap |                 |      |

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified

## 3.20 Electromagnetic compatibility (EMC) characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### 3.20.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user apply EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

- Software recommendations: The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

- Prequalification trials: Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the reset pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note *Software Techniques For Improving Microcontroller EMC Performance* (AN1015)).

| Symbol                 |    | с | Parameter                                                                                                                                                 | Conditions <sup>(1)</sup>     |     |     | Unit |      |

|------------------------|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|------|------|

| Symbo                  | 1  | C | Parameter                                                                                                                                                 | Conditions                    | Min | Тур | Max  | Unit |

| t <sub>FIRCSU</sub>    | сс | С | Fast internal RC oscillator start-up time                                                                                                                 | V <sub>DD</sub> = 5.0 V ± 10% | —   | 1.1 | 2.0  | μs   |

| $\Delta_{FIRCPRE}$     | сс |   | Fast internal RC oscillator precision after software trimming of f <sub>FIRC</sub>                                                                        | T <sub>A</sub> = 25 °C        | -1  | _   | +1   | %    |

|                        | сс | т | Fast internal RC oscillator trimming step                                                                                                                 | T <sub>A</sub> = 25 °C        | _   | 1.6 |      | %    |

| $\Delta_{\sf FIRCVAR}$ | сс | Ρ | Fast internal RC oscillator variation<br>in over temperature and supply with<br>respect to $f_{FIRC}$ at $T_A = 25$ °C in<br>high-frequency configuration | _                             | -5  |     | +5   | %    |

Table 42. Fast internal RC oscillator (16 MHz) electrical characteristics (continued)

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

# 3.25 Slow internal RC oscillator (128 kHz) electrical characteristics

The device provides a 128 kHz slow internal RC oscillator. This can be used as the reference clock for the RTC module.

| Symbol                           |    | С | Parameter                                                                                                                                            | Conditions <sup>(1)</sup>                                |     |     | Unit |       |

|----------------------------------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----|-----|------|-------|

| Symbol                           |    | C | Farameter                                                                                                                                            | Conditions                                               | Min | Тур | Max  | Unit  |

| f                                | СС | Ρ | Slow internal RC oscillator low                                                                                                                      | T <sub>A</sub> = 25 °C, trimmed                          | —   | 128 |      | kHz   |

| f <sub>SIRC</sub> SF             | SR |   | frequency                                                                                                                                            |                                                          | 100 | —   | 150  | KI IZ |

| I <sub>SIRC</sub> <sup>(2)</sup> | сс | С | Slow internal RC oscillator low<br>frequency current                                                                                                 | T <sub>A</sub> = 25 °C, trimmed                          | —   | _   | 5    | μA    |

| tsircsu                          | сс | Ρ | Slow internal RC oscillator start-up time                                                                                                            | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 5.0 V ±<br>10% | _   | 8   | 12   | μs    |

|                                  | сс | с | Slow internal RC oscillator precision after software trimming of <sup>f</sup> sIRC                                                                   | T <sub>A</sub> = 25 °C                                   | -2  | _   | +2   | %     |

|                                  | сс | С | Slow internal RC oscillator trimming step                                                                                                            | _                                                        | —   | 2.7 | _    |       |

|                                  | сс | С | Slow internal RC oscillator variation<br>in temperature and supply with<br>respect to $f_{SIRC}$ at $T_A = 55$ °C in<br>high frequency configuration | High frequency configuration                             | -10 | _   | +10  | %     |

Table 43. Slow internal RC oscillator (128 kHz) electrical characteristics

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

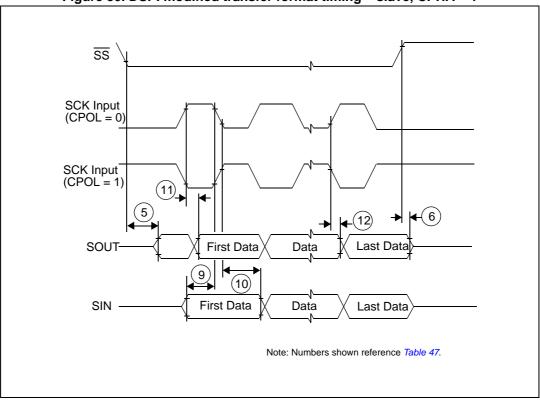

Figure 30. DSPI modified transfer format timing – slave, CPHA = 1

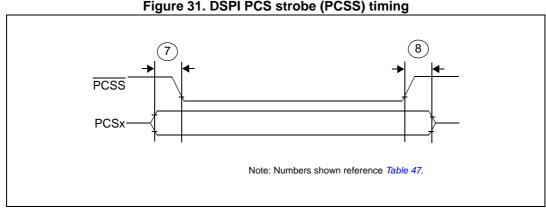

### Figure 31. DSPI PCS strobe (PCSS) timing

#### 3.27.3 **Nexus characteristics**

| Table 48. Nexus cha | aracteristics |

|---------------------|---------------|

|---------------------|---------------|

| No. | Symbo             | al | с | Parameter                  |     | Unit |     |      |

|-----|-------------------|----|---|----------------------------|-----|------|-----|------|

| NO. | Symbo             | 0  | C | Falameter                  | Min | Тур  | Max | onit |

| 1   | t <sub>TCYC</sub> | CC | D | TCK cycle time             | 64  | —    | —   | ns   |

| 2   | t <sub>MCYC</sub> | СС | D | MCKO cycle time            | 32  | —    | —   | ns   |

| 3   | t <sub>MDOV</sub> | CC | D | MCKO low to MDO data valid | —   | —    | 8   | ns   |

DocID14619 Rev 13

| Table 31. Ewi 1 100 mechanical data (continued) |        |        |        |                       |        |        |

|-------------------------------------------------|--------|--------|--------|-----------------------|--------|--------|

| Occurs have b                                   |        | mm     |        | inches <sup>(1)</sup> |        |        |

| Symbol                                          | Min    | Тур    | Мах    | Min                   | Тур    | Max    |

| E1                                              | 13.800 | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| E3                                              | —      | 12.000 | _      | _                     | 0.4724 | —      |

| е                                               | —      | 0.500  | _      | _                     | 0.0197 | —      |

| L                                               | 0.450  | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1                                              | —      | 1.000  | _      | _                     | 0.0394 | —      |

| k                                               | 0.0 °  | 3.5 °  | 7.0 °  | 0.0 °                 | 3.5 °  | 7.0 °  |

| Tolerance                                       | mm     |        |        | inches                |        |        |

| CCC                                             |        | 0.080  |        |                       | 0.0031 |        |

Table 51. LQFP100 mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## 4.2.3 LQFP144

Figure 36. LQFP144 package mechanical drawing

DocID14619 Rev 13

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Jan-2010 | 5        | Table: "Absolute maximum ratings"<br>- V <sub>DD_BV</sub> , V <sub>DD_ADC</sub> , V <sub>IN</sub> : changed max value<br>Table: "Recommended operating conditions (3.3 V)"<br>- TV <sub>DD</sub> : deleted min value<br>Table: "Reset electrical characteristics"<br>- Changed footnotes 2 and 5<br>Table: "Voltage regulator electrical characteristics"<br>- C <sub>REGn</sub> : changed max value<br>- C <sub>DEC1</sub> : split into 2 rows<br>- Updated voltage values in footnote 3<br>Table: "Low voltage monitor electrical characteristics"<br>- Updated voltage nonitor electrical characteristics"<br>- Updated voltage nonitor electrical characteristics"<br>- Updated column Conditions<br>- V <sub>LVDLVCORL</sub> , V <sub>LVDLVBKPL</sub> : changed min/max value<br>Table: "Program and erase specifications"<br>- T <sub>dwprogram</sub> : added initial max value<br>Table: "Flash module life"<br>- Retention: changed min value for blocks with 100K P/E cycles<br>Table: "Flash power supply DC electrical characteristics"<br>- IFREAD, IFMOD: added typ value<br>- Added a footnote<br>Added Section: " NVUSRO[WATCHDOG_EN] field description"<br>Section 4.18: "ADC electrical characteristics" has been moved up in hierarchy (it was<br>Section 4.18: 5).<br>Table: "ADC conversion characteristics"<br>- R <sub>AD</sub> : changed initial max value<br>Table: "On-chip peripherals current consumption"<br>- Removed min/max from the heading<br>- Changed unit of measurement and consequently rounded the values |

| 15-Mar-2010 | 6        | Internal release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 55. Document revision history (continued)

| Table 55. | Document | revision | history | (continued) | ) |

|-----------|----------|----------|---------|-------------|---|

|           | Document | 10131011 | matory  | Commuca     | , |