Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                |

| Peripherals                | DMA, POR, PWM, WDT                                                    |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                           |

| Data Converters            | A/D 12x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f070c6t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F070CB/RB/C6/F6 microcontrollers.

This document should be read in conjunction with the STM32F0x0xx reference manual (RM0360). The reference manual is available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core, please refer to the Cortex<sup>®</sup>-M0 Technical Reference Manual, available from the www.arm.com website.

# 3 Functional overview

# 3.1 ARM<sup>®</sup>-Cortex<sup>®</sup>-M0 core with embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processor is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The STM32F0xx family has an embedded ARM core and is therefore compatible with all ARM tools and software.

Figure 1 shows the general block diagram of the device family.

### 3.2 Memories

The device has the following features:

- 6 to 16 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for failcritical applications.

- The non-volatile memory is divided into two arrays:

- 32 to 128 Kbytes of embedded Flash memory for programs and data

- Option bytes

The option bytes are used to write-protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex<sup>®</sup>-M0 serial wire) and boot in RAM selection disabled

## 3.3 Boot modes

At startup, the boot pin and boot selector option bit are used to select one of the three boot options:

- Boot from User Flash

- Boot from System Memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART on pins PA14/PA15 or PA9/PA10.

## 3.4 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

### 3.5 **Power management**

#### 3.5.1 Power supply schemes

- V<sub>DD</sub> = 2.4 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through VDD pins.

- V<sub>DDA</sub> = from V<sub>DD</sub> to 3.6 V: external analog power supply for ADC, Reset blocks, RCs and PLL. The V<sub>DDA</sub> voltage level must be always greater or equal to the V<sub>DD</sub> voltage level and must be provided first.

For more details on how to connect power pins, refer to *Figure 9: Power supply scheme*.

#### 3.5.2 Power supply supervisors

The device has integrated power-on reset (POR) and power-down reset (PDR) circuits. They are always active, and ensure proper operation above a threshold of 2 V. The device remains in reset mode when the monitored supply voltage is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

#### 3.5.3 Voltage regulator

The regulator has two operating modes and it is always enabled after reset.

- Main (MR) is used in normal operating mode (Run).

- Low power (LPR) can be used in Stop mode where the power demand is reduced.

In Standby mode, it is put in power down mode. In this mode, the regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost).

#### 3.5.4 Low-power modes

The STM32F070CB/RB/C6/F6 microcontrollers support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines and RTC.

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the RTC domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pins, or an RTC event occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

## 3.6 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the application to configure the frequency of the AHB and the APB domains. The maximum frequency of the AHB and the APB domains is 48 MHz.

## 3.10 Analog to digital converter (ADC)

The 12-bit analog to digital converter has up to 16 external and two internal (temperature sensor, voltage reference measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

#### 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\mbox{\scriptsize SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                               | Memory address            |

|------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV) | 0x1FFF F7B8 - 0x1FFF F7B9 |

Table 2. Temperature sensor calibration values

### 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Table 3. | Internal | voltage | reference | calibration values |

|----------|----------|---------|-----------|--------------------|

|----------|----------|---------|-----------|--------------------|

| Calibration value name | Description                                                                                        | Memory address            |

|------------------------|----------------------------------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV) | 0x1FFF F7BA - 0x1FFF F7BB |

|           | Table 9. Legend/abbreviations used in the pinout table |                                                                                                   |                                                                                                   |  |  |

|-----------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| Na        | me                                                     | Abbreviation                                                                                      | Definition                                                                                        |  |  |

| Pin r     | name                                                   |                                                                                                   | specified in brackets below the pin name, the pin function during and same as the actual pin name |  |  |

|           |                                                        | S                                                                                                 | Supply pin                                                                                        |  |  |

| Pin       | type                                                   | I                                                                                                 | Input only pin                                                                                    |  |  |

|           |                                                        | I/O                                                                                               | Input / output pin                                                                                |  |  |

|           |                                                        | FT                                                                                                | 5 V tolerant I/O                                                                                  |  |  |

|           |                                                        | FTf                                                                                               | 5 V tolerant I/O, FM+ capable                                                                     |  |  |

| 1/O atr   | ucture                                                 | ТТа                                                                                               | 3.3 V tolerant I/O directly connected to ADC                                                      |  |  |

| 1/O Sti   | ucture                                                 | TC                                                                                                | Standard 3.3 V I/O                                                                                |  |  |

|           |                                                        | В                                                                                                 | Dedicated BOOT0 pin                                                                               |  |  |

|           |                                                        | RST                                                                                               | Bidirectional reset pin with embedded weak pull-up resistor                                       |  |  |

| No        | tes                                                    | Unless otherwise specified by a note, all I/Os are set as floating inputs during and after reset. |                                                                                                   |  |  |

| Pin       | Alternate<br>functions                                 | Functions selecte                                                                                 | Functions selected through GPIOx_AFR registers                                                    |  |  |

| functions | Additional functions                                   | Functions directly                                                                                | selected/enabled through peripheral registers                                                     |  |  |

|             | Table 11. Alternate functions selected through GPIOA_AFR registers for port A |            |                        |          |                           |                           |          |     |  |

|-------------|-------------------------------------------------------------------------------|------------|------------------------|----------|---------------------------|---------------------------|----------|-----|--|

| Pin<br>name | AF0                                                                           | AF1        | AF2                    | AF3      | AF4                       | AF5                       | AF6      | AF7 |  |

| PA0         | -                                                                             | USART2_CTS | -                      | -        | USART4_TX <sup>(1)</sup>  | -                         | -        | -   |  |

| PA1         | EVENTOUT                                                                      | USART2_RTS | -                      | -        | USART4_RX <sup>(1)</sup>  | TIM15_CH1N <sup>(1)</sup> | -        | -   |  |

| PA2         | TIM15_CH1 <sup>(1)</sup>                                                      | USART2_TX  | -                      | -        | -                         | -                         | -        | -   |  |

| PA3         | TIM15_CH2 <sup>(1)</sup>                                                      | USART2_RX  | -                      | -        | -                         | -                         | -        | -   |  |

| PA4         | SPI1_NSS                                                                      | USART2_CK  | USB_NOE <sup>(2)</sup> | -        | TIM14_CH1                 | -                         | -        | -   |  |

| PA5         | SPI1_SCK                                                                      | -          | -                      | -        | -                         | -                         | -        | -   |  |

| PA6         | SPI1_MISO                                                                     | TIM3_CH1   | TIM1_BKIN              | -        | USART3_CTS <sup>(1)</sup> | TIM16_CH1                 | EVENTOUT | -   |  |

| PA7         | SPI1_MOSI                                                                     | TIM3_CH2   | TIM1_CH1N              | -        | TIM14_CH1                 | TIM17_CH1                 | EVENTOUT | -   |  |

| PA8         | MCO                                                                           | USART1_CK  | TIM1_CH1               | EVENTOUT | -                         | -                         | -        | -   |  |

| PA9         | TIM15_BKIN <sup>(1)</sup>                                                     | USART1_TX  | TIM1_CH2               | -        | I2C1_SCL (2)              | -                         | -        | -   |  |

| PA10        | TIM17_BKIN                                                                    | USART1_RX  | TIM1_CH3               | -        | I2C1_SDA (2)              | -                         | -        | -   |  |

| PA11        | EVENTOUT                                                                      | USART1_CTS | TIM1_CH4               | -        | -                         | -                         | -        | -   |  |

| PA12        | EVENTOUT                                                                      | USART1_RTS | TIM1_ETR               | -        | -                         | -                         | -        | -   |  |

| PA13        | SWDIO                                                                         | IR_OUT     | USB_NOE                | -        | -                         | -                         | -        | -   |  |

| PA14        | SWCLK                                                                         | USART2_TX  | -                      | -        | -                         | -                         | -        | -   |  |

| PA15        | SPI1_NSS                                                                      | USART2_RX  | -                      | EVENTOUT | USART4_RTS <sup>(1)</sup> | -                         | -        | -   |  |

Table 11. Alternate functions selected through GPIOA AFR registers for port A

1. Available on STM32F070CB/RB devices only.

2. Available on STM32F070C6/F6 devices only.

| Pin name | AF0                      | AF1                     | AF2        | AF3                       | AF4                       | AF5                       |

|----------|--------------------------|-------------------------|------------|---------------------------|---------------------------|---------------------------|

| PB0      | EVENTOUT                 | TIM3_CH3                | TIM1_CH2N  | -                         | USART3_CK <sup>(1)</sup>  | -                         |

| PB1      | TIM14_CH1                | TIM3_CH4                | TIM1_CH3N  | -                         | USART3_RTS <sup>(1)</sup> | -                         |

| PB2      | -                        | -                       | -          | -                         | -                         | -                         |

| PB3      | SPI1_SCK                 | EVENTOUT                | -          | -                         | -                         | -                         |

| PB4      | SPI1_MISO                | TIM3_CH1                | EVENTOUT   | -                         | -                         | TIM17_BKIN                |

| PB5      | SPI1_MOSI                | TIM3_CH2                | TIM16_BKIN | I2C1_SMBA                 | -                         | -                         |

| PB6      | USART1_TX                | I2C1_SCL                | TIM16_CH1N | -                         | -                         | -                         |

| PB7      | USART1_RX                | I2C1_SDA                | TIM17_CH1N | -                         | USART4_CTS <sup>(1)</sup> | -                         |

| PB8      | -                        | I2C1_SCL                | TIM16_CH1  | -                         | -                         | -                         |

| PB9      | IR_OUT                   | I2C1_SDA                | TIM17_CH1  | EVENTOUT                  | -                         | SPI2_NSS <sup>(1)</sup>   |

| PB10     | -                        | I2C2_SCL <sup>(1)</sup> | -          | -                         | USART3_TX <sup>(1)</sup>  | SPI2_SCK <sup>(1)</sup>   |

| PB11     | EVENTOUT                 | I2C2_SDA <sup>(1)</sup> | -          | -                         | USART3_RX <sup>(1)</sup>  | -                         |

| PB12     | SPI2_NSS <sup>(1)</sup>  | EVENTOUT                | TIM1_BKIN  | -                         | USART3_CK <sup>(1)</sup>  | TIM15_BKIN <sup>(1)</sup> |

| PB13     | SPI2_SCK <sup>(1)</sup>  | -                       | TIM1_CH1N  | -                         | USART3_CTS <sup>(1)</sup> | I2C2_SCL <sup>(1)</sup>   |

| PB14     | SPI2_MISO <sup>(1)</sup> | TIM15_CH1               | TIM1_CH2N  | -                         | USART3_RTS <sup>(1)</sup> | I2C2_SDA <sup>(1)</sup>   |

| PB15     | SPI2_MOSI <sup>(1)</sup> | TIM15_CH2               | TIM1 CH3N  | TIM15_CH1N <sup>(1)</sup> | -                         | -                         |

1. Available on STM32F070xB devices only.

577

| Pin name | AF0 <sup>(1)</sup>       | AF1 <sup>(1)</sup>       |

|----------|--------------------------|--------------------------|

| PC0      | EVENTOUT <sup>(1)</sup>  | -                        |

| PC1      | EVENTOUT <sup>(1)</sup>  | -                        |

| PC2      | EVENTOUT <sup>(1)</sup>  | SPI2_MISO <sup>(1)</sup> |

| PC3      | EVENTOUT <sup>(1)</sup>  | SPI2_MOSI <sup>(1)</sup> |

| PC4      | EVENTOUT <sup>(1)</sup>  | USART3_TX <sup>(1)</sup> |

| PC5      | -                        | USART3_RX <sup>(1</sup>  |

| PC6      | TIM3_CH1 <sup>(1)</sup>  | -                        |

| PC7      | TIM3_CH2 <sup>(1)</sup>  | -                        |

| PC8      | TIM3_CH3 <sup>(1)</sup>  | -                        |

| PC9      | TIM3_CH4 <sup>(1)</sup>  | -                        |

| PC10     | USART4_TX <sup>(1)</sup> | USART3_TX <sup>(1)</sup> |

| PC11     | USART4_RX <sup>(1)</sup> | USART3_RX <sup>(1</sup>  |

| PC12     | USART4_CK <sup>(1)</sup> | USART3_CK <sup>(1</sup>  |

| PC13     | -                        | -                        |

| PC14     | -                        | -                        |

| PC15     | -                        | -                        |

Table 13. Alternate functions selected through GPIOC\_AFR registers for port C

1. Available on STM32F070xB devices only.

#### Table 14. Alternate functions selected through GPIOD\_AFR registers for port D

| Pin name | AF0 <sup>(1)</sup>      | AF1 <sup>(1)</sup> |

|----------|-------------------------|--------------------|

| PD2      | TIM3_ETR <sup>(1)</sup> | -                  |

1. Available on STM32F070xB devices only.

#### Table 15. Alternate functions selected through GPIOF\_AFR registers for port F

| Pin name | AF0 | AF1                     |

|----------|-----|-------------------------|

| PF0      | -   | I2C1_SDA <sup>(1)</sup> |

| PF1      | -   | I2C1_SCL <sup>(1)</sup> |

1. Available on STM32F070x6 devices only.

| Bus  | Boundary address          | Size    | Peripheral      |

|------|---------------------------|---------|-----------------|

| -    | 0x4800 1800 - 0x5FFF FFFF | ~384 MB | Reserved        |

|      | 0x4800 1400 - 0x4800 17FF | 1 KB    | GPIOF           |

|      | 0x4800 1000 - 0x4800 13FF | 1 KB    | Reserved        |

| AHB2 | 0x4800 0C00 - 0x4800 0FFF | 1 KB    | GPIOD           |

| ANDZ | 0x4800 0800 - 0x4800 0BFF | 1 KB    | GPIOC           |

|      | 0x4800 0400 - 0x4800 07FF | 1 KB    | GPIOB           |

|      | 0x4800 0000 - 0x4800 03FF | 1 KB    | GPIOA           |

| -    | 0x4002 4400 - 0x47FF FFFF | ~128 MB | Reserved        |

|      | 0x4002 3400 - 0x4002 43FF | 4 KB    | Reserved        |

|      | 0x4002 3000 - 0x4002 33FF | 1 KB    | CRC             |

|      | 0x4002 2400 - 0x4002 2FFF | 3 KB    | Reserved        |

|      | 0x4002 2000 - 0x4002 23FF | 1 KB    | FLASH Interface |

| AHB1 | 0x4002 1400 - 0x4002 1FFF | 3 KB    | Reserved        |

|      | 0x4002 1000 - 0x4002 13FF | 1 KB    | RCC             |

|      | 0x4002 0400 - 0x4002 0FFF | 3 KB    | Reserved        |

|      | 0x4002 0000 - 0x4002 03FF | 1 KB    | DMA             |

| -    | 0x4001 8000 - 0x4001 FFFF | 32 KB   | Reserved        |

|      | 0x4001 5C00 - 0x4001 7FFF | 9 KB    | Reserved        |

|      | 0x4001 5800 - 0x4001 5BFF | 1 KB    | DBGMCU          |

|      | 0x4001 4C00 - 0x4001 57FF | 3 KB    | Reserved        |

|      | 0x4001 4800 - 0x4001 4BFF | 1 KB    | TIM17           |

|      | 0x4001 4400 - 0x4001 47FF | 1 KB    | TIM16           |

|      | 0x4001 4000 - 0x4001 43FF | 1 KB    | TIM15           |

|      | 0x4001 3C00 - 0x4001 3FFF | 1 KB    | Reserved        |

|      | 0x4001 3800 - 0x4001 3BFF | 1 KB    | USART1          |

| APB  | 0x4001 3400 - 0x4001 37FF | 1 KB    | Reserved        |

|      | 0x4001 3000 - 0x4001 33FF | 1 KB    | SPI1            |

|      | 0x4001 2C00 - 0x4001 2FFF | 1 KB    | TIM1            |

|      | 0x4001 2800 - 0x4001 2BFF | 1 KB    | Reserved        |

|      | 0x4001 2400 - 0x4001 27FF | 1 KB    | ADC             |

|      | 0x4001 0800 - 0x4001 23FF | 7 KB    | Reserved        |

|      | 0x4001 0400 - 0x4001 07FF | 1 KB    | EXTI            |

|      | 0x4001 0000 - 0x4001 03FF | 1 KB    | SYSCFG          |

| -    | 0x4000 8000 - 0x4000 FFFF | 32 KB   | Reserved        |

### Table 16. STM32F070CB/RB/C6/F6 peripheral register boundary addresses

DocID027114 Rev 3

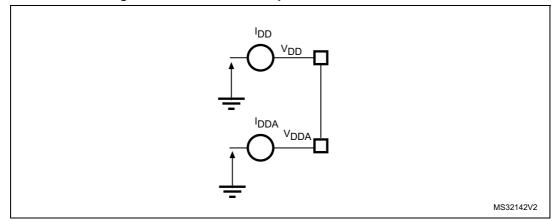

### 6.1.7 Current consumption measurement

#### Figure 10. Current consumption measurement scheme

### 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 17: Voltage characteristics*, *Table 18: Current characteristics* and *Table 19: Thermal characteristics* may cause permanent damage to the device. These are stress *ratings* only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                               | Min                                  | Мах                                     | Unit |

|-----------------------------------|-------------------------------------------------------|--------------------------------------|-----------------------------------------|------|

| $V_{DD} - V_{SS}$                 | External main supply voltage                          | -0.3                                 | 4.0                                     | V    |

| $V_{DDA} - V_{SS}$                | External analog supply voltage                        | -0.3                                 | 4.0                                     | V    |

| V <sub>DD</sub> -V <sub>DDA</sub> | Allowed voltage difference for $V_{DD} > V_{DDA}$     | -                                    | 0.4                                     | V    |

|                                   | Input voltage on FT and FTf pins                      | V <sub>SS</sub> –0.3                 | V <sub>DDIOx</sub> + 4.0 <sup>(3)</sup> | V    |

| $V_{IN}^{(2)}$                    | Input voltage on TTa pins                             | V <sub>SS</sub> –0.3                 | 4.0                                     | V    |

|                                   | BOOT0                                                 | 0                                    | V <sub>DDIOx</sub> + 4.0 <sup>(3)</sup> | V    |

|                                   | Input voltage on any other pin                        | V <sub>SS</sub> –0.3                 | 4.0                                     | V    |

| $ \Delta V_{DDx} $                | Variations between different $V_{DD}$ power pins      | -                                    | 50                                      | mV   |

| V <sub>SSx</sub> -V <sub>SS</sub> | Variations between all the different ground pins      | -                                    | 50                                      | mV   |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage<br>(human body model) | see Section 6.3<br>sensitivity chara |                                         | -    |

| Table 17 | . Voltage | characteristics <sup>(1)</sup> | ) |

|----------|-----------|--------------------------------|---|

|----------|-----------|--------------------------------|---|

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 18: Current characteristics* for the maximum allowed injected current values.

3.  $V_{DDIOx}$  is internally connected with VDD pin.

| Symbol                               | Ratings                                                                      | Max.                 | Unit |

|--------------------------------------|------------------------------------------------------------------------------|----------------------|------|

| ΣI <sub>VDD</sub>                    | Total current into sum of all VDD power lines (source) <sup>(1)</sup>        | 120                  |      |

| ΣI <sub>VSS</sub>                    | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>       | -120                 |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each VDD power pin (source) <sup>(1)</sup>              | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>             | -100                 |      |

|                                      | Output current sunk by any I/O and control pin                               | 25                   |      |

| I <sub>IO(PIN)</sub>                 | Output current source by any I/O and control pin                             | -25                  |      |

| ΣΙ                                   | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup> | 80                   | mA   |

| $\Sigma I_{IO(PIN)}$                 | Total output current sourced by sum of all I/Os and control $pins^{(2)}$     | -80                  |      |

|                                      | Injected current on FT and FTf pins                                          | -5/+0 <sup>(4)</sup> |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on TC and RST pin                                           | ± 5                  |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                  | ± 5                  | 1    |

| Σl <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>      | ± 25                 | 1    |

1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

A positive injection is induced by V<sub>IN</sub> > V<sub>DDIOx</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 17: Voltage characteristics* for the maximum allowed input voltage values.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

On these I/Os, a positive injection is induced by V<sub>IN</sub> > V<sub>DDA</sub>. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 51: ADC accuracy*.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 19. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

## 6.3 Operating conditions

### 6.3.1 General operating conditions

| Table 20 | . General | operating | conditions |

|----------|-----------|-----------|------------|

|----------|-----------|-----------|------------|

| Symbol            | Parameter                    | Conditions | Min | Мах | Unit |

|-------------------|------------------------------|------------|-----|-----|------|

| f <sub>HCLK</sub> | Internal AHB clock frequency | -          | 0   | 48  | MHz  |

| f <sub>PCLK</sub> | Internal APB clock frequency | -          | 0   | 48  |      |

| V <sub>DD</sub>   | Standard operating voltage   | -          | 2.4 | 3.6 | V    |

|                  |                                      |                             |                   | Т                      |                         |      |  |

|------------------|--------------------------------------|-----------------------------|-------------------|------------------------|-------------------------|------|--|

| Symbol           | Parameter Conditions                 |                             | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit |  |

|                  | Supply current in Run                | Running from                | 48 MHz            | 23.5                   | 13.5                    |      |  |

| IDD              | mode from V <sub>DD</sub><br>supply  | HSE crystal<br>clock 8 MHz, | 8 MHz             | 4.8                    | 3.1                     | mA   |  |

|                  | Supply current in Run                | code executing              | 48 MHz            | 163.3                  | 163.3                   |      |  |

| I <sub>DDA</sub> | mode from V <sub>DDA</sub><br>supply | from Flash                  | 8 MHz             | 2.5                    | 2.5                     | μA   |  |

Table 27. Typical current consumption in Run mode, code with data processingrunning from Flash

### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 45: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously, the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

| Symbol                  | Parameter Conditions <sup>(1)</sup> |                                                            | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |  |

|-------------------------|-------------------------------------|------------------------------------------------------------|--------------------|-----|--------------------|------|--|

|                         |                                     | During startup <sup>(3)</sup>                              | -                  | -   | 8.5                |      |  |

| I <sub>DD</sub>         | HSE current consumption             | V <sub>DD</sub> = 3.3 V,<br>Rm = 45 Ω<br>CL = 10 pF@8 MHz  | -                  | 0.5 | -                  | mA   |  |

|                         |                                     | V <sub>DD</sub> = 3.3 V,<br>Rm = 30 Ω<br>CL = 20 pF@32 MHz | -                  | 1.5 | -                  |      |  |

| 9 <sub>m</sub>          | Oscillator transconductance         | Startup                                                    | 10                 | -   | -                  | mA/V |  |

| $t_{\rm SU(HSE)}^{(4)}$ | Startup time                        | $V_{DD}$ is stabilized                                     | -                  | 2   | -                  | ms   |  |

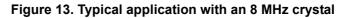

| Table 32. HSE oscillator | characteristics |

|--------------------------|-----------------|

|--------------------------|-----------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

- 2. Guaranteed by design, not tested in production.

- 3. This consumption level occurs during the first 2/3 of the  $t_{\mbox{SU(HSE)}}$  startup time

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 13*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

#### Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

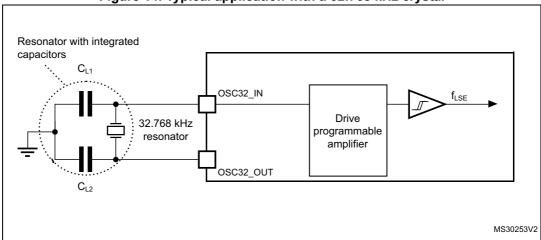

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results

obtained with typical external components specified in *Table 33*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions <sup>(1)</sup>        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-----------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

|                                     |                                         | low drive capability             | -                  | 0.5 | 0.9                |      |

|                                     | LSE current                             | medium-low drive capability      | -                  | -   | 1                  |      |

| I <sub>DD</sub>                     | onsumption medium-high drive capability |                                  | -                  | -   | 1.3                | μA   |

|                                     |                                         | high drive capability            |                    | -   | 1.6                |      |

|                                     | low drive capability                    |                                  | 5                  | -   | -                  |      |

|                                     | Oscillator                              | medium-low drive capability      | 8                  | -   | -                  | µA/V |

| 9 <sub>m</sub>                      | transconductance                        | medium-high drive capability     | 15                 | -   | -                  | μΑνν |

|                                     | high drive capability                   |                                  | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                            | V <sub>DDIOx</sub> is stabilized | -                  | 2   | -                  | S    |

Table 33. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 14. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

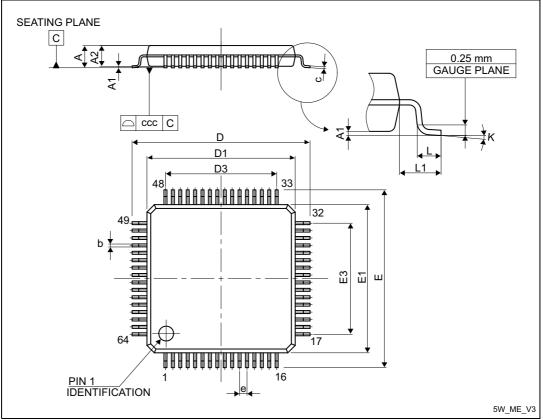

## 7.1 LQFP64 package information

LQFP64 is 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 24. LQFP64 outline

1. Drawing is not to scale.

Table 59. LQFP64 mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| Cumhal | millimeters |        | inches <sup>(1)</sup> |        |        |        |

|--------|-------------|--------|-----------------------|--------|--------|--------|

| Symbol | Min         | Тур    | Max                   | Min    | Тур    | Max    |

| b      | 0.170       | 0.220  | 0.270                 | 0.0067 | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200                 | 0.0035 | -      | 0.0079 |

| D      | -           | 12.000 | -                     | -      | 0.4724 | -      |

| D1     | -           | 10.000 | -                     | -      | 0.3937 | -      |

| D3     | -           | 7.500  | -                     | -      | 0.2953 | -      |

| E      | -           | 12.000 | -                     | -      | 0.4724 | -      |

| E1     | -           | 10.000 | -                     | -      | 0.3937 | -      |

| E3     | -           | 7.500  | -                     | -      | 0.2953 | -      |

| е      | -           | 0.500  | -                     | -      | 0.0197 | -      |

| К      | 0°          | 3.5°   | 7°                    | 0°     | 3.5°   | 7°     |

| L      | 0.450       | 0.600  | 0.750                 | 0.0177 | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -                     | -      | 0.0394 | -      |

| CCC    | -           | -      | 0.080                 | -      | -      | 0.0031 |

Table 59. LQFP64 mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

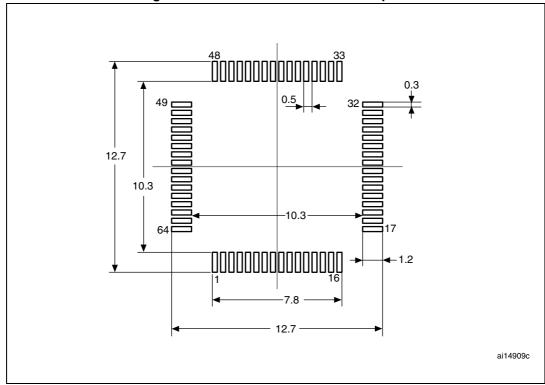

#### Figure 25. LQFP64 recommended footprint

1. Dimensions are expressed in millimeters.

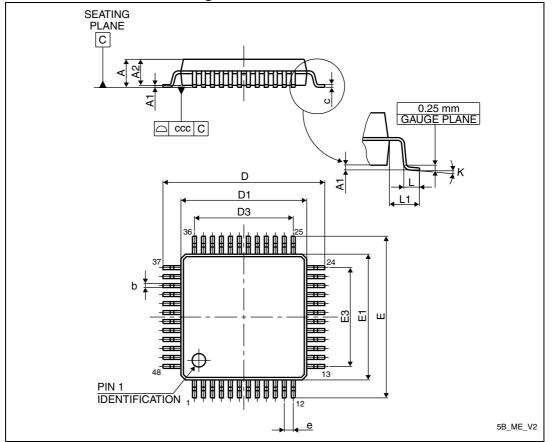

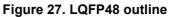

# 7.2 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7 mm low-profile quad flat package

<sup>1.</sup> Drawing is not to scale.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур   | Max   | Min                   | Тур    | Max    |  |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| E      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

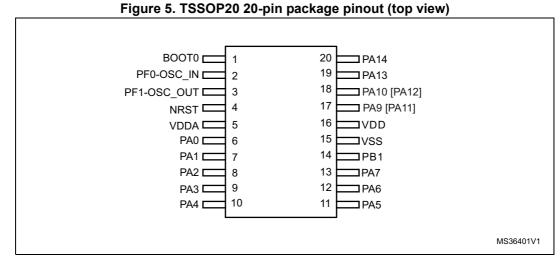

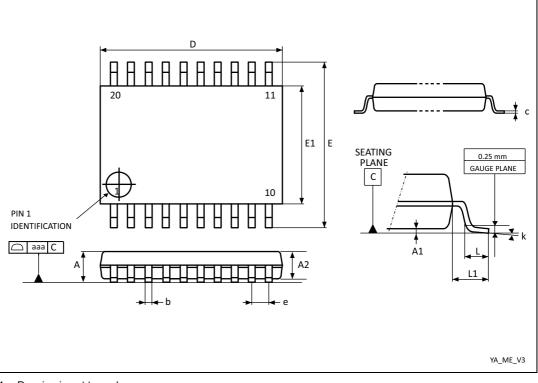

# 7.3 TSSOP20 package information

TSSOP20 is a 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch package.

Figure 30.TSSOP20 outline

1. Drawing is not to scale.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |

| А      | -           | -     | 1.200 | -                     | -      | 0.0472 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 0.800       | 1.000 | 1.050 | 0.0315                | 0.0394 | 0.0413 |

| b      | 0.190       | -     | 0.300 | 0.0075                | -      | 0.0118 |

| с      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 6.400       | 6.500 | 6.600 | 0.2520                | 0.2559 | 0.2598 |

| E      | 6.200       | 6.400 | 6.600 | 0.2441                | 0.2520 | 0.2598 |

| E1     | 4.300       | 4.400 | 4.500 | 0.1693                | 0.1732 | 0.1772 |

| е      | -           | 0.650 | -     | -                     | 0.0256 | -      |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | _                     | 0.0394 | -      |

| Symbol | millimeters |      |       | inches <sup>(1)</sup> |      |        |

|--------|-------------|------|-------|-----------------------|------|--------|

|        | Min.        | Тур. | Max.  | Min.                  | Тур. | Max.   |

| k      | 0°          | -    | 8°    | 0°                    | -    | 8°     |

| aaa    | -           | -    | 0.100 | -                     | -    | 0.0039 |

Table 61. TSSOP20 mechanical data (continued)

1. Values in inches are converted from mm and rounded to four decimal digits.

### Figure 31. TSSOP20 footprint

1. Dimensions are expressed in millimeters.