Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 29                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | OTP                                                            |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 21x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t610-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| C2 Register Definition 27.1. C2ADD: C2 Address                         | 208 |

|------------------------------------------------------------------------|-----|

| C2 Register Definition 27.2. DEVICEID: C2 Device ID                    | 209 |

| C2 Register Definition 27.3. REVID: C2 Revision ID                     | 209 |

| C2 Register Definition 27.4. DEVCTL: C2 Device Control                 | 210 |

| C2 Register Definition 27.5. EPCTL: EPROM Programming Control Register | 210 |

| C2 Register Definition 27.6. EPDAT: C2 EPROM Data                      | 211 |

| C2 Register Definition 27.7. EPSTAT: C2 EPROM Status                   | 211 |

| C2 Register Definition 27.8. EPADDRH: C2 EPROM Address High Byte       | 212 |

| C2 Register Definition 27.9. EPADDRL: C2 EPROM Address Low Byte        | 212 |

| C2 Register Definition 27.10. CRC0: CRC Byte 0                         | 213 |

| C2 Register Definition 27.11. CRC1: CRC Byte 1                         | 213 |

| C2 Register Definition 27.12. CRC2: CRC Byte 2                         | 214 |

| C2 Register Definition 27.13. CRC3: CRC Byte 3                         | 214 |

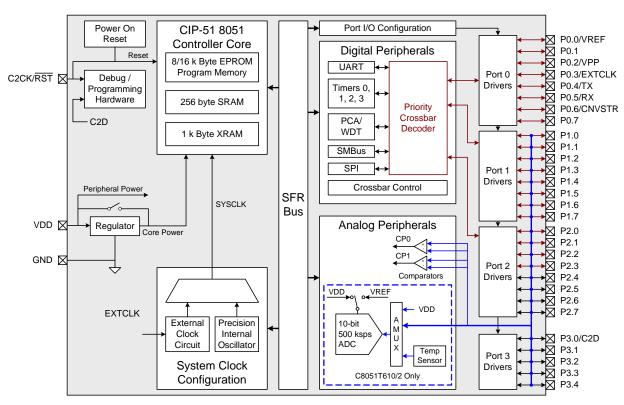

# 1. System Overview

C8051T610/1/2/3/4/5/6/7 devices are fully integrated, mixed-signal, system-on-a-chip MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- C8051F310 ISP Flash device is available for quick in-system code development

- 10-bit 500 ksps Single-ended ADC with analog multiplexer and integrated temperature sensor

- Precision calibrated 24.5 MHz internal oscillator

- 16 k or 8 k of on-chip Byte-Programmable EPROM—(512 bytes are reserved on 16k version)

- 1280 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, SPI, and Enhanced UART serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset and  $V_{DD}$  Monitor

- On-chip Voltage Comparators (2)

- 29/25/21 Port I/O

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051T610/1/2/3/4/5/6/7 devices are truly stand-alone, system-on-a-chip solutions. User software has complete control of all peripherals and may individually shut down any or all peripherals for power savings.

Code written for the C8051T610/1/2/3/4/5/6/7 family of processors will run on the C8051F310 Mixed-Signal ISP Flash microcontroller, providing a quick, cost-effective way to develop code without requiring special emulator circuitry. The C8051T610/1/2/3/4/5/6/7 processors include Silicon Laboratories' 2-Wire C2 Debug and Programming interface, which allows non-intrusive (uses no on-chip resources), full speed, incircuit debugging using the production MCU installed in the final application. This debug logic supports inspection of memory, viewing and modification of special function registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 1.8-3.6 V operation over the industrial temperature range (-45 to +85 °C). An internal LDO is used to supply the processor core voltage. The Port I/O and RST pins are tolerant of input signals up to 5 V. See Table 2.1 for ordering information. Block diagrams of the devices in the C8051T610/1/2/3/4/5/6/7 family are shown in Figure 1.1, Figure 1.2 and Figure 1.3.

Figure 1.1. C8051T610/2/4 Block Diagram (32-pin LQFP)

# SFR Definition 8.2. ADC0H: ADC0 Data Word MSB

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | ADC0H[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xBE

| Bit | Name       | Function                                                                                                     |

|-----|------------|--------------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                              |

|     |            | For AD0LJST = 0: Bits 7–2 will read 000000b. Bits 1–0 are the upper 2 bits of the 10-<br>bit ADC0 Data Word. |

|     |            | For AD0LJST = 1: Bits 7–0 are the most-significant bits of the 10-bit ADC0 Data Word.                        |

|     |            | <b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0H holds the 8-bit data word.                          |

# SFR Definition 8.3. ADC0L: ADC0 Data Word LSB

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | ADC0L[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xBD

| Bit | Name       | Function                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------|

| 7:0 | ADC0L[7:0] | ADC0 Data Word Low-Order Bits.                                                                      |

|     |            | For AD0LJST = 0: Bits 7–0 are the lower 8 bits of the 10-bit Data Word.                             |

|     |            | For AD0LJST = 1: Bits 7–6 are the lower 2 bits of the 10-bit Data Word. Bits 5–0 will read 000000b. |

|     |            | <b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0L will read back 0000000b.                   |

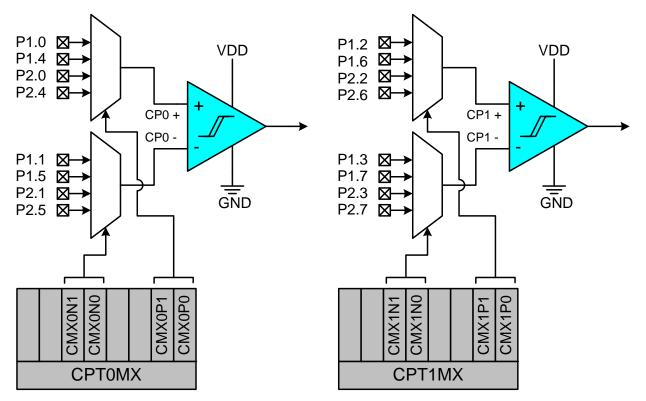

## 12.1. Comparator Multiplexers

C8051T610/1/2/3/4/5/6/7 devices include analog input multiplexers to connect Port I/O pins to the comparator inputs. The Comparator0 inputs are selected in the CPT0MX register (SFR Definition 12.5). The CMX-0P1–CMX0P0 bits select the Comparator0 positive input; the CMX0N1–CMX0N0 bits select the Comparator0 negative input. Likewise, the Comparator1 inputs are selected in the CPT1MX register (SFR Definition 12.6). **Important Note About Comparator Inputs:** The Port pins selected as comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see Section "21.5. Special Function Registers for Accessing and Configuring Port I/O" on page 124).

Figure 12.4. Comparator Input Multiplexer Block Diagram

# SFR Definition 12.5. CPT0MX: Comparator0 MUX Selection

| Bit   | 7 | 6 | 5    | 4      | 3 | 2 | 1    | 0      |

|-------|---|---|------|--------|---|---|------|--------|

| Name  |   |   | CMX0 | N[1:0] |   |   | CMX0 | P[1:0] |

| Туре  | R | R | R/W  |        | R | R | R/   | W      |

| Reset | 0 | 0 | 0 0  |        | 0 | 0 | 0    | 0      |

SFR Address = 0x9F

| Bit | Name       | Function                                  |  |  |  |  |  |

|-----|------------|-------------------------------------------|--|--|--|--|--|

| 7:6 | Unused     | Inused, Read = 00b; Write = Don't Care    |  |  |  |  |  |

| 5:4 | CMX0N[1:0] | Comparator0 Negative Input MUX Selection. |  |  |  |  |  |

|     |            | 00: P1.1                                  |  |  |  |  |  |

|     |            | 01: P1.5                                  |  |  |  |  |  |

|     |            | 10: P2.1                                  |  |  |  |  |  |

|     |            | 11: P2.5                                  |  |  |  |  |  |

| 3:2 | Unused     | Unused, Read = 00b; Write = Don't Care    |  |  |  |  |  |

| 1:0 | CMX0P[1:0] | Comparator0 Positive Input MUX Selection. |  |  |  |  |  |

|     |            | 00: P1.0                                  |  |  |  |  |  |

|     |            | 01: P1.4                                  |  |  |  |  |  |

|     |            | 10: P2.0                                  |  |  |  |  |  |

|     |            | 11: P2.4                                  |  |  |  |  |  |

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

## 13.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

### 13.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 13.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

| Mnemonic                                                                 | Description                                         | Bytes | Clock<br>Cycles |

|--------------------------------------------------------------------------|-----------------------------------------------------|-------|-----------------|

| ANL C, bit                                                               | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit                                                              | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit                                                               | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit                                                              | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit                                                               | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C                                                               | Move Carry to direct bit                            | 2     | 2               |

| JC rel                                                                   | Jump if Carry is set                                | 2     | 2/3             |

| JNC rel                                                                  | Jump if Carry is not set                            | 2     | 2/3             |

| JB bit, rel                                                              | Jump if direct bit is set                           | 3     | 3/4             |

| JNB bit, rel                                                             | Jump if direct bit is not set                       | 3     | 3/4             |

| JBC bit, rel                                                             | Jump if direct bit is set and clear bit             | 3     | 3/4             |

| Program Branching                                                        |                                                     |       |                 |

| ACALL addr11                                                             | Absolute subroutine call                            | 2     | 3               |

| LCALL addr16                                                             | Long subroutine call                                | 3     | 4               |

| RET                                                                      | Return from subroutine                              | 1     | 5               |

| RETI                                                                     | Return from interrupt                               | 1     | 5               |

| AJMP addr11                                                              | Absolute jump                                       | 2     | 3               |

| LJMP addr16                                                              | Long jump                                           | 3     | 4               |

| SJMP rel                                                                 | Short jump (relative address)                       | 2     | 3               |

| JMP @A+DPTR                                                              | Jump indirect relative to DPTR                      | 1     | 3               |

| JZ rel                                                                   | Jump if A equals zero                               | 2     | 2/3             |

| JNZ rel                                                                  | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel                                                      | Compare direct byte to A and jump if not equal      | 3     | 4/5             |

| CJNE A, #data, rel                                                       | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel                                                      | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel Compare immediate to indirect and jump if not equal |                                                     | 3     | 4/5             |

| DJNZ Rn, rel                                                             | Decrement Register and jump if not zero             | 2     | 2/3             |

| DJNZ direct, rel                                                         | Decrement direct byte and jump if not zero          | 3     | 3/4             |

| NOP                                                                      | No operation                                        | 1     | 1               |

# Table 13.1. CIP-51 Instruction Set Summary (Continued)

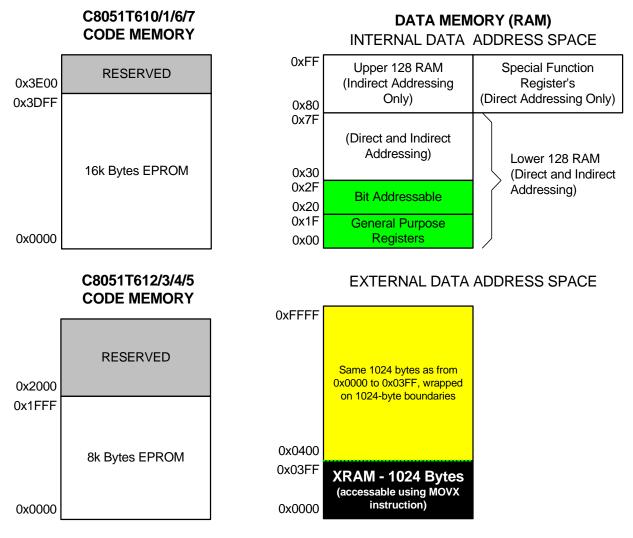

# 14. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory organization of the C8051T610/1/2/3/4/5/6/7 device family is shown in Figure 14.1

Figure 14.1. Memory Map

### 14.2.1.1. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 13.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 14.2.1.2. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 14.2.1.3. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

#### 14.2.2. External RAM

There are 1024 bytes of on-chip RAM mapped into the external data memory space. All of these address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMIOCN as shown in SFR Definition 14.1).

For a 16-bit MOVX operation (@DPTR), the upper 7 bits of the 16-bit external data memory address word are "don't cares". As a result, the 1024-byte RAM is mapped modulo style over the entire 64 k external data memory address range. For example, the XRAM byte at address 0x0000 is shadowed at addresses 0x0400, 0x0800, 0x0C00, 0x1000, etc. This is a useful feature when performing a linear memory fill, as the address pointer doesn't have to be reset when reaching the RAM block boundary.

## SFR Definition 19.1. VDM0CN: V<sub>DD</sub> Monitor Control

| Bit   | 7      | 6       | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---------|---|---|---|---|---|---|

| Name  | VDMEN  | VDDSTAT |   |   |   |   |   |   |

| Туре  | R/W    | R       | R | R | R | R | R | R |

| Reset | Varies | Varies  | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xFF

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 19.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source. See Table 7.4 for the minimum V <sub>DD</sub> Monitor turn-on time.<br>0: V <sub>DD</sub> Monitor Disabled.<br>1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         | This bit indicates the current power supply status ( $V_{DD}$ Monitor output).<br>0: $V_{DD}$ is at or below the $V_{DD}$ monitor threshold.<br>1: $V_{DD}$ is above the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5:0 | Unused  | Unused. Read = 000000b; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## 19.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 7.4 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

## 19.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the missing clock detector timeout, the one-shot will generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

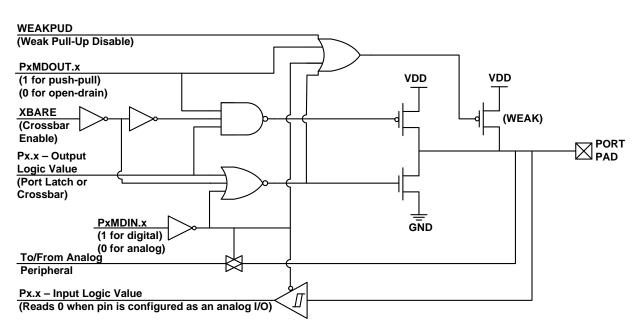

## Figure 21.2. Port I/O Cell Block Diagram

### 21.1.3. Interfacing Port I/O to 5V Logic

All Port I/O configured for digital, open-drain operation are capable of interfacing to digital logic operating at a supply voltage higher than VDD and less than 5.25 V. An external pullup resistor to the higher supply voltage on output pins is typically required for most systems.

**Important Notes:** The absolute maximum voltage of any Port I/O pin should be limited to VDD + 3.6V. When interfacing to systems with supply voltages higher than 3.6V, care must be taken to limit the voltage on I/O pins when the VDD supply to the device is not present. In a multi-voltage interface, the external pullup resistor should be sized to allow a current of at least 150  $\mu$ A to flow into the Port pin when the supply voltage is between (VDD + 0.6 V) and (VDD + 1.0 V). Once the Port pin voltage increases beyond this range, the current flowing into the Port pin is minimal.

## SFR Definition 22.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

#### SFR Address = 0xC0; Bit-Addressable

| Bit | Name    | Description                                                                                                                                                                                                      | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                                     | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                               | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                                | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                                 | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                                    | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                               | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | <b>SMBus Interrupt Flag.</b><br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | 0: Clear interrupt, and initi-<br>ate next state machine<br>event.<br>1: Force interrupt.                                                                                            |

|                    | Val                         | ues                                                | Rea                                                                                  | ad  |                                                 |                                                                                                |      | lues<br>Vrit |     | itus<br>bected                 |

|--------------------|-----------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------|-----|-------------------------------------------------|------------------------------------------------------------------------------------------------|------|--------------|-----|--------------------------------|

| Mode               | Status<br>Vector            | ACKRQ                                              | ARBLOST                                                                              | ACK | Current SMbus State                             | Typical Response Options                                                                       | STA  | STO          | ACK | Next Status<br>Vector Expected |

|                    | 1110                        | 0                                                  | 0                                                                                    | Х   | A master START was gener-<br>ated.              | Load slave address + R/W into SMB0DAT.                                                         | 0    | 0            | Х   | 1100                           |

|                    |                             |                                                    |                                                                                      |     | A master data or address byte                   | Set STA to restart transfer.                                                                   | 1    | 0            | Х   | 1110                           |

| tter               |                             | 0                                                  | 0                                                                                    | 0   | was transmitted; NACK received.                 | Abort transfer.                                                                                | 0    | 1            | Х   | _                              |

| insmit             |                             |                                                    |                                                                                      |     |                                                 | Load next data byte into SMB0DAT.                                                              | 0    | 0            | Х   | 1100                           |

| Tra                | 1100                        |                                                    | End transfer with STOP.                                                              | 0   | 1                                               | Х                                                                                              | _    |              |     |                                |

| Master Transmitter | A master<br>0 0 1 was trans | A master data or address byte was transmitted; ACK | End transfer with STOP and start another transfer.                                   | 1   | 1                                               | Х                                                                                              | _    |              |     |                                |

| 2                  |                             |                                                    |                                                                                      |     | received.                                       | Send repeated START.                                                                           | 1    | 0            | Х   | 1110                           |

|                    |                             |                                                    | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT). | 0   | 0                                               | Х                                                                                              | 1000 |              |     |                                |

|                    |                             |                                                    |                                                                                      |     |                                                 | Acknowledge received byte;<br>Read SMB0DAT.                                                    | 0    | 0            | 1   | 1000                           |

|                    |                             |                                                    |                                                                                      |     |                                                 | Send NACK to indicate last byte, and send STOP.                                                | 0    | 1            | 0   | _                              |

| ver                |                             |                                                    |                                                                                      |     |                                                 | Send NACK to indicate last byte,<br>and send STOP followed by<br>START.                        | 1    | 1            | 0   | 1110                           |

| Master Receiver    | 1000                        | ) 1                                                | 0                                                                                    | x   | A master data byte was received; ACK requested. | Send ACK followed by repeated START.                                                           | 1    | 0            | 1   | 1110                           |

| Aaster             | laster                      |                                                    |                                                                                      |     |                                                 | Send NACK to indicate last byte, and send repeated START.                                      | 1    | 0            | 0   | 1110                           |

|                    |                             |                                                    |                                                                                      |     |                                                 | Send ACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI).    | 0    | 0            | 1   | 1100                           |

|                    |                             |                                                    |                                                                                      |     |                                                 | Send NACK and switch to Mas-<br>ter Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0    | 0            | 0   | 1100                           |

Table 22.4. SMBus Status Decoding

## SFR Definition 23.1. SCON0: Serial Port 0 Control

| Bit   | 7      | 6 | 5    | 4    | 3    | 2    | 1   | 0   |

|-------|--------|---|------|------|------|------|-----|-----|

| Name  | SOMODE |   | MCE0 | REN0 | TB80 | RB80 | TIO | RI0 |

| Туре  | R/W    | R | R/W  | R/W  | R/W  | R/W  | R/W | R/W |

| Reset | 0      | 1 | 0    | 0    | 0    | 0    | 0   | 0   |

### SFR Address = 0x98; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SOMODE | Serial Port 0 Operation Mode.<br>Selects the UART0 Operation Mode.<br>0: 8-bit UART with Variable Baud Rate.<br>1: 9-bit UART with Variable Baud Rate.                                                                                                                                                                                                                                                                                                                                                         |

| 6   | Unused | Unused. Read = 1b, Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   | MCE0   | <ul> <li>Multiprocessor Communication Enable.</li> <li>The function of this bit is dependent on the Serial Port 0 Operation Mode:</li> <li>Mode 0: Checks for valid stop bit.</li> <li>0: Logic level of stop bit is ignored.</li> <li>1: RI0 will only be activated if stop bit is logic level 1.</li> <li>Mode 1: Multiprocessor Communications Enable.</li> <li>0: Logic level of ninth bit is ignored.</li> <li>1: RI0 is set and an interrupt is generated only when the ninth bit is logic 1.</li> </ul> |

| 4   | REN0   | Receive Enable.<br>0: UART0 reception disabled.<br>1: UART0 reception enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3   | TB80   | Ninth Transmission Bit.<br>The logic level of this bit will be sent as the ninth transmission bit in 9-bit UART Mode<br>(Mode 1). Unused in 8-bit mode (Mode 0).                                                                                                                                                                                                                                                                                                                                               |

| 2   | RB80   | Ninth Receive Bit.<br>RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the<br>9th data bit in Mode 1.                                                                                                                                                                                                                                                                                                                                                                         |

| 1   | TIO    | <b>Transmit Interrupt Flag.</b><br>Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bit in 8-bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the UART0 interrupt is enabled, setting this bit causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software.                                                                                                                                     |

| 0   | RIO    | <b>Receive Interrupt Flag.</b><br>Set to 1 by hardware when a byte of data has been received by UART0 (set at the STOP bit sampling time). When the UART0 interrupt is enabled, setting this bit to 1 causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software.                                                                                                                                                                                          |

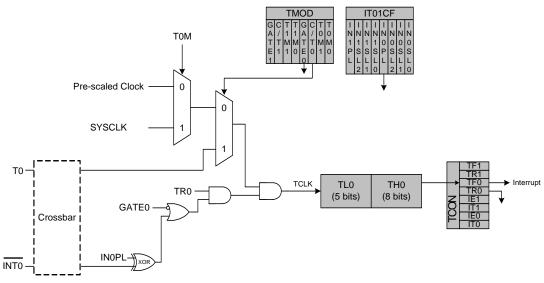

Figure 25.1. T0 Mode 0 Block Diagram

### 25.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

## SFR Definition 25.9. TMR2RLL: Timer 2 Reload Register Low Byte

| Bit    | 7                  | 6            | 5        | 4 | 3 | 2 | 1 | 0 |

|--------|--------------------|--------------|----------|---|---|---|---|---|

| Name   |                    | TMR2RLL[7:0] |          |   |   |   |   |   |

| Туре   |                    | R/W          |          |   |   |   |   |   |

| Reset  | 0                  | 0            | 0        | 0 | 0 | 0 | 0 | 0 |

| SFR Ad | SFR Address = 0xCA |              |          |   |   |   |   |   |

| Bit    | Name               |              | Function |   |   |   |   |   |

| ы   | Name         | i uncuon                                                    |

|-----|--------------|-------------------------------------------------------------|

| 7:0 | TMR2RLL[7:0] | Timer 2 Reload Register Low Byte.                           |

|     |              | TMR2RLL holds the low byte of the reload value for Timer 2. |

## SFR Definition 25.10. TMR2RLH: Timer 2 Reload Register High Byte

| Bit      | 7               | 6 | 5                                                                                                         | 4     | 3        | 2 | 1 | 0 |

|----------|-----------------|---|-----------------------------------------------------------------------------------------------------------|-------|----------|---|---|---|

| Nam      | e               |   | L                                                                                                         | TMR2R | LH[7:0]  |   | I | I |

| Type R/W |                 |   |                                                                                                           |       |          |   |   |   |

| Rese     | et <sup>0</sup> | 0 | 0                                                                                                         | 0     | 0        | 0 |   |   |

| SFR /    | Address = 0xCE  | 5 |                                                                                                           |       |          |   |   |   |

| Bit      | Name            |   |                                                                                                           |       | Function |   |   |   |

| 7:0      | TMR2RLH[7:0     |   | <b>Fimer 2 Reload Register High Byte.</b><br>FMR2RLH holds the high byte of the reload value for Timer 2. |       |          |   |   |   |

## SFR Definition 25.11. TMR2L: Timer 2 Low Byte

| Bit   | 7 | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|----|---|---|---|---|--|

| Name  |   | TMR2L[7:0]      |   |    |   |   |   |   |  |

| Туре  |   |                 |   | R/ | W |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |    |   |   |   |   |  |

#### SFR Address = 0xCC

| Bit | Name       | Function                                                                                                                                          |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2L[7:0] | Timer 2 Low Byte.                                                                                                                                 |

|     |            | In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2L contains the 8-bit low byte timer value. |

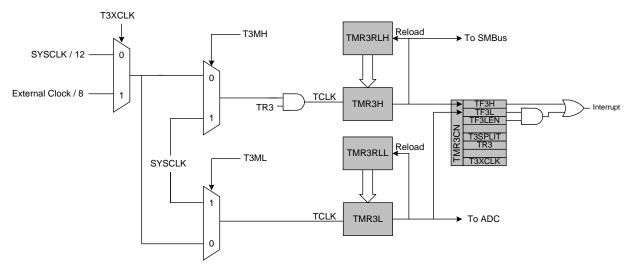

#### 25.3.2. 8-bit Timers with Auto-Reload

When T3SPLIT is set, Timer 3 operates as two 8-bit timers (TMR3H and TMR3L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.7. TMR3RLL holds the reload value for TMR3L; TMR3RLH holds the reload value for TMR3H. The TR3 bit in TMR3CN handles the run control for TMR3H. TMR3L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 3 Clock Select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bit (T3XCLK in TMR3CN), as follows:

| ТЗМН | T3XCLK | TMR3H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T3ML | T3XCLK | TMR3L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF3H bit is set when TMR3H overflows from 0xFF to 0x00; the TF3L bit is set when TMR3L overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled, an interrupt is generated each time TMR3H overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TMR3L or TMR3H overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.7. Timer 3 8-Bit Mode Block Diagram

# SFR Definition 25.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4   | 3       | 2   | 1 | 0      |

|-------|------|------|--------|-----|---------|-----|---|--------|

| Name  | TF3H | TF3L | TF3LEN |     | T3SPLIT | TR3 |   | T3XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0   | 0       | 0   | 0 | 0      |

### SFR Address = 0x91; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | TF3H    | Timer 3 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|     |         | Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                               |  |  |  |

| 6   | TF3L    | Timer 3 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|     |         | Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                            |  |  |  |

| 5   | TF3LEN  | Timer 3 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|     |         | When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                       |  |  |  |

| 4   | Unused  | Unused. Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 3   | T3SPLIT | Timer 3 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|     |         | When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.<br>0: Timer 3 operates in 16-bit auto-reload mode.<br>1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                           |  |  |  |

| 2   | TR3     | Timer 3 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 2   |         | Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 1   | Unused  | Unused. Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 0   | T3XCLK  | Timer 3 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|     |         | This bit selects the external clock source for Timer 3. If Timer 3 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.<br>0: Timer 3 clock is the system clock divided by 12.<br>1: Timer 3 clock is the external clock divided by 8 (synchronized with SYSCLK). |  |  |  |

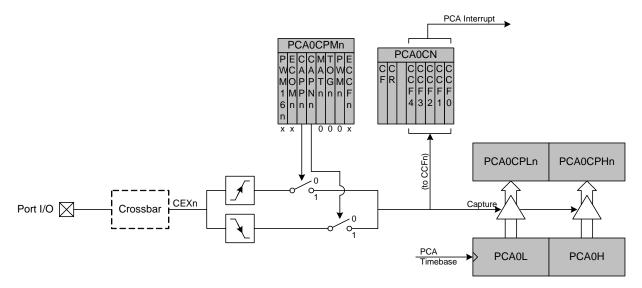

#### 26.3.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or fall-ing-edge caused the capture.

Figure 26.4. PCA Capture Mode Diagram

**Note:** The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.