Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                  |

| Program Memory Type        | OTP                                                             |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1.25К х 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 17x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t611-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. System Overview

C8051T610/1/2/3/4/5/6/7 devices are fully integrated, mixed-signal, system-on-a-chip MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- C8051F310 ISP Flash device is available for quick in-system code development

- 10-bit 500 ksps Single-ended ADC with analog multiplexer and integrated temperature sensor

- Precision calibrated 24.5 MHz internal oscillator

- 16 k or 8 k of on-chip Byte-Programmable EPROM—(512 bytes are reserved on 16k version)

- 1280 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, SPI, and Enhanced UART serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset and  $V_{DD}$  Monitor

- On-chip Voltage Comparators (2)

- 29/25/21 Port I/O

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051T610/1/2/3/4/5/6/7 devices are truly stand-alone, system-on-a-chip solutions. User software has complete control of all peripherals and may individually shut down any or all peripherals for power savings.

Code written for the C8051T610/1/2/3/4/5/6/7 family of processors will run on the C8051F310 Mixed-Signal ISP Flash microcontroller, providing a quick, cost-effective way to develop code without requiring special emulator circuitry. The C8051T610/1/2/3/4/5/6/7 processors include Silicon Laboratories' 2-Wire C2 Debug and Programming interface, which allows non-intrusive (uses no on-chip resources), full speed, incircuit debugging using the production MCU installed in the final application. This debug logic supports inspection of memory, viewing and modification of special function registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 1.8-3.6 V operation over the industrial temperature range (-45 to +85 °C). An internal LDO is used to supply the processor core voltage. The Port I/O and RST pins are tolerant of input signals up to 5 V. See Table 2.1 for ordering information. Block diagrams of the devices in the C8051T610/1/2/3/4/5/6/7 family are shown in Figure 1.1, Figure 1.2 and Figure 1.3.

# 5. QFN-28 Package Specifications

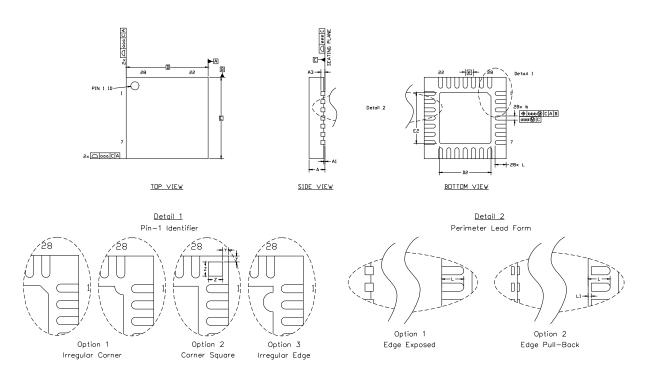

Figure 5.1. QFN-28 Package Drawing

| Dimension | Min       | Тур       | Max  |  | Dimension | Min  | Тур  | Ма  |

|-----------|-----------|-----------|------|--|-----------|------|------|-----|

| А         | 0.80      | 0.90      | 1.00 |  | L         | 0.35 | 0.55 | 0.6 |

| A1        | 0.00      | 0.02      | 0.05 |  | L1        | 0.00 | —    | 0.1 |

| A3        | 0.25 REF  |           |      |  | aaa       |      | 0.15 |     |

| b         | 0.18      | 0.23      | 0.30 |  | bbb       | 0.10 |      |     |

| D         |           | 5.00 BSC. |      |  | ddd       | 0.05 |      |     |

| D2        | 2.90      | 3.15      | 3.35 |  | eee       | 0.08 |      |     |

| е         | 0.50 BSC. |           |      |  | Z         |      | 0.44 |     |

| E         | 5.00 BSC. |           |      |  | Y         |      | 0.18 |     |

| E2        | 2.90      | 3.15      | 3.35 |  |           |      |      |     |

## Table 5.1. QFN-28 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, Z, Y, and L which are toleranced per supplier designation.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

#### 7.2. Electrical Characteristics

#### Table 7.2. Global Electrical Characteristics

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                                            | Conditions                                                           | Min        | Тур                        | Max                  | Units                |

|----------------------------------------------------------------------|----------------------------------------------------------------------|------------|----------------------------|----------------------|----------------------|

| Supply Voltage (Note 1)                                              | Regulator in Normal Mode<br>Regulator in Bypass Mode                 | 1.8<br>1.7 | 3.0<br>1.8                 | 3.6<br>1.9           | V<br>V               |

| Digital Supply Current with<br>CPU Active                            |                                                                      |            | 6.2<br>2.7<br>7<br>2.9     | 8.8<br>—<br>8.9<br>— | mA<br>mA<br>mA<br>mA |

| Digital Supply Current with<br>CPU Inactive (not accessing<br>EPROM) |                                                                      |            | 2.2<br>0.41<br>2.3<br>0.42 | 3<br>—<br>3.1<br>—   | mA<br>mA<br>mA<br>mA |

| Digital Supply Current<br>(shutdown)                                 | Oscillator not running (stop mode),<br>Internal Regulator Off        | —          | 4                          | _                    | μΑ                   |

|                                                                      | Oscillator not running (stop or suspend mode), Internal Regulator On | —          | 400                        | _                    | μΑ                   |

| Digital Supply RAM Data<br>Retention Voltage                         |                                                                      | —          | 1.5                        | _                    | V                    |

| Specified Operating<br>Temperature Range                             |                                                                      | -40        | _                          | +85                  | °C                   |

| SYSCLK (system clock<br>frequency)                                   | (Note 2)                                                             | 0          |                            | 25                   | MHz                  |

| Tsysl (SYSCLK low time)                                              |                                                                      | 18         | _                          | _                    | ns                   |

| Tsysh (SYSCLK high time)                                             |                                                                      | 18         |                            |                      | ns                   |

Analog performance is not guaranteed when V<sub>DD</sub> is belined.

SYSCLK must be at least 32 kHz to enable debugging.

#### Table 7.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameters          | Conditions                                   | Min                   | Тур                   | Max | Units |

|---------------------|----------------------------------------------|-----------------------|-----------------------|-----|-------|

| Output High Voltage | I <sub>OH</sub> = –3 mA, Port I/O push-pull  | V <sub>DD</sub> - 0.2 |                       |     | V     |

|                     | I <sub>OH</sub> = –10 μA, Port I/O push-pull | V <sub>DD</sub> - 0.1 | —                     | —   | V     |

|                     | I <sub>OH</sub> = –10 mA, Port I/O push-pull | —                     | V <sub>DD</sub> - 0.4 | —   | V     |

| Output Low Voltage  | I <sub>OL</sub> = 8.5 mA                     | —                     |                       | 0.4 | V     |

|                     | I <sub>OL</sub> = 10 μA                      | —                     | —                     | 0.1 | V     |

|                     | I <sub>OL</sub> = 25 mA                      | —                     | 0.6                   | —   | V     |

| Input High Voltage  |                                              | 0.7 x V <sub>DD</sub> | _                     | _   | V     |

| Input Low Voltage   |                                              | —                     | _                     | 0.6 | V     |

| Input Leakage       | Weak Pullup Off                              | -1                    | _                     | 1   | μA    |

| Current             | Weak Pullup On, V <sub>IN</sub> = 0 V        | —                     | 25                    | 50  | μA    |

#### Table 7.4. Reset Electrical Characteristics

-40 to +85 °C unless otherwise specified.

| Parameter                                             | Conditions                                                                            | Min                                        | Тур  | Max | Units           |

|-------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------|------|-----|-----------------|

| RST Output Low Voltage                                | I <sub>OL</sub> = 8.5 mA,<br>V <sub>DD</sub> = 1.8 V to 3.6 V                         | —                                          |      | 0.6 | V               |

| RST Input High Voltage                                |                                                                                       | $0.75 \mathrm{x} \mathrm{V}_{\mathrm{DD}}$ |      |     | V               |

| RST Input Low Voltage                                 |                                                                                       | —                                          |      | 0.6 | V <sub>DD</sub> |

| RST Input Pullup Current                              | RST = 0.0 V                                                                           | —                                          | 25   | 50  | μA              |

| V <sub>DD</sub> POR Ramp Time                         |                                                                                       | _                                          |      | 1   | ms              |

| V <sub>DD</sub> Monitor Threshold (V <sub>RST</sub> ) |                                                                                       | 1.7                                        | 1.75 | 1.8 | V               |

| Missing Clock Detector<br>Timeout                     | Time from last system clock rising edge to reset initiation                           | 500                                        | 625  | 750 | μs              |

| Reset Time Delay                                      | Delay between release of any<br>reset source and code<br>execution at location 0x0000 | _                                          | _    | 60  | μs              |

| Minimum RST Low Time to<br>Generate a System Reset    |                                                                                       | 15                                         |      | _   | μs              |

| V <sub>DD</sub> Monitor Turn-on Time                  | V <sub>DD</sub> = V <sub>RST</sub> - 0.1 V                                            |                                            | 50   |     | μs              |

| V <sub>DD</sub> Monitor Supply Current                |                                                                                       |                                            | 20   | 30  | μA              |

#### 8.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

#### SFR Definition 8.5. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit   | 7                                                             | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------------------------------------------------------------|-------------|---|---|---|---|---|---|--|

| Nam   | Name ADC0GTH[7:0]                                             |             |   |   |   |   |   |   |  |

| Туре  | 9                                                             | R/W         |   |   |   |   |   |   |  |

| Rese  | et 1                                                          | 1           | 1 | 1 | 1 | 1 | 1 | 1 |  |

| SFR A | Address = 0xC4                                                |             |   |   |   |   |   |   |  |

| Bit   | Name                                                          | me Function |   |   |   |   |   |   |  |

| 7:0   | 7:0 ADC0GTH[7:0] ADC0 Greater-Than Data Word High-Order Bits. |             |   |   |   |   |   |   |  |

# SFR Definition 8.6. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit                | 7            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|--------------|-----|---|---|---|---|---|---|

| Name               | ADC0GTL[7:0] |     |   |   |   |   |   |   |

| Туре               |              | R/W |   |   |   |   |   |   |

| Reset              | 1            | 1   | 1 | 1 | 1 | 1 | 1 | 1 |

| SFR Address = 0xC3 |              |     |   |   |   |   |   |   |

| E | Bit | Name         | Function                                    |

|---|-----|--------------|---------------------------------------------|

| 7 | :0  | ADC0GTL[7:0] | ADC0 Greater-Than Data Word Low-Order Bits. |

## SFR Definition 8.9. AMX0P: AMUX0 Positive Channel Select

| Bit  | 7              | 6           | 5                                                                          | 4                                                                                   | 3      |     | 2            | 1                    | 0 |  |

|------|----------------|-------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------|-----|--------------|----------------------|---|--|

| Nam  | e              |             |                                                                            |                                                                                     |        |     | AMX0P[4:0]   | ]                    |   |  |

| Туре | e R            | R           | R                                                                          |                                                                                     |        |     | R/W          | /W                   |   |  |

| Rese | <b>t</b> 0     | 0           | 0                                                                          | 1                                                                                   | 1      |     | 1            | 1                    | 1 |  |

|      | Address = 0xE  |             |                                                                            |                                                                                     |        |     |              |                      |   |  |

| Bit  | Name           |             |                                                                            |                                                                                     | Functi | ion |              |                      |   |  |

| 7:5  | Unused         | Linused Rea | d – 000b <sup>.</sup> V                                                    | Vrite – Don't                                                                       |        |     |              |                      |   |  |

| -    |                |             | Inused. Read = 000b; Write = Don't Care.<br>MUX0 Positive Input Selection. |                                                                                     |        |     |              |                      |   |  |

| 4.0  | / 10//01 [4:0] |             |                                                                            |                                                                                     |        |     |              |                      |   |  |

|      |                | Setting     |                                                                            | innel                                                                               |        |     | ilable on Pa | •                    |   |  |

|      |                | 00000:      | P1.(                                                                       | -                                                                                   |        |     | , · · ·      | 28, QFN-24           |   |  |

|      |                | 00001:      |                                                                            |                                                                                     |        |     | ,            | 28, QFN-24           |   |  |

|      |                | 00010:      | P1.2                                                                       |                                                                                     |        |     | ,            | 28, QFN-24           |   |  |

|      |                | 00011:      | P1.3                                                                       |                                                                                     |        |     |              | 28, QFN-24           |   |  |

|      |                | 00100:      | P1.4                                                                       |                                                                                     |        |     |              | 28, QFN-24           |   |  |

|      |                | 00101:      | P1.5                                                                       |                                                                                     |        |     | ,            | ·28, QFN-24          |   |  |

|      |                | 00110:      | P1.6                                                                       |                                                                                     |        |     | P-32, QFN-   |                      |   |  |

|      |                | 00111:      | P1.7                                                                       |                                                                                     |        |     | P-32, QFN-   |                      |   |  |

|      |                | 01000:      | P2.0                                                                       |                                                                                     |        |     |              | 28, QFN-24           |   |  |

|      |                | 01001:      | P2.′                                                                       |                                                                                     |        |     | ,            | P-32, QFN-28, QFN-24 |   |  |

|      |                | 01010:      |                                                                            | P2.2         LQFP-32, QFN-28, QFN-24           P2.3         LQFP-32, QFN-28, QFN-24 |        |     |              |                      |   |  |

|      |                | 01011:      |                                                                            |                                                                                     |        |     |              |                      |   |  |

|      |                | 01100:      | P2.4                                                                       |                                                                                     |        |     | ,            | 28, QFN-24           |   |  |

|      |                | 01101:      | P2.5                                                                       |                                                                                     |        |     | ,            | -28, QFN-24          |   |  |

|      |                | 01110:      | P2.6                                                                       |                                                                                     |        |     | P-32, QFN-   |                      |   |  |

|      |                | 01111:      | P2.7                                                                       |                                                                                     |        |     | P-32, QFN-   |                      |   |  |

|      |                | 10000:      | P3.0                                                                       |                                                                                     |        |     | -            | -28, QFN-24          |   |  |

|      |                | 10001:      | P3.′                                                                       |                                                                                     |        |     | P-32         |                      |   |  |

|      |                | 10010:      | P3.2                                                                       |                                                                                     |        |     | P-32         |                      |   |  |

|      |                | 10011:      | P3.3                                                                       |                                                                                     |        |     | P-32         |                      |   |  |

|      |                | 10100:      | P3.4                                                                       |                                                                                     | -      |     | P-32         |                      |   |  |

|      |                | 10101-11101 |                                                                            | nput Selecte                                                                        | ed     | N/A |              |                      |   |  |

|      |                | 11110:      |                                                                            | p Sensor                                                                            |        |     | -            | -28, QFN-24          |   |  |

|      |                | 11111:      | V <sub>DD</sub>                                                            | l i i i i i i i i i i i i i i i i i i i                                             |        | LQF | P-32, QFN-   | ·28, QFN-24          |   |  |

# SFR Definition 11.1. REG0CN: Voltage Regulator Control

| Bit   | 7          | 6                                                                                                                 | 5                                                                                                                                                     | 4                             | 3                                                | 2                                                   | 1              | 0                   |  |  |

|-------|------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------|-----------------------------------------------------|----------------|---------------------|--|--|

| Nam   | e STOPC    | F BYPASS                                                                                                          |                                                                                                                                                       |                               |                                                  |                                                     |                | MPCE                |  |  |

| Туре  | R/W        | R/W                                                                                                               | R/W                                                                                                                                                   | R/W                           | R/W                                              | R/W                                                 | R/W            | R/W                 |  |  |

| Rese  | et 0       | 0                                                                                                                 | 0                                                                                                                                                     | 0                             | 0                                                | 0                                                   | 0              | 0                   |  |  |

| SFR A | ddress = 0 | ×C7                                                                                                               |                                                                                                                                                       |                               |                                                  |                                                     |                |                     |  |  |

| Bit   | Name       |                                                                                                                   |                                                                                                                                                       |                               | Function                                         |                                                     |                |                     |  |  |

| 7     | STOPCF     | Stop Mode Co                                                                                                      | onfiguratio                                                                                                                                           | n.                            |                                                  |                                                     |                |                     |  |  |

|       |            | This bit config                                                                                                   | -                                                                                                                                                     |                               |                                                  |                                                     |                |                     |  |  |

|       |            | 0: Regulator is<br>device.                                                                                        | s still active                                                                                                                                        | in STOP mo                    | de. Any ena                                      | bled reset so                                       | burce will res | set the             |  |  |

|       |            | 1: Regulator is shut down in STOP mode. Only the $\overline{\text{RST}}$ pin or power cycle can reset the device. |                                                                                                                                                       |                               |                                                  |                                                     |                |                     |  |  |

| 6     | BYPASS     | Bypass Interr                                                                                                     | Bypass Internal Regulator.                                                                                                                            |                               |                                                  |                                                     |                |                     |  |  |

|       |            | This bit places                                                                                                   |                                                                                                                                                       |                               |                                                  | ng off the reg                                      | julator, and a | allowing the        |  |  |

|       |            | core to run directly from the V <sub>DD</sub> supply pin.<br>0: Normal Mode—Regulator is on.                      |                                                                                                                                                       |                               |                                                  |                                                     |                |                     |  |  |

|       |            |                                                                                                                   | •                                                                                                                                                     |                               | the microco                                      | ontroller core                                      | operates di    | rates directly from |  |  |

|       |            | the V <sub>DD</sub> supply                                                                                        |                                                                                                                                                       | de le ferrue                  |                                                  |                                                     | .leter ee the  |                     |  |  |

|       |            | IMPORTANT: voltage only.                                                                                          |                                                                                                                                                       |                               |                                                  |                                                     |                |                     |  |  |

|       |            | voltage is gre                                                                                                    | ater than th                                                                                                                                          | ne specifica                  | tions given                                      |                                                     |                |                     |  |  |

| 5:1   | Decerced   | may cause pe                                                                                                      |                                                                                                                                                       |                               | le device.                                       |                                                     |                |                     |  |  |

| _     | Reserved   |                                                                                                                   |                                                                                                                                                       |                               |                                                  |                                                     |                |                     |  |  |

| 0     | MPCE       | Memory Powe                                                                                                       |                                                                                                                                                       |                               | or at alower                                     | aveter alaa                                         | k fraguancia   | a (abaut            |  |  |

|       |            | This bit can he 2.0 MHz or les                                                                                    |                                                                                                                                                       |                               |                                                  |                                                     |                |                     |  |  |

|       |            | when informat                                                                                                     | ion is not be                                                                                                                                         | eing fetched                  | from the EP                                      | ROM memo                                            | ry.            |                     |  |  |

|       |            |                                                                                                                   | lormal Mode—Memory power controller disabled (EPROM memory is always on).<br>ow Power Mode—Memory power controller enabled (EPROM memory turns on/off |                               |                                                  |                                                     |                |                     |  |  |

|       |            | as needed).                                                                                                       |                                                                                                                                                       |                               | er controller enabled (EPROW memory turns on/oil |                                                     |                |                     |  |  |

|       |            | will turn                                                                                                         | quency chang                                                                                                                                          | ges from slow<br>20 clocks ma | (<2.0 MHz) t                                     | ory Power Cor<br>o fast (> 2.0 M<br>I" to ensure th | 1Hz), the EPR  | ROM power           |  |  |

### SFR Definition 16.2. IP: Interrupt Priority

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xB8; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | Unused. Read = 1, Write = Don't Care.                                                                                                                                                                                                                          |

| 6   | PSPI0  | <ul> <li>Serial Peripheral Interface (SPI0) Interrupt Priority Control.</li> <li>This bit sets the priority of the SPI0 interrupt.</li> <li>0: SPI0 interrupt set to low priority level.</li> <li>1: SPI0 interrupt set to high priority level.</li> </ul>     |

| 5   | PT2    | Timer 2 Interrupt Priority Control.This bit sets the priority of the Timer 2 interrupt.0: Timer 2 interrupt set to low priority level.1: Timer 2 interrupt set to high priority level.                                                                         |

| 4   | PS0    | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                                                                     |

| 3   | PT1    | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                                                         |

| 2   | PX1    | <ul> <li>External Interrupt 1 Priority Control.</li> <li>This bit sets the priority of the External Interrupt 1 interrupt.</li> <li>0: External Interrupt 1 set to low priority level.</li> <li>1: External Interrupt 1 set to high priority level.</li> </ul> |

| 1   | PT0    | Timer 0 Interrupt Priority Control.This bit sets the priority of the Timer 0 interrupt.0: Timer 0 interrupt set to low priority level.1: Timer 0 interrupt set to high priority level.                                                                         |

| 0   | PX0    | <ul> <li>External Interrupt 0 Priority Control.</li> <li>This bit sets the priority of the External Interrupt 0 interrupt.</li> <li>0: External Interrupt 0 set to low priority level.</li> <li>1: External Interrupt 0 set to high priority level.</li> </ul> |

### 16.3. External Interrupts INT0 and INT1

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "25.1. Timer 0 and Timer 1" on page 172) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | /INT0 Interrupt              |  |  |

|-----|-------|------------------------------|--|--|

| 1   | 0     | Active low, edge sensitive   |  |  |

| 1   | 1     | Active high, edge sensitive  |  |  |

| 0   | 0     | Active low, level sensitive  |  |  |

| 0   | 1     | Active high, level sensitive |  |  |

| IT1 | IN1PL | /INT1 Interrupt              |  |  |

|-----|-------|------------------------------|--|--|

| 1   | 0     | Active low, edge sensitive   |  |  |

| 1   | 1     | Active high, edge sensitive  |  |  |

| 0   | 0     | Active low, level sensitive  |  |  |

| 0   | 1     | Active high, level sensitive |  |  |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 16.5). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see Section "21.3. Priority Crossbar Decoder" on page 117 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

92

### 17.3. Program Memory CRC

A CRC engine is included on-chip which provides a means of verifying EPROM contents once the device has been programmed. The CRC engine is available for EPROM verification even if the device is fully read and write locked, allowing for verification of code contents at any time.

The CRC engine is operated through the C2 debug and programming interface, and performs 16-bit CRCs on individual 256-Byte blocks of program memory, or a 32-bit CRC the entire memory space. To prevent hacking and extrapolation of security-locked source code, the CRC engine will only allow CRCs to be performed on contiguous 256-Byte blocks beginning on 256-Byte boundaries (lowest 8-bits of address are 0x00). For example, the CRC engine can perform a CRC for locations 0x0400 through 0x04FF, but it cannot perform a CRC for locations 0x0401 through 0x0500, or on block sizes smaller or larger than 256 bytes.

#### 17.3.1. Performing 32-bit CRCs on Full EPROM Content

A 32-bit CRC on the entire EPROM space is initiated by writing to the CRC1 byte over the C2 interface. The CRC calculation begins at address 0x0000 and ends at the end of user EPROM space. The EPBusy bit in register C2ADD will be set during the CRC operation, and cleared once the operation is complete. The 32-bit results will be available in the CRC3-0 registers. CRC3 is the MSB, and CRC0 is the LSB. The polynomial used for the 32-bit CRC calculation is 0x04C11DB7.

**Note**: If a 16-bit CRC has been performed since the last device reset, a device reset should be initiated before performing a 32-bit CRC operation.

#### 17.3.2. Performing 16-bit CRCs on 256-Byte EPROM Blocks

A 16-bit CRC of individual 256-byte blocks of EPROM can be initiated by writing to the CRC0 byte over the C2 interface. The value written to CRC0 is the high byte of the beginning address for the CRC. For example, if CRC0 is written to 0x02, the CRC will be performed on the 256-bytes beginning at address 0x0200, and ending at address 0x2FF. The EPBusy bit in register C2ADD will be set during the CRC operation, and cleared once the operation is complete. The 16-bit results will be available in the CRC1-0 registers. CRC1 is the MSB, and CRC0 is the LSB. The polynomial for the 16-bit CRC calculation is 0x1021

### 19.2. Power-Fail Reset/V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 19.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is enabled after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is disabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be disabled after the reset.

**Important Note:** If the  $V_{DD}$  monitor is being turned on from a disabled state, it should be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. In some applications, this reset may be undesirable. If this is not desirable in the application, a delay should be introduced between enabling the monitor and selecting it as a reset source. The procedure for enabling the  $V_{DD}$  monitor and configuring it as a reset source from a disabled state is shown below:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = 1).

- 2. If necessary, wait for the V<sub>DD</sub> monitor to stabilize (see Table 7.4 for the V<sub>DD</sub> Monitor turn-on time).

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 19.2 for  $V_{DD}$  monitor timing; note that the power-on-reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 7.4 for complete electrical characteristics of the  $V_{DD}$  monitor.

## SFR Definition 20.4. OSCXCN: External Oscillator Control

| Bit   | 7 | 6           | 5     | 4 | 3 | 2         | 1   | 0 |

|-------|---|-------------|-------|---|---|-----------|-----|---|

| Name  |   | XOSCMD[2:0] |       |   |   | XFCN[2:0] |     |   |

| Туре  | R |             | R/W   |   |   |           | R/W |   |

| Reset | 0 | 0           | 0 0 0 |   |   | 0         | 0   | 0 |

#### SFR Address = 0xB1

| Bit | Name        |                    | Func                                 | tion            |  |  |  |  |  |

|-----|-------------|--------------------|--------------------------------------|-----------------|--|--|--|--|--|

| 7   | Unused      | Read =             | Read = 0b; Write = Don't Care        |                 |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa            | External Oscillator Mode Select.     |                 |  |  |  |  |  |

|     |             |                    | ternal Oscillator circuit off.       |                 |  |  |  |  |  |

|     |             |                    | ternal CMOS Clock Mode.              |                 |  |  |  |  |  |

|     |             |                    | ternal CMOS Clock Mode with divi     |                 |  |  |  |  |  |

|     |             |                    | C Oscillator Mode with divide by 2 s | •               |  |  |  |  |  |

|     |             | 101: Ca<br>11x: Re | pacitor Oscillator Mode with divide  | by 2 stage.     |  |  |  |  |  |

|     |             |                    |                                      |                 |  |  |  |  |  |

| 3   | Unused      | Read =             | 0b; Write = Don't Care               |                 |  |  |  |  |  |

| 2:0 | XFCN[2:0]   | Externa            | al Oscillator Frequency Control I    | Bits.           |  |  |  |  |  |

|     |             |                    | ording to the desired frequency rar  | -               |  |  |  |  |  |

|     |             | Set acc            | ording to the desired K Factor for ( | C mode.         |  |  |  |  |  |

|     |             | XFCN               | RC Mode                              | C Mode          |  |  |  |  |  |

|     |             | 000                | f ≤ 25 kHz                           | K Factor = 0.87 |  |  |  |  |  |

|     |             | 001                | 25 kHz < f ≤ 50 kHz                  | K Factor = 2.6  |  |  |  |  |  |

|     |             | 010                | 50 kHz < f ≤ 100 kHz                 | K Factor = 7.7  |  |  |  |  |  |

|     |             | 011                | 100 kHz < f ≤ 200 kHz                | K Factor = 22   |  |  |  |  |  |

|     |             | 100                | 200 kHz < f ≤ 400 kHz                | K Factor = 65   |  |  |  |  |  |

|     |             | 101                | 400 kHz < f ≤ 800 kHz                | K Factor = 180  |  |  |  |  |  |

|     |             | 110                | 800 kHz < f ≤ 1.6 MHz                | K Factor = 664  |  |  |  |  |  |

|     |             | 111                | 1.6 MHz < f ≤ 3.2 MHz                | K Factor = 1590 |  |  |  |  |  |

## SFR Definition 21.6. P0SKIP: Port 0 Skip

| Bit   | 7           | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------|-----|---|---|---|---|---|---|--|

| Name  | P0SKIP[7:0] |     |   |   |   |   |   |   |  |

| Туре  |             | R/W |   |   |   |   |   |   |  |

| Reset | 0           | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xD4

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                       |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0SKIP[7:0] | Port 0 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                              |

|     |             | <ul><li>These bits select Port 0 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li><li>0: Corresponding P0.n pin is not skipped by the Crossbar.</li><li>1: Corresponding P0.n pin is skipped by the Crossbar.</li></ul> |

#### SFR Definition 21.7. P1: Port 1

| Bit   | 7       | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|-----|---|---|---|---|---|---|

| Name  | P1[7:0] |     |   |   |   |   |   |   |

| Туре  |         | R/W |   |   |   |   |   |   |

| Reset | 1       | 1   | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0x90; Bit-Addressable

| Bit   | Name                                                                               | Description                                                                                                                                   | Write                                                                         | Read                                                                    |  |  |  |  |

|-------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| 7:0   | P1[7:0]                                                                            | <b>Port 1 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P1.n Port pin is logic<br>LOW.<br>1: P1.n Port pin is logic<br>HIGH. |  |  |  |  |

| Note: | Note: P1.6 and P1.7 are not connected to external pins on the C8051T616/7 devices. |                                                                                                                                               |                                                                               |                                                                         |  |  |  |  |

# SFR Definition 22.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

#### SFR Address = 0xC0; Bit-Addressable

| Bit | Name    | Description                                                                                                                                                                                                      | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                                     | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                               | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                                | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                                 | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                                    | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                             | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                               | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | <b>SMBus Interrupt Flag.</b><br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | 0: Clear interrupt, and initi-<br>ate next state machine<br>event.<br>1: Force interrupt.                                                                                            |

# SFR Definition 25.1. CKCON: Clock Control

| Bit   | 7    | 6    | 5    | 4    | 3   | 2   | 1        | 0 |

|-------|------|------|------|------|-----|-----|----------|---|

| Name  | ТЗМН | T3ML | T2MH | T2ML | T1M | ТОМ | SCA[1:0] |   |

| Туре  | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W      |   |

| Reset | 0    | 0    | 0    | 0    | 0   | 0   | 0        | 0 |

#### SFR Address = 0x8E

| Bit | Name     | Function                                                                                                                                                                                                                                                                          |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ТЗМН     | Timer 3 High Byte Clock Select.                                                                                                                                                                                                                                                   |

|     |          | Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).<br>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.                                                                                                                    |

|     |          | 1: Timer 3 high byte uses the system clock.                                                                                                                                                                                                                                       |

| 6   | T3ML     | Timer 3 Low Byte Clock Select.                                                                                                                                                                                                                                                    |

|     |          | Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.                                                                                                                                                             |

|     |          | <ul><li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li><li>1: Timer 3 low byte uses the system clock.</li></ul>                                                                                                                                      |

| 5   | T2MH     | Timer 2 High Byte Clock Select.                                                                                                                                                                                                                                                   |

|     |          | Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).<br>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.<br>1: Timer 2 high byte uses the system clock.                                                                     |

| 4   | T2ML     | Timer 2 Low Byte Clock Select.                                                                                                                                                                                                                                                    |

|     |          | Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.<br>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.<br>1: Timer 2 low byte uses the system clock. |

| 3   | T1       | Timer 1 Clock Select.                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                             |

| 2   | Т0       | Timer 0 Clock Select.                                                                                                                                                                                                                                                             |

|     |          | Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.<br>0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].<br>1: Counter/Timer 0 uses the system clock.                                                                             |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.                                                                                                                                                                                                                                                          |

|     |          | These bits control the Timer 0/1 Clock Prescaler:                                                                                                                                                                                                                                 |

|     |          | 00: System clock divided by 12<br>01: System clock divided by 4                                                                                                                                                                                                                   |

|     |          | 10: System clock divided by 48                                                                                                                                                                                                                                                    |

|     |          | 11: External clock divided by 8 (synchronized with the system clock)                                                                                                                                                                                                              |

# SFR Definition 25.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4   | 3       | 2   | 1 | 0      |

|-------|------|------|--------|-----|---------|-----|---|--------|

| Name  | TF3H | TF3L | TF3LEN |     | T3SPLIT | TR3 |   | T3XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0   | 0       | 0   | 0 | 0      |

#### SFR Address = 0x91; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF3H    | Timer 3 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                               |

| 6   | TF3L    | Timer 3 Low Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |         | Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                            |

| 5   | TF3LEN  | Timer 3 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |         | When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows.                                                                                                                                                                                                                                                                                                       |

| 4   | Unused  | Unused. Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3   | T3SPLIT | Timer 3 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |         | When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.<br>0: Timer 3 operates in 16-bit auto-reload mode.<br>1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                           |

| 2   | TR3     | Timer 3 Run Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2   |         | Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                       |

| 1   | Unused  | Unused. Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | T3XCLK  | Timer 3 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |         | This bit selects the external clock source for Timer 3. If Timer 3 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.<br>0: Timer 3 clock is the system clock divided by 12.<br>1: Timer 3 clock is the external clock divided by 8 (synchronized with SYSCLK). |

# SFR Definition 25.17. TMR3H Timer 3 High Byte

| Bit   | 7            | 6        | 5 | 4    | 3      | 2 | 1 | 0 |

|-------|--------------|----------|---|------|--------|---|---|---|

| Nam   | e            | ·        |   | TMR3 | H[7:0] |   |   |   |

| Туре  | )            | R/W      |   |      |        |   |   |   |

| Rese  | <b>t</b> 0   | 0        | 0 | 0    | 0      | 0 | 0 | 0 |

| SFR A | ddress = 0x9 | 5        |   |      |        |   |   |   |

| Bit   | Name         | Function |   |      |        |   |   |   |

| Bit | Name       | Function                                                                                                                                            |  |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:0 | TMR3H[7:0] | Timer 3 Low Byte.                                                                                                                                   |  |

|     |            | In 16-bit mode, the TMR3H register contains the high byte of the 16-bit Timer 3. In 8-<br>bit mode, TMR3H contains the 8-bit high byte timer value. |  |

# SFR Definition 26.3. PCA0CPMn: PCA Capture/Compare Mode

| Bit                                                                                 | 7           | 6                                                                                                                                                                                                                                                                                                                 | 5              | 4              | 3            | 2            | 1             | 0     |