Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EPROM Size                 | -                                                                                |

| RAM Size                   | 4K x 8                                                                           |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x12b; D/A 1x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep32gs502t-e-mx |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

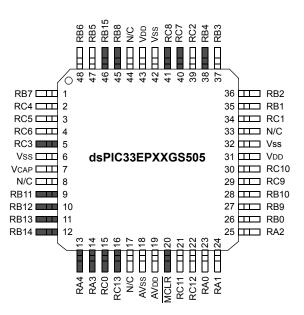

### Pin Diagrams (Continued)

| Pin | Pin Function                   | Pin | Pin Function                                       |

|-----|--------------------------------|-----|----------------------------------------------------|

| 1   | PGEC1/AN21/SDA1/RP39/RB7       | 25  | AN2/PGA1P3/PGA2P2/CMP1C/CMP2A/RA2                  |

| 2   | AN1ALT/RP52/RC4                | 26  | AN3/PGA2P3/CMP1D/CMP2B/ <b>RP32</b> /RB0           |

| 3   | AN0ALT/RP53/RC5                | 27  | AN4/CMP2C/CMP3A/ISRC4/ <b>RP41</b> /RB9            |

| 4   | AN17/ <b>RP54</b> /RC6         | 28  | AN5/CMP2D/CMP3B/ISRC3/RP42/RB10                    |

| 5   | RP51/RC3                       | 29  | AN11/PGA1N3/ <b>RP57</b> /RC9                      |

| 6   | Vss                            | 30  | AN10/PGA1P4/EXTREF2/RP58/RC10                      |

| 7   | VCAP                           | 31  | VDD                                                |

| 8   | N/C                            | 32  | Vss                                                |

| 9   | TMS/PWM3H/RP43/RB11            | 33  | N/C                                                |

| 10  | TCK/PWM3L/ <b>RP44</b> /RB12   | 34  | AN8/PGA2P4/CMP4C/ <b>RP49</b> /RC1                 |

| 11  | PWM2H/ <b>RP45</b> /RB13       | 35  | OSC1/CLKI/AN6/CMP3C/CMP4A/ISRC2/RP33/RB1           |

| 12  | PWM2L/ <b>RP46</b> /RB14       | 36  | OSC2/CLKO/AN7/PGA1N2/CMP3D/CMP4B/ <b>RP34</b> /RB2 |

| 13  | PWM1H/RA4                      | 37  | PGED2/AN18/DACOUT1/INT0/RP35/RB3                   |

| 14  | PWM1L/RA3                      | 38  | PGEC2/ADTRG31/ <b>RP36</b> /RB4                    |

| 15  | FLT12/ <b>RP48</b> /RC0        | 39  | AN9/CMP4D/EXTREF1/RP50 /RC2                        |

| 16  | FLT11/ <b>RP61</b> /RC13       | 40  | ASDA1/RP55/RC7                                     |

| 17  | N/C                            | 41  | ASCL1/RP56/RC8                                     |

| 18  | AVss                           | 42  | Vss                                                |

| 19  | AVDD                           | 43  | VDD                                                |

| 20  | MCLR                           | 44  | N/C                                                |

| 21  | AN12/ISRC1/ <b>RP59</b> /RC11  | 45  | PGED3/SDA2/ <b>RP40</b> /RB8                       |

| 22  | AN14/PGA2N3/ <b>RP60</b> /RC12 | 46  | PGEC3/SCL2/RP47/RB15                               |

| 23  | AN0/PGA1P1/CMP1A/RA0           | 47  | TDO/AN19/PGA2N2/ <b>RP37</b> /RB5                  |

| 24  | AN1/PGA1P2/PGA2P1/CMP1B/RA1    | 48  | PGED1/TDI/AN20/SCL1/RP38/RB6                       |

Legend: Shaded pins are up to 5 VDC tolerant.

RPn represents remappable peripheral functions. See Table 10-1 and Table 10-2 for the complete list of remappable sources.

#### 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXGS50X family ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- · 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

#### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- · 32-bit signed/16-bit signed divide

- · 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.9 DSP Engine

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are, ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed, unsigned or mixed-sign DSP multiply (USx)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

| Instruction | Algebraic<br>Operation  | ACC<br>Write-Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \cdot y$         | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

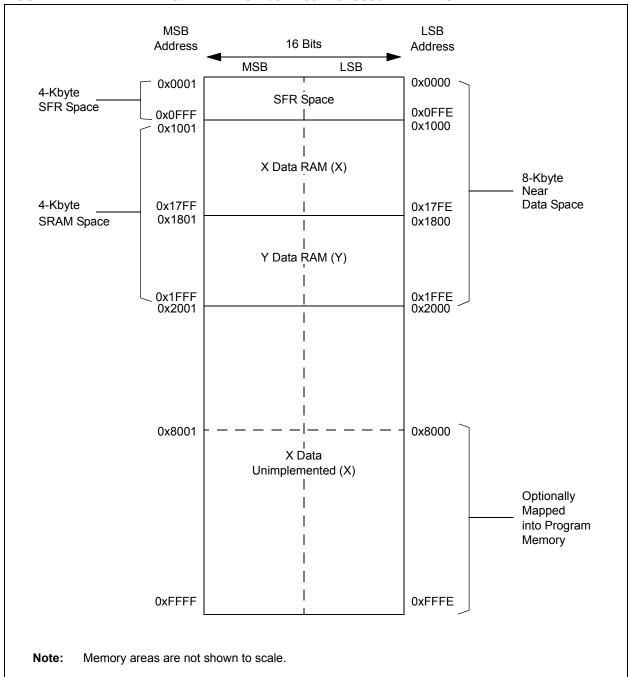

FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32GS50X DEVICES

| _                |

|------------------|

| Υ,               |

| Ų                |

| c                |

| Ē                |

| Ç                |

| <u> </u>         |

| N                |

|                  |

| DS/UU0512/C-page |

| ö                |

| ā                |

| ă                |

|                  |

| 49               |

| ď                |

|                  |

|                  |

| <b>TABLE 4-7:</b> | PWM REGISTER MAP     |

|-------------------|----------------------|

| IADLL 4-1.        | EVVIVINEGISTEN IVIAE |

| SFR<br>Name | Addr.                                                            | Bit 15   | Bit 14                                                                                   | Bit 13 | Bit 12 | Bit 11  | Bit 10  | Bit 9         | Bit 8          | Bit 7         | Bit 6           | Bit 5         | Bit 4    | Bit 3   | Bit 2   | Bit 1       | Bit 0   | All<br>Resets |

|-------------|------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------|--------|--------|---------|---------|---------------|----------------|---------------|-----------------|---------------|----------|---------|---------|-------------|---------|---------------|

| PTCON       | 0C00                                                             | PTEN     | _                                                                                        | PTSIDL | SESTAT | SEIEN   | EIPU    | SYNCPOL       | SYNCOEN        | SYNCEN        | SYNCSRC2        | SYNCSRC1      | SYNCSRC0 | SEVTPS3 | SEVTPS2 | SEVTPS1     | SEVTPS0 | 0000          |

| PTCON2      | 0C02                                                             | -        | _                                                                                        | 1      | _      | _       | _       | ı             | _              | -             | ı               | ı             | -        | ı       | F       | PCLKDIV<2:0 | >       | 0000          |

| PTPER       | 0C04 PWMx Primary Master Time Base Period Register (PTPER<15:0>) |          |                                                                                          |        |        |         |         |               |                |               | FFF8            |               |          |         |         |             |         |               |

| SEVTCMP     | 0C06                                                             |          | PWMx Special Event Compare Register (SEVTCMP12:0>) — — — — — — — — — — — — — — — — — — — |        |        |         |         |               |                |               | 0000            |               |          |         |         |             |         |               |

| MDC         | 0C0A                                                             |          |                                                                                          |        |        |         |         | F             | WMx Master     | Duty Cycle Ro | egister (MDC<   | :15:0>)       |          |         |         |             |         | 0000          |

| STCON       | 0C0E                                                             | -        | _                                                                                        | _      | SESTAT | SEIEN   | EIPU    | SYNCPOL       | SYNCOEN        | SYNCEN        | SYNCSRC2        | SYNCSRC1      | SYNCSRC0 | SEVTPS3 | SEVTPS2 | SEVTPS1     | SEVTPS0 | 0000          |

| STCON2      | 0C10                                                             | _        | _                                                                                        |        |        | _       | _       | ı             | _              | -             | -               | ı             | _        | I       | F       | PCLKDIV<2:0 | >       | 0000          |

| STPER       | 0C12                                                             |          |                                                                                          |        |        |         |         | PWMx Sec      | ondary Master  | r Time Base F | Period Register | r (STPER<15:0 | )>)      |         |         |             |         | FFF8          |

| SSEVTCMP    | 0C14                                                             |          |                                                                                          |        | F      | PWMx Se | condary | Special Event | Compare Rec    | gister (SSEVT | CMP<12:0>)      |               |          |         | _       | _           | _       | 0000          |

| CHOP        | 0C1A                                                             | CHPCLKEN | CHPCLKEN — — — — CHOPCLK6 CHOPCLK5 CHOPCLK4 CHOPCLK3 CHOPCLK2 CHOPCLK1 CHOPCLK0 — — — 0  |        |        |         |         |               |                | 0000          |                 |               |          |         |         |             |         |               |

| PWMKEY      | 0C1E                                                             |          |                                                                                          |        |        | •       |         | PWMx F        | Protection Loc | k/Unlock Key  | Register (PWI   | MKEY<15:0>)   |          | •       |         |             |         | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-8: PWM GENERATOR 1 REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15  | Bit 14                                                | Bit 13  | Bit 12  | Bit 11    | Bit 10           | Bit 9           | Bit 8          | Bit 7         | Bit 6         | Bit 5        | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|-------------------------------------------------------|---------|---------|-----------|------------------|-----------------|----------------|---------------|---------------|--------------|----------|----------|----------|----------|----------|---------------|

| PWMCON1     | 0C20  | FLTSTAT | CLSTAT                                                | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN           | ITB             | MDCS           | DTC1          | DTC0          | _            | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON1      | 0C22  | PENH    | PENL                                                  | POLH    | POLL    | PMOD1     | PMOD0            | OVRENH          | OVRENL         | OVRDAT1       | OVRDAT0       | FLTDAT1      | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON1     | 0C24  | IFLTMOD | CLSRC4                                                | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0           | CLPOL           | CLMOD          | FLTSRC4       | FLTSRC3       | FLTSRC2      | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC1        | 0C26  |         | PWM1 Generator Duty Cycle Register (PDC1<15:0>)       |         |         |           |                  |                 |                |               |               |              |          | 0000     |          |          |          |               |

| PHASE1      | 0C28  |         |                                                       |         |         |           | PWM1 Primar      | y Phase-Shift o | or Independent | Time Base     | Period Regis  | ster (PHASE1 | <15:0>)  |          |          |          |          | 0000          |

| DTR1        | 0C2A  | 1       | -                                                     |         |         |           |                  |                 | PWM1 [         | Dead-Time R   | Register (DTF | R1<13:0>)    |          |          |          |          |          | 0000          |

| ALTDTR1     | 0C2C  | -       | — — PWM1 Alternate Dead-Time Register (ALTDTR1<13:0>) |         |         |           |                  |                 |                |               |               |              | 0000     |          |          |          |          |               |

| SDC1        | 0C2E  |         |                                                       |         |         |           |                  | PWM1 Sec        | ondary Duty C  | ycle Registe  | er (SDC1<15   | :0>)         |          |          |          |          |          | 0000          |

| SPHASE1     | 0C30  |         |                                                       |         |         |           |                  | PWM1 Secon      | dary Phase-Sl  | nift Register | (SPHASE1<     | 15:0>)       |          |          |          |          |          | 0000          |

| TRIG1       | 0C32  |         |                                                       |         |         | PWM1 P    | rimary Trigger ( | Compare Value   | Register (TR   | GCMP<12:0     | <b>)&gt;)</b> |              |          |          | _        | _        | _        | 0000          |

| TRGCON1     | 0C34  | TRGDIV3 | TRGDIV2                                               | TRGDIV1 | TRGDIV0 | 1         | 1                | _               | _              | DTM           | _             | TRGSTRT5     | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG1      | 0C36  |         |                                                       |         |         | PWM1 Sec  | ondary Trigger   | Compare Valu    | e Register (ST | RGCMP<12      | 2:0>)         |              |          |          | _        | _        | _        | 0000          |

| PWMCAP1     | 0C38  |         |                                                       |         |         | PWM1      | Primary Time E   | Base Capture F  | Register (PWM  | CAP<12:0>     | )             |              |          |          | _        | _        | _        | 0000          |

| LEBCON1     | 0C3A  | PHR     | PHF                                                   | PLR     | PLF     | FLTLEBEN  | CLLEBEN          | _               | _              | _             | _             | BCH          | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY1     | 0C3C  | _       | _                                                     | _       | _       |           |                  | PWM1 Lea        | ding-Edge Bla  | nking Delay   | Register (LE  | B<8:0>)      |          |          | _        | _        | _        | 0000          |

| AUXCON1     | 0C3E  | HRPDIS  | HRDDIS                                                | _       | _       | BLANKSEL3 | BLANKSEL2        | BLANKSEL1       | BLANKSEL0      | _             | _             | CHOPSEL3     | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

dsPIC33EPXXGS50X FAMILY

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

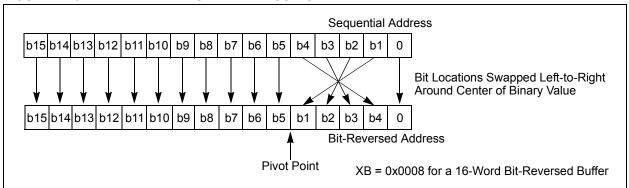

FIGURE 4-13: BIT-REVERSED ADDRESSING EXAMPLE

TABLE 4-39: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma      | al Addre | ss      |    |    | Bit-Rev    | ersed Ac | ldress  |

|----|----|------------|----------|---------|----|----|------------|----------|---------|

| А3 | A2 | <b>A</b> 1 | A0       | Decimal | А3 | A2 | <b>A</b> 1 | A0       | Decimal |

| 0  | 0  | 0          | 0        | 0       | 0  | 0  | 0          | 0        | 0       |

| 0  | 0  | 0          | 1        | 1       | 1  | 0  | 0          | 0        | 8       |

| 0  | 0  | 1          | 0        | 2       | 0  | 1  | 0          | 0        | 4       |

| 0  | 0  | 1          | 1        | 3       | 1  | 1  | 0          | 0        | 12      |

| 0  | 1  | 0          | 0        | 4       | 0  | 0  | 1          | 0        | 2       |

| 0  | 1  | 0          | 1        | 5       | 1  | 0  | 1          | 0        | 10      |

| 0  | 1  | 1          | 0        | 6       | 0  | 1  | 1          | 0        | 6       |

| 0  | 1  | 1          | 1        | 7       | 1  | 1  | 1          | 0        | 14      |

| 1  | 0  | 0          | 0        | 8       | 0  | 0  | 0          | 1        | 1       |

| 1  | 0  | 0          | 1        | 9       | 1  | 0  | 0          | 1        | 9       |

| 1  | 0  | 1          | 0        | 10      | 0  | 1  | 0          | 1        | 5       |

| 1  | 0  | 1          | 1        | 11      | 1  | 1  | 0          | 1        | 13      |

| 1  | 1  | 0          | 0        | 12      | 0  | 0  | 1          | 1        | 3       |

| 1  | 1  | 0          | 1        | 13      | 1  | 0  | 1          | 1        | 11      |

| 1  | 1  | 1          | 0        | 14      | 0  | 1  | 1          | 1        | 7       |

| 1  | 1  | 1          | 1        | 15      | 1  | 1  | 1          | 1        | 15      |

#### 5.2 RTSP Operation

The dsPIC33EPXXGS50X family Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a single page (8 rows or 512 instructions) of memory at a time and to program one row at a time. It is possible to program two instructions at a time as well.

The page erase and single row write blocks are edgealigned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively. Figure 26-14 in **Section 26.0 "Electrical Characteristics"** lists the typical erase and programming times.

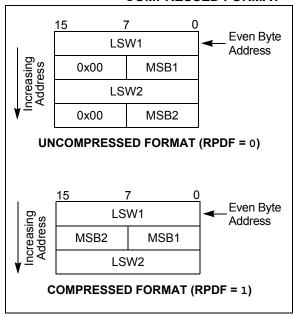

Row programming is performed by loading 192 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADR register. Once the write has been initiated, the device will automatically load the write latches and increment the NVMSRCADR and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

The basic sequence for RTSP word programming is to use the <code>TBLWTL</code> and <code>TBLWTH</code> instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. Refer to Figure 4-1 through Figure 4-4 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

All erase and program operations may optionally use the NVM interrupt to signal the successful completion of the operation. For example, when performing Flash write operations on the Inactive Partition in Dual Partition mode, where the CPU remains running, it is necessary to wait for the NVM interrupt before programming the next block of Flash program memory.

FIGURE 5-2: UNCOMPRESSED/ COMPRESSED FORMAT

### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

# 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000000, 0x000004, 0x000008, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

### REGISTER 9-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| _      | _   | _   | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD |

| bit 15 |     |     |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 **PWM5MD:** PWM5 Module Disable bit

1 = PWM5 module is disabled 0 = PWM5 module is enabled

bit 11 **PWM4MD:** PWM4 Module Disable bit

1 = PWM4 module is disabled 0 = PWM4 module is enabled

bit 10 **PWM3MD:** PWM3 Module Disable bit

1 = PWM3 module is disabled 0 = PWM3 module is enabled

bit 9 **PWM2MD:** PWM2 Module Disable bit

1 = PWM2 module is disabled 0 = PWM2 module is enabled

bit 8 **PWM1MD:** PWM1 Module Disable bit

1 = PWM1 module is disabled0 = PWM1 module is enabled

bit 7-0 **Unimplemented:** Read as '0'

#### 10.7 Peripheral Pin Select Registers

#### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| INT1R<7:0> |       |       |       |       |       |       |       |  |  |  |

| bit 15     |       |       |       |       |       |       | bit 8 |  |  |  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 INT1R<7:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits

10110101 = Input tied to RP181

10110100 = Input tied to RP180

•

•

00000001 = Input tied to RP1 00000000 = Input tied to Vss

bit 7-0 **Unimplemented:** Read as '0'

#### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | INT2F | R<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 INT2R<7:0>: Assign External Interrupt 2 (INT2) to the Corresponding RPn Pin bits

10110101 = Input tied to RP181 10110100 = Input tied to RP180

•

00000001 = Input tied to RP1 00000000 = Input tied to Vss

#### REGISTER 10-5: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| IC2R7  | IC2R6 | IC2R5 | IC2R4 | IC2R3 | IC2R2 | IC2R1 | IC2R0 |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IC1R7 | IC1R6 | IC1R5 | IC1R4 | IC1R3 | IC1R2 | IC1R1 | IC1R0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 IC2R<7:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits

> 10110101 = Input tied to RP181 10110100 = Input tied to RP180

00000001 = Input tied to RP1

00000000 = Input tied to Vss

bit 7-0 IC1R<7:0>: Assign Input Capture 1 (IC1) to the Corresponding RPn Pin bits

10110101 = Input tied to RP181

10110100 = Input tied to RP180

00000001 = Input tied to RP1

00000000 = Input tied to Vss

#### REGISTER 15-20: IOCONx: PWMx I/O CONTROL REGISTER (x = 1 to 5) (CONTINUED)

bit 3-2 CLDAT<1:0>: State for PWMxH and PWMxL Pins if CLMOD is Enabled bits<sup>(2)</sup>

IFLTMOD (FCLCONx<15>) = 0: Normal Fault Mode:

If current limit is active, then CLDAT1 provides the state for the PWMxH pin. If current limit is active, then CLDAT0 provides the state for the PWMxL pin.

IFLTMOD (FCLCONx<15>) = 1: Independent Fault Mode:

CLDAT<1:0> bits are ignored.

bit 1 **SWAP:** SWAP PWMxH and PWMxL Pins bit

- 1 = PWMxH output signal is connected to the PWMxL pins; PWMxL output signal is connected to the PWMxH pins

- 0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 **OSYNC:** Output Override Synchronization bit

- 1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx time base

- 0 = Output overrides via the OVRDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: State represents the active/inactive state of the PWMx depending on the POLH and POLL bits settings.

#### REGISTER 15-21: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER (x = 1 to 5)

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | TRGCM | P<12:5> |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|-------|-------|-------------|-------|-------|-----|-----|-------|

|       |       | TRGCMP<4:0> | _     | _     | _   |     |       |

| bit 7 |       |             |       |       |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **TRGCMP<12:0>:** Trigger Compare Value bits

When the primary PWMx functions in the local time base, this register contains the compare values

that can trigger the ADC module.

bit 2-0 **Unimplemented:** Read as '0'

#### 16.3 SPI Control Registers

#### REGISTER 16-1: SPIXSTAT: SPIX STATUS AND CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | U-0 | U-0 | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|-----|-----|---------|---------|---------|

| SPIEN  | _   | SPISIDL | _   | _   | SPIBEC2 | SPIBEC1 | SPIBEC0 |

| bit 15 |     |         |     |     |         |         | bit 8   |

| R/W-0 | R/C-0, HS | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R-0, HS, HC | R-0, HS, HC |

|-------|-----------|--------|--------|--------|--------|-------------|-------------|

| SRMPT | SPIROV    | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF      | SPIRBF      |

| bit 7 |           |        |        |        |        |             | bit 0       |

| Legend:           | C = Clearable bit | U = Unimplemented bit, read | as '0'                      |

|-------------------|-------------------|-----------------------------|-----------------------------|

| R = Readable bit  | W = Writable bit  | HS = Hardware Settable bit  | HC = Hardware Clearable bit |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown          |

bit 15 SPIEN: SPIx Enable bit

1 = Enables the module and configures SCKx, SDOx, SDIx and  $\overline{SSx}$  as serial port pins

0 = Disables the module

bit 14 Unimplemented: Read as '0'

bit 13 SPISIDL: SPIx Stop in Idle Mode bit

1 = Discontinues the module operation when device enters Idle mode

0 = Continues the module operation in Idle mode

bit 12-11 **Unimplemented:** Read as '0'

bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode)

Master Mode:

Number of SPIx transfers that are pending.

Slave Mode:

Number of SPIx transfers that are unread.

bit 7 SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode)

1 = SPIx Shift register is empty and ready to send or receive the data

0 = SPIx Shift register is not empty

bit 6 SPIROV: SPIx Receive Overflow Flag bit

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register

0 = No overflow has occurred

bit 5 SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)

1 = RX FIFO is empty

0 = RX FIFO is not empty

bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

110 = Interrupt when the last bit is shifted into SPIxSR, and as a result, the TX FIFO is empty

101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

100 = Interrupt when one data is shifted into the SPIxSR, and as a result, the TX FIFO has one open memory location

011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)

010 = Interrupt when the SPIx receive buffer is 3/4 or more full

001 = Interrupt when data is available in the receive buffer (SRMPT bit is set)

000 = Interrupt when the last data in the receive buffer is read, and as a result, the buffer is empty (SRXMPT bit is set)

#### REGISTER 16-2: SPIxCON1: SPIx CONTROL REGISTER 1 (CONTINUED)

#### REGISTER 19-5: ADCON3L: ADC CONTROL REGISTER 3 LOW

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R-0, HSC | R/W-0   | R-0, HSC |

|---------|---------|---------|---------|---------|----------|---------|----------|

| REFSEL2 | REFSEL1 | REFSEL0 | SUSPEND | SUSPCIE | SUSPRDY  | SHRSAMP | CNVRTCH  |

| bit 15  |         |         |         |         |          |         | bit 8    |

| R/W-0   | R-0, HSC | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|---------|----------|-----------|-----------|-----------|-----------|-----------|-----------|

| SWLCTRG | SWCTRG   | CNVCHSEL5 | CNVCHSEL4 | CNVCHSEL3 | CNVCHSEL2 | CNVCHSEL1 | CNVCHSEL0 |

| bit 7   |          |           |           |           |           |           | bit 0     |

**Legend:** U = Unimplemented bit, read as '0'

R = Readable bit W = Writable bit HSC = Hardware Settable/Clearable bit

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-13 **REFSEL<2:0>:** ADC Reference Voltage Selection bits

| Value | VREFH | VREFL |

|-------|-------|-------|

| 000   | AVDD  | AVss  |

001-111 = Unimplemented: Do not use

bit 12 SUSPEND: All ADC Cores Triggers Disable bit

1 = All new trigger events for all ADC cores are disabled

0 = All ADC cores can be triggered

bit 11 SUSPCIE: Suspend All ADC Cores Common Interrupt Enable bit

1 = Common interrupt will be generated when ADC core triggers are suspended (SUSPEND bit = 1) and all previous conversions are finished (SUSPRDY bit becomes set)

0 = Common interrupt is not generated for suspend ADC cores event

bit 10 SUSPRDY: All ADC Cores Suspended Flag bit

1 = All ADC cores are suspended (SUSPEND bit = 1) and have no conversions in progress

0 = ADC cores have previous conversions in progress

bit 9 SHRSAMP: Shared ADC Core Sampling Direct Control bit

This bit should be used with the individual channel conversion trigger controlled by the CNVRTCH bit. It connects an analog input, specified by the CNVCHSEL<5:0> bits, to the shared ADC core and allows extending the sampling time. This bit is not controlled by hardware and must be cleared before the conversion starts (setting CNVRTCH to '1').

- 1 = Shared ADC core samples an analog input specified by the CNVCHSEL<5:0> bits

- 0 = Sampling is controlled by the shared ADC core hardware

bit 8 CNVRTCH: Software Individual Channel Conversion Trigger bit

- 1 = Single trigger is generated for an analog input specified by the CNVCHSEL<5:0> bits; when the bit is set, it is automatically cleared by hardware on the next instruction cycle

- 0 = Next individual channel conversion trigger can be generated

bit 7 SWLCTRG: Software Level-Sensitive Common Trigger bit

- 1 = Triggers are continuously generated for all channels with the software, level-sensitive common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers

- 0 = No software, level-sensitive common triggers are generated

bit 6 **SWCTRG:** Software Common Trigger bit

- 1 = Single trigger is generated for all channels with the software, common trigger selected as a source in the ADTRIGxL and ADTRIGxH registers; when the bit is set, it is automatically cleared by hardware on the next instruction cycle

- 0 = Ready to generate the next software, common trigger

- bit 5-0 **CNVCHSEL <5:0>:** Channel Number Selection for Software Individual Channel Conversion Trigger bits These bits define a channel to be converted when the CNVRTCH bit is set.

# 23.2 Device Calibration and Identification

The PGAx and current source modules on the dsPIC33EPXXGS50X family devices require Calibration Data registers to improve performance of the module over a wide operating range. These Calibration registers are read-only and are stored in configuration memory space. Prior to enabling the module, the calibration data must be read (TBLPAG and Table Read instruction) and loaded into their respective SFR registers. The device calibration addresses are shown in Table 23-3.

The dsPIC33EPXXGS50X devices have two identification registers near the end of configuration memory space that store the Device ID (DEVID) and Device Revision (DEVREV). These registers are used to determine the mask, variant and manufacturing information about the device. These registers are read-only and are shown in Register 23-1 and Register 23-2.

### TABLE 23-3: DEVICE CALIBRATION ADDRESSES<sup>(1)</sup>

| PGA1CAL         800E48         —         —         —         —         —         —         PGA1 Calibration Data           PGA2CAL         800E4C         —         —         —         —         —         —         PGA2 Calibration Data           ISRCCAL         800E78         —         —         —         —         —         —         —         —         — | Calibration<br>Name | Address | Bits 23-16 | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5                           | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|---------------------------------|-------|-------|-------|-------|-------|

| PGA2CAL 800E4C — — — — — — — — PGA2 Calibration Data                                                                                                                                                                                                                                                                                                                   | DOMAGNI             | 000540  |            |        |        |        |        |        |        |       |       |       |       | 50110 !!! !! 5 !                |       |       |       |       |       |

|                                                                                                                                                                                                                                                                                                                                                                        | PGATCAL             | 800E48  | _          | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | PGA1 Calibration Data           |       |       |       |       |       |

|                                                                                                                                                                                                                                                                                                                                                                        | PGA2CAI             | 800E4C  |            |        |        |        |        |        |        |       |       |       |       | PGA2 Calibration Data           |       |       |       |       |       |

| ISRCCAL 800F78 — — — — — — — — — — — — — Current Source Calibration Data                                                                                                                                                                                                                                                                                               | I OAZOAL            | 000L+C  |            |        |        |        |        |        |        |       |       |       |       | 1 OA2 Calibration Data          |       |       |       |       |       |

|                                                                                                                                                                                                                                                                                                                                                                        | ISRCCAL             | 800E78  |            | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | Current Source Calibration Data |       | ata   |       |       |       |

Note 1: The calibration data must be copied into its respective registers prior to enabling the module.

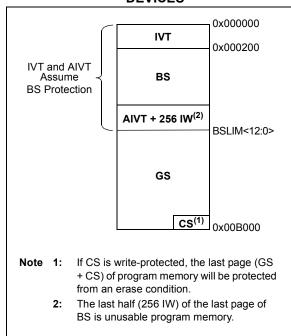

The different device security segments are shown in Figure 23-3. Here, all three segments are shown but are not required. If only basic code protection is required, then GS can be enabled independently or combined with CS. if desired.

**FIGURE 23-3:** SECURITY SEGMENTS **EXAMPLE FOR** dsPIC33EP64GS50X **DEVICES**

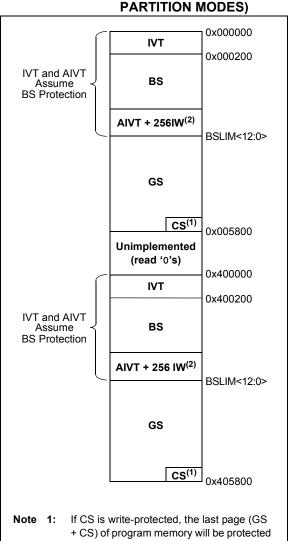

dsPIC33EP64GS50X family devices can be operated in Dual Partition mode, where security is required for each partition. When operating in Dual Partition mode, the Active and Inactive Partitions both contain unique copies of the Reset vector, Interrupt Vector Tables (IVT and AIVT, if enabled) and the Flash Configuration Words. Both partitions have the three security segments described previously. Code may not be executed from the Inactive Partition, but it may be programmed by, and read from, the Active Partition, subject to defined code protection. Figure 23-4 shows the different security segments for a device operating in Dual Partition mode.

The device may also operate in a Protected Dual Partition mode or in Privileged Dual Partition mode. In Protected Dual Partition mode, Partition 1 is permanently erase/write-protected. This implementation allows for a "Factory Default" mode, which provides a fail-safe backup image to be stored in Partition 1. For example, a fail-safe bootloader can be placed in Partition 1, along with a fail-safe backup code image. which can be used or rewritten into Partition 2 in the event of a failed Flash update to Partition 2.

Privileged Dual Partition mode performs the same function as Protected Dual Partition mode, except additional constraints are applied in an effort to prevent code in the Boot Segment and General Segment from being used against each other.

**FIGURE 23-4: SECURITY SEGMENTS EXAMPLE FOR** dsPIC33EP64GS50X **DEVICES (DUAL**

- from an erase condition.

- The last half (256 IW) of the last page of BS is unusable program memory.

TABLE 26-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |                           |      | (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |        |            |          |  |  |  |  |

|--------------------|---------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|----------|--|--|--|--|

| Parameter<br>No.   | Тур.                      | Max. | Units                                                                                                                                                                                                 |        | Conditions |          |  |  |  |  |

| Operating Cur      | rent (IDD) <sup>(1)</sup> |      |                                                                                                                                                                                                       |        |            |          |  |  |  |  |

| DC20d              | 7                         | 12   | mA                                                                                                                                                                                                    | -40°C  |            |          |  |  |  |  |

| DC20a              | 7                         | 12   | mA                                                                                                                                                                                                    | +25°C  | 3.3V       | 10 MIPS  |  |  |  |  |

| DC20b              | 7                         | 12   | mA                                                                                                                                                                                                    | +85°C  | 3.3 V      | 10 WIFS  |  |  |  |  |

| DC20c              | 7                         | 12   | mA                                                                                                                                                                                                    | +125°C |            |          |  |  |  |  |

| DC22d              | 11                        | 19   | mA                                                                                                                                                                                                    | -40°C  |            |          |  |  |  |  |

| DC22a              | 11                        | 19   | mA                                                                                                                                                                                                    | +25°C  | 3.3V       | 20 MIPS  |  |  |  |  |

| DC22b              | 11                        | 19   | mA                                                                                                                                                                                                    | +85°C  | 3.34       |          |  |  |  |  |

| DC22c              | 11                        | 19   | mA                                                                                                                                                                                                    | +125°C |            |          |  |  |  |  |

| DC24d              | 19                        | 30   | mA                                                                                                                                                                                                    | -40°C  |            | 40 MIPS  |  |  |  |  |

| DC24a              | 19                        | 30   | mA                                                                                                                                                                                                    | +25°C  | 3.3V       |          |  |  |  |  |

| DC24b              | 19                        | 30   | mA                                                                                                                                                                                                    | +85°C  | 3.34       |          |  |  |  |  |

| DC24c              | 19                        | 30   | mA                                                                                                                                                                                                    | +125°C |            |          |  |  |  |  |

| DC25d              | 26                        | 41   | mA                                                                                                                                                                                                    | -40°C  |            |          |  |  |  |  |

| DC25a              | 26                        | 41   | mA                                                                                                                                                                                                    | +25°C  | 3.3V       | 60 MIPS  |  |  |  |  |

| DC25b              | 26                        | 41   | mA                                                                                                                                                                                                    | +85°C  | 3.34       | 60 MIPS  |  |  |  |  |

| DC25c              | 26                        | 41   | mA                                                                                                                                                                                                    | +125°C |            |          |  |  |  |  |

| DC26d              | 30                        | 46   | mA                                                                                                                                                                                                    | -40°C  |            |          |  |  |  |  |

| DC26a              | 30                        | 46   | mA                                                                                                                                                                                                    | +25°C  | 3.3V       | 70 MIPS  |  |  |  |  |

| DC26b              | 30                        | 46   | mA                                                                                                                                                                                                    | +85°C  |            |          |  |  |  |  |

| DC27d              | 51                        | 81   | mA                                                                                                                                                                                                    | -40°C  |            | 70 MIPS  |  |  |  |  |

| DC27a              | 51                        | 81   | mA                                                                                                                                                                                                    | +25°C  | 3.3V       |          |  |  |  |  |

| DC27b              | 52                        | 82   | mA                                                                                                                                                                                                    | +85°C  | 3.3 v      | (Note 2) |  |  |  |  |

| DC27c              | 53                        | 83   | mA                                                                                                                                                                                                    | +125°C |            |          |  |  |  |  |

Standard Operating Conditions: 3.0V to 3.6V

- **Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- · No peripheral modules are operating or being clocked (all defined PMDx bits are set)

- CPU is executing while (1) statement

- · JTAG is disabled

- 2: For this specification, the following test conditions apply:

- APLL clock is enabled

- All 5 PWMs enabled and operating at maximum speed (PTCON2<2:0> = 000), PTPER = 1000h, 50% duty cycle

- · All other peripherals are disabled (corresponding PMDx bits are set)

TABLE 26-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT       | ERISTICS                     |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                  |      |  |  |  |  |

|------------------|------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|--|--|--|--|

| Parameter<br>No. | Тур.                         | Max. | Units                                                                                                                                                                                                                                            | Units Conditions |      |  |  |  |  |

| Power-Down       | Current (IPD) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                  |                  |      |  |  |  |  |

| DC60d            | 12                           | 100  | μА                                                                                                                                                                                                                                               | -40°C            |      |  |  |  |  |

| DC60a            | 18                           | 100  | μА                                                                                                                                                                                                                                               | +25°C            | 3.3V |  |  |  |  |

| DC60b            | 130                          | 400  | μА                                                                                                                                                                                                                                               | +85°C            | 3.30 |  |  |  |  |

| DC60c            | 500                          | 1100 | μА                                                                                                                                                                                                                                               | +125°C           |      |  |  |  |  |

Note 1: IPD (Sleep) current is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all set)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- · JTAG is disabled

### TABLE 26-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT (△IWDT)<sup>(1)</sup>

| DC CHARACTER  | RISTICS |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |            |      |  |  |  |

|---------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|--|--|--|

| Parameter No. | Тур.    | Max. | Units                                                                                                                                                                                                                                            | Conditions |      |  |  |  |

| DC61d         | 13      | 50   | μА                                                                                                                                                                                                                                               | -40°C      |      |  |  |  |

| DC61a 19      |         | 80   | μΑ                                                                                                                                                                                                                                               | +25°C      | 3.3V |  |  |  |

| DC61b         | 12      | _    | μΑ                                                                                                                                                                                                                                               | +85°C      | 3.3V |  |  |  |

| DC61c         | 13      | _    | μΑ                                                                                                                                                                                                                                               | +125°C     |      |  |  |  |

**Note 1:** The ΔIWDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

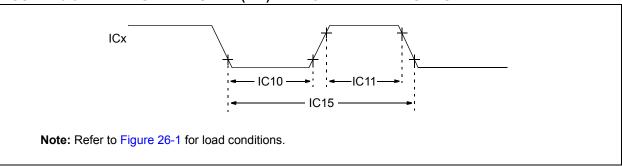

### FIGURE 26-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

TABLE 26-27: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHA        | NRACTERI | STICS                          | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extende |      |       |                                  |                                  |  |  |  |

|---------------|----------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|--|--|

| Param.<br>No. | Symbol   | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                            | Max. | Units | Conditions                       |                                  |  |  |  |

| IC10          | TccL     | ICx Input Low Time             | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                 | _    | ns    | Must also meet<br>Parameter IC15 |                                  |  |  |  |

| IC11          | TccH     | ICx Input High Time            | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                 | _    | ns    | Must also meet<br>Parameter IC15 | N = Prescale Value<br>(1, 4, 16) |  |  |  |

| IC15          | TCCP     | ICx Input Period               | Greater of:<br>25 + 50 or<br>(1 Tcy/N) + 50                                                                                                                                                                                                     | _    | ns    |                                  |                                  |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

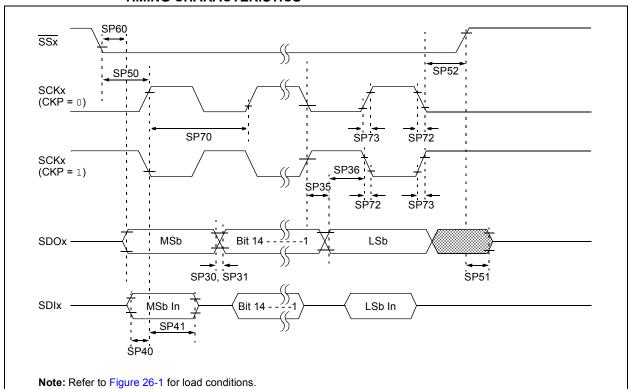

FIGURE 26-16: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)

TIMING CHARACTERISTICS

| <u> </u> | 33EPX | INUS: | JUA FA | -VIAII [ ] |  |  |

|----------|-------|-------|--------|------------|--|--|

| NOTES:   |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |

|          |       |       |        |            |  |  |