Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | POR, PWM, Voltage Detect, WDT                                                    |

| Number of I/O              | 27                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 2.5K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 32-LQFP                                                                          |

| Supplier Device Package    | 32-LQFP (7x7)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f21336tnfp-x6 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                  | Function          | Specification                                                                                                                                                                                                                                                                                                                                                  |  |

|---------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Serial                                | UART0             | Clock synchronous serial I/O/UART                                                                                                                                                                                                                                                                                                                              |  |

| Interface                             | UART2             | Clock synchronous serial I/O/UART, I <sup>2</sup> C mode (I <sup>2</sup> C-bus), SSU mode, multiprocessor communication function                                                                                                                                                                                                                               |  |

| LIN Module                            |                   | Hardware LIN: 1 (timer RA, UART0)                                                                                                                                                                                                                                                                                                                              |  |

| A/D Converter                         |                   | 10-bit resolution $\times$ 12 channels, includes sample and hold function, with sweep mode                                                                                                                                                                                                                                                                     |  |

| Sensor Contro                         | l Unit            | System CH x 3, electrostatic capacitive touch detection x 18                                                                                                                                                                                                                                                                                                   |  |

| Flash Memory                          |                   | <ul> <li>Programming and erasure voltage: VCC = 2.7 V to 5.5 V</li> <li>Programming and erasure endurance: 10,000 times (data flash)<br/>1,000 times (program ROM)</li> <li>Program security: ROM code protect, ID code check</li> <li>Debug functions: On-chip debug, on-board flash rewrite function</li> <li>Background operation (BGO) function</li> </ul> |  |

| Operating Frequency/Supply<br>Voltage |                   | f(XIN) = 20 MHz (VCC = 2.7 V to 5.5 V)<br>f(XIN) = 5 MHz (VCC = 1.8 V to 5.5 V)                                                                                                                                                                                                                                                                                |  |

| Current Consumption                   |                   | Typ. 6.5 mA (VCC = 5.0 V, f(XIN) = 20 MHz)<br>Typ. 3.5 mA (VCC = 3.0 V, f(XIN) = 10 MHz)<br>Typ. 3.5 $\mu$ A (VCC = 3.0 V, wait mode)<br>Typ. 2.0 $\mu$ A (VCC = 3.0 V, stop mode)                                                                                                                                                                             |  |

| Operating Amb                         | pient Temperature | -20 to 85°C (N version)                                                                                                                                                                                                                                                                                                                                        |  |

| Package                               |                   | 32-pin LQFP<br>Package code: PLQP0032GB-A (previous code: 32P6U-A)                                                                                                                                                                                                                                                                                             |  |

# Table 1.2 Specifications for R8C/33T Group (2)

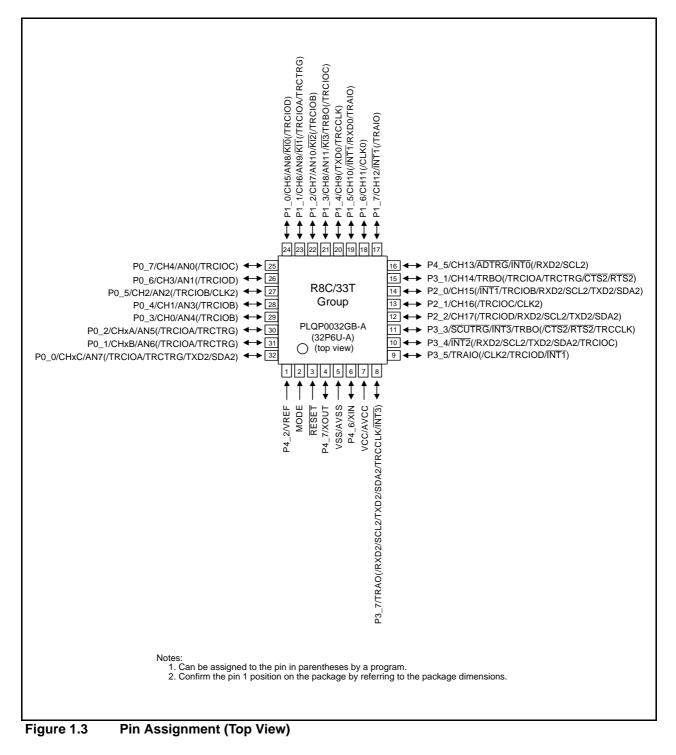

## 1.4 Pin Assignment

Figure 1.3 shows Pin Assignment (Top View). Table 1.4 outlines the Pin Name Information by Pin Number.

## 1.5 Pin Functions

Table 1.5 lists Pin Functions.

#### Table 1.5Pin Functions

| Item                         | Pin Name                                                          | I/O<br>Type | Description                                                                                                                                                                                                                    |

|------------------------------|-------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply input           | VCC, VSS                                                          | —           | Apply 1.8 V to 5.5 V to the VCC pin. Apply 0 V to the VSS pin                                                                                                                                                                  |

| Analog power<br>supply input | AVCC, AVSS                                                        | —           | Power supply for the A/D converter.<br>Connect a capacitor between AVCC and AVSS.                                                                                                                                              |

| Reset input                  | RESET                                                             | I           | Input "L" on this pin resets the MCU.                                                                                                                                                                                          |

| MODE                         | MODE                                                              | I           | Connect this pin to VCC via a resistor.                                                                                                                                                                                        |

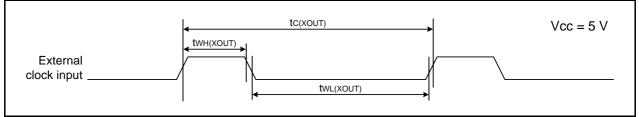

| XIN clock input              | XIN                                                               | I           | These pins are provided for XIN clock generation circuit I/O.<br>Connect a ceramic resonator or a crystal oscillator between                                                                                                   |

| XIN clock output             | XOUT                                                              | I/O         | the XIN and XOUT pins. <sup>(1)</sup><br>To use an external clock, input it to the XOUT pin and leave<br>the XIN pin open.                                                                                                     |

| INT interrupt input          | INT0 to INT3                                                      | Ι           | INT interrupt input pins.<br>INT0 is timer RB, and RC input pin.                                                                                                                                                               |

| Key input interrupt          | KI0 to KI3                                                        | I           | Key input interrupt input pins                                                                                                                                                                                                 |

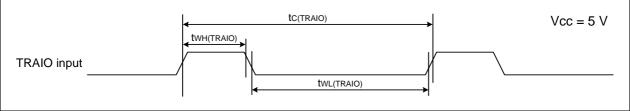

| Timer RA                     | TRAIO                                                             | I/O         | Timer RA I/O pin                                                                                                                                                                                                               |

|                              | TRAO                                                              | 0           | Timer RA output pin                                                                                                                                                                                                            |

| Timer RB                     | TRBO                                                              | 0           | Timer RB output pin                                                                                                                                                                                                            |

| Timer RC                     | TRCCLK                                                            | I           | External clock input pin                                                                                                                                                                                                       |

|                              | TRCTRG                                                            | I           | External trigger input pin                                                                                                                                                                                                     |

|                              | TRCIOA, TRCIOB,<br>TRCIOC, TRCIOD                                 | I/O         | Timer RC I/O pins                                                                                                                                                                                                              |

| Serial interface             | CLK0, CLK2                                                        | I/O         | Transfer clock I/O pins                                                                                                                                                                                                        |

|                              | RXD0, RXD2                                                        | I           | Serial data input pins                                                                                                                                                                                                         |

|                              | TXD0, TXD2                                                        | 0           | Serial data output pins                                                                                                                                                                                                        |

|                              | CTS2                                                              | I           | Transmission control input pin                                                                                                                                                                                                 |

|                              | RTS2                                                              | 0           | Reception control output pin                                                                                                                                                                                                   |

|                              | SCL2                                                              | I/O         | I <sup>2</sup> C mode clock I/O pin                                                                                                                                                                                            |

|                              | SDA2                                                              | I/O         | I <sup>2</sup> C mode data I/O pin                                                                                                                                                                                             |

| Reference voltage input      | VREF                                                              | I           | Reference voltage input pin to A/D converter                                                                                                                                                                                   |

| A/D converter                | AN0 to AN11                                                       | I           | Analog input pins to A/D converter                                                                                                                                                                                             |

|                              | ADTRG                                                             | I           | AD external trigger input pin                                                                                                                                                                                                  |

| Sensor control unit          | CHxA, CHxB, CHxC                                                  | I/O         | Control pins for electrostatic capacitive touch detection                                                                                                                                                                      |

|                              | CH0 to CH17                                                       | I           | Electrostatic capacitive touch detection pins                                                                                                                                                                                  |

|                              | SCUTRG                                                            | I           | Sensor control unit external trigger input                                                                                                                                                                                     |

| I/O port                     | P0_0 to P0_7,                                                     | I/O         | CMOS I/O ports. Each port has an I/O select direction                                                                                                                                                                          |

|                              | P1_0 to P1_7,<br>P2_0 to P2_2,<br>P3_1,<br>P3_3 to P3_5,<br>P3_7, |             | register, allowing each pin in the port to be directed for input<br>or output individually.<br>Any port set to input can be set to use a pull-up resistor or not<br>by a program.<br>All ports can be used as LED drive ports. |

|                              | P4_5 to P4_7                                                      |             |                                                                                                                                                                                                                                |

|                              | 1                                                                 | 1           |                                                                                                                                                                                                                                |

Note:

State was the second second

1. Refer to the oscillator manufacturer for oscillation characteristics.

## 2.1 Data Registers (R0, R1, R2, and R3)

R0 is a 16-bit register for transfer, arithmetic, and logic operations. The same applies to R1 to R3. R0 can be split into high-order bits (R0H) and low-order bits (R0L) to be used separately as 8-bit data registers. R1H and R1L are analogous to R0H and R0L. R2 can be combined with R0 and used as a 32-bit data register (R2R0). R3R1 is analogous to R2R0.

## 2.2 Address Registers (A0 and A1)

A0 is a 16-bit register for address register indirect addressing and address register relative addressing. It is also used for transfer, arithmetic, and logic operations. A1 is analogous to A0. A1 can be combined with A0 and as a 32-bit address register (A1A0).

### 2.3 Frame Base Register (FB)

FB is a 16-bit register for FB relative addressing.

### 2.4 Interrupt Table Register (INTB)

INTB is a 20-bit register that indicates the starting address of an interrupt vector table.

## 2.5 Program Counter (PC)

PC is 20 bits wide and indicates the address of the next instruction to be executed.

## 2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

The stack pointers (SP), USP and ISP, are each 16 bits wide. The U flag of FLG is used to switch between USP and ISP.

#### 2.7 Static Base Register (SB)

SB is a 16-bit register for SB relative addressing.

### 2.8 Flag Register (FLG)

FLG is an 11-bit register indicating the CPU state.

### 2.8.1 Carry Flag (C)

The C flag retains carry, borrow, or shift-out bits that have been generated by the arithmetic and logic unit.

### 2.8.2 Debug Flag (D)

The D flag is for debugging only. Set it to 0.

## 2.8.3 Zero Flag (Z)

The Z flag is set to 1 when an arithmetic operation results in 0; otherwise to 0.

### 2.8.4 Sign Flag (S)

The S flag is set to 1 when an arithmetic operation results in a negative value; otherwise to 0.

### 2.8.5 Register Bank Select Flag (B)

Register bank 0 is selected when the B flag is 0. Register bank 1 is selected when this flag is set to 1.

### 2.8.6 Overflow Flag (O)

The O flag is set to 1 when an operation results in an overflow; otherwise to 0.

# 3. Memory

## 3.1 R8C/33T Group

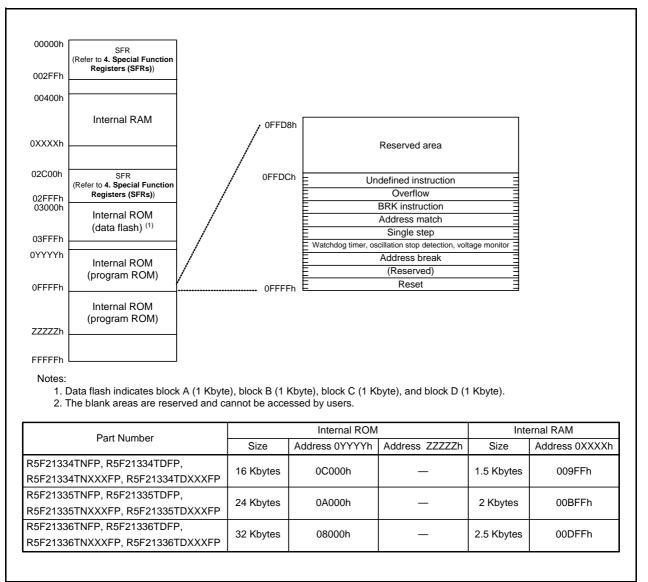

Figure 3.1 is a Memory Map of R8C/33T Group. The R8C/33T Group has a 1-Mbyte address space from addresses 00000h to FFFFFh. For example, a 32-Kbyte internal ROM area is allocated addresses 08000h to 0FFFFh.

The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. The starting address of each interrupt routine is stored here.

The internal ROM (data flash) is allocated addresses 03000h to 03FFFh.

The internal RAM is allocated higher addresses, beginning with address 00400h. For example, a 2.5-Kbyte internal RAM area is allocated addresses 00400h to 00DFFh. The internal RAM is used not only for data storage but also as a stack area when a subroutine is called or when an interrupt request is acknowledged.

Special function registers (SFRs) are allocated addresses 00000h to 002FFh and 02C00h to 02FFFh. Peripheral function control registers are allocated here. All unallocated spaces within the SFRs are reserved and cannot be accessed by users.

RENESAS

| Address | Register | Symbol | After Reset |

|---------|----------|--------|-------------|

| 0140h   |          |        |             |

| 0141h   |          |        |             |

| 0142h   |          |        |             |

| 0143h   |          |        |             |

| 0144h   |          |        |             |

| 0145h   |          |        |             |

| 0146h   |          |        |             |

| 0147h   |          |        |             |

| 0148h   |          |        |             |

| 0149h   |          |        |             |

| 014Ah   |          |        |             |

| 014Bh   |          |        |             |

| 014Ch   |          |        |             |

| 014Dh   |          |        |             |

| 014Eh   |          |        |             |

| 014Fh   |          |        |             |

| 0150h   |          |        |             |

| 0151h   |          |        |             |

| 0152h   |          |        |             |

| 0153h   |          |        | 1           |

| 0154h   |          | 1      | 1           |

| 0155h   |          |        |             |

| 0156h   |          |        |             |

| 0157h   |          |        |             |

| 0158h   |          |        |             |

| 0159h   |          |        |             |

| 015Ah   |          |        |             |

| 015Bh   |          |        |             |

| 015Ch   |          |        |             |

| 015Dh   |          |        |             |

| 015Eh   |          |        |             |

| 015Eh   |          |        |             |

| 0160h   |          |        |             |

| 0161h   |          |        |             |

| 0162h   |          |        |             |

| 0162h   |          |        |             |

| 0164h   |          |        |             |

| 0165h   |          |        |             |

| 0166h   |          |        |             |

| 0166h   |          |        |             |

|         |          |        |             |

| 0168h   |          |        |             |

| 0169h   |          |        |             |

| 016Ah   |          |        |             |

| 016Bh   |          |        |             |

| 016Ch   |          |        |             |

| 016Dh   |          |        |             |

| 016Eh   |          |        |             |

| 016Fh   |          |        |             |

| 0170h   |          |        |             |

| 0171h   |          |        |             |

| 0172h   |          |        |             |

| 0173h   |          |        |             |

| 0174h   |          |        |             |

| 0175h   |          |        |             |

| 0176h   |          |        |             |

| 0177h   |          |        |             |

| 0178h   |          |        |             |

| 0179h   |          |        |             |

| 017Ah   |          |        |             |

| 017Bh   |          |        |             |

| 017Ch   |          |        |             |

| 017Dh   |          | 1      | 1           |

| 017Eh   |          |        |             |

| 017Eh   |          |        |             |

| Note:   |          | 1      |             |

| Table 4.6 | SFR Information (6) <sup>(1)</sup> |

|-----------|------------------------------------|

|-----------|------------------------------------|

Note:

1. The blank areas are reserved and cannot be accessed by users.

| Address        | Register                                  | Symbol       | After Reset |

|----------------|-------------------------------------------|--------------|-------------|

| 01C0h          | Address Match Interrupt Register 0        | RMAD0        | XXh         |

| 01C1h          |                                           |              | XXh         |

| 01C2h          |                                           |              | 0000XXXXb   |

| 01C3h          | Address Match Interrupt Enable Register 0 | AIER0        | 00h         |

| 01C4h          | Address Match Interrupt Register 1        | RMAD1        | XXh         |

|                | Address Match Interrupt Register 1        | RIVIADI      |             |

| 01C5h          |                                           |              | XXh         |

| 01C6h          |                                           |              | 0000XXXXb   |

| 01C7h          | Address Match Interrupt Enable Register 1 | AIER1        | 00h         |

| 01C8h          |                                           |              |             |

| 01C9h          |                                           |              |             |

| 01CAh          |                                           |              |             |

| 01CBh          |                                           |              |             |

| 01CCh          |                                           |              |             |

| 01CDh          |                                           |              |             |

| 01CEh          |                                           |              |             |

| 01CFh          |                                           |              |             |

| 01D0h          |                                           |              |             |

| 01D1h          |                                           |              |             |

| 01D1h<br>01D2h |                                           |              |             |

| 01D2h<br>01D3h |                                           |              |             |

|                |                                           |              |             |

| 01D4h          |                                           |              |             |

| 01D5h          |                                           |              |             |

| 01D6h          |                                           |              |             |

| 01D7h          |                                           |              |             |

| 01D8h          |                                           |              |             |

| 01D9h          |                                           |              |             |

| 01DAh          |                                           |              |             |

| 01DBh          |                                           |              |             |

| 01DCh          |                                           |              |             |

| 01DDh          |                                           |              |             |

| 01DEh          |                                           |              |             |

| 01DFh          |                                           |              |             |

| 01E0h          | Pull-Up Control Register 0                | PUR0         | 00h         |

| 01E1h          | Pull-Up Control Register 1                | PUR1         | 00h         |

| 01E2h          |                                           |              | 0011        |

| 01E2h          |                                           |              |             |

|                |                                           |              |             |

| 01E4h          |                                           |              |             |

| 01E5h          |                                           |              |             |

| 01E6h          |                                           |              |             |

| 01E7h          |                                           |              |             |

| 01E8h          |                                           |              |             |

| 01E9h          |                                           |              |             |

| 01EAh          |                                           |              |             |

| 01EBh          |                                           |              |             |

| 01ECh          |                                           |              |             |

| 01EDh          |                                           |              |             |

| 01EEh          |                                           |              |             |

| 01EFh          |                                           |              |             |

|                | Port P1 Drive Capacity Control Register   | P1DRR        | 00h         |

| 01F1h          | Port P2 Drive Capacity Control Register   | P2DRR        | 00h         |

| 01F2h          | Drive Capacity Control Register 0         | DRR0         | 00h         |

| 01F3h          | Drive Capacity Control Register 0         | DRR1         | 00h         |

| 01F4h          |                                           |              | 0011        |

| 01F5h          | Input Threshold Control Register 0        | VLT0         | 00h         |

| 01F5h          | Input Threshold Control Register 0        | VLT0<br>VLT1 |             |

| 01500          |                                           | VLII         | 00h         |

| 01F7h          |                                           |              |             |

| 01F8h          |                                           |              |             |

| 01F9h          |                                           |              |             |

| 01FAh          | External Input Enable Register 0          | INTEN        | 00h         |

| 01FBh          |                                           |              |             |

| 01FCh          | INT Input Filter Select Register 0        | INTF         | 00h         |

| 01FDh          |                                           |              |             |

| 01FEh          | Key Input Enable Register 0               | KIEN         | 00h         |

| 01FFh          | -                                         |              |             |

| X: Undefined   |                                           | 1            |             |

Table 4.8SFR Information (8) (1)

X: Undefined

Note:

1. The blank areas are reserved and cannot be accessed by users.

| A -1 -1                                            |                                      | <b>2</b> · · · |                          |

|----------------------------------------------------|--------------------------------------|----------------|--------------------------|

| Address                                            | Register                             | Symbol         | After Reset              |

| 02C0h                                              | SCU Control Register 0               | SCUCR0         | 00h                      |

| 02C1h                                              | SCU Mode Register                    | SCUMR          | 00h                      |

| 02C2h                                              | SCU Timing Control Register 0        | SCTCR0         | 00000011b                |

| 02C3h                                              | SCU Timing Control Register 1        | SCTCR1         | 0000001b                 |

| 02C4h                                              | SCU Timing Control Register 2        | SCTCR2         | 00010000b                |

| 02C5h                                              | SCU Timing Control Register 3        | SCTCR3         | 00h                      |

| 02C6h                                              | SCU Channel Control Register         | SCHCR          | 00h                      |

| 02C7h                                              | SCU Channel Control Counter          | SCUCHC         | 00h                      |

| 02C8h                                              | SCU Flag Register                    | SCUFR          | 00h                      |

| 02C8h                                              | SCU Status Counter                   | SCUSTC         | 00h                      |

|                                                    |                                      |                |                          |

| 02CAh                                              | SCU Secondary Counter Set Register   | SCSCSR         | 00000111b                |

| 02CBh                                              | SCU Secondary Counter                | SCUSCC         | 00000111b                |

| 02CCh                                              |                                      |                |                          |

| 02CDh                                              |                                      |                |                          |

| 02CEh                                              | SCU Destination Address Register     | SCUDAR         | 00h                      |

| 02CFh                                              |                                      |                | 00001100b                |

| 02D0h                                              | SCU Data Buffer Register             | SCUDBR         | 00h                      |

| 02D1h                                              |                                      | 000000         | 00h                      |

| 02D1h                                              | SCU Primary Counter                  | SCUPRC         | 00h                      |

|                                                    |                                      | SCOFIC         |                          |

| 02D3h                                              |                                      |                | 00h                      |

| 02D4h                                              |                                      |                |                          |

| 02D5h                                              |                                      |                |                          |

| 02D6h                                              |                                      |                |                          |

| 02D7h                                              |                                      |                |                          |

| 02D8h                                              |                                      | 1              |                          |

| 02D9h                                              |                                      | 1              |                          |

| 02DOh                                              |                                      |                |                          |

| 02DBh                                              |                                      |                |                          |

| 02DBh<br>02DCh                                     | Touch Sensor Input Enable Register 0 |                | 0.01                     |

|                                                    |                                      | TSIER0         | 00h                      |

| 02DDh                                              | Touch Sensor Input Enable Register 1 | TSIER1         | 00h                      |

| 02DEh                                              | Touch Sensor Input Enable Register 2 | TSIER2         | 00h                      |

| 02DFh                                              |                                      |                |                          |

| :                                                  |                                      |                |                          |

| 2C00h                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C01h                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C02h                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C03h                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C04h                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C05h                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C05h                                              |                                      |                | XXh                      |

|                                                    | DTC Transfer Vector Area             |                |                          |

| 2C07h                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C08h                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C09h                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C0Ah                                              | DTC Transfer Vector Area             |                | XXh                      |

| :                                                  | DTC Transfer Vector Area             |                | XXh                      |

| :                                                  | DTC Transfer Vector Area             |                | XXh                      |

| 2C3Ah                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C3An<br>2C3Bh                                     | DTC Transfer Vector Area             |                | XXh                      |

|                                                    |                                      |                |                          |

| 2C3Ch                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C3Dh                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C3Eh                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C3Fh                                              | DTC Transfer Vector Area             |                | XXh                      |

| 2C40h                                              | DTC Control Data 0                   | DTCD0          | XXh                      |

| 2C41h                                              | 1                                    | 1              | XXh                      |

| 2C42h                                              | 1                                    |                | XXh                      |

| 2C43h                                              | 1                                    |                | XXh                      |

| 2C43h                                              | 4                                    |                | XXh                      |

|                                                    | 4                                    |                |                          |

| 2C45h                                              | 4                                    |                | XXh                      |

| 2C46h                                              | 1                                    |                | XXh                      |

|                                                    |                                      |                | XXh                      |

| 2C47h                                              | DTC Control Data 1                   | DTCD1          | XXh                      |

| 2C47h<br>2C48h                                     |                                      | 1              | XXh                      |

|                                                    |                                      |                |                          |

| 2C48h<br>2C49h                                     |                                      |                |                          |

| 2C48h<br>2C49h<br>2C4Ah                            |                                      |                | XXh                      |

| 2C48h<br>2C49h<br>2C4Ah<br>2C4Bh                   |                                      |                | XXh<br>XXh               |

| 2C48h<br>2C49h<br>2C4Ah<br>2C4Bh<br>2C4Ch          |                                      |                | XXh<br>XXh<br>XXh        |

| 2C48h<br>2C49h<br>2C4Ah<br>2C4Bh<br>2C4Ch<br>2C4Ch |                                      |                | XXh<br>XXh<br>XXh<br>XXh |

| 2C48h<br>2C49h<br>2C4Ah<br>2C4Bh<br>2C4Ch          |                                      |                | XXh<br>XXh<br>XXh        |

# Table 4.9SFR Information (9) (1)

Note:

1. The blank areas are reserved and cannot be accessed by users.

| Address | Area Name                         | Symbol After R |           |  |

|---------|-----------------------------------|----------------|-----------|--|

| :       |                                   |                |           |  |

| FFDBh   | Option Function Select Register 2 | OFS2           | (Note 1)  |  |

| :       |                                   |                |           |  |

| FFDFh   | ID1                               |                | (Note 2)  |  |

| :       |                                   |                |           |  |

| FFE3h   | ID2                               |                | (Note 2)  |  |

| :       |                                   |                |           |  |

| FFEBh   | ID3                               |                | (Note 2)  |  |

| :       |                                   |                |           |  |

| FFEFh   | ID4                               |                | (Note 2)  |  |

| :       |                                   |                |           |  |

| FFF3h   | ID5                               |                | (Note 2)  |  |

| :       | 100                               |                |           |  |

| FFF7h   | ID6                               |                | (Note 2)  |  |

| :       |                                   |                |           |  |

| FFFBh   | ID7                               |                | (Note 2)  |  |

|         | Ortion Function Colort Desister   | 050            | (NI-4- 4) |  |

| FFFFh   | Option Function Select Register   | OFS            | (Note 1)  |  |

Table 4.13 ID Code Areas and Option Function Select Area

Notes:

The option function select area is allocated in the flash memory, not in the SFRs. Set appropriate values as ROM data by a program. Do not write additions to the option function select area. If the block including the option function select area is erased, the option function select area is set to FFh.

When blank products are shipped, the option function select area is set to FFh. It is set to the written value after written by the user. When factory-programming products are shipped, the value of the option function select area is the value programmed by the user.

2. The ID code areas are allocated in the flash memory, not in the SFRs. Set appropriate values as ROM data by a program. Do not write additions to the ID code areas. If the block including the ID code areas is erased, the ID code areas are set to FFh. When blank products are shipped, the ID code areas are set to FFh. They are set to the written value after written by the user. When factory-programming products are shipped, the value of the ID code areas is the value programmed by the user.

| Cumhal    | Parameter                         |                                                 |                          | Conditions            | Standard                                           |          |      | Unit     |      |

|-----------|-----------------------------------|-------------------------------------------------|--------------------------|-----------------------|----------------------------------------------------|----------|------|----------|------|

| Symbol    |                                   | Pa                                              | arameter                 |                       | Conditions                                         | Min.     | Тур. | Max.     | Unit |

| Vcc/AVcc  | Supply voltage                    |                                                 |                          |                       |                                                    | 1.8      |      | 5.5      | V    |

| Vss/AVss  | Supply voltage                    |                                                 |                          |                       |                                                    | —        | 0    | _        | V    |

| Viн       | Input "H" voltage                 | Other th                                        | nan CMOS ir              | nput                  |                                                    | 0.8 Vcc  | —    | Vcc      | V    |

|           |                                   | CMOS                                            | Input level              | Input level selection | $4.0~V \leq Vcc \leq 5.5~V$                        | 0.5 Vcc  | _    | Vcc      | V    |

|           |                                   | input                                           | switching                | : 0.35 Vcc            | $2.7~V \leq Vcc < 4.0~V$                           | 0.55 Vcc |      | Vcc      | V    |

|           |                                   |                                                 | function<br>(I/O port)   |                       | $1.8~V \leq Vcc < 2.7~V$                           | 0.65 Vcc |      | Vcc      | V    |

|           |                                   |                                                 | (1/0 port)               | Input level selection | $4.0~V \leq Vcc \leq 5.5~V$                        | 0.65 Vcc |      | Vcc      | V    |

|           |                                   |                                                 |                          | : 0.5 Vcc             | $2.7~V \leq Vcc < 4.0~V$                           | 0.7 Vcc  |      | Vcc      | V    |

|           |                                   |                                                 |                          |                       | $1.8 \text{ V} \leq \text{Vcc} < 2.7 \text{ V}$    | 0.8 Vcc  | _    | Vcc      | V    |

|           |                                   |                                                 |                          | Input level selection | $4.0~V \leq Vcc \leq 5.5~V$                        | 0.85 Vcc | —    | Vcc      | V    |

|           |                                   |                                                 |                          | : 0.7 Vcc             | $2.7~V \leq Vcc < 4.0~V$                           | 0.85 Vcc | —    | Vcc      | V    |

|           |                                   |                                                 |                          |                       | $1.8 \text{ V} \leq \text{Vcc} < 2.7 \text{ V}$    | 0.85 Vcc | _    | Vcc      | V    |

|           |                                   |                                                 | I clock input            | . ,                   |                                                    | 1.2      | —    | Vcc      | V    |

| VIL       | Input "L" voltage                 | -                                               | nan CMOS ir              |                       |                                                    | 0        | _    | 0.2 Vcc  | V    |

|           |                                   | CMOS                                            | Input level              | Input level selection |                                                    | 0        | —    | 0.2 Vcc  | V    |

|           |                                   | input                                           | switching<br>function    | : 0.35 Vcc            | $2.7~V \leq Vcc < 4.0~V$                           | 0        | _    | 0.2 Vcc  | V    |

|           |                                   |                                                 | (I/O port)               |                       | $1.8 \text{ V} \leq \text{Vcc} < 2.7 \text{ V}$    | 0        | _    | 0.2 Vcc  | V    |

|           |                                   |                                                 | (                        | Input level selection | $4.0~V \leq Vcc \leq 5.5~V$                        | 0        |      | 0.4 Vcc  | V    |

|           |                                   |                                                 |                          | : 0.5 Vcc             | $2.7~V \leq Vcc < 4.0~V$                           | 0        |      | 0.3 Vcc  | V    |

|           |                                   |                                                 |                          |                       | $1.8~V \leq Vcc < 2.7~V$                           | 0        |      | 0.2 Vcc  | V    |

|           |                                   |                                                 |                          | Input level selection | $4.0~V \leq Vcc \leq 5.5~V$                        | 0        |      | 0.55 Vcc | V    |

|           |                                   |                                                 |                          | : 0.7 Vcc             | $2.7~V \leq Vcc < 4.0~V$                           | 0        |      | 0.45 Vcc | V    |

|           |                                   |                                                 |                          |                       | $1.8 \text{ V} \leq \text{Vcc} < 2.7 \text{ V}$    | 0        | _    | 0.35 Vcc | V    |

|           |                                   |                                                 | I clock input            |                       |                                                    | 0        |      | 0.4 Vcc  | V    |

| IOH(sum)  | Peak sum output<br>"H" current    | Sum of all pins IOH(peak)                       |                          |                       | _                                                  | _        | -160 | mA       |      |

| IOH(sum)  | Average sum<br>output "H" current | Sum of                                          | Sum of all pins IOH(avg) |                       |                                                    | —        | —    | -80      | mA   |

| IOH(peak) | Peak output "H"                   | Drive ca                                        | apacity Low              |                       |                                                    | —        |      | -10      | mA   |

|           | current                           | Drive ca                                        | apacity High             |                       |                                                    | —        | —    | -40      | mA   |

| IOH(avg)  | Average output                    | Drive ca                                        | apacity Low              |                       |                                                    | —        |      | -5       | mA   |

|           | "H" current                       | Drive ca                                        | apacity High             |                       |                                                    | —        |      | -20      | mA   |

| IOL(sum)  | Peak sum output<br>"L" current    | Sum of                                          | all pins IOL(p           | eak)                  |                                                    | —        | _    | 160      | mA   |

| IOL(sum)  | Average sum<br>output "L" current | Sum of                                          | all pins IOL(a           | vg)                   |                                                    | —        | —    | 80       | mA   |

| IOL(peak) | Peak output "L"                   | Drive ca                                        | apacity Low              |                       |                                                    | _        | _    | 10       | mA   |

|           | current                           | Drive ca                                        | apacity High             |                       |                                                    | _        | _    | 40       | mA   |

| IOL(avg)  | Average output                    | Drive ca                                        | apacity Low              |                       |                                                    | _        | _    | 5        | mA   |

|           | "L" current                       | Drive ca                                        | apacity High             |                       |                                                    | _        | _    | 20       | mA   |

| f(XIN)    | XIN clock input os                | cillation fr                                    | requency                 |                       | $2.7~V \leq Vcc \leq 5.5~V$                        | —        | _    | 20       | MHz  |

|           |                                   |                                                 |                          |                       | $1.8~V \leq Vcc < 2.7~V$                           | —        | _    | 5        | MHz  |

| fOCO40M   | When used as the                  | as the count source for timer RC <sup>(3)</sup> |                          |                       | $2.7~V \leq Vcc \leq 5.5~V$                        | 32       | —    | 40       | MHz  |

| fOCO-F    | fOCO-F frequency                  |                                                 |                          |                       | $2.7~V \leq Vcc \leq 5.5~V$                        | _        | —    | 20       | MHz  |

|           |                                   |                                                 |                          |                       | $1.8~V \leq Vcc < 2.7~V$                           | _        | —    | 5        | MHz  |

| —         | System clock frequ                | lency                                           |                          |                       | $2.7 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ |          | _    | 20       | MHz  |

|           |                                   |                                                 |                          |                       | $1.8~V \leq Vcc < 2.7~V$                           | _        | —    | 5        | MHz  |

| f(BCLK)   | CPU clock frequer                 | ю                                               |                          |                       | $2.7~V \leq Vcc \leq 5.5~V$                        |          | —    | 20       | MHz  |

|           |                                   |                                                 |                          |                       | $1.8 \text{ V} \le \text{Vcc} < 2.7 \text{ V}$     | _        | _    | 5        | MHz  |

#### Table 5.2 Recommended Operating Conditions

Notes:

1. Vcc = 1.8 V to 5.5 V at Topr =  $-20^{\circ}$ C to 85°C (N version), unless otherwise specified.

2. The average output current indicates the average value of current measured during 100 ms.

3. fOCO40M can be used as the count source for timer RC in the range of Vcc = 2.7 V to 5.5 V.

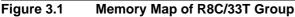

Figure 5.1 Ports P0 to P4 Timing Measurement Circuit

| Symbol  | Parameter                                                                    |                                                       | Standard |      |      | Unit |

|---------|------------------------------------------------------------------------------|-------------------------------------------------------|----------|------|------|------|

|         | Parameter                                                                    | Condition                                             | Min.     | Тур. | Max. | Unit |

| Vdet0   | Voltage detection level Vdet0_0 <sup>(2)</sup>                               |                                                       | 1.80     | 1.90 | 2.05 | V    |

|         | Voltage detection level Vdet0_1 <sup>(2)</sup>                               |                                                       | 2.15     | 2.35 | 2.50 | V    |

|         | Voltage detection level Vdet0_2 (2)                                          |                                                       | 2.70     | 2.85 | 3.05 | V    |

|         | Voltage detection level Vdet0_3 <sup>(2)</sup>                               |                                                       | 3.55     | 3.80 | 4.05 | V    |

| _       | Voltage detection 0 circuit response time <sup>(4)</sup>                     | At the falling of Vcc from 5 V to $(Vdet0_0 - 0.1) V$ | —        | 6    | 150  | μS   |

| _       | Voltage detection circuit self power consumption                             | VCA25 = 1, Vcc = 5.0 V                                | —        | 1.5  |      | μA   |

| td(E-A) | Waiting time until voltage detection circuit operation starts <sup>(3)</sup> |                                                       | —        | —    | 100  | μS   |

| Table 5.6 | Voltage Detection 0 Circuit Electrical Characteristics |

|-----------|--------------------------------------------------------|

|           |                                                        |

Notes:

1. The measurement condition is Vcc = 1.8 V to 5.5 V and Topr =  $-20^{\circ}$ C to 85°C (N version).

2. Select the voltage detection level with bits VDSEL0 and VDSEL1 in the OFS register.

3. Necessary time until the voltage detection circuit operates when setting to 1 again after setting the VCA25 bit in the VCA2 register to 0.

4. Time until the voltage monitor 0 reset is generated after the voltage passes Vdet0.

| Table 5.7 | Voltage Detection 1 Circuit Electrical Characteristics |

|-----------|--------------------------------------------------------|

|-----------|--------------------------------------------------------|

| Symbol  | Deremeter                                                                    | Condition                                             |      | Standard | l    | Unit |

|---------|------------------------------------------------------------------------------|-------------------------------------------------------|------|----------|------|------|

| Symbol  | Parameter                                                                    | Condition                                             | Min. | Тур.     | Max. | Unit |

| Vdet1   | Voltage detection level Vdet1_0 <sup>(2)</sup>                               | At the falling of Vcc                                 | 2.00 | 2.20     | 2.40 | V    |

|         | Voltage detection level Vdet1_1 <sup>(2)</sup>                               | At the falling of Vcc                                 | 2.15 | 2.35     | 2.55 | V    |

|         | Voltage detection level Vdet1_2 <sup>(2)</sup>                               | At the falling of Vcc                                 | 2.30 | 2.50     | 2.70 | V    |

|         | Voltage detection level Vdet1_3 <sup>(2)</sup>                               | At the falling of Vcc                                 | 2.45 | 2.65     | 2.85 | V    |

|         | Voltage detection level Vdet1_4 <sup>(2)</sup>                               | At the falling of Vcc                                 | 2.60 | 2.80     | 3.00 | V    |

|         | Voltage detection level Vdet1_5 <sup>(2)</sup>                               | At the falling of Vcc                                 | 2.75 | 2.95     | 3.15 | V    |

|         | Voltage detection level Vdet1_6 <sup>(2)</sup>                               | At the falling of Vcc                                 | 2.85 | 3.10     | 3.40 | V    |

|         | Voltage detection level Vdet1_7 <sup>(2)</sup>                               | At the falling of Vcc                                 | 3.00 | 3.25     | 3.55 | V    |

|         | Voltage detection level Vdet1_8 <sup>(2)</sup>                               | At the falling of Vcc                                 | 3.15 | 3.40     | 3.70 | V    |

|         | Voltage detection level Vdet1_9 <sup>(2)</sup>                               | At the falling of Vcc                                 | 3.30 | 3.55     | 3.85 | V    |

|         | Voltage detection level Vdet1_A (2)                                          | At the falling of Vcc                                 | 3.45 | 3.70     | 4.00 | V    |

|         | Voltage detection level Vdet1_B (2)                                          | At the falling of Vcc                                 | 3.60 | 3.85     | 4.15 | V    |

|         | Voltage detection level Vdet1_C (2)                                          | At the falling of Vcc                                 | 3.75 | 4.00     | 4.30 | V    |

|         | Voltage detection level Vdet1_D (2)                                          | At the falling of Vcc                                 | 3.90 | 4.15     | 4.45 | V    |

|         | Voltage detection level Vdet1_E (2)                                          | At the falling of Vcc                                 | 4.05 | 4.30     | 4.60 | V    |

|         | Voltage detection level Vdet1_F (2)                                          | At the falling of Vcc                                 | 4.20 | 4.45     | 4.75 | V    |

| _       | Hysteresis width at the rising of Vcc in voltage                             | Vdet1_0 to Vdet1_5 selected                           | _    | 0.07     |      | V    |

|         | detection 1 circuit                                                          | Vdet1_6 to Vdet1_F selected                           | —    | 0.10     | _    | V    |

| _       | Voltage detection 1 circuit response time (3)                                | At the falling of Vcc from 5 V to $(Vdet1_0 - 0.1) V$ | _    | 60       | 150  | μS   |

| _       | Voltage detection circuit self power consumption                             | VCA26 = 1, Vcc = 5.0 V                                | —    | 1.7      |      | μA   |

| td(E-A) | Waiting time until voltage detection circuit operation starts <sup>(4)</sup> |                                                       |      |          | 100  | μs   |

Notes:

1. The measurement condition is Vcc = 1.8 V to 5.5 V and Topr =  $-20^{\circ}$ C to  $85^{\circ}$ C (N version).

2. Select the voltage detection level with bits VD1S0 to VD1S3 in the VD1LS register.

3. Time until the voltage monitor 1 interrupt request is generated after the voltage passes Vdet1.

4. Necessary time until the voltage detection circuit operates when setting to 1 again after setting the VCA26 bit in the VCA2 register to 0.

| Symbol  | Parameter                                                                    | Condition                                             |      | Standard |      | Unit |

|---------|------------------------------------------------------------------------------|-------------------------------------------------------|------|----------|------|------|

| Symbol  | Faranielei                                                                   | Condition                                             | Min. | Тур.     | Max. | Unit |

| Vdet2   | Voltage detection level Vdet2_0                                              | At the falling of Vcc                                 | 3.70 | 4.00     | 4.30 | V    |

| _       | Hysteresis width at the rising of Vcc in voltage detection 2 circuit         |                                                       | —    | 0.10     | —    | V    |

|         | Voltage detection 2 circuit response time <sup>(2)</sup>                     | At the falling of Vcc from 5 V to $(Vdet2_0 - 0.1)$ V | —    | 20       | 150  | μS   |

| —       | Voltage detection circuit self power consumption                             | VCA27 = 1, Vcc = 5.0 V                                |      | 1.7      |      | μA   |

| td(E-A) | Waiting time until voltage detection circuit operation starts <sup>(3)</sup> |                                                       | —    | —        | 100  | μS   |

#### Table 5.8 Voltage Detection 2 Circuit Electrical Characteristics

Notes:

- 1. The measurement condition is Vcc = 1.8 V to 5.5 V and Topr =  $-20^{\circ}$ C to  $85^{\circ}$ C (N version).

- 2. Time until the voltage monitor 2 interrupt request is generated after the voltage passes Vdet2.

- 3. Necessary time until the voltage detection circuit operates after setting to 1 again after setting the VCA27 bit in the VCA2 register to 0.

#### Table 5.9 Power-on Reset Circuit <sup>(2)</sup>

| Symbol | Parameter                        | Condition |      | Standard | 1     | Unit    |

|--------|----------------------------------|-----------|------|----------|-------|---------|

| Symbol | Falameter                        | Condition | Min. | Тур.     | Max.  | Unit    |

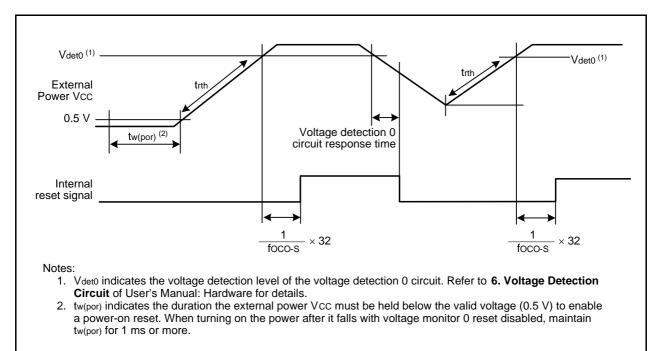

| trth   | External power Vcc rise gradient | (Note 1)  | 0    | —        | 50000 | mV/msec |

Notes:

1. The measurement condition is Topr = -20°C to 85°C (N version), unless otherwise specified.

2. To use the power-on reset function, enable voltage monitor 0 reset by setting the LVDAS bit in the OFS register to 0.

#### Figure 5.3 Power-on Reset Circuit Electrical Characteristics

| Symbol | Parameter                                                                                                                                                                                               | Condition                                                                                                             |        | Standard |        | Unit |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------|----------|--------|------|

| Symbol | Falanielei                                                                                                                                                                                              | Condition                                                                                                             | Min.   | Тур.     | Max.   | Onit |

| —      | High-speed on-chip oscillator frequency after reset                                                                                                                                                     | Vcc = 1.8 V to 5.5 V<br>−20°C ≤ Topr ≤ 85°C                                                                           | 38.4   | 40       | 41.6   | MHz  |

|        | High-speed on-chip oscillator frequency when the<br>FRA4 register correction value is written into the<br>FRA1 register and the FRA5 register correction<br>value into the FRA3 register <sup>(2)</sup> | $\label{eq:Vcc} \begin{array}{l} Vcc = 1.8 \ V \ to \ 5.5 \ V \\ -20^{\circ}C \leq Topr \leq 85^{\circ}C \end{array}$ | 35.389 | 36.864   | 38.338 | MHz  |

|        | High-speed on-chip oscillator frequency when the<br>FRA6 register correction value is written into the<br>FRA1 register and the FRA7 register correction<br>value into the FRA3 register                | Vcc = 1.8 V to 5.5 V<br>−20°C ≤ Topr ≤ 85°C                                                                           | 30.72  | 32       | 33.28  | MHz  |

| —      | Oscillation stability time                                                                                                                                                                              | Vcc = 5.0 V, Topr = 25°C                                                                                              | —      | 0.5      | 3      | ms   |

| —      | Self power consumption at oscillation                                                                                                                                                                   | Vcc = 5.0 V, Topr = 25°C                                                                                              | _      | 400      | _      | μΑ   |

#### Table 5.10 High-speed On-Chip Oscillator Circuit Electrical Characteristics

Notes:

1. Vcc = 1.8 V to 5.5 V, Topr =  $-20^{\circ}$ C to  $85^{\circ}$ C (N version), unless otherwise specified.

2. This enables the setting errors of bit rates such as 9600 bps and 38400 bps to be 0% when the serial interface is used in UART mode.

#### Table 5.11 Low-speed On-Chip Oscillator Circuit Electrical Characteristics

| Symbol | Parameter                              | Condition                            |      | Standard |      | Unit |

|--------|----------------------------------------|--------------------------------------|------|----------|------|------|

| Symbol | Falanielei                             | Condition                            | Min. | Тур.     | Max. | Unit |

| fOCO-S | Low-speed on-chip oscillator frequency |                                      | 60   | 125      | 250  | kHz  |

| —      | Oscillation stability time             | Vcc = 5.0 V, Topr = 25°C             | —    | 30       | 100  | μS   |

| —      | Self power consumption at oscillation  | $Vcc = 5.0 V$ , Topr = $25^{\circ}C$ | _    | 2        | _    | μΑ   |

Note:

1. Vcc = 1.8 V to 5.5 V, Topr =  $-20^{\circ}$ C to  $85^{\circ}$ C (N version), unless otherwise specified.

#### Table 5.12 Power Supply Circuit Timing Characteristics

| Symbol  | Parameter                                                                   | Condition |      | Standard |      | Unit |

|---------|-----------------------------------------------------------------------------|-----------|------|----------|------|------|

| Symbol  | i arameter                                                                  | Condition | Min. | Тур.     | Max. | Onit |

| td(P-R) | Time for internal power supply stabilization during power-on <sup>(2)</sup> |           |      | —        | 2000 | μs   |

Notes:

1. The measurement condition is Vcc = 1.8 V to 5.5 V and Topr =  $25^{\circ}$ C.

2. Waiting time until the internal power supply generation circuit stabilizes during power-on.

| Table 5.14 | Electrical Characteristics (2) [3.3 V $\leq$ Vcc $\leq$ 5.5 V]                      |

|------------|-------------------------------------------------------------------------------------|

|            | (Topr = $-20^{\circ}$ C to $85^{\circ}$ C (N version), unless otherwise specified.) |

| Symbol | Parameter                                                                                    |                                                                                                                                                                        | Condition                                                                                                                                                                                                     |      | Standar | d    | Unit |

|--------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|------|

| Symbol | i alametei                                                                                   |                                                                                                                                                                        | Condition                                                                                                                                                                                                     | Min. | Тур.    | Max. | Onit |

| Icc    | Power supply current<br>(Vcc = 3.3 V to 5.5 V)<br>Single-chip mode,<br>output pins are open, | High-speed<br>clock mode                                                                                                                                               | XIN = 20 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>No division                                                                                   | -    | 6.5     | 15   | mA   |

|        | other pins are Vss                                                                           |                                                                                                                                                                        | XIN = 16 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>No division                                                                                   | _    | 5.3     | 12.5 | mA   |

|        |                                                                                              |                                                                                                                                                                        | XIN = 10 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>No division                                                                                   | -    | 3.6     | —    | mA   |