# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                          |

| Number of I/O              | 39                                                             |

| Program Memory Size        | 15KB (15K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | 32 x 8                                                         |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 12x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 48-QFN (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f704-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

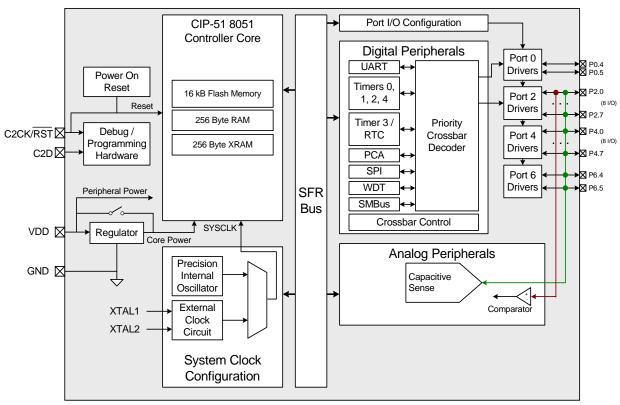

## C8051F70x/71x

Figure 1.8. C8051F717 Block Diagram

#### 10.3.2. Tracking Modes

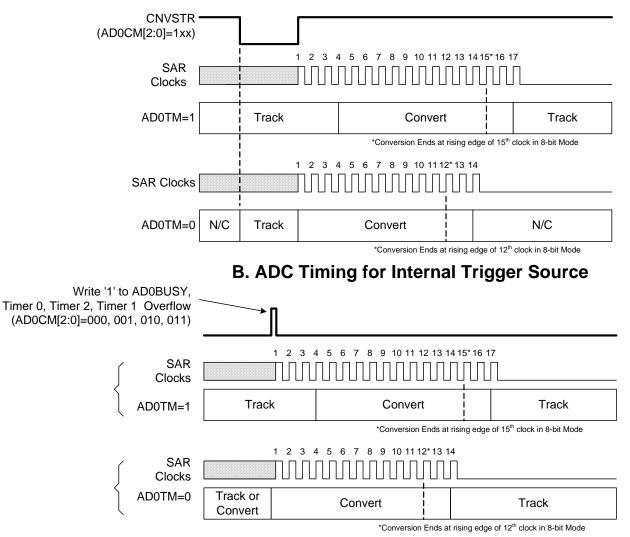

The AD0TM bit in register ADC0CN enables "delayed conversions", and will delay the actual conversion start by three SAR clock cycles, during which time the ADC will continue to track the input. If AD0TM is left at logic 0, a conversion will begin immediately, without the extra tracking time. For internal start-of-conversion sources, the ADC will track anytime it is not performing a conversion. When the CNVSTR signal is used to initiate conversions, ADC0 will track either when AD0TM is logic 1, or when AD0TM is logic 0 and CNVSTR is held low. See Figure 10.2 for track and convert timing details. Delayed conversion mode is useful when AMUX settings are frequently changed, due to the settling time requirements described in Section "10.3.3. Settling Time Requirements" on page 58.

Figure 10.2. 10-Bit ADC Track and Conversion Example Timing

## SFR Definition 12.1. REF0CN: Voltage Reference Control

| Bit   | 7 | 6 | 5      | 4     | 3   | 2     | 1     | 0 |

|-------|---|---|--------|-------|-----|-------|-------|---|

| Name  |   |   | REFGND | REFSL |     | TEMPE | BIASE |   |

| Туре  | R | R | R/W    | R/W   | R/W | R/W   | R/W   | R |

| Reset | 0 | 0 | 0      | 1     | 0   | 0     | 0     | 0 |

#### SFR Address = 0xD2; SFR Page = F

| Bit | Name   | Function                                                                           |

|-----|--------|------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                                                    |

| 5   | REFGND | Analog Ground Reference.                                                           |

|     |        | Selects the ADC0 ground reference.                                                 |

|     |        | 0: The ADC0 ground reference is the GND pin.                                       |

|     |        | 1: The ADC0 ground reference is the P0.1/AGND pin.                                 |

| 4:3 | REFSL  | Voltage Reference Select.                                                          |

|     |        | Selects the ADC0 voltage reference.                                                |

|     |        | 00: The ADC0 voltage reference is the P0.0/VREF pin.                               |

|     |        | 01: The ADC0 voltage reference is the VDD pin.                                     |

|     |        | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage.       |

|     |        | 11: The ADC0 voltage reference is the internal 1.6 V high-speed voltage reference. |

| 2   | TEMPE  | Temperature Sensor Enable.                                                         |

|     |        | Enables/Disables the internal temperature sensor.                                  |

|     |        | 0: Temperature Sensor Disabled.                                                    |

|     |        | 1: Temperature Sensor Enabled.                                                     |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.                                         |

|     |        | 0: Internal Bias Generator off.                                                    |

|     |        | 1: Internal Bias Generator on.                                                     |

| 0   | Unused | Read = 0b; Write = Don't Care.                                                     |

## SFR Definition 14.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5      | 4      | 3 | 2 | 1          | 0 |

|-------|---|---|--------|--------|---|---|------------|---|

| Name  |   |   | CP0RIE | CP0FIE |   |   | CP0MD[1:0] |   |

| Туре  | R | R | R/W    | R/W    | R | R | R/W        |   |

| Reset | 0 | 0 | 0      | 0      | 0 | 0 | 1          | 0 |

#### SFR Address = 0x9D; SFR Page = 0

| Bit | Name       | Function                                                                   |

|-----|------------|----------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = Don't Care.                                            |

| 5   | CP0RIE     | Comparator0 Rising-Edge Interrupt Enable.                                  |

|     |            | 0: Comparator0 Rising-edge interrupt disabled.                             |

|     |            | 1: Comparator0 Rising-edge interrupt enabled.                              |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.                                 |

|     |            | 0: Comparator0 Falling-edge interrupt disabled.                            |

|     |            | 1: Comparator0 Falling-edge interrupt enabled.                             |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                            |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.                                                   |

|     |            | These bits affect the response time and power consumption for Comparator0. |

|     |            | 00: Mode 0 (Fastest Response Time, Highest Power Consumption)              |

|     |            | 01: Mode 1                                                                 |

|     |            | 10: Mode 2                                                                 |

|     |            | 11: Mode 3 (Slowest Response Time, Lowest Power Consumption)               |

If CS0BUSY is used to initiate conversions, and then polled to determine if the conversion is finished, at least one clock cycle must be inserted between setting CS0BUSY to 1 and polling the CS0BUSY bit.

Conversions can be configured to be initiated continuously through one of two methods. CS0 can be configured to convert at a single channel continuously or it can be configured to convert continuously with auto-scan enabled. When configured to convert continuously, conversions will begin after the CS0BUSY bit in CS0CF has been set. An interrupt will be generated if CS0 conversion complete interrupts are enabled by setting the ECSCPT bit (EIE2.0).

The CS0 module uses a method of successive approximation to determine the value of an external capacitance. The number of bits the CS0 module converts is adjustable using the CS0CR bits in register CS0MD2. Conversions are 13 bits long by default, but they can be adjusted to 12, 13, 14, or 16 bits depending on the needs of the application. Unconverted bits will be set to 0. Shorter conversion lengths produce faster conversion rates, and vice-versa. Applications can take advantage of faster conversion rates when the unconverted bits fall below the noise floor.

**Note:** CS0 conversion complete interrupt behavior depends on the settings of the CS0 accumulator. If CS0 is configured to accumulate multiple conversions on an input channel, a CS0 conversion complete interrupt will be generated only after the last conversion completes.

### SFR Definition 15.10. CS0MD1: Capacitive Sense Mode 1

| Bit   | 7 | 6 | 5          | 4 | 3 | 2          | 1   | 0   |

|-------|---|---|------------|---|---|------------|-----|-----|

| Name  |   |   | CS0DR[1:0] |   |   | CS0CG[2:0] |     |     |

| Туре  | R |   | R/W        |   | R | R/W        | R/W | R/W |

| Reset | 0 | 0 | 0          | 0 | 0 | 1          | 1   | 1   |

#### SFR Address = 0xAD; SFR Page = 0

| Bit | Name                                                  | Description                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused                                                | Read = 00b; Write = Don't care                                                                                                                                                                                                                                                                                                                                                       |

| 5:4 | CS0DR[1:0]                                            | <b>CS0 Double Reset Select.</b><br>These bits adjust the secondary CS0 reset time. For most touch-sensitive switches, the default (fastest) value is sufficient, and these bits should not be modified.                                                                                                                                                                              |

|     |                                                       | 00: No additional time is used for secondary reset (recommended for most switches)                                                                                                                                                                                                                                                                                                   |

|     |                                                       | 01: An additional 0.75 µs is used for secondary reset.                                                                                                                                                                                                                                                                                                                               |

|     | 10: An additional 1.5 µs is used for secondary reset. |                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                                                       | 11: An additional 2.25 μs is used for secondary reset.                                                                                                                                                                                                                                                                                                                               |

| 3   | Unused                                                | Read = 0b; Write = Don't care                                                                                                                                                                                                                                                                                                                                                        |

| 2:0 | CS0CG[2:0]                                            | <b>CS0 Reference Gain Select.</b><br>These bits select the "gain" applied to the current used to charge an internal reference capacitor. Lower gain values decrease the current setting, and increase both the size of the capacitance that can be measured with the CS0 module, and the base conversion time. Refer to "15.2. CS0 Gain Adjustment" on page 81 for more information. |

|     |                                                       | 000: Gain = 1x                                                                                                                                                                                                                                                                                                                                                                       |

|     |                                                       | 001: Gain = 2x                                                                                                                                                                                                                                                                                                                                                                       |

|     |                                                       | 010: Gain = 3x                                                                                                                                                                                                                                                                                                                                                                       |

|     |                                                       | 011: Gain = 4x                                                                                                                                                                                                                                                                                                                                                                       |

|     |                                                       | 100: Gain = 5x                                                                                                                                                                                                                                                                                                                                                                       |

|     |                                                       | 101: Gain = 6x                                                                                                                                                                                                                                                                                                                                                                       |

|     |                                                       | 110: Gain = 7x                                                                                                                                                                                                                                                                                                                                                                       |

|     |                                                       | 111: Gain = 8x (default)                                                                                                                                                                                                                                                                                                                                                             |

## SFR Definition 18.2. EMI0CF: External Memory Configuration

| Bit   | 7 | 6 | 5 | 4    | 3   | 2             | 1    | 0     |

|-------|---|---|---|------|-----|---------------|------|-------|

| Name  |   |   |   | EMD2 | EMD | <b>[</b> 1:0] | EALE | [1:0] |

| Туре  |   | R |   |      |     | R/W           |      |       |

| Reset | 0 | 0 | 0 | 0    | 0   | 0             | 1    | 1     |

#### SFR Address = 0xC7; SFR Page = F

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused    | Read = 000b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | EMD2      | EMIF Multiplex Mode Select Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |           | 0: EMIF operates in multiplexed address/data mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           | 1: EMIF operates in non-multiplexed mode (separate address and data pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3:2 | EMD[1:0]  | EMIF Operating Mode Select Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |           | 00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to<br>on-chip memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |           | <ul> <li>01: Split Mode without Bank Select: Accesses below the 256 B boundary are directed on-chip. Accesses above the 256 B boundary are directed off-chip. 8-bit off-chip MOVX operations use current contents of the Address high port latches to resolve the upper address byte. To access off chip space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 256 B boundary are directed on-chip. Accesses above the 256 B boundary are directed off-chip. 8-bit off-chip MOVX operations uses the contents of EMI0CN to determine the high-byte of the address.</li> <li>11: External Only: MOVX accesses off-chip XRAM only. On-chip XRAM is not visible to the CPU.</li> </ul> |

| 1:0 | EALE[1:0] | ALE Pulse-Width Select Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |           | These bits only have an effect when $EMD2 = 0$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |           | 00: ALE high and ALE low pulse width = 1 SYSCLK cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |           | 01: ALE high and ALE low pulse width = 2 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |           | 10: ALE high and ALE low pulse width = 3 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |           | 11: ALE high and ALE low pulse width = 4 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### SFR Definition 21.4. EIE2: Extended Interrupt Enable 2

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |

|-------|---|---|---|---|---|---|--------|--------|

| Name  |   |   |   |   |   |   | ECSGRT | ECSCPT |

| Туре  | R | R | R | R | R | R | R/W    | R/W    |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0      |

#### SFR Address = 0xE7; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b; Write = don't care.                                                                                                                                                                       |

| 1   | ECSGRT | Enable Capacitive Sense Greater Than Comparator Interrupt.<br>0: Disable Capacitive Sense Greater Than Comparator interrupt.<br>1: Enable interrupt requests generated by CS0CMPF.                        |

| 0   | ECSCPT | <ul> <li>Enable Capacitive Sense Conversion Complete Interrupt.</li> <li>0: Disable Capacitive Sense Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by CS0INT.</li> </ul> |

## C8051F70x/71x

### SFR Definition 23.3. EECNTL: EEPROM Control

| Bit   | 7    | 6 | 5 | 4 | 3 | 2      | 1     | 0       |

|-------|------|---|---|---|---|--------|-------|---------|

| Name  | EEEN |   |   |   |   | EEREAD | EEWRT | AUTOINC |

| Туре  | R/W  |   | F | 2 |   |        | R/W   |         |

| Reset | 0    | 0 | 0 | 0 | 0 | 0      | 0     | 1       |

SFR Address = 0xC5; SFR Page = F

| Bit | Name     | Description                                                                |

|-----|----------|----------------------------------------------------------------------------|

| 7   | EEEN     | EEPROM Enable.                                                             |

|     |          | 0: EEPROM control logic disabled.                                          |

|     |          | 1: EEPROM control logic enabled. EEPROM reads and writes can be performed. |

| 6:4 | Reserved | Reserved. Read = variable; Write = Don't Care                              |

| 3   | Reserved | Reserved. Read = 0b, Write = 0                                             |

| 2   | EEREAD   | EEPROM 32-Byte Read.                                                       |

|     |          | 0: Does nothing.                                                           |

|     |          | 1: 32 bytes of EEPROM Data will be read from Flash to internal RAM.        |

| 1   | EEWRITE  | EEPROM 32-Byte Write.                                                      |

|     |          | 0: Does nothing.                                                           |

|     |          | 1: 32 bytes of EEPROM Data will be written from internal RAM to Flash.     |

| 0   | AUTOINC  | Auto Increment.                                                            |

|     |          | 0: Disable auto-increment.                                                 |

|     |          | 1: Enable auto-increment.                                                  |

## 24. Power Management Modes

The C8051F70x/71x devices have three software programmable power management modes: Idle, Stop, and Suspend. Idle mode and Stop mode are part of the standard 8051 architecture, while Suspend mode is an enhanced power-saving mode implemented by the high-speed oscillator peripheral.

Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Suspend mode is similar to Stop mode in that the internal oscillator and CPU are halted, but the device can wake on events such as a Port Mismatch, Comparator low output, or a Timer 3 overflow. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode and Suspend mode consume the least power because the majority of the device is shut down with no clocks active. SFR Definition 24.1 describes the Power Control Register (PCON) used to control the C8051F70x/71x's Stop and Idle power management modes. Suspend mode is controlled by the SUSPEND bit in the OSCICN register (SFR Definition 27.3).

Although the C8051F70x/71x has Idle, Stop, and Suspend modes available, more control over the device power can be achieved by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off oscillators lowers power consumption considerably, at the expense of reduced functionality.

#### 24.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the hardware to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

**Note:** If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Therefore, instructions that set the IDLE bit should be followed by an instruction that has two or more opcode bytes, for example:

| // in `C':<br>PCON  = 0x01;<br>PCON = PCON;        | <pre>// set IDLE bit // followed by a 3-cycle dummy instruction</pre> |

|----------------------------------------------------|-----------------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction           |

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "26. Watchdog Timer" on page 169 for more information on the use and configuration of the WDT.

#### 27.2. Programmable Internal High-Frequency (H-F) Oscillator

All C8051F70x/71x devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICL register as defined by SFR Definition 27.2.

On C8051F70x/71x devices, OSCICL is factory calibrated to obtain a 24.5 MHz base frequency.

The internal oscillator output frequency may be divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

The precision oscillator supports a spread spectrum mode which modulates the output frequency in order to reduce the EMI generated by the system. When enabled (SSE = 1), the oscillator output frequency is modulated by a stepped triangle wave whose frequency is equal to the oscillator frequency divided by 384 (63.8 kHz using the factory calibration). The maximum deviation from the center frequency is  $\pm 0.75\%$ . The output frequency updates occur every 32 cycles and the step size is typically 0.25% of the center frequency.

#### SFR Definition 27.2. OSCICL: Internal H-F Oscillator Calibration

| Bit   | 7           | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|-------------|--------|--------|--------|--------|--------|--------|--------|--|--|

| Name  | OSCICL[6:0] |        |        |        |        |        |        |        |  |  |

| Туре  | R/W         |        |        |        |        |        |        |        |  |  |

| Reset | Varies      | Varies | Varies | Varies | Varies | Varies | Varies | Varies |  |  |

|       |             |        |        |        |        |        |        |        |  |  |

#### SFR Address = 0xBF; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                   |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0 | OSCICL[7:0] | Internal Oscillator Calibration Bits.                                                                                                                                                                                                                                                                      |

|     |             | These bits determine the internal oscillator period. When set to 00000000b, the H-F oscillator operates at its fastest setting. When set to 11111111b, the H-F oscillator operates at its slowest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24.5 MHz. |

### SFR Definition 27.3. OSCICN: Internal H-F Oscillator Control

| Bit   | 7      | 6     | 5       | 4      | 3   | 2 | 1         | 0 |  |

|-------|--------|-------|---------|--------|-----|---|-----------|---|--|

| Name  | IOSCEN | IFRDY | SUSPEND | STSYNC | SSE |   | IFCN[1:0] |   |  |

| Туре  | R/W    | R     | R/W     | R      | R/W | R | R/W       |   |  |

| Reset | 1      | 1     | 0       | 0      | 0   | 0 | 0         | 0 |  |

#### SFR Address = 0xA9; SFR Page = F

| Bit | Name      | Function                                                                                                                                                                                                                                                                                              |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IOSCEN    | Internal H-F Oscillator Enable Bit.                                                                                                                                                                                                                                                                   |

|     |           | 0: Internal H-F Oscillator Disabled.                                                                                                                                                                                                                                                                  |

|     |           | 1: Internal H-F Oscillator Enabled.                                                                                                                                                                                                                                                                   |

| 6   | IFRDY     | Internal H-F Oscillator Frequency Ready Flag.                                                                                                                                                                                                                                                         |

|     |           | 0: Internal H-F Oscillator is not running at programmed frequency.                                                                                                                                                                                                                                    |

|     |           | 1: Internal H-F Oscillator is running at programmed frequency.                                                                                                                                                                                                                                        |

| 5   | SUSPEND   | Internal Oscillator Suspend Enable Bit.                                                                                                                                                                                                                                                               |

|     |           | Setting this bit to logic 1 places the internal oscillator in SUSPEND mode. The inter-<br>nal oscillator resumes operation when one of the SUSPEND mode awakening<br>events occurs.                                                                                                                   |

| 4   | STSYNC    | Suspend Timer Synchronization Bit.                                                                                                                                                                                                                                                                    |

|     |           | This bit is used to indicate when it is safe to read and write the registers associated with the suspend wake-up timer. If a suspend wake-up source other than Timer 3 has brought the oscillator out of suspend mode, it make take up to three timer clocks before the timer can be read or written. |

|     |           | 0: Timer 3 registers can be read safely.                                                                                                                                                                                                                                                              |

|     |           | 1: Timer 3 register reads and writes should not be performed.                                                                                                                                                                                                                                         |

| 3   | SSE       | Spread Spectrum Enable.                                                                                                                                                                                                                                                                               |

|     |           | Spread spectrum enable bit.                                                                                                                                                                                                                                                                           |

|     |           | 0: Spread Spectrum clock dithering disabled.                                                                                                                                                                                                                                                          |

|     |           | 1: Spread Spectrum clock dithering enabled.                                                                                                                                                                                                                                                           |

| 2   | Unused    | Read = 0b; Write = Don't Care                                                                                                                                                                                                                                                                         |

| 1:0 | IFCN[1:0] | Internal H-F Oscillator Frequency Divider Control Bits.                                                                                                                                                                                                                                               |

|     |           | 00: SYSCLK derived from Internal H-F Oscillator divided by 8.                                                                                                                                                                                                                                         |

|     |           | 01: SYSCLK derived from Internal H-F Oscillator divided by 4.                                                                                                                                                                                                                                         |

|     |           | 10: SYSCLK derived from Internal H-F Oscillator divided by 2.                                                                                                                                                                                                                                         |

|     |           | 11: SYSCLK derived from Internal H-F Oscillator divided by 1.                                                                                                                                                                                                                                         |

#### 28.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals.

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 28.8 for the PnMDIN register details.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a 0 to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to 1 enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Configuration Wizard utility of the Silicon Labs IDE software will determine the Port I/O pin-assignments based on the XBRn Register settings.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. Port output drivers are disabled while the Crossbar is disabled.

## C8051F70x/71x

## SFR Definition 28.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7       | 6     | 5   | 4   | 3    | 2 | 1           | 0   |  |

|-------|---------|-------|-----|-----|------|---|-------------|-----|--|

| Name  | WEAKPUD | XBARE | T1E | T0E | ECIE |   | PCA0ME[1:0] |     |  |

| Туре  | R/W     | R/W   | R/W | R/W | R/W  | R | R/W         | R/W |  |

| Reset | 0       | 0     | 0   | 0   | 0    | 0 | 0           | 0   |  |

### SFR Address = 0xE2; SFR Page = F

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | WEAKPUD     | Port I/O Weak Pullup Disable.                                                 |

|     |             | 0: Weak Pullups enabled (except for Ports whose I/O are configured for analog |

|     |             | mode).                                                                        |

|     |             | 1: Weak Pullups disabled.                                                     |

| 6   | XBARE       | Crossbar Enable.                                                              |

|     |             | 0: Crossbar disabled.                                                         |

|     |             | 1: Crossbar enabled.                                                          |

| 5   | T1E         | T1 Enable.                                                                    |

|     |             | 0: T1 unavailable at Port pin.                                                |

|     |             | 1: T1 routed to Port pin.                                                     |

| 4   | T0E         | T0 Enable.                                                                    |

|     |             | 0: T0 unavailable at Port pin.                                                |

|     |             | 1: T0 routed to Port pin.                                                     |

| 3   | ECIE        | PCA0 External Counter Input Enable.                                           |

|     |             | 0: ECI unavailable at Port pin.                                               |

|     |             | 1: ECI routed to Port pin.                                                    |

| 2   | Unused      | Read = 0b; Write = Don't Care.                                                |

| 1:0 | PCA0ME[1:0] | PCA Module I/O Enable Bits.                                                   |

|     |             | 00: All PCA I/O unavailable at Port pins.                                     |

|     |             | 01: CEX0 routed to Port pin.                                                  |

|     |             | 10: CEX0, CEX1 routed to Port pins.                                           |

|     |             | 11: CEX0, CEX1, CEX2 routed to Port pins.                                     |

#### **30.1. Supporting Documents**

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I<sup>2</sup>C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification—Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification—Version 1.1, SBS Implementers Forum.

#### **30.2. SMBus Configuration**

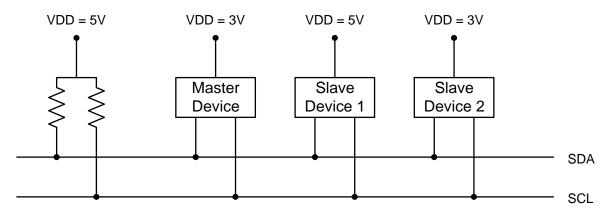

Figure 30.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pullup resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 30.2. Typical SMBus Configuration

#### 30.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. It is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Bytes that are received (by a master or slave) are acknowledged (ACK) with a low SDA during a high SCL (see Figure 30.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

The direction bit (R/W) occupies the least-significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

#### 30.4.4. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

#### SFR Definition 30.5. SMB0DAT: SMBus Data

| Bit                              | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------------------------------|--------------|---|---|---|---|---|---|---|--|--|

| Name                             | SMB0DAT[7:0] |   |   |   |   |   |   |   |  |  |

| Туре                             | R/W          |   |   |   |   |   |   |   |  |  |

| Reset                            | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR Address = 0xC2; SFR Page = 0 |              |   |   |   |   |   |   |   |  |  |

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SMB0DAT[7:0] | SMBus Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | The SMB0DAT register contains a byte of data to be transmitted on the SMBus serial interface or a byte that has just been received on the SMBus serial interface. The CPU can read from or write to this register whenever the SI serial interrupt flag (SMB0CN.0) is set to logic 1. The serial data in the register remains stable as long as the SI flag is set. When the SI flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register. |

| Table 30.5. SMBus Status Decoding: Hardware ACK Disabled | (EHACK = 0) | (Continued)                             |  |

|----------------------------------------------------------|-------------|-----------------------------------------|--|

|                                                          |             | ( • • • • • • • • • • • • • • • • • • • |  |

|                   | Valu             | ies                        | Rea     | d                                            |                                                                                             |                                                            |     | lues<br>Vrit |      | tus<br>ected                   |

|-------------------|------------------|----------------------------|---------|----------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|--------------|------|--------------------------------|

| Mode              | Status<br>Vector | ACKRQ                      | ARBLOST | ACK                                          | Current SMbus State                                                                         | Typical Response Options                                   | STA | STO          | ACK  | Next Status<br>Vector Expected |

| r                 |                  | 0                          | 0       | 0                                            | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).             | 0   | 0            | Х    | 0001                           |

| smitte            | 0100             | 0                          | 0       | 1                                            | A slave byte was transmitted;<br>ACK received.                                              | Load SMB0DAT with next data byte to transmit.              | 0   | 0            | Х    | 0100                           |

| Slave Transmitter |                  | 0                          | 1       | х                                            | A Slave byte was transmitted; error detected.                                               | No action required (expecting Master to end transfer).     | 0   | 0            | Х    | 0001                           |

| Slav              | 0101             | 0                          | x       | x                                            | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                 | 0   | 0            | Х    | _                              |

|                   |                  |                            |         |                                              |                                                                                             | If Write, Acknowledge received address                     | 0   | 0            | 1    | 0000                           |

|                   |                  | 1                          | 0       | Х                                            | A slave address + R/W was received; ACK requested.                                          | If Read, Load SMB0DAT with data byte; ACK received address | 0   | 0            | 1    | 0100                           |

|                   |                  |                            |         |                                              |                                                                                             | NACK received address.                                     | 0   | 0            | 0    | _                              |

|                   | 0010             |                            |         |                                              |                                                                                             | If Write, Acknowledge received address                     | 0   | 0            | 1    | 0000                           |

| iver              |                  | 1                          | 1       | х                                            | Lost arbitration as master;<br>slave address + R/W received;                                | If Read, Load SMB0DAT with data byte; ACK received address | 0   | 0            | 1    | 0100                           |

| tece              |                  |                            |         |                                              | ACK requested.                                                                              | NACK received address.                                     | 0   | 0            | 0    | _                              |

| Slave Receiver    |                  |                            |         |                                              |                                                                                             | Reschedule failed transfer;<br>NACK received address.      | 1   | 0            | 0    | 1110                           |

|                   | 0001             | 0                          | 0       | x                                            | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver.       | Clear STO.                                                 | 0   | 0            | Х    | —                              |

|                   |                  | 1                          | 1       | х                                            | Lost arbitration while attempt-<br>ing a STOP.                                              | No action required (transfer complete/aborted).            | 0   | 0            | 0    | —                              |

|                   | 0000             | A slave byte was received; |         | A slave byte was received;<br>ACK requested. | Acknowledge received byte;<br>Read SMB0DAT.                                                 | 0                                                          | 0   | 1            | 0000 |                                |

|                   |                  |                            |         |                                              |                                                                                             | NACK received byte.                                        | 0   | 0            | 0    | —                              |

1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

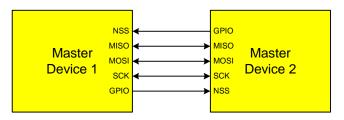

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 31.2 shows a connection diagram between two master devices in multiple-master mode.

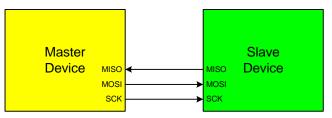

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 31.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 31.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

Figure 31.2. Multiple-Master Mode Connection Diagram

Figure 31.3. 3-Wire Single Master and Single Slave Mode Connection Diagram

#### 33.2.2. 8-bit Timers with Auto-Reload

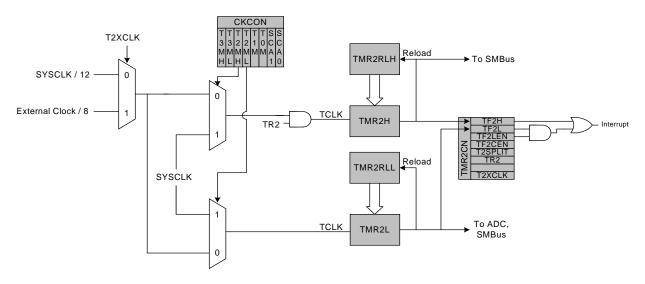

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 33.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 33.5. Timer 2 8-Bit Mode Block Diagram

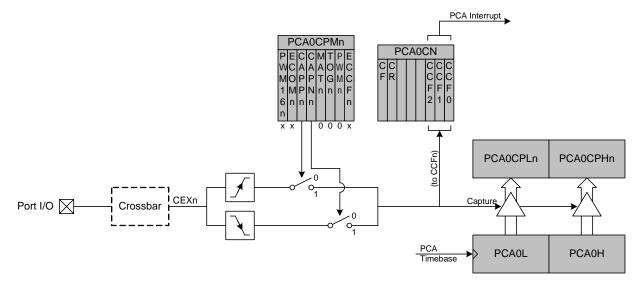

#### 34.3.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or fall-ing-edge caused the capture.

Figure 34.4. PCA Capture Mode Diagram

**Note:** The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.