# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 39                                                              |

| Program Memory Size        | 15KB (15K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | 32 x 8                                                          |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f704-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 16.1.1. Instruction and CPU Timing                                 | 99  |

|--------------------------------------------------------------------|-----|

| 16.2. CIP-51 Register Descriptions                                 |     |

| 17. Memory Organization                                            |     |

| 17.1. Program Memory                                               |     |

| 17.1.1. MOVX Instruction and Program Memory                        |     |

| 17.2. EEPROM Memory                                                |     |

| 17.3. Data Memory                                                  |     |

| 17.3.1. Internal RAM                                               |     |

| 17.3.1.1. General Purpose Registers                                |     |

| 17.3.1.2. Bit Addressable Locations                                |     |

| 17.3.1.3. Stack                                                    |     |

| 18. External Data Memory Interface and On-Chip XRAM                |     |

| 18.1. Accessing XRAM                                               |     |

| 18.1.1. 16-Bit MOVX Example                                        |     |

| 18.1.2. 8-Bit MOVX Example                                         |     |

| 18.2. Configuring the External Memory Interface                    |     |

| 18.3. Port Configuration                                           | 112 |

| 18.4. Multiplexed and Non-multiplexed Selection                    |     |

| 18.4.1. Multiplexed Configuration                                  |     |

| 18.4.2. Non-multiplexed Configuration                              | 116 |

| 18.5. Memory Mode Selection                                        |     |

| 18.5.1. Internal XRAM Only                                         | 117 |

| 18.5.2. Split Mode without Bank Select                             |     |

| 18.5.3. Split Mode with Bank Select                                |     |

| 18.5.4. External Only                                              |     |

| 18.6. Timing                                                       |     |

| 18.6.1. Non-Multiplexed Mode                                       | 120 |

| 18.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111              | 120 |

| 18.6.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111 | 121 |

| 18.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110           | 122 |

| 18.6.2. Multiplexed Mode                                           | 123 |

| 18.6.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011              | 123 |

| 18.6.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011 | 124 |

| 18.6.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010           | 125 |

| 19. In-System Device Identification                                | 128 |

| 20. Special Function Registers                                     | 130 |

| 21. Interrupts                                                     | 137 |

| 21.1. MCU Interrupt Sources and Vectors                            | 138 |

| 21.1.1. Interrupt Priorities                                       | 138 |

| 21.1.2. Interrupt Latency                                          | 138 |

| 21.2. Interrupt Register Descriptions                              | 140 |

| 21.3. INTO and INT1 External Interrupts                            | 146 |

| 22. Flash Memory                                                   | 148 |

| 22.1. Programming The Flash Memory                                 |     |

| 22.1.1. Flash Lock and Key Functions                               | 148 |

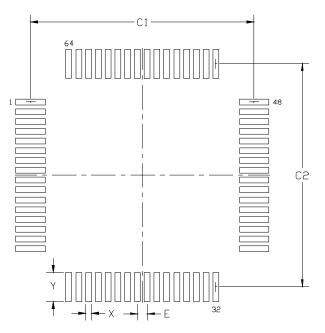

Figure 4.2. TQFP-64 PCB Land Pattern

#### Table 4.2. TQFP-64 PCB Land Pattern Dimensions

| Dimension | Min   | Мах   |

|-----------|-------|-------|

| C1        | 11.30 | 11.40 |

| C2        | 11.30 | 11.40 |

| E         | 0.50  | BSC   |

| X         | 0.20  | 0.30  |

| Y         | 1.40  | 1.50  |

Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This land pattern design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

#### Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

Card Assembly

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### Table 9.14. Comparator Electrical Characteristics

$V_{DD}$  = 3.0 V, –40 to +85 °C unless otherwise noted.

| Parameter                                         | Conditions             | Min   | Тур  | Max                    | Units |

|---------------------------------------------------|------------------------|-------|------|------------------------|-------|

| Response Time:                                    | CP0+ - CP0- = 100 mV   |       | 300  |                        | ns    |

| Mode 0, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  | _     | 200  | _                      | ns    |

| Response Time:                                    | CP0+ – CP0– = 100 mV   |       | 400  | _                      | ns    |

| Mode 1, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  | _     | 350  | _                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV   | _     | 570  | _                      | ns    |

| Mode 2, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  |       | 870  | _                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV   |       | 1500 |                        | ns    |

| Mode 3, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  | _     | 4500 | _                      | ns    |

| Common-Mode Rejection Ratio                       |                        |       | 1    | 4                      | mV/V  |

| Positive Hysteresis 1                             | Mode 2, CP0HYP1–0 = 00 | _     | 0    | 1                      | mV    |

| Positive Hysteresis 2                             | Mode 2, CP0HYP1–0 = 01 | 2     | 5    | 10                     | mV    |

| Positive Hysteresis 3                             | Mode 2, CP0HYP1–0 = 10 | 7     | 10   | 20                     | mV    |

| Positive Hysteresis 4                             | Mode 2, CP0HYP1–0 = 11 | 10    | 20   | 30                     | mV    |

| Negative Hysteresis 1                             | Mode 2, CP0HYN1–0 = 00 | —     | 0    | 1                      | mV    |

| Negative Hysteresis 2                             | Mode 2, CP0HYN1–0 = 01 | 2     | 5    | 10                     | mV    |

| Negative Hysteresis 3                             | Mode 2, CP0HYN1–0 = 10 | 7     | 10   | 20                     | mV    |

| Negative Hysteresis 4                             | Mode 2, CP0HYN1–0 = 11 | 10    | 20   | 30                     | mV    |

| Inverting or Non-Inverting Input<br>Voltage Range |                        | -0.25 | _    | V <sub>DD</sub> + 0.25 | V     |

| Input Offset Voltage                              |                        | -7.5  | _    | 7.5                    | mV    |

| Power Specifications                              |                        |       |      |                        |       |

| Power Supply Rejection                            |                        | _     | 0.1  | _                      | mV/V  |

| Powerup Time                                      |                        | —     | 10   | —                      | μs    |

| Supply Current at DC                              | Mode 0                 | —     | 25   |                        | μA    |

|                                                   | Mode 1                 | —     | 10   | _                      | μA    |

|                                                   | Mode 2                 | —     | 3    | —                      | μA    |

|                                                   | Mode 3                 | —     | 0.5  | —                      | μA    |

| Note: Vcm is the common-mode vol                  | tage on CP0+ and CP0–. |       |      |                        |       |

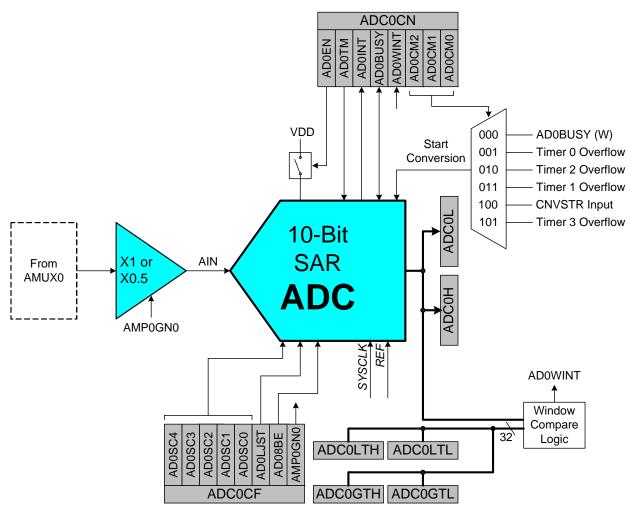

## 10. 10-Bit ADC (ADC0)

ADC0 on the C8051F700/2/4/6/8 and C8051F710/2/4/6 is a 500 ksps, 10-bit successive-approximationregister (SAR) ADC with integrated track-and-hold, a gain stage programmable to 1x or 0.5x, and a programmable window detector. The ADC is fully configurable under software control via Special Function Registers. The ADC may be configured to measure various different signals using the analog multiplexer described in Section "10.5. ADC0 Analog Multiplexer" on page 65. The voltage reference for the ADC is selected as described in Section "11. Temperature Sensor" on page 67. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

Figure 10.1. ADC0 Functional Block Diagram

#### 12.1. External Voltage References

To use an external voltage reference, REFSL[1:0] should be set to 00. Bypass capacitors should be added as recommended by the manufacturer of the external voltage reference.

#### 12.2. Internal Voltage Reference Options

A 1.6 V high-speed reference is included on-chip. The high speed internal reference is selected by setting REFSL[1:0] to 11. When selected, the high-speed internal reference will be automatically enabled on an as-needed basis by ADC0.

For applications with a non-varying power supply voltage, using the power supply as the voltage reference can provide ADC0 with added dynamic range at the cost of reduced power supply noise rejection. To use the 1.8 to 3.6 V power supply voltage ( $V_{DD}$ ) or the 1.8 V regulated digital supply voltage as the reference source, REFSL[1:0] should be set to 01 or 10, respectively.

#### 12.3. Analog Ground Reference

To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for ADC0 is taken from the P0.1/AGND pin. Any external sensors sampled by ADC0 should be referenced to the P0.1/AGND pin. The separate analog ground reference option is enabled by setting REFGND to 1. Note that when using this option, P0.1/AGND must be connected to the same potential as GND.

#### 12.4. Temperature Sensor Enable

The TEMPE bit in register REF0CN enables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

## SFR Definition 12.1. REF0CN: Voltage Reference Control

| Bit   | 7 | 6 | 5      | 4   | 3   | 2     | 1     | 0 |

|-------|---|---|--------|-----|-----|-------|-------|---|

| Name  |   |   | REFGND | REI | FSL | TEMPE | BIASE |   |

| Туре  | R | R | R/W    | R/W | R/W | R/W   | R/W   | R |

| Reset | 0 | 0 | 0      | 1   | 0   | 0     | 0     | 0 |

#### SFR Address = 0xD2; SFR Page = F

| Bit | Name   | Function                                                                           |

|-----|--------|------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                                                    |

| 5   | REFGND | Analog Ground Reference.                                                           |

|     |        | Selects the ADC0 ground reference.                                                 |

|     |        | 0: The ADC0 ground reference is the GND pin.                                       |

|     |        | 1: The ADC0 ground reference is the P0.1/AGND pin.                                 |

| 4:3 | REFSL  | Voltage Reference Select.                                                          |

|     |        | Selects the ADC0 voltage reference.                                                |

|     |        | 00: The ADC0 voltage reference is the P0.0/VREF pin.                               |

|     |        | 01: The ADC0 voltage reference is the VDD pin.                                     |

|     |        | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage.       |

|     |        | 11: The ADC0 voltage reference is the internal 1.6 V high-speed voltage reference. |

| 2   | TEMPE  | Temperature Sensor Enable.                                                         |

|     |        | Enables/Disables the internal temperature sensor.                                  |

|     |        | 0: Temperature Sensor Disabled.                                                    |

|     |        | 1: Temperature Sensor Enabled.                                                     |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.                                         |

|     |        | 0: Internal Bias Generator off.                                                    |

|     |        | 1: Internal Bias Generator on.                                                     |

| 0   | Unused | Read = 0b; Write = Don't Care.                                                     |

### SFR Definition 15.1. CS0CN: Capacitive Sense Control

| Bit   | 7     | 6      | 5      | 4       | 3        | 2 | 1 | 0       |

|-------|-------|--------|--------|---------|----------|---|---|---------|

| Name  | CS0EN | CS0PME | CS0INT | CS0BUSY | CS0CMPEN |   |   | CS0CMPF |

| Туре  | R/W   | R/W    | R/W    | R/W     | R/W      | R | R | R       |

| Reset | 0     | 0      | 0      | 0       | 0        | 0 | 0 | 0       |

#### SFR Address = 0x9A; SFR Page = 0

| Bit | Name     | Description                                                                                                                                                                                            |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CS0EN    | CS0 Enable.                                                                                                                                                                                            |

|     |          | 0: CS0 disabled and in low-power mode.                                                                                                                                                                 |

|     |          | 1: CS0 enabled and ready to convert.                                                                                                                                                                   |

| 6   | CS0PME   | CS0 Pin Monitor Event.                                                                                                                                                                                 |

|     |          | Set if any converter re-try requests have occurred due to a pin monitor event. This bit remains set until cleared by firmware.                                                                         |

| 5   | CS0INT   | CS0 Interrupt Flag.                                                                                                                                                                                    |

|     |          | 0: CS0 has not completed a data conversion since the last time CS0INT was cleared.                                                                                                                     |

|     |          | 1: CS0 has completed a data conversion.                                                                                                                                                                |

|     |          | This bit is not automatically cleared by hardware.                                                                                                                                                     |

| 4   | CS0BUSY  | CS0 Busy.                                                                                                                                                                                              |

|     |          | Read:                                                                                                                                                                                                  |

|     |          | 0: CS0 conversion is complete or a conversion is not currently in progress.                                                                                                                            |

|     |          | 1: CS0 conversion is in progress.<br>Write:                                                                                                                                                            |

|     |          | 0: No effect.                                                                                                                                                                                          |

|     |          | 1: Initiates CS0 conversion if CS0CM[2:0] = 000b, 110b, or 111b.                                                                                                                                       |

| 3   | CS0CMPEN | CS0 Digital Comparator Enable Bit.                                                                                                                                                                     |

|     |          | Enables the digital comparator, which compares accumulated CS0 conversion<br>output to the value stored in CS0THH:CS0THL.<br>0: CS0 digital comparator disabled.<br>1: CS0 digital comparator enabled. |

| 2:1 | Unused   | Read = 00b; Write = Don't care                                                                                                                                                                         |

| 0   | CS0CMPF  | CS0 Digital Comparator Interrupt Flag.                                                                                                                                                                 |

|     |          | 0: CS0 result is smaller than the value set by CS0THH and CS0THL since the last time CS0CMPF was cleared.                                                                                              |

|     |          | 1: CS0 result is greater than the value set by CS0THH and CS0THL since the last time CS0CMPF was cleared.                                                                                              |

### SFR Definition 15.9. CS0PM: Capacitive Sense Pin Monitor

| Bit   | 7    | 6     | 5     | 4     | 3     | 2     | 1           | 0 |

|-------|------|-------|-------|-------|-------|-------|-------------|---|

| Name  | UAPM | SPIPM | SMBPM | PCAPM | PIOPM | CP0PM | CSPMMD[1:0] |   |

| Туре  | R/W  | R/W   | R/W   | R/W   | R/W   | R/W   | R/W         |   |

| Reset | 0    | 0     | 0     | 0     | 0     | 0     | 0           | 0 |

SFR Address = 0x9F; SFR Page = F

| Bit | Name        | Description                                                          |

|-----|-------------|----------------------------------------------------------------------|

| 7   | UAPM        | UART Pin Monitor Enable.                                             |

|     |             | Enables monitoring of the UART TX pin.                               |

| 6   | SPIPM       | SPI Pin Monitor Enable.                                              |

|     |             | Enables monitoring SPI output pins.                                  |

| 5   | SMBPM       | SMBus Pin Monitor Enable.                                            |

|     |             | Enables monitoring of the SMBus pins.                                |

| 4   | PCAPM       | PCA Pin Monitor Enable.                                              |

|     |             | Enables monitoring of PCA output pins.                               |

| 3   | PIOPM       | Port I/O Pin Monitor Enable.                                         |

|     |             | Enables monitoring of writes to the port latch registers.            |

| 2   | CP0PM       | CP0 Pin Monitor Enable.                                              |

|     |             | Enables monitoring of the comparator CP0 (synchronous) output.       |

| 1:0 | CSPMMD[1:0] | CS0 Pin Monitor Mode.                                                |

|     |             | Selects the operation to take when a monitored signal changes state. |

|     |             | 00: Always retry bit cycles on a pin state change.                   |

|     |             | 01: Retry up to twice on consecutive bit cycles.                     |

|     |             | 10: Retry up to four times on consecutive bit cycles.                |

|     |             | 11: Reserved.                                                        |

| Mnemonic             | Description                                         | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

| ANL C, bit           | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |

| JC rel               | Jump if Carry is set                                | 2     | 2/3             |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/3             |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/4             |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/4             |

| JBC bit, rel         | Jump if direct bit is set and clear bit             | 3     | 3/4             |

| Program Branching    |                                                     |       |                 |

| ACALL addr11         | Absolute subroutine call                            | 2     | 3               |

| LCALL addr16         | Long subroutine call                                | 3     | 4               |

| RET                  | Return from subroutine                              | 1     | 5               |

| RETI                 | Return from interrupt                               | 1     | 5               |

| AJMP addr11          | Absolute jump                                       | 2     | 3               |

| LJMP addr16          | Long jump                                           | 3     | 4               |

| SJMP rel             | Short jump (relative address)                       | 2     | 3               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 3               |

| JZ rel               | Jump if A equals zero                               | 2     | 2/3             |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 4/5             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/4             |

| NOP                  | No operation                                        | 1     | 1               |

Table 16.1. CIP-51 Instruction Set Summary (Continued)

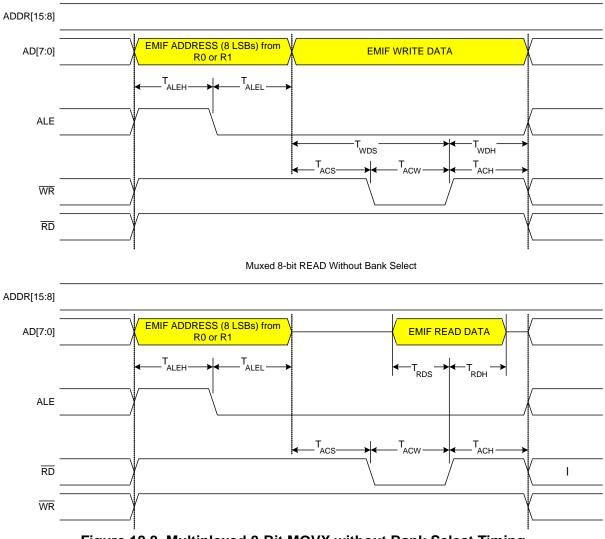

#### 18.6.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011

Muxed 8-bit WRITE Without Bank Select

Figure 18.8. Multiplexed 8-Bit MOVX without Bank Select Timing

#### 21.1. MCU Interrupt Sources and Vectors

The C8051F70x/71x MCUs support 16 interrupt sources. Software can simulate an interrupt by setting an interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 21.1. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 21.1.1. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP or EIP1) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 21.1.

#### 21.1.2. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

unlocked pages, and user firmware executing on locked pages. Table 22.1 summarizes the Flash security features of the C8051F70x/71x devices.

| Action                                                                        | C2 Debug      | User Firmware executing from: |               |  |  |

|-------------------------------------------------------------------------------|---------------|-------------------------------|---------------|--|--|

|                                                                               | Interface     | an unlocked page              | a locked page |  |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)           | Permitted     | Permitted                     | Permitted     |  |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)             | Not Permitted | FEDR                          | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)           | Permitted     | Permitted                     | Permitted     |  |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)            | Not Permitted | FEDR                          | Permitted     |  |  |

| Read contents of Lock Byte<br>(if no pages are locked)                        | Permitted     | Permitted                     | Permitted     |  |  |

| Read contents of Lock Byte<br>(if any page is locked)                         | Not Permitted | FEDR                          | Permitted     |  |  |

| Erase page containing Lock Byte<br>(if no pages are locked)                   | Permitted     | FEDR                          | FEDR          |  |  |

| Erase page containing Lock Byte - Unlock all pages<br>(if any page is locked) | Only by C2DE  | FEDR                          | FEDR          |  |  |

| Lock additional pages<br>(change '1's to '0's in the Lock Byte)               | Not Permitted | FEDR                          | FEDR          |  |  |

| Unlock individual pages<br>(change '0's to '1's in the Lock Byte)             | Not Permitted | FEDR                          | FEDR          |  |  |

| Read, Write or Erase Reserved Area                                            | Not Permitted | FEDR                          | FEDR          |  |  |

Table 22.1. Flash Security Summary

C2DE - C2 Device Erase (Erases all Flash pages including the page containing the Lock Byte) FEDR - Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset)

All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

#### 22.4. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of VDD, system clock frequency, or temperature. This accidental execution of Flash modifying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

To help prevent the accidental modification of Flash by firmware, the VDD Monitor must be enabled and enabled as a reset source on C8051F70x/71x devices for the Flash to be successfully modified. If either the VDD Monitor or the VDD Monitor reset source is not enabled, a Flash Error Device Reset will be generated when the firmware attempts to modify the Flash.

#### 24.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the controller core to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the device performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ s.

#### 24.3. Suspend Mode

Suspend mode allows a system running from the internal oscillator to go to a very low power state similar to Stop mode, but the processor can be awakened by certain events without requiring a reset of the device. Setting the SUSPEND bit (OSCICN.5) causes the hardware to halt the CPU and the high-frequency internal oscillator, and go into Suspend mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. Most digital peripherals are not active in Suspend mode. The exception to this is the Port Match feature and Timer 3, when it is run from an external oscillator source.

Note that the clock divider bits CLKDIV[2:0] in register CLKSEL must be set to "divide by 1" when entering Suspend mode.

Suspend mode can be terminated by five types of events, a port match (described in Section "28.5. Port Match" on page 192), a Timer 3 overflow (described in Section "33.3. Timer 3" on page 278), a comparator low output (if enabled), a capacitive sense greater-than comparator interrupt, or a device reset event. In order to run Timer 3 in Suspend mode, the timer must be configured to clock from the external clock source/8. When Suspend mode is terminated, the device will continue execution on the instruction following the one that set the SUSPEND bit. If the wake event (port match or Timer 3 overflow) was configured to generate an interrupt, the interrupt will be serviced upon waking the device. If Suspend mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

Note: The device will still enter Suspend mode if a wake source is "pending", and the device will not wake on such pending sources. It is important to ensure that the intended wake source will trigger after the device enters Suspend mode. For example, if a CS0 conversion completes and the interrupt fires before the device is in Suspend mode, that interrupt cannot trigger the wake event. Because port match events are level-sensitive, pre-existing port match events will trigger a wake, as long as the match condition is still present when the device enters Suspend.

### SFR Definition 28.15. P1SKIP: Port 1 Skip

| Bit   | 7           | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------|-----------------|---|---|---|---|---|---|--|--|

| Name  | P1SKIP[7:0] |                 |   |   |   |   |   |   |  |  |

| Туре  |             | R/W             |   |   |   |   |   |   |  |  |

| Reset | 0           | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

#### SFR Address = 0xD5; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                                                                                                                              |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[7:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                     |

|     |             | These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins<br>used for analog, special functions or GPIO should be skipped by the Crossbar.<br>0: Corresponding P1.n pin is not skipped by the Crossbar.<br>1: Corresponding P1.n pin is skipped by the Crossbar. |

#### SFR Definition 28.16. P1DRV: Port 1 Drive Strength

| Bit   | 7          | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|-----------------|---|---|---|---|---|---|--|--|

| Name  | P1DRV[7:0] |                 |   |   |   |   |   |   |  |  |

| Туре  | R/W        |                 |   |   |   |   |   |   |  |  |

| Reset | 0          | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

#### SFR Address = 0xFA; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |

### SFR Definition 28.31. P5MDIN: Port 5 Input Mode

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-----------------|---|---|---|---|---|---|---|--|--|

| Name  | P5MDIN[7:0]     |   |   |   |   |   |   |   |  |  |

| Туре  | R/W             |   |   |   |   |   |   |   |  |  |

| Reset | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |   |  |  |

#### SFR Address = 0xF6; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P5MDIN[7:0] | Analog Configuration Bits for P5.7–P5.0 (respectively).                                                                                                                 |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled.<br>0: Corresponding P5.n pin is configured for analog mode. |

|     |             | 1: Corresponding P5.n pin is not configured for analog mode.                                                                                                            |

#### SFR Definition 28.32. P5MDOUT: Port 5 Output Mode

| Bit   | 7            | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------|-----------------|---|---|---|---|---|---|--|--|

| Name  | P5MDOUT[7:0] |                 |   |   |   |   |   |   |  |  |

| Туре  | R/W          |                 |   |   |   |   |   |   |  |  |

| Reset | 0            | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |

#### SFR Address = 0x9B; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P5MDOUT[7:0] | Output Configuration Bits for P5.7–P5.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P5MDIN is logic 0.<br>0: Corresponding P5.n Output is open-drain.<br>1: Corresponding P5.n Output is push-pull. |

### SFR Definition 32.1. SCON0: Serial Port 0 Control

| Bit   | 7          | 6                                                                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                          | 3             | 2               | 1               | 0          |  |  |  |

|-------|------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------|-----------------|-----------------|------------|--|--|--|

| Nam   | e S0MOD    | E                                                                                                | MCE0                                                                                                                                                                                                                                                                                                                                                                                                                  | REN0                       | TB80          | RB80            | TI0             | RI0        |  |  |  |

| Туре  | R/W        | R                                                                                                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W                        | R/W           | R/W             | R/W             | R/W        |  |  |  |

| Rese  | <b>t</b> 0 | 1                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                          | 0             | 0               | 0               | 0          |  |  |  |

| SFR A | ddress = 0 | x98; SFR Page                                                                                    | = All Pages                                                                                                                                                                                                                                                                                                                                                                                                           | ; Bit-Addres               | sable         |                 | I               | 11         |  |  |  |

| Bit   | Name       |                                                                                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                              |                            |               |                 |                 |            |  |  |  |

| 7     | SOMODE     | Selects the U/<br>0: 8-bit UART                                                                  | Serial Port 0 Operation Mode.<br>Selects the UART0 Operation Mode.<br>0: 8-bit UART with Variable Baud Rate.<br>1: 9-bit UART with Variable Baud Rate.                                                                                                                                                                                                                                                                |                            |               |                 |                 |            |  |  |  |

| 6     | Unused     | Read = 1b, W                                                                                     | rite = Don't (                                                                                                                                                                                                                                                                                                                                                                                                        | Care.                      |               |                 |                 |            |  |  |  |

| 5     | MCE0       | The function of <b>Mode 0: Chee</b><br>0: Logic level<br>1: RI0 will only<br><b>Mode 1: Mult</b> | <ul> <li>Multiprocessor Communication Enable.</li> <li>The function of this bit is dependent on the Serial Port 0 Operation Mode:</li> <li>Mode 0: Checks for valid stop bit.</li> <li>0: Logic level of stop bit is ignored.</li> <li>1: RI0 will only be activated if stop bit is logic level 1.</li> <li>Mode 1: Multiprocessor Communications Enable.</li> <li>0: Logic level of ninth bit is ignored.</li> </ul> |                            |               |                 |                 |            |  |  |  |

| 4     | REN0       | Receive Enat<br>0: UART0 rec<br>1: UART0 rec                                                     | eption disab                                                                                                                                                                                                                                                                                                                                                                                                          |                            |               |                 |                 |            |  |  |  |

| 3     | TB80       | Ninth Transm                                                                                     | ission Bit.                                                                                                                                                                                                                                                                                                                                                                                                           |                            |               |                 |                 |            |  |  |  |

|       |            | The logic leve<br>(Mode 1). Unu                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |               | ansmission b    | oit in 9-bit UA | ART Mode   |  |  |  |

| 2     | RB80       | Ninth Receive                                                                                    | e Bit.                                                                                                                                                                                                                                                                                                                                                                                                                |                            |               |                 |                 |            |  |  |  |

|       |            | RB80 is assig<br>9th data bit in                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       | e of the STC               | OP bit in Moo | de 0; it is ass | igned the va    | lue of the |  |  |  |

| 1     | TI0        | Transmit Inte                                                                                    | rrupt Flag.                                                                                                                                                                                                                                                                                                                                                                                                           |                            |               |                 |                 |            |  |  |  |

|       |            | in 8-bit UART<br>the UART0 int                                                                   | Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bit in 8-bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the UART0 interrupt is enabled, setting this bit causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software.                                                                               |                            |               |                 |                 |            |  |  |  |

| 0     | RI0        | Receive Inter                                                                                    | • •                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |               |                 |                 |            |  |  |  |

|       |            | Set to 1 by ha<br>STOP bit sam<br>causes the CF<br>cleared manua                                 | pling time).<br>U to vector                                                                                                                                                                                                                                                                                                                                                                                           | When the UA<br>to the UART | ART0 interru  | pt is enabled   | I, setting this | s bit to 1 |  |  |  |

### SFR Definition 33.2. TCON: Timer Control

| Bit   | 7            | 6                                                                                                                                                                             | 5                                                                                                                                                                                                                                                                                                         | 4                   | 3        | 2                                          | 1   | 0   |  |  |

|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|--------------------------------------------|-----|-----|--|--|

|       |              | TR1                                                                                                                                                                           | TF0                                                                                                                                                                                                                                                                                                       | TR0                 | IE1      | IT1                                        | IE0 | IT0 |  |  |

| Name  |              |                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                           |                     |          |                                            |     |     |  |  |

| Туре  | R/W          | R/W                                                                                                                                                                           | R/W                                                                                                                                                                                                                                                                                                       | R/W                 | R/W      | R/W                                        | R/W | R/W |  |  |

| Rese  | <b>t</b> 0   | 0                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                         | 0                   | 0        | 0                                          | 0   | 0   |  |  |

| SFR A | ddress = 0x8 | 8; SFR Page                                                                                                                                                                   | = All Pages                                                                                                                                                                                                                                                                                               | ; Bit-Addres        | sable    |                                            |     |     |  |  |

| Bit   | Name         |                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                           |                     | Function |                                            |     |     |  |  |

| 7     | TF1          | Timer 1 Ov                                                                                                                                                                    | Timer 1 Overflow Flag.                                                                                                                                                                                                                                                                                    |                     |          |                                            |     |     |  |  |

|       |              | -                                                                                                                                                                             | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                                                                                             |                     |          |                                            |     |     |  |  |

| 6     | TR1          | Timer 1 Ru                                                                                                                                                                    | n Control.                                                                                                                                                                                                                                                                                                |                     |          |                                            |     |     |  |  |

|       |              | Timer 1 is e                                                                                                                                                                  | nabled by se                                                                                                                                                                                                                                                                                              | etting this bit     | to 1.    |                                            |     |     |  |  |

| 5     | TF0          | Timer 0 Ov                                                                                                                                                                    | erflow Flag                                                                                                                                                                                                                                                                                               |                     |          |                                            |     |     |  |  |

|       |              | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine. |                                                                                                                                                                                                                                                                                                           |                     |          |                                            |     |     |  |  |

| 4     | TR0          | Timer 0 Ru                                                                                                                                                                    | n Control.                                                                                                                                                                                                                                                                                                |                     |          |                                            |     |     |  |  |

|       |              | Timer 0 is enabled by setting this bit to 1.                                                                                                                                  |                                                                                                                                                                                                                                                                                                           |                     |          |                                            |     |     |  |  |

| 3     | IE1          | External Int                                                                                                                                                                  | terrupt 1.                                                                                                                                                                                                                                                                                                |                     |          |                                            |     |     |  |  |

|       |              | can be clear                                                                                                                                                                  | ed by softwa                                                                                                                                                                                                                                                                                              | are but is au       |          | of type defin<br>leared when<br>ered mode. |     |     |  |  |

| 2     | IT1          | Interrupt 1                                                                                                                                                                   | Type Select                                                                                                                                                                                                                                                                                               | t.                  |          |                                            |     |     |  |  |

|       |              |                                                                                                                                                                               | figured activ<br>on 21.7).<br>evel triggere                                                                                                                                                                                                                                                               | ve low or hig<br>d. |          | errupt will be<br>PL bit in the            |     |     |  |  |

| 1     | IE0          | External Int                                                                                                                                                                  | terrupt 0.                                                                                                                                                                                                                                                                                                |                     |          |                                            |     |     |  |  |

|       |              | can be clear                                                                                                                                                                  | ed by softwa                                                                                                                                                                                                                                                                                              | are but is au       |          | of type defin<br>leared when<br>ered mode. |     |     |  |  |

| 0     | IT0          | Interrupt 0                                                                                                                                                                   | Type Select                                                                                                                                                                                                                                                                                               | t.                  |          |                                            |     |     |  |  |

|       |              | INT0 is conf<br>Definition 2 <sup>2</sup><br>0: INT0 is le                                                                                                                    | Interrupt 0 Type Select.<br><u>This bit selects whether the configured INT0 interrupt will be edge or level sensitive.</u><br>INT0 is configured active low or high by the IN0PL bit in register IT01CF (see SFR<br>Definition 21.7).<br>0: <u>INT0</u> is level triggered.<br>1: INT0 is edge triggered. |                     |          |                                            |     |     |  |  |

## SFR Definition 33.9. TMR2RLL: Timer 2 Reload Register Low Byte

| Bit   | 7              | 6                                             | 5     | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|----------------|-----------------------------------------------|-------|---|---|---|---|---|--|--|--|

| Nam   | e              | TMR2RLL[7:0]                                  |       |   |   |   |   |   |  |  |  |

| Туре  | •              | R/W                                           |       |   |   |   |   |   |  |  |  |

| Rese  | et 0           | 0                                             | 0     | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR A | Address = 0xCA | ; SFR Page                                    | e = 0 |   |   |   |   |   |  |  |  |

| Bit   | Name           | Function                                      |       |   |   |   |   |   |  |  |  |

| 7:0   | TMR2RLL[7:0    | MR2RLL[7:0] Timer 2 Reload Register Low Byte. |       |   |   |   |   |   |  |  |  |

TMR2RLL holds the low byte of the reload value for Timer 2.

### SFR Definition 33.10. TMR2RLH: Timer 2 Reload Register High Byte

| Bit                              | 7    | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------------------------------|------|--------------|---|---|---|---|---|---|--|--|

| Name                             | 9    | TMR2RLH[7:0] |   |   |   |   |   |   |  |  |

| Туре                             | •    | R/W          |   |   |   |   |   |   |  |  |

| Rese                             | t 0  | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR Address = 0xCB; SFR Page = 0 |      |              |   |   |   |   |   |   |  |  |

| Bit                              | Name |              |   |   |   |   |   |   |  |  |

| Dit | Hamo                                            | i dilotioni                                                  |  |  |  |  |

|-----|-------------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| 7:0 | TMR2RLH[7:0] Timer 2 Reload Register High Byte. |                                                              |  |  |  |  |

|     |                                                 | TMR2RLH holds the high byte of the reload value for Timer 2. |  |  |  |  |

## C2 Register Definition 35.2. DEVICEID: C2 Device ID

| Bit   | 7            | 6                                                                          | 5          | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|--------------|----------------------------------------------------------------------------|------------|---|---|---|---|---|--|--|--|

| Nam   | e            | DEVICEID[7:0]                                                              |            |   |   |   |   |   |  |  |  |

| Туре  | e            | R/W                                                                        |            |   |   |   |   |   |  |  |  |

| Rese  | et O         | 0                                                                          | 0          | 1 | 1 | 1 | 1 | 0 |  |  |  |

| C2 Ad | dress: 0x00  |                                                                            |            |   |   | L |   | L |  |  |  |

| Bit   | Name         |                                                                            | Function   |   |   |   |   |   |  |  |  |

| 7:0   | DEVICEID[7:0 | ] Device II                                                                | Device ID. |   |   |   |   |   |  |  |  |

|       |              | This read-only register returns the 8-bit device ID: 0x1E (C8051F70x/71x). |            |   |   |   |   |   |  |  |  |

### C2 Register Definition 35.3. REVID: C2 Revision ID

| Bit              | 7          | 6                                                                                      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|------------------|------------|----------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|

| Nam              | е          | REVID[7:0]                                                                             |        |        |        |        |        |        |  |  |  |

| Туре             | e          | R/W                                                                                    |        |        |        |        |        |        |  |  |  |

| Rese             | et Varies  | Varies                                                                                 | Varies | Varies | Varies | Varies | Varies | Varies |  |  |  |

| C2 Address: 0x01 |            |                                                                                        |        |        |        |        |        |        |  |  |  |

| Bit              | Name       | Name Function                                                                          |        |        |        |        |        |        |  |  |  |

| 7:0              | REVID[7:0] | :0] Revision ID.                                                                       |        |        |        |        |        |        |  |  |  |

|                  |            | This read-only register returns the 8-bit revision ID. For example: 0x00 = Revision A. |        |        |        |        |        |        |  |  |  |