# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                            |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                          |

| Number of I/O              | 39                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 12x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 48-QFN (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f706-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 34.3. PCA0PWM: PCA PWM Configuration              | 297 |

|------------------------------------------------------------------|-----|

| SFR Definition 34.4. PCA0CPMn: PCA Capture/Compare Mode          |     |

| SFR Definition 34.5. PCA0L: PCA Counter/Timer Low Byte           |     |

| SFR Definition 34.6. PCA0H: PCA Counter/Timer High Byte          | 299 |

| SFR Definition 34.7. PCA0CPLn: PCA Capture Module Low Byte       | 300 |

| SFR Definition 34.8. PCA0CPHn: PCA Capture Module High Byte      | 300 |

| C2 Register Definition 35.1. C2ADD: C2 Address                   | 301 |

| C2 Register Definition 35.2. DEVICEID: C2 Device ID              | 302 |

| C2 Register Definition 35.3. REVID: C2 Revision ID               |     |

| C2 Register Definition 35.4. FPCTL: C2 Flash Programming Control | 303 |

| C2 Register Definition 35.5. FPDAT: C2 Flash Programming Data    | 303 |

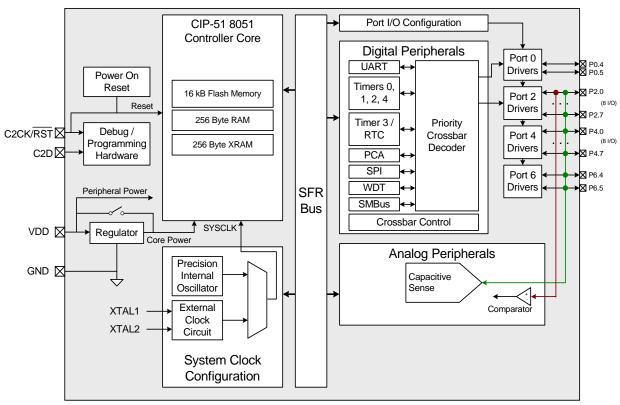

Figure 1.8. C8051F717 Block Diagram

### Table 9.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameters          | Conditions                                   | Min                    | Тур                   | Мах | Units |

|---------------------|----------------------------------------------|------------------------|-----------------------|-----|-------|

| Output High Voltage | High Drive Strength                          |                        |                       |     |       |

|                     | I <sub>OH</sub> = −3 mA, Port I/O push-pull  | V <sub>DD</sub> – 0.7  | —                     | —   | V     |

|                     | I <sub>OH</sub> = –10 μA, Port I/O push-pull | V <sub>DD</sub> – 0.1  | —                     | —   | V     |

|                     | I <sub>OH</sub> = –10 mA, Port I/O push-pull | —                      | V <sub>DD</sub> – 0.8 | —   | V     |

|                     | Low Drive Strength                           |                        |                       |     |       |

|                     | I <sub>OH</sub> = −1 mA, Port I/O push-pull  | V <sub>DD</sub> – 0.7  | —                     | —   | V     |

|                     | I <sub>OH</sub> = –10 μA, Port I/O push-pull | V <sub>DD</sub> – 0.1  | —                     | —   | V     |

|                     | I <sub>OH</sub> = –3 mA, Port I/O push-pull  | —                      | V <sub>DD</sub> – 0.8 | —   | V     |

| Output Low Voltage  | High Drive Strength                          |                        |                       |     |       |

|                     | l <sub>OL</sub> = 8.5 mA                     | —                      | —                     | 0.6 | V     |

|                     | I <sub>OL</sub> = 10 μA                      | —                      | —                     | 0.1 | V     |

|                     | I <sub>OL</sub> = 25 mA                      | —                      | 1.0                   | —   | V     |

|                     | Low Drive Strength                           |                        |                       |     |       |

|                     | I <sub>OL</sub> = 1.4 mA                     | —                      | —                     | 0.6 | V     |

|                     | I <sub>OL</sub> = 10 μA                      | —                      | —                     | 0.1 | V     |

|                     | I <sub>OL</sub> = 4 mA                       | —                      | 1.0                   | —   | V     |

| Input High Voltage  |                                              | 0.75 x V <sub>DD</sub> | _                     | _   | V     |

| Input Low Voltage   |                                              | —                      | _                     | 0.6 | V     |

| Input Leakage       | Weak Pullup Off                              | -1                     | —                     | 1   | μA    |

| Current             | Weak Pullup On, V <sub>IN</sub> = 0 V        |                        | 25                    | 50  | μA    |

### **Table 9.4. Reset Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V, -40 to +85 °C unless otherwise specified.

| Parameter                                             | Conditions                                                                            | Min                       | Тур  | Max                   | Units    |

|-------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------|------|-----------------------|----------|

| RST Output Low Voltage                                | I <sub>OL</sub> = 8.5 mA,<br>V <sub>DD</sub> = 1.8 V to 3.6 V                         | —                         |      | 0.6                   | V        |

| RST Input High Voltage                                |                                                                                       | $0.75 \mathrm{~x~V_{DD}}$ |      | _                     | V        |

| RST Input Low Voltage                                 |                                                                                       | _                         |      | 0.3 x V <sub>DD</sub> | $V_{DD}$ |

| RST Input Pullup Current                              | RST = 0.0 V                                                                           |                           | 25   | 50                    | μA       |

| V <sub>DD</sub> POR Ramp Time                         |                                                                                       | —                         | _    | 1                     | ms       |

| V <sub>DD</sub> Monitor Threshold (V <sub>RST</sub> ) |                                                                                       | 1.7                       | 1.75 | 1.8                   | V        |

| Missing Clock Detector<br>Timeout                     | Time from last system clock rising edge to reset initiation                           | 100                       | 500  | 1000                  | μs       |

| Reset Time Delay                                      | Delay between release of any<br>reset source and code<br>execution at location 0x0000 | _                         | _    | 30                    | μs       |

| Minimum RST Low Time to<br>Generate a System Reset    |                                                                                       | 15                        | _    | —                     | μs       |

| V <sub>DD</sub> Monitor Turn-on Time                  | V <sub>DD</sub> = V <sub>RST</sub> – 0.1 V                                            |                           | 50   |                       | μs       |

| V <sub>DD</sub> Monitor Supply Current                |                                                                                       | _                         | 25   | 30                    | μA       |

## SFR Definition 10.7. ADC0LTH: ADC0 Less-Than Data High Byte

| Bit   | 7             | 6            | 5                                        | 4 | 3 | 2 | 1 | 0 |

|-------|---------------|--------------|------------------------------------------|---|---|---|---|---|

| Nam   | e             | ADC0LTH[7:0] |                                          |   |   |   |   |   |

| Туре  | 9             | R/W          |                                          |   |   |   |   |   |

| Rese  | et 0          | 0            | 0                                        | 0 | 0 | 0 | 0 | 0 |

| SFR A | Address = 0xC | 6; SFR Page  | e = 0                                    |   |   |   |   |   |

| Bit   | Name          |              | Function                                 |   |   |   |   |   |

| 7:0   | ADC0LTH[7:0   | )] ADC0 Le   | DC0 Less-Than Data Word High-Order Bits. |   |   |   |   |   |

## SFR Definition 10.8. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit   | 7              | 6            | 5                                       | 4 | 3 | 2 | 1 | 0 |  |

|-------|----------------|--------------|-----------------------------------------|---|---|---|---|---|--|

| Nam   | e              | ADC0LTL[7:0] |                                         |   |   |   |   |   |  |

| Туре  | R/W            |              |                                         |   |   |   |   |   |  |

| Rese  | et O           | 0            | 0                                       | 0 | 0 | 0 | 0 | 0 |  |

| SFR A | Address = 0xC5 | ; SFR Page   | e = 0                                   |   |   |   |   |   |  |

| Bit   | Name           |              | Function                                |   |   |   |   |   |  |

| 7:0   | ADC0LTL[7:0    | ADC0 Le      | DC0 Less-Than Data Word Low-Order Bits. |   |   |   |   |   |  |

## SFR Definition 12.1. REF0CN: Voltage Reference Control

| Bit   | 7 | 6 | 5      | 4     | 3   | 2     | 1     | 0 |

|-------|---|---|--------|-------|-----|-------|-------|---|

| Name  |   |   | REFGND | REFSL |     | TEMPE | BIASE |   |

| Туре  | R | R | R/W    | R/W   | R/W | R/W   | R/W   | R |

| Reset | 0 | 0 | 0      | 1     | 0   | 0     | 0     | 0 |

### SFR Address = 0xD2; SFR Page = F

| Bit | Name   | Function                                                                           |

|-----|--------|------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                                                    |

| 5   | REFGND | Analog Ground Reference.                                                           |

|     |        | Selects the ADC0 ground reference.                                                 |

|     |        | 0: The ADC0 ground reference is the GND pin.                                       |

|     |        | 1: The ADC0 ground reference is the P0.1/AGND pin.                                 |

| 4:3 | REFSL  | Voltage Reference Select.                                                          |

|     |        | Selects the ADC0 voltage reference.                                                |

|     |        | 00: The ADC0 voltage reference is the P0.0/VREF pin.                               |

|     |        | 01: The ADC0 voltage reference is the VDD pin.                                     |

|     |        | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage.       |

|     |        | 11: The ADC0 voltage reference is the internal 1.6 V high-speed voltage reference. |

| 2   | TEMPE  | Temperature Sensor Enable.                                                         |

|     |        | Enables/Disables the internal temperature sensor.                                  |

|     |        | 0: Temperature Sensor Disabled.                                                    |

|     |        | 1: Temperature Sensor Enabled.                                                     |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.                                         |

|     |        | 0: Internal Bias Generator off.                                                    |

|     |        | 1: Internal Bias Generator on.                                                     |

| 0   | Unused | Read = 0b; Write = Don't Care.                                                     |

### 18.4. Multiplexed and Non-multiplexed Selection

The External Memory Interface is capable of acting in a Multiplexed mode or a Non-multiplexed mode, depending on the state of the EMD2 (EMI0CF.4) bit.

#### 18.4.1. Multiplexed Configuration

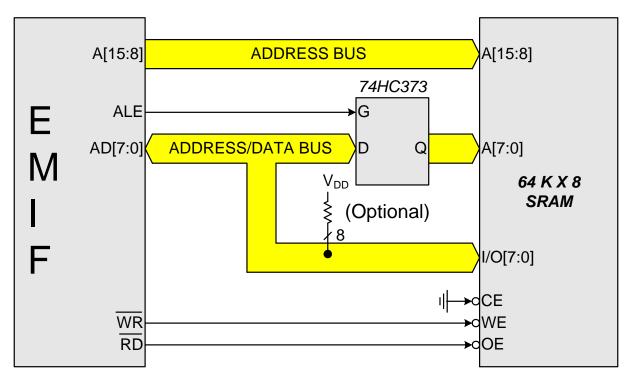

In Multiplexed mode, the Data Bus and the lower 8-bits of the Address Bus share the same Port pins: AD[7:0]. In this mode, an external latch (74HC373 or equivalent logic gate) is used to hold the lower 8-bits of the RAM address. The external latch is controlled by the ALE (Address Latch Enable) signal, which is driven by the External Memory Interface logic. An example of a Multiplexed Configuration is shown in Figure 18.1.

In Multiplexed mode, the external MOVX operation can be broken into two phases delineated by the state of the ALE signal. During the first phase, ALE is high and the lower 8-bits of the Address Bus are presented to AD[7:0]. During this phase, the address latch is configured such that the Q outputs reflect the states of the 'D' inputs. When ALE falls, signaling the beginning of the second phase, the address latch outputs remain fixed and are no longer dependent on the latch inputs. Later in the second phase, the Data Bus controls the state of the AD[7:0] port at the time RD or WR is asserted.

See Section "18.6.2. Multiplexed Mode" on page 123 for more information.

Figure 18.1. Multiplexed Configuration Example

## **19. In-System Device Identification**

The C8051F70x/71x has SFRs that identify the device family and derivative. These SFRs can be read by firmware at runtime to determine the capabilities of the MCU that is executing code. This allows the same firmware image to run on MCUs with different memory sizes and peripherals, and dynamically changing functionality to suit the capabilities of that MCU.

In order for firmware to identify the MCU, it must read three SFRs. HWID describes the MCU's family, DERIVID describes the specific derivative within that device family, and REVID describes the hardware revision of the MCU.

### SFR Definition 19.1. HWID: Hardware Identification Byte

| Bit   | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-----------|---|---|---|---|---|---|--|

| Name  |   | HWID[7:0] |   |   |   |   |   |   |  |

| Туре  | R | R         | R | R | R | R | R | R |  |

| Reset | 0 | 0         | 0 | 1 | 1 | 1 | 1 | 0 |  |

#### SFR Address = 0xC4; SFR Page = F

| Bit | Name      | Description                                                                         |

|-----|-----------|-------------------------------------------------------------------------------------|

| 7:0 | HWID[7:0] | Hardware Identification Byte.                                                       |

|     |           | Describes the MCU family.<br>0x1E: Devices covered in this document (C8051F70x/71x) |

### SFR Definition 19.2. DERIVID: Derivative Identification Byte

| Bit   | 7      | 6            | 5      | 4      | 3      | 2      | 1      | 0      |  |

|-------|--------|--------------|--------|--------|--------|--------|--------|--------|--|

| Name  |        | DERIVID[7:0] |        |        |        |        |        |        |  |

| Туре  | R      | R            | R      | R      | R      | R      | R      | R      |  |

| Reset | Varies | Varies       | Varies | Varies | Varies | Varies | Varies | Varies |  |

SFR Address = 0xEC; SFR Page = F

| Bit | Name         | Description                                                        |

|-----|--------------|--------------------------------------------------------------------|

| 7:0 | DERIVID[7:0] | Derivative Identification Byte.                                    |

|     |              | Shows the C8051F70x/71x derivative being used.                     |

|     |              | 0xD0: C8051F700; 0xD1: C8051F701; 0xD2: C8051F702; 0xD3: C8051F703 |

|     |              | 0xD4: C8051F704; 0xD5: C8051F705; 0xD6: C8051F706; 0xD7: C8051F707 |

|     |              | 0xD8: C8051F708; 0xD9: C8051F709; 0xDA: C8051F710; 0xDB: C8051F711 |

|     |              | 0xDC: C8051F712; 0xDD: C8051F713; 0xDE: C8051F714; 0xDF: C8051F715 |

|     |              | 0xE0: C8051F716; 0xE1: C8051F717                                   |

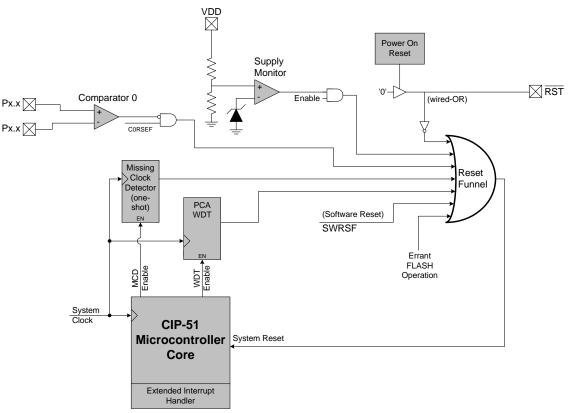

## 25. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source. Program execution begins at location 0x0000.

Figure 25.1. Reset Sources

## 27. Oscillators and Clock Selection

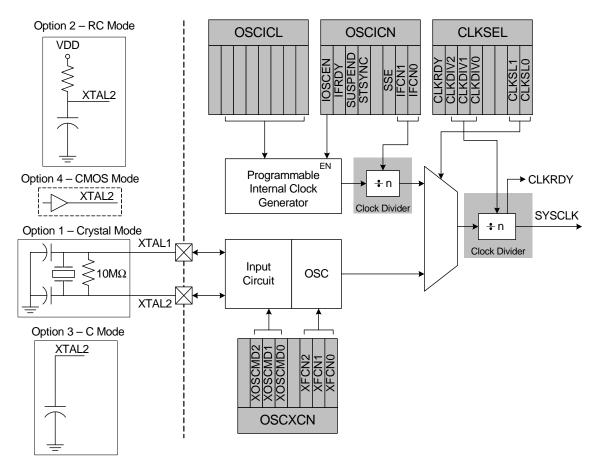

C8051F70x/71x devices include a programmable internal high-frequency oscillator and an external oscillator drive circuit. The internal high-frequency oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 27.1. The system clock can be sourced by the external oscillator circuit or the internal oscillator (default). The internal oscillator offers a selectable post-scaling feature, which is initially set to divide the clock by 8.

Figure 27.1. Oscillator Options

### 27.1. System Clock Selection

The system clock source for the MCU can be selected using the CLKSEL register. The clock selected as the system clock can be divided by 1, 2, 4, 8, 16, 32, 64, or 128. When switching between two clock divide values, the transition may take up to 128 cycles of the undivided clock source. The CLKRDY flag can be polled to determine when the new clock divide value has been applied. The clock divider must be set to "divide by 1" when entering Suspend mode. The system clock source may also be switched on-the-fly. The switchover takes effect after one clock period of the slower oscillator.

### 27.3. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 27.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 27.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 27.4).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see Section "28.3. Priority Crossbar Decoder" on page 185 for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See Section "28.4. Port I/O Initialization" on page 189 for details on Port input mode selection.

## SFR Definition 28.17. P2: Port 2

| Bit   | 7 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

|-------|---|-----------------|--|--|--|--|--|--|--|

| Name  |   | P2[7:0]         |  |  |  |  |  |  |  |

| Туре  |   | R/W             |  |  |  |  |  |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 1 |  |  |  |  |  |  |  |

SFR Address = 0xA0; SFR Page = All Pages; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------|

| 7:0 | P2[7:0] | <b>Port 2 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. |       | 0: P2.n Port pin is logic<br>LOW.<br>1: P2.n Port pin is logic<br>HIGH. |

### SFR Definition 28.18. P2MDIN: Port 2 Input Mode

| Bit   | 7 | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|----|---|---|---|---|--|

| Name  |   | P2MDIN[7:0]     |   |    |   |   |   |   |  |

| Туре  |   |                 |   | R/ | W |   |   |   |  |

| Reset | 1 | 1 1 1 1 1 1 1 1 |   |    |   |   |   |   |  |

### SFR Address = 0xF3; SFR Page = F

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDIN[7:0] | Analog Configuration Bits for P2.7–P2.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P2.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P2.n pin is not configured for analog mode.                                                |

### SFR Definition 28.19. P2MDOUT: Port 2 Output Mode

| Bit   | 7 | 6               | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|----|---|---|---|---|--|

| Name  |   | P2MDOUT[7:0]    |   |    |   |   |   |   |  |

| Туре  |   |                 |   | R/ | W |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |    |   |   |   |   |  |

#### SFR Address = 0xA6; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDOUT[7:0] | Output Configuration Bits for P2.7–P2.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P2MDIN is logic 0.<br>0: Corresponding P2.n Output is open-drain.<br>1: Corresponding P2.n Output is push-pull. |

### SFR Definition 28.20. P2SKIP: Port 2 Skip

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|---|---|---|---|---|--|

| Name  |   | P2SKIP[7:0]     |   |   |   |   |   |   |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |

SFR Address = 0xD6; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2SKIP[3:0] | Port 2 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 2 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P2.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P2.n pin is skipped by the Crossbar.</li> </ul> |

### SFR Definition 28.33. P5DRV: Port 5 Drive Strength

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|---|---|---|---|---|--|

| Name  |   | P5DRV[7:0]      |   |   |   |   |   |   |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |

SFR Address = 0xFE; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P5DRV[7:0] | Drive Strength Configuration Bits for P5.7–P5.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P5.n Output has low output drive strength.<br>1: Corresponding P5.n Output has high output drive strength. |

### SFR Definition 28.34. P6: Port 6

| Bit   | 7 | 6 | 5       | 4         | 3 | 2 | 1 | 0 |

|-------|---|---|---------|-----------|---|---|---|---|

| Name  |   |   | P6[5:0] |           |   |   |   |   |

| Туре  | R | R |         | R/W       |   |   |   |   |

| Reset | 0 | 0 | 1       | 1 1 1 1 1 |   |   |   |   |

SFR Address = 0xB2; SFR Page = All Pages

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:6 | Unused  | Read = 00b; Write = Don't Ca                                                                                                                  | re                                                                            |                                                                         |

| 5:0 | P6[5:0] | <b>Port 6 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P6.n Port pin is logic<br>LOW.<br>1: P6.n Port pin is logic<br>HIGH. |

## SFR Definition 30.4. SMB0ADM: SMBus Slave Address Mask

| Bit   | 7         | 6 | 5 | 4 | 3 | 2 | 1     | 0   |

|-------|-----------|---|---|---|---|---|-------|-----|

| Name  | SLVM[6:0] |   |   |   |   |   | EHACK |     |

| Туре  | R/W       |   |   |   |   |   |       | R/W |

| Reset | 1         | 1 | 1 | 1 | 1 | 1 | 1     | 0   |

### SFR Address = 0xBB; SFR Page = F

| Bit | Name      | Function                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:1 | SLVM[6:0] | SMBus Slave Address Mask.                                                                                                                                                                                                                                                          |  |  |  |  |

|     |           | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM[6:0] enables comparisons with the corresponding bit in SLV[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |  |  |  |  |

| 0   | EHACK     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                       |  |  |  |  |

|     |           | <ul><li>Enables hardware acknowledgement of slave address and received data bytes.</li><li>0: Firmware must manually acknowledge all incoming address and data bytes.</li><li>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.</li></ul>                |  |  |  |  |

### 31.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

### 31.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 31.5. For slave mode, the clock and data relationships are shown in Figure 31.6 and Figure 31.7. CKPHA should be set to 0 on both the master and slave SPI when communicating between two Silicon Labs C8051 devices.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 31.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e., half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

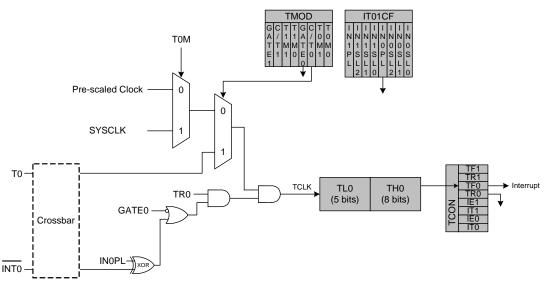

Figure 33.1. T0 Mode 0 Block Diagram

### 33.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

### 33.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 in the TCON register is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 in the TMOD register is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "21.3. INT0 and INT1 External Interrupts" on page 146 for details on the external input signals INT0 and INT1).

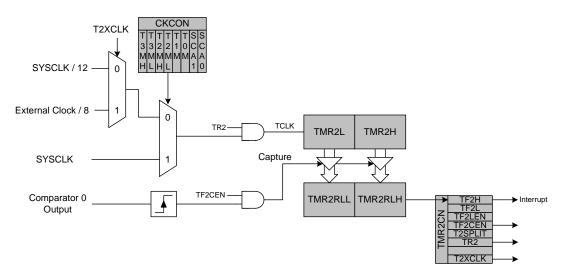

### 33.2.3. Comparator 0 Capture Mode

The capture mode in Timer 2 allows Comparator 0 rising edges to be captured with the timer clocking from the system clock or the system clock divided by 12. Timer 2 capture mode is enabled by setting TF2CEN to 1 and T2SPLIT to 0.

When capture mode is enabled, a capture event will be generated on every Comparator 0 rising edge. When the capture event occurs, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set (triggering an interrupt if Timer 2 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 0 period can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading.

This mode allows software to determine the time between consecutive Comparator 0 rising edges, which can be used for detecting changes in the capacitance of a capacitive switch, or measuring the frequency of a low-level analog signal.

Figure 33.6. Timer 2 Capture Mode Block Diagram

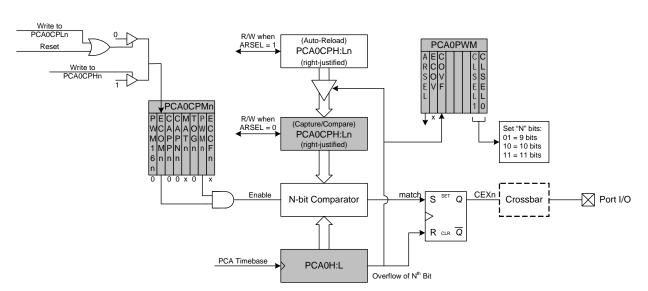

### 34.3.5.2. 9/10/11-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 9/10/11-bit PWM mode should be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA0CPHn and PCA0CPLn register locations. The data written to define the duty cycle should be right-justified in the registers. The auto-reload registers are accessed (read or written) when the bit ARSEL in PCA0PWM is set to 1. The capture/compare registers are accessed when ARSEL is set to 0.

When the least-significant N bits of the PCA0 counter match the value in the associated module's capture/compare register (PCA0CPn), the output on CEXn is asserted high. When the counter overflows from the Nth bit, CEXn is asserted low (see Figure 34.9). Upon an overflow from the Nth bit, the COVF flag is set, and the value stored in the module's auto-reload register is loaded into the capture/compare register. The value of N is determined by the CLSEL bits in register PCA0PWM.

The 9, 10 or 11-bit PWM mode is selected by setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to the desired cycle length (other than 8-bits). If the MATn bit is set to 1, the CCFn flag for the module will be set each time a comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 512 (9-bit), 1024 (10-bit) or 2048 (11-bit) PCA clock cycles. The duty cycle for 9/10/11-Bit PWM Mode is given in Equation 34.2, where N is the number of bits in the PWM cycle.

**Important Note About PCA0CPHn and PCA0CPLn Registers**: When writing a 16-bit value to the PCA0CPn registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(2^N - PCA0CPn)}{2^N}$$

Equation 34.3. 9, 10, and 11-Bit PWM Duty Cycle

A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 34.9. PCA 9, 10 and 11-Bit PWM Mode Diagram

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

### http://www.silabs.com