# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                          |

| Number of I/O              | 39                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 12x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f706-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Mnemonic             | Description                                                              | Bytes | Clock<br>Cycles |

|----------------------|--------------------------------------------------------------------------|-------|-----------------|

| ANL C, bit           | AND direct bit to Carry                                                  | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry                                    | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                                                   | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                                     | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                                                 | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                                                 | 2     | 2               |

| JC rel               | Jump if Carry is set                                                     | 2     | 2/3             |

| JNC rel              | Jump if Carry is not set                                                 | 2     | 2/3             |

| JB bit, rel          | Jump if direct bit is set                                                | 3     | 3/4             |

| JNB bit, rel         | Jump if direct bit is not set                                            | 3     | 3/4             |

| JBC bit, rel         | Jump if direct bit is set and clear bit                                  | 3     | 3/4             |

| Program Branching    |                                                                          |       |                 |

| ACALL addr11         | Absolute subroutine call                                                 | 2     | 3               |

| LCALL addr16         | Long subroutine call                                                     | 3     | 4               |

| RET                  | Return from subroutine                                                   | 1     | 5               |

| RETI                 | Return from interrupt                                                    | 1     | 5               |

| AJMP addr11          | Absolute jump                                                            | 2     | 3               |

| LJMP addr16          | Long jump                                                                | 3     | 4               |

| SJMP rel             | Short jump (relative address)                                            | 2     | 3               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                                           | 1     | 3               |

| JZ rel               | Jump if A equals zero                                                    | 2     | 2/3             |

| JNZ rel              | Jump if A does not equal zero                                            | 2     | 2/3             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal                           | 3     | 4/5             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal                             | 3     | 3/4             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal                      | 3     | 3/4             |

| CJNE @Ri, #data, rel | CJNE @Ri, #data, rel Compare immediate to indirect and jump if not equal |       | 4/5             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero                                  | 2     | 2/3             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero                               | 3     | 3/4             |

| NOP                  | No operation                                                             | 1     | 1               |

Table 16.1. CIP-51 Instruction Set Summary (Continued)

## 17. Memory Organization

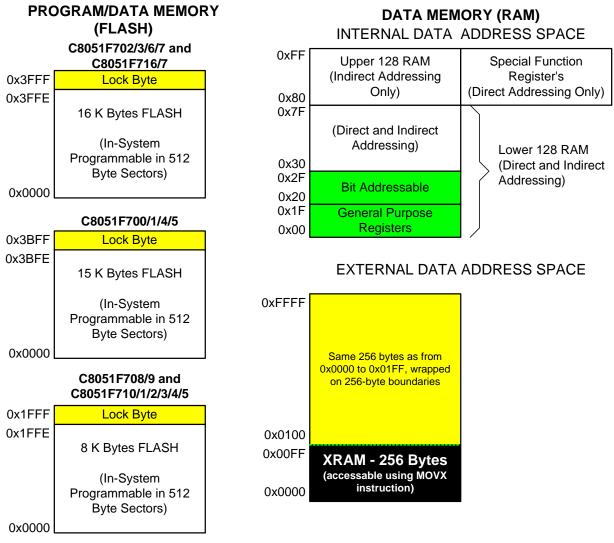

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory organization of the C8051F70x/71x device family is shown in Figure 17.1

Figure 17.1. C8051F70x/71x Memory Map

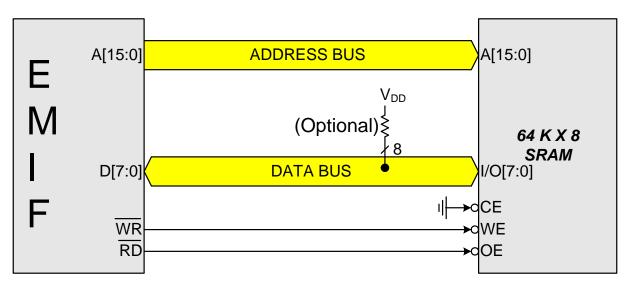

#### 18.4.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Nonmultiplexed Configuration is shown in Figure 18.2. See Section "18.6.1. Non-Multiplexed Mode" on page 120 for more information about Non-multiplexed operation.

Figure 18.2. Non-multiplexed Configuration Example

## SFR Definition 21.2. IP: Interrupt Priority

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xB8; SFR Page = All Pages; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                 |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | Read = 1b, Write = Don't Care.                                                                                                                                                                                           |

| 6   | PSPI0  | Serial Peripheral Interface (SPI0) Interrupt Priority Control.<br>This bit sets the priority of the SPI0 interrupt.<br>0: SPI0 interrupt set to low priority level.<br>1: SPI0 interrupt set to high priority level.     |

| 5   | PT2    | Timer 2 Interrupt Priority Control.This bit sets the priority of the Timer 2 interrupt.0: Timer 2 interrupt set to low priority level.1: Timer 2 interrupt set to high priority level.                                   |

| 4   | PS0    | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                               |

| 3   | PT1    | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                   |

| 2   | PX1    | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt.<br>0: External Interrupt 1 set to low priority level.<br>1: External Interrupt 1 set to high priority level. |

| 1   | PT0    | Timer 0 Interrupt Priority Control.This bit sets the priority of the Timer 0 interrupt.0: Timer 0 interrupt set to low priority level.1: Timer 0 interrupt set to high priority level.                                   |

| 0   | PX0    | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>0: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level. |

## 22. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 9.6 for complete Flash memory electrical characteristics.

### 22.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "35. C2 Interface" on page 301.

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before programming Flash memory using MOVX, Flash programming operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

**Note:** A minimum SYSCLK frequency is required for writing or erasing Flash memory, as detailed in Section "Table 9.6. Flash Electrical Characteristics" on page 50.

For detailed guidelines on programming Flash from firmware, please see Section "22.4. Flash Write and Erase Guidelines" on page 150.

To ensure the integrity of the Flash contents, the on-chip VDD Monitor must be enabled and enabled as a reset source in any system that includes code that writes and/or erases Flash memory from software. Furthermore, there should be no delay between enabling the  $V_{DD}$  Monitor and enabling the  $V_{DD}$  Monitor as a reset source. Any attempt to write or erase Flash memory while the  $V_{DD}$  Monitor is disabled, or not enabled as a reset source, will cause a Flash Error device reset.

#### 22.1.1. Flash Lock and Key Functions

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 22.2.

#### 22.1.2. Flash Erase Procedure

The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- 1. Save current interrupt state and disable interrupts.

- 2. Set the PSEE bit (register PSCTL).

- 3. Set the PSWE bit (register PSCTL).

- 4. Write the first key code to FLKEY: 0xA5.

- 5. Write the second key code to FLKEY: 0xF1.

#### 22.4.3. System Clock

- 12. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 13. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories web site.

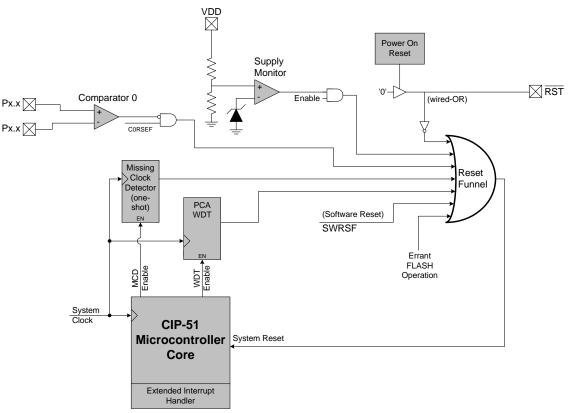

## 25. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source. Program execution begins at location 0x0000.

Figure 25.1. Reset Sources

## SFR Definition 25.1. VDM0CN: $V_{DD}$ Monitor Control

| Bit   | 7      | 6       | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|---------|--------|--------|--------|--------|--------|--------|

| Name  | VDMEN  | VDDSTAT |        |        |        |        |        |        |

| Туре  | R/W    | R       | R      | R      | R      | R      | R      | R      |

| Reset | Varies | Varies  | Varies | Varies | Varies | Varies | Varies | Varies |

#### SFR Address = 0xFF; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | VDMEN   | V <sub>DD</sub> Monitor Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |         | This bit turns the V <sub>DD</sub> monitor circuit on/off. The V <sub>DD</sub> Monitor cannot generate system resets until it is also selected as a reset source in register RSTSRC (SFR Definition 25.2). Selecting the V <sub>DD</sub> monitor as a reset source before it has stabilized may generate a system reset. In systems where this reset would be undesirable, a delay should be introduced between enabling the V <sub>DD</sub> Monitor and selecting it as a reset source.<br>0: V <sub>DD</sub> Monitor Disabled.<br>1: V <sub>DD</sub> Monitor Enabled. |

| 6   | VDDSTAT | V <sub>DD</sub> Status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |         | This bit indicates the current power supply status (V <sub>DD</sub> Monitor output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |         | 0: $V_{DD}$ is at or below the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |         | 1: $V_{DD}$ is above the $V_{DD}$ monitor threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5:0 | Unused  | Read = Varies; Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### 25.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Section "9. Electrical Characteristics" on page 47 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### 25.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than the MCD timeout, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

### 25.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

#### 25.6. Watchdog Timer Reset

The programmable Watchdog Timer (WDT) can be used to prevent software from running out of control during a system malfunction. The WDT function can be enabled or disabled by software as described in Section "26. Watchdog Timer" on page 169. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.3) is set to 1. The state of the RST pin is unaffected by this reset.

#### 25.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above address 0x3DFF.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above address 0x3DFF.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above 0x3DFF.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "22.3. Security Options" on page 149).

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

#### 25.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

## 26. Watchdog Timer

The MCU includes a programmable Watchdog Timer (WDT) running off the system clock. A WDT overflow will force the MCU into the reset state. To prevent the reset, the WDT must be restarted by application software before overflow. If the system experiences a software or hardware malfunction preventing the software from restarting the WDT, the WDT will overflow and cause a reset.

Following a reset the WDT is automatically enabled and running with the default maximum time interval. If desired the WDT can be disabled by system software or locked on to prevent accidental disabling. Once locked, the WDT cannot be disabled until the next system reset. The state of the /RST pin is unaffected by this reset.

The WDT consists of a 21-bit timer running from the programmed system clock. The timer measures the period between specific writes to its control register. If this period exceeds the programmed limit, a WDT reset is generated. The WDT can be enabled and disabled as needed in software, or can be permanently enabled if desired. Watchdog features are controlled via the Watchdog Timer Control Register (WDTCN) shown in SFR Definition 26.1.

#### 26.1. Enable/Reset WDT

The watchdog timer is both enabled and reset by writing 0xA5 to the WDTCN register. The user's application software should include periodic writes of 0xA5 to WDTCN as needed to prevent a watchdog timer overflow. The WDT is enabled and reset as a result of any system reset.

### 26.2. Disable WDT

Writing 0xDE followed by 0xAD to the WDTCN register disables the WDT. The following code segment illustrates disabling the WDT:

CLR EA ; disable all interrupts MOV WDTCN,#0DEh ; disable software watchdog timer MOV WDTCN,#0ADh SETB EA ; re-enable interrupts

The writes of 0xDE and 0xAD must occur within 4 clock cycles of each other, or the disable operation is ignored. Interrupts should be disabled during this procedure to avoid delay between the two writes.

### 26.3. Disable WDT Lockout

Writing 0xFF to WDTCN locks out the disable feature. Once locked out, the disable operation is ignored until the next system reset. Writing 0xFF does not enable or reset the watchdog timer. Applications always intending to use the watchdog should write 0xFF to WDTCN in the initialization code.

#### 26.4. Setting WDT Interval

WDTCN.[2:0] control the watchdog timeout interval. The interval is given by the following equation:

4^(3+WDTCN[2-0]) x Tsysclk ;where Tsysclk is the system clock period.

For a 3 MHz system clock, this provides an interval range of 0.021 to 349.5 ms. WDTCN.7 must be logic 0 when setting this interval. Reading WDTCN returns the programmed interval. WDTCN.[2:0] reads 111b after a system reset.

## SFR Definition 28.15. P1SKIP: Port 1 Skip

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-------------|---|---|---|---|---|---|--|

| Name  |   | P1SKIP[7:0] |   |   |   |   |   |   |  |

| Туре  |   | R/W         |   |   |   |   |   |   |  |

| Reset | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |  |

#### SFR Address = 0xD5; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                                                                                                                              |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[7:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                     |

|     |             | These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins<br>used for analog, special functions or GPIO should be skipped by the Crossbar.<br>0: Corresponding P1.n pin is not skipped by the Crossbar.<br>1: Corresponding P1.n pin is skipped by the Crossbar. |

### SFR Definition 28.16. P1DRV: Port 1 Drive Strength

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | P1DRV[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xFA; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |

### SFR Definition 28.27. P4MDIN: Port 4 Input Mode

| Bit   | 7   | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|-------------|---|---|---|---|---|---|--|

| Name  |     | P4MDIN[7:0] |   |   |   |   |   |   |  |

| Туре  | R/W |             |   |   |   |   |   |   |  |

| Reset | 1   | 1           | 1 | 1 | 1 | 1 | 1 | 1 |  |

#### SFR Address = 0xF5; SFR Page = F

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P4MDIN[7:0] | Analog Configuration Bits for P4.7–P4.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P4.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P4.n pin is not configured for analog mode.                                                |

### SFR Definition 28.28. P4MDOUT: Port 4 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P4MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0x9A; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P4MDOUT[7:0] | Output Configuration Bits for P4.7–P4.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P4MDIN is logic 0.<br>0: Corresponding P4.n Output is open-drain.<br>1: Corresponding P4.n Output is push-pull. |

### SFR Definition 28.31. P5MDIN: Port 5 Input Mode

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P5MDIN[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Address = 0xF6; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P5MDIN[7:0] | Analog Configuration Bits for P5.7–P5.0 (respectively).                                                                                                                 |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled.<br>0: Corresponding P5.n pin is configured for analog mode. |

|     |             | 1: Corresponding P5.n pin is not configured for analog mode.                                                                                                            |

### SFR Definition 28.32. P5MDOUT: Port 5 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P5MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0x9B; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P5MDOUT[7:0] | Output Configuration Bits for P5.7–P5.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P5MDIN is logic 0.<br>0: Corresponding P5.n Output is open-drain.<br>1: Corresponding P5.n Output is push-pull. |

case, either a 1 or a 0 value are acceptable on the incoming slave address. Additionally, if the GC bit in register SMB0ADR is set to 1, hardware will recognize the General Call Address (0x00). Table 30.4 shows some example parameter settings and the slave addresses that will be recognized by hardware under those conditions.

| Hardware Slave Address<br>SLV[6:0] | Slave Address Mask<br>SLVM[6:0] | GC bit | Slave Addresses Recognized by Hardware |

|------------------------------------|---------------------------------|--------|----------------------------------------|

| 0x34                               | 0x7F                            | 0      | 0x34                                   |

| 0x34                               | 0x7F                            | 1      | 0x34, 0x00 (General Call)              |

| 0x34                               | 0x7E                            | 0      | 0x34, 0x35                             |

| 0x34                               | 0x7E                            | 1      | 0x34, 0x35, 0x00 (General Call)        |

| 0x70                               | 0x73                            | 0      | 0x70, 0x74, 0x78, 0x7C                 |

Table 30.4. Hardware Address Recognition Examples (EHACK = 1)

#### SFR Definition 30.3. SMB0ADR: SMBus Slave Address

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

|-------|----------|---|---|---|---|---|-----|---|

| Name  | SLV[6:0] |   |   |   |   |   | GC  |   |

| Туре  | R/W      |   |   |   |   |   | R/W |   |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0   | 0 |

SFR Address = 0xBA; SFR Page = F

| Eı | ın | cti | 0 |

|----|----|-----|---|

| Bit | Name     | Function                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV[6:0] | SMBus Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |          | Defines the SMBus Slave Address(es) for automatic hardware acknowledgement.<br>Only address bits which have a 1 in the corresponding bit position in SLVM[6:0]<br>are checked against the incoming address. This allows multiple addresses to be<br>recognized.            |

| 0   | GC       | General Call Address Enable.                                                                                                                                                                                                                                               |

|     |          | <ul> <li>When hardware address recognition is enabled (EHACK = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

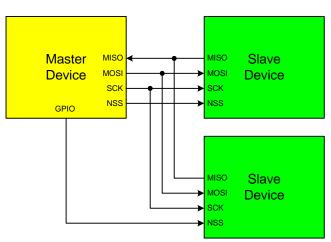

Figure 31.4. 4-Wire Single Master Mode and Slave Mode Connection Diagram

### 31.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. The NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 31.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 31.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

## SFR Definition 31.2. SPI0CN: SPI0 Control

| Bit   | 7    | 6    | 5    | 4      | 3    | 2      | 1     | 0     |

|-------|------|------|------|--------|------|--------|-------|-------|

| Name  | SPIF | WCOL | MODF | RXOVRN | NSSM | D[1:0] | TXBMT | SPIEN |

| Туре  | R/W  | R/W  | R/W  | R/W    | R/W  |        | R     | R/W   |

| Reset | 0    | 0    | 0    | 0      | 0    | 1      | 1     | 0     |

#### SFR Address = 0xF8; SFR Page = All Pages; Bit-Addressable

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF       | <b>SPI0 Interrupt Flag.</b><br>This bit is set to logic 1 by hardware at the end of a data transfer. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                                                                            |

| 6   | WCOL       | Write Collision Flag.<br>This bit is set to logic 1 if a write to SPI0DAT is attempted when TXBMT is 0. When<br>this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be<br>written. If SPI interrupts are enabled, an interrupt will be generated. This bit is not<br>automatically cleared by hardware, and must be cleared by software.                                           |

| 5   | MODF       | <b>Mode Fault Flag.</b><br>This bit is set to logic 1 by hardware when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                        |

| 4   | RXOVRN     | <b>Receive Overrun Flag (valid in slave mode only).</b><br>This bit is set to logic 1 by hardware when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI0 shift register. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.    |

| 3:2 | NSSMD[1:0] | Slave Select Mode.<br>Selects between the following NSS operation modes:<br>(See Section 31.2 and Section 31.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |

| 1   | TXBMT      | <b>Transmit Buffer Empty.</b><br>This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.                                                                                                   |

| 0   | SPIEN      | SPI0 Enable.<br>0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                                                                                                                                                                                |

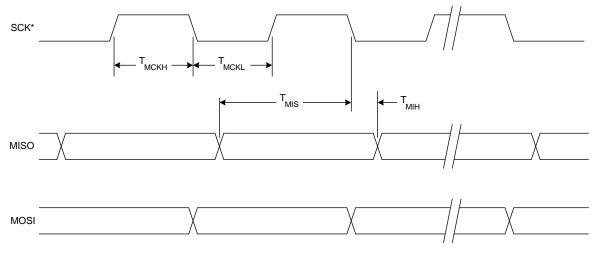

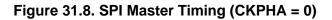

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

### Figure 31.9. SPI Master Timing (CKPHA = 1)

## SFR Definition 33.6. TH0: Timer 0 High Byte

| Bit                                      | 7        | 6                  | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------------------------------------|----------|--------------------|---|---|---|---|---|---|--|

| Nam                                      | TH0[7:0] |                    |   |   |   |   |   |   |  |

| Туре                                     | ;        | R/W                |   |   |   |   |   |   |  |

| Rese                                     | et 0     | 0                  | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR Address = 0x8C; SFR Page = All Pages |          |                    |   |   |   |   |   |   |  |

| Bit                                      | Name     | Function           |   |   |   |   |   |   |  |

| 7:0                                      | TH0[7:0] | Timer 0 High Byte. |   |   |   |   |   |   |  |

## SFR Definition 33.7. TH1: Timer 1 High Byte

| Bit                                      | 7        | 6                  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|------------------------------------------|----------|--------------------|---|---|---|---|---|---|--|--|--|

| Nam                                      | e        | TH1[7:0]           |   |   |   |   |   |   |  |  |  |

| Туре                                     | 9        | R/W                |   |   |   |   |   |   |  |  |  |

| Rese                                     | et 0     | 0                  | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR Address = 0x8D; SFR Page = All Pages |          |                    |   |   |   |   |   |   |  |  |  |

| Bit                                      | Name     | Function           |   |   |   |   |   |   |  |  |  |

| 7:0                                      | TH1[7:0] | Timer 1 High Byte. |   |   |   |   |   |   |  |  |  |

|  | The TH1 register is the high byte of the 16-bit Timer 1. |

|--|----------------------------------------------------------|

|--|----------------------------------------------------------|

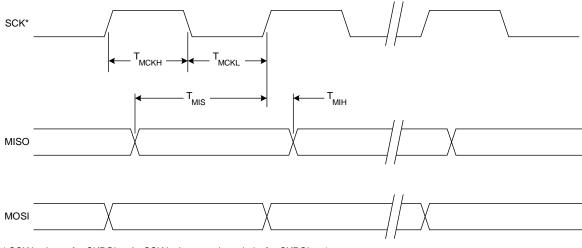

### 34.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2–CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 34.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2                                                                                 | CPS1 | CPS0 | Timebase                                                              |  |  |  |

|--------------------------------------------------------------------------------------|------|------|-----------------------------------------------------------------------|--|--|--|

| 0                                                                                    | 0    | 0    | System clock divided by 12                                            |  |  |  |

| 0                                                                                    | 0    | 1    | System clock divided by 4                                             |  |  |  |

| 0                                                                                    | 1    | 0    | Timer 0 overflow                                                      |  |  |  |

| 0                                                                                    | 1    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |  |  |  |

| 1                                                                                    | 0    | 0    | System clock                                                          |  |  |  |

| 1                                                                                    | 0    | 1    | External oscillator source divided by 8 <sup>*</sup>                  |  |  |  |

| 1                                                                                    | 1    | х    | Reserved                                                              |  |  |  |

| Note: External oscillator source divided by 8 is synchronized with the system clock. |      |      |                                                                       |  |  |  |

#### Table 34.1. PCA Timebase Input Options

IDLE PCA0MD PCA0CN D L To SFR Bus PCA0I read Snapshot Register SYSCLK/12 000 SYSCLK/4 001 Timer 0 Overflow 010 Overflow PCA0L PCA0H To PCA Interrupt System ECI 011 SYSCLK CF 100 External Clock/8 101 To PCA Modules

## 35. C2 Interface

C8051F70x/71x devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface operates using only two pins: a bi-directional data signal (C2D), and a clock input (C2CK). See the C2 Interface Specification for details on the C2 protocol.

#### 35.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming functions through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

#### C2 Register Definition 35.1. C2ADD: C2 Address

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------|---|---|---|---|---|---|---|

| Name  | C2ADD[7:0]      |   |   |   |   |   |   |   |

| Туре  | R/W             |   |   |   |   |   |   |   |

| Reset | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

| Bit   | Name                        | Function                                                                                                                       |                                                   |                                              |  |  |  |  |

|-------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------|--|--|--|--|

| 7:0   | C2ADD[7:0]                  | C2ADD[7:0] C2 Address.                                                                                                         |                                                   |                                              |  |  |  |  |

|       |                             | The C2ADD register is accessed via the C2 interface to select the target Data reg<br>for C2 Data Read and Data Write commands. |                                                   |                                              |  |  |  |  |

|       |                             | Address                                                                                                                        | ess Name Description                              |                                              |  |  |  |  |

|       |                             | 0x00                                                                                                                           | DEVICEID                                          | Selects the Device ID Register (read only)   |  |  |  |  |

|       |                             | 0x01                                                                                                                           | REVID                                             | Selects the Revision ID Register (read only) |  |  |  |  |

|       |                             | FPCTL                                                                                                                          | Selects the C2 Flash Programming Control Register |                                              |  |  |  |  |

|       |                             | FPDAT                                                                                                                          | Selects the C2 Flash Data Register                |                                              |  |  |  |  |

|       |                             | 0x96                                                                                                                           | CRC0AUTO*                                         | Selects the CRC0AUTO Register                |  |  |  |  |

|       |                             | 0x97                                                                                                                           | CRC0CNT*                                          | Selects the CRC0CNT Register                 |  |  |  |  |

|       |                             | 0x91                                                                                                                           | CRC0CN*                                           | Selects the CRC0CN Register                  |  |  |  |  |

|       |                             | 0xD9                                                                                                                           | CRC0DATA*                                         | Selects the CRC0DATA Register                |  |  |  |  |

|       |                             | 0x95                                                                                                                           | CRC0FLIP*                                         | Selects the CRC0FLIP Register                |  |  |  |  |

|       | Selects the CRC0IN Register |                                                                                                                                |                                                   |                                              |  |  |  |  |

| Note: | CRC registers page 211.     | s and functions are described in Section "29. Cyclic Redundancy Check Unit (CRC0)" on                                          |                                                   |                                              |  |  |  |  |