# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, WDT                                        |

| Number of I/O              | 39                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            |                                                                 |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 48-QFN (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f707-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 16.1.1. Instruction and CPU Timing                                 | 99  |

|--------------------------------------------------------------------|-----|

| 16.2. CIP-51 Register Descriptions                                 |     |

| 17. Memory Organization                                            |     |

| 17.1. Program Memory                                               |     |

| 17.1.1. MOVX Instruction and Program Memory                        |     |

| 17.2. EEPROM Memory                                                |     |

| 17.3. Data Memory                                                  |     |

| 17.3.1. Internal RAM                                               |     |

| 17.3.1.1. General Purpose Registers                                |     |

| 17.3.1.2. Bit Addressable Locations                                |     |

| 17.3.1.3. Stack                                                    |     |

| 18. External Data Memory Interface and On-Chip XRAM                |     |

| 18.1. Accessing XRAM                                               |     |

| 18.1.1. 16-Bit MOVX Example                                        |     |

| 18.1.2. 8-Bit MOVX Example                                         |     |

| 18.2. Configuring the External Memory Interface                    |     |

| 18.3. Port Configuration                                           | 112 |

| 18.4. Multiplexed and Non-multiplexed Selection                    |     |

| 18.4.1. Multiplexed Configuration                                  |     |

| 18.4.2. Non-multiplexed Configuration                              | 116 |

| 18.5. Memory Mode Selection                                        |     |

| 18.5.1. Internal XRAM Only                                         | 117 |

| 18.5.2. Split Mode without Bank Select                             |     |

| 18.5.3. Split Mode with Bank Select                                |     |

| 18.5.4. External Only                                              |     |

| 18.6. Timing                                                       |     |

| 18.6.1. Non-Multiplexed Mode                                       | 120 |

| 18.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111              | 120 |

| 18.6.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111 | 121 |

| 18.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110           | 122 |

| 18.6.2. Multiplexed Mode                                           | 123 |

| 18.6.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011              | 123 |

| 18.6.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011 | 124 |

| 18.6.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010           | 125 |

| 19. In-System Device Identification                                | 128 |

| 20. Special Function Registers                                     | 130 |

| 21. Interrupts                                                     | 137 |

| 21.1. MCU Interrupt Sources and Vectors                            | 138 |

| 21.1.1. Interrupt Priorities                                       | 138 |

| 21.1.2. Interrupt Latency                                          | 138 |

| 21.2. Interrupt Register Descriptions                              | 140 |

| 21.3. INTO and INT1 External Interrupts                            | 146 |

| 22. Flash Memory                                                   | 148 |

| 22.1. Programming The Flash Memory                                 |     |

| 22.1.1. Flash Lock and Key Functions                               | 148 |

### List of Tables

| Table 2.1. Product Selection Guide                                       | . 27 |

|--------------------------------------------------------------------------|------|

| Table 3.1. Pin Definitions for the C8051F70x/71x                         | . 28 |

| Table 4.1. TQFP-64 Package Dimensions                                    | . 37 |

| Table 4.2. TQFP-64 PCB Land Pattern Dimensions                           | . 38 |

| Table 5.1. TQFP-48 Package Dimensions                                    |      |

| Table 5.2. TQFP-48 PCB Land Pattern Dimensions                           | . 40 |

| Table 6.1. QFN-48 Package Dimensions                                     | . 41 |

| Table 6.2. QFN-48 PCB Land Pattern Dimensions                            | . 42 |

| Table 7.1. QFN-32 Package Dimensions                                     | . 43 |

| Table 7.2. QFN-32 PCB Land Pattern Dimensions                            | . 44 |

| Table 8.1. QFN-24 Package Dimensions                                     | . 45 |

| Table 8.2. QFN-24 PCB Land Pattern Dimensions                            | . 46 |

| Table 9.1. Absolute Maximum Ratings                                      | . 47 |

| Table 9.2. Global Electrical Characteristics                             | . 48 |

| Table 9.3. Port I/O DC Electrical Characteristics                        | . 49 |

| Table 9.4. Reset Electrical Characteristics                              |      |

| Table 9.5. Internal Voltage Regulator Electrical Characteristics         | . 50 |

| Table 9.6. Flash Electrical Characteristics                              |      |

| Table 9.7. Internal High-Frequency Oscillator Electrical Characteristics |      |

| Table 9.8. Capacitive Sense Electrical Characteristics                   |      |

| Table 9.9. EEPROM Electrical Characteristics                             |      |

| Table 9.10. ADC0 Electrical Characteristics                              |      |

| Table 9.11. Power Management Electrical Characteristics                  | . 53 |

| Table 9.12. Temperature Sensor Electrical Characteristics                |      |

| Table 9.13. Voltage Reference Electrical Characteristics                 |      |

| Table 9.14. Comparator Electrical Characteristics                        |      |

| Table 15.1. Gain Setting vs. Maximum Capacitance and Conversion Time     |      |

| Table 15.2. Operation with Auto-scan and Accumulate                      |      |

| Table 16.1. CIP-51 Instruction Set Summary                               |      |

| Table 18.1. AC Parameters for External Memory Interface                  |      |

| Table 18.2. EMIF Pinout (C8051F700/1/2/3/8/9 and C8051F710/1)            |      |

| Table 20.1. Special Function Register (SFR) Memory Map                   |      |

| Table 20.2. Special Function Registers                                   |      |

| Table 21.1. Interrupt Summary                                            |      |

| Table 22.1. Flash Security Summary                                       |      |

| Table 28.1. Port I/O Assignment for Analog Functions                     |      |

| Table 28.2. Port I/O Assignment for Digital Functions                    |      |

| Table 28.3. Port I/O Assignment for External Event Trigger Functions     |      |

| Table 29.1. Example 16-bit CRC Outputs                                   | 212  |

| Table 29.2. Example 32-bit CRC Outputs                                   |      |

| Table 30.1. SMBus Clock Source Selection                                 |      |

| Table 30.2. Minimum SDA Setup and Hold Times                             |      |

| Table 30.3. Sources for Hardware Changes to SMB0CN                       | 228  |

#### Table 9.8. Capacitive Sense Electrical Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_{A}$  = –40 to +85 °C unless otherwise specified.

| Parameter                           | Conditions                                                                       | Min | Тур | Max  | Units    |

|-------------------------------------|----------------------------------------------------------------------------------|-----|-----|------|----------|

| Single Conversion Time <sup>1</sup> | 12-bit Mode                                                                      | 20  | 29  | 40   | μs       |

| -                                   | 13-bit Mode (default)                                                            | 21  | 31  | 42.5 |          |

|                                     | 14-bit Mode                                                                      | 23  | 33  | 45   |          |

|                                     | 16-bit Mode                                                                      | 26  | 38  | 50   |          |

| Number of Channels                  | 64-pin Packages                                                                  |     | 38  |      | Channels |

|                                     | 48-pin Packages                                                                  |     | 27  |      |          |

|                                     | 32-pin Packages                                                                  |     | 26  |      |          |

|                                     | 24-pin Packages                                                                  |     | 18  |      |          |

| Capacitance per Code                | Default Configuration                                                            |     | 1   | —    | fF       |

| External Capacitive Load            | CS0CG = 111b (Default)                                                           |     |     | 45   | pF       |

|                                     | CSOCG = 000b                                                                     |     |     | 500  | pF       |

| External Series Impedance           | CS0CG = 111b (Default)                                                           |     |     | 50   | kΩ       |

| Quantization Noise <sup>12</sup>    | RMS                                                                              |     | 3   | _    | fF       |

|                                     | Peak-to-Peak                                                                     |     | 20  | —    | fF       |

| Power Supply Current                | CS module bias current, 25 °C                                                    |     | 50  | 60   | μA       |

|                                     | CS module alone, maximum code<br>output, 25 °C                                   | _   | 90  | 105  | μA       |

|                                     | Wake-on-CS threshold (suspend mode with regulator and CS module on) <sup>3</sup> |     | 130 | 145  | μA       |

1. Conversion time is specified with the default configuration.

2. RMS Noise is equivalent to one standard deviation. Peak-to-peak noise encompasses ±3.3 standard deviations. The RMS noise value is specified with the default configuration.

3. Includes only current from regulator, CS module, and MCU in suspend mode.

#### SFR Definition 10.7. ADC0LTH: ADC0 Less-Than Data High Byte

| Bit   | 7             | 6            | 5                                         | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------------|--------------|-------------------------------------------|---|---|---|---|---|--|

| Nam   | e             | ADC0LTH[7:0] |                                           |   |   |   |   |   |  |

| Туре  | R/W           |              |                                           |   |   |   |   |   |  |

| Rese  | et 0          | 0            | 0 0 0 0 0 0                               |   |   |   |   |   |  |

| SFR A | Address = 0xC | 6; SFR Page  | e = 0                                     |   |   |   |   |   |  |

| Bit   | Name          |              | Function                                  |   |   |   |   |   |  |

| 7:0   | ADC0LTH[7:0   | )] ADC0 Le   | ADC0 Less-Than Data Word High-Order Bits. |   |   |   |   |   |  |

### SFR Definition 10.8. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit   | 7              | 6          | 5                                        | 4 | 3 | 2 | 1 | 0 |

|-------|----------------|------------|------------------------------------------|---|---|---|---|---|

| Nam   | ADC0LTL[7:0]   |            |                                          |   |   |   |   |   |

| Туре  | 9              |            | R/W                                      |   |   |   |   |   |

| Rese  | et O           | 0          | 0                                        | 0 | 0 | 0 | 0 | 0 |

| SFR A | Address = 0xC5 | ; SFR Page | e = 0                                    |   |   |   |   |   |

| Bit   | Name           |            | Function                                 |   |   |   |   |   |

| 7:0   | ADC0LTL[7:0    | ADC0 Le    | ADC0 Less-Than Data Word Low-Order Bits. |   |   |   |   |   |

### 14. Comparator0

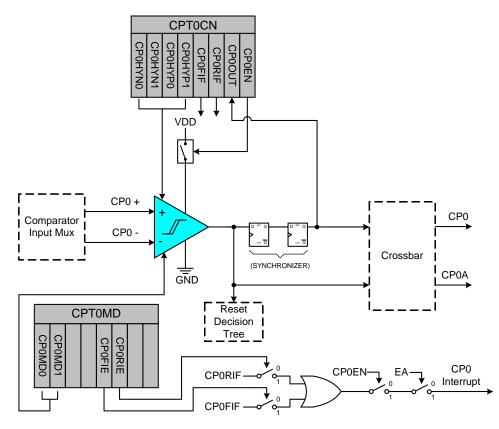

C8051F70x/71x devices include an on-chip programmable voltage comparator, Comparator0, shown in Figure 14.1.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0), or an asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output with the device in STOP mode. When assigned to a Port pin, the Comparator output may be configured as open drain or push-pull (see Section "28.4. Port I/O Initialization" on page 189). Comparator0 may also be used as a reset source (see Section "25.5. Comparator0 Reset" on page 167).

The Comparator0 inputs are selected by the comparator input multiplexer, as detailed in Section "14.1. Comparator Multiplexer" on page 78.

Figure 14.1. Comparator0 Functional Block Diagram

The Comparator output can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, the Comparator output is available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and the power supply to the comparator is turned off. See Section "28.3. Priority Crossbar Decoder" on page 185 for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to (V<sub>DD</sub>) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Section "9. Electrical Characteristics" on page 47.

### SFR Definition 14.3. CPT0MX: Comparator0 MUX Selection

| Bit   | 7                             | 6                           | 5                                                                                  | 4                            | 3                           | 2                                   |                  | 1                      | 0                         |  |

|-------|-------------------------------|-----------------------------|------------------------------------------------------------------------------------|------------------------------|-----------------------------|-------------------------------------|------------------|------------------------|---------------------------|--|

| Name  |                               |                             | CMX0N[2:0]                                                                         |                              |                             | CMX0P[2:0]                          |                  |                        |                           |  |

| Туре  | e R                           |                             | R/W                                                                                |                              | R                           |                                     | R                | z/W                    |                           |  |

| Rese  | et O                          | 0                           | 0                                                                                  | 0                            | 0                           | 0                                   |                  | 0                      | 0                         |  |

| SFR A | Address = 0x9                 | F; SFR Pa                   | ; SFR Page = 0                                                                     |                              |                             |                                     |                  |                        |                           |  |

| Bit   | Name                          |                             | Function                                                                           |                              |                             |                                     |                  |                        |                           |  |

| 7     | Unused                        | Read = 0                    | ; Write = don't                                                                    | care.                        |                             |                                     |                  |                        |                           |  |

| 6:4   | CMX0N[2:0]                    | Compara                     | tor0 Negative                                                                      | Input MUX                    | Selection                   |                                     |                  |                        |                           |  |

|       |                               |                             | 64-Pin Device                                                                      | es 48-Pi                     | n Devices                   | 32-Pin Dev                          | ices             | 24-Pi                  | n Devices                 |  |

|       |                               | 000                         | P1.1                                                                               |                              | P1.1                        |                                     |                  |                        | _                         |  |

|       |                               | 001                         | P1.3                                                                               |                              | P1.3                        | —                                   |                  | —                      |                           |  |

|       |                               | 010                         |                                                                                    |                              | —                           | —                                   |                  | —                      |                           |  |

|       |                               | 011                         | P1.7                                                                               |                              | —                           |                                     | P2.0 (see note)  |                        | (see note)                |  |

|       |                               | 100-111                     | No input                                                                           |                              | o input                     | No input                            |                  | No input               |                           |  |

|       |                               |                             | selected.                                                                          |                              | elected.                    | selected.                           |                  | selected.              |                           |  |

| 3     | Unused                        |                             | o; Write = don't                                                                   |                              |                             |                                     |                  |                        |                           |  |

| 2:0   | CMX0P[2:0]                    | Compara                     | tor0 Positive I                                                                    | -                            |                             |                                     |                  |                        |                           |  |

|       |                               |                             | 64-Pin Device                                                                      |                              | n Devices                   | 32-Pin Devices                      |                  | 24-Pi                  | n Devices                 |  |

|       |                               | 000                         | P1.0                                                                               |                              | P1.0                        |                                     |                  |                        | _                         |  |

|       |                               | 001                         | P1.2                                                                               |                              | P1.2                        | —                                   |                  |                        | _                         |  |

|       |                               | 010                         | P1.4                                                                               |                              | —                           |                                     |                  |                        | _                         |  |

|       |                               | 011                         | P1.6                                                                               |                              |                             | (P1.6—see                           | ,                | `                      | -see note)                |  |

|       |                               | 100-111                     | No input selected.                                                                 |                              | o input<br>elected.         | No inpu<br>selected                 |                  |                        | o input<br>lected.        |  |

| Note  | On 22 and 24                  | nin dovices                 |                                                                                    |                              |                             |                                     |                  |                        |                           |  |

| NOTE: | near the GND the selection of | or VDD sup<br>of P2.0 as th | , P2.0 can be use<br>pply rails. The P1.<br>e negative input.<br>gh P1.6 is not co | .6 setting fo<br>P1.6 should | the positive<br>be configur | input should be<br>ed for push-pull | e used<br>I mode | in conju<br>e and driv | nction with<br>ven to the |  |

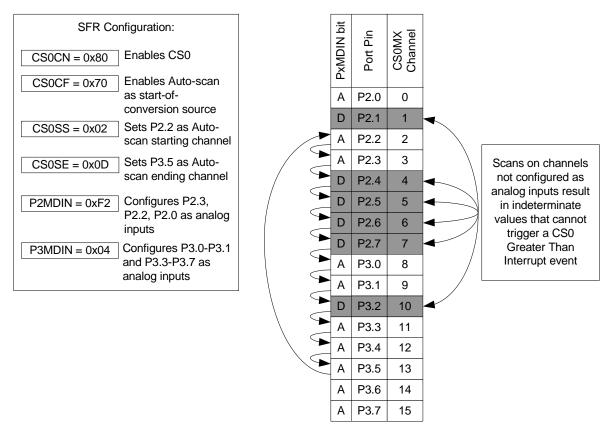

#### 15.4. Automatic Scanning

CS0 can be configured to automatically scan a sequence of contiguous CS0 input channels by configuring and enabling auto-scan. Using auto-scan with the CS0 comparator interrupt enabled allows a system to detect a change in measured capacitance without requiring any additional dedicated MCU resources.

Auto-scan is enabled by setting the CS0 start-of-conversion bits (CS0CF6:4) to 111b. After enabling autoscan, the starting and ending channels should be set to appropriate values in CS0SS and CS0SE, respectively. Writing to CS0SS when auto-scan is enabled will cause the value written to CS0SS to be copied into CS0MX. After being enabled, writing a 1 to CS0BUSY will start auto-scan conversions. When auto-scan completes the number of conversions defined in the CS0 accumulator bits (CS0CF2:0), auto-scan configures CS0MX to the next sequential port pin configured as an analog input and begins a conversion on that channel. The scan sequence continues until CS0MX reaches the ending input channel value defined in CS0SE.

**Note:** All other CS0 pins configured for analog input with a 0 in the port latch are grounded during the conversion.

After the final channel conversion, auto-scan configures CS0MX back to the starting input channel. For an example system configured to use auto-scan, please see Figure "15.2 Auto-Scan Example" on page 83.

**Note:** Auto-scan attempts one conversion on a CS0MX channel regardless of whether that channel's port pin has been configured as an analog input. Auto-scan will also complete the current rotation when the device is halted for debugging.

If auto-scan is enabled when the device enters suspend mode, auto-scan will remain enabled and running. This feature allows the device to wake from suspend through CS0 greater-than comparator event on any configured capacitive sense input included in the auto-scan sequence of inputs.

Figure 15.2. Auto-Scan Example

### SFR Definition 15.12. CS0MX: Capacitive Sense Mux Channel Select

| Bit   | 7             | 6                                  |         | 5                     | 4      |      | 3                   | 2        | 1                     |               | 0             |

|-------|---------------|------------------------------------|---------|-----------------------|--------|------|---------------------|----------|-----------------------|---------------|---------------|

| Nam   | e CSOUC       |                                    |         | I                     |        | I    | CS0MX               | [5:0]    |                       |               |               |

| Туре  | e R/W         | R/W                                |         |                       |        |      | R/V                 | V        |                       |               |               |

| Rese  | et 0          | 0                                  |         | 0                     | 0      |      | 0                   | 0        | C                     | )             | 0             |

| SFR A | Address = 0x9 | PC; SFR Page = 0                   |         |                       |        |      |                     |          |                       |               |               |

| Bit   | Name          |                                    |         | Description           |        |      |                     |          |                       |               |               |

| 7     | CS0UC         | CS0 Unc                            |         |                       |        |      |                     |          |                       |               |               |

|       |               | Disconne<br>0: CS0 co<br>1: CS0 di | onnecte | d to port             | pins   | •    | dless of t          | he selec | ted chani             | nel.          |               |

| 6     | Reserved      | Write = 0                          | b       |                       |        |      |                     |          |                       |               |               |

| 5:0   | CS0MX[5:0]    | CS0 Mux                            |         |                       |        |      |                     | Correct  |                       |               |               |

|       |               | Value                              |         | •                     | 32-pin |      | Capacitive<br>Value | 64-pin   | 48-pin                | on.<br>32-pin | 24-pin        |

|       |               | 000000                             | P2.0    | <b>40-pin</b><br>P2.0 | P2.0   | P2.0 | 010011              | P4.3     | <b>46-ріп</b><br>Р4.3 | sz-pin        | 24-pm<br>P4.3 |

|       |               | 000000                             | P2.0    | P2.0                  | P2.0   | P2.0 | 010100              | P4.4     | F 4.5                 |               | P4.3          |

|       |               | 000010                             | P2.2    | P2.2                  | P2.2   | P2.2 | 010100              | P4.5     |                       |               | P4.5          |

|       |               | 000011                             | P2.3    | P2.3                  | P2.3   | P2.3 | 010110              | P4.6     | _                     |               | P4.6          |

|       |               | 000100                             | P2.4    | P2.4                  | P2.4   | P2.4 | 010111              | P4.7     | _                     | _             | P4.7          |

|       |               | 000101                             | P2.5    | P2.5                  | P2.5   | P2.5 | 011000              | P5.0     | P5.0                  | P5.0          | _             |

|       |               | 000110                             | P2.6    | P2.6                  | P2.6   | P2.6 | 011001              | P5.1     | P5.1                  | P5.1          |               |

|       |               | 000111                             | P2.7    | P2.7                  | P2.7   | P2.7 | 011010              | P5.2     | P5.2                  | P5.2          | —             |

|       |               | 001000                             | P3.0    | —                     | P3.0   | —    | 011011              | P5.3     | P5.3                  | P5.3          | _             |

|       |               | 001001                             | P3.1    |                       | P3.1   |      | 011100              | P5.4     | P5.4                  | P5.4          | —             |

|       |               | 001010                             | P3.2    |                       | P3.2   |      | 011101              | P5.5     | P5.5                  | P5.5          | —             |

|       |               | 001011                             | P3.3    | _                     | P3.3   | _    | 011110              | P5.6     | P5.6                  | P5.6          | —             |

|       |               | 001100                             | P3.4    | P3.4                  | P3.4   | —    | 011111              | P5.7     | P5.7                  | P5.7          | —             |

|       |               | 001101                             | P3.5    | P3.5                  | P3.5   |      | 100000              | P6.0     |                       | —             | —             |

|       |               | 001110                             | P3.6    | P3.6                  | P3.6   |      | 100001              | P6.1     |                       | —             | —             |

|       |               | 001111                             | P3.7    | P3.7                  | —      | —    | 100010              | P6.2     | —                     | —             | —             |

|       |               | 010000                             | P4.0    | P4.0                  | —      | P4.0 | 100011              | P6.3     | P6.3                  | P6.3          |               |

|       |               | 010001                             | P4.1    | P4.1                  | —      | P4.1 | 100100              | P6.4     | P6.4                  | P6.4          | P6.4          |

|       |               | 010010                             | P4.2    | P4.2                  | —      | P4.2 | 100101              | P6.5     | P6.5                  | P6.5          | P6.5          |

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### 16.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 16.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 16.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

#### 16.2. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should always be written to the value indicated in the SFR description. Future product versions may use these bits to implement new features in which case the reset value of the bit will be the indicated value, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

#### SFR Definition 16.1. DPL: Data Pointer Low Byte

| Bit   | 7             | 6                                                    | 5           | 4  | 3 | 2 | 1 | 0 |  |

|-------|---------------|------------------------------------------------------|-------------|----|---|---|---|---|--|

| Nam   | Name DPL[7:0] |                                                      |             |    |   |   |   |   |  |

| Туре  | Type R/W      |                                                      |             |    |   |   |   |   |  |

| Rese  | et 0          | 0                                                    | 0           | 0  | 0 | 0 | 0 | 0 |  |

| SFR A | Address = 0x8 | 32; SFR Page                                         | = All Pages | i. |   |   |   |   |  |

| Bit   | Name          |                                                      | Function    |    |   |   |   |   |  |

| 7:0   | DPL[7:0]      | Data Pointer Low.                                    |             |    |   |   |   |   |  |

|       |               | The DPL register is the low byte of the 16-bit DPTR. |             |    |   |   |   |   |  |

#### SFR Definition 16.2. DPH: Data Pointer High Byte

| Bit                                      | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------|----------|---|---|---|---|---|---|---|

| Name                                     | DPH[7:0] |   |   |   |   |   |   |   |

| Туре                                     | R/W      |   |   |   |   |   |   |   |

| Reset                                    | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0x83; SFR Page = All Pages |          |   |   |   |   |   |   |   |

| 01107 |          |                                                       |  |  |  |

|-------|----------|-------------------------------------------------------|--|--|--|

| Bit   | Name     | Function                                              |  |  |  |

| 7:0   | DPH[7:0] | Data Pointer High.                                    |  |  |  |

|       |          | The DPH register is the high byte of the 16-bit DPTR. |  |  |  |

#### SFR Definition 18.1. EMI0CN: External Memory Interface Control

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|------------|-----|---|---|---|---|---|---|--|--|--|--|

| Name  | PGSEL[7:0] |     |   |   |   |   |   |   |  |  |  |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |  |  |  |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

#### SFR Address = 0xAA; SFR Page = F

| Bit | Name       | Function                                                                           |

|-----|------------|------------------------------------------------------------------------------------|

| 7:0 | PGSEL[7:0] | XRAM Page Select Bits.                                                             |

|     |            | The XRAM Page Select Bits provide the high byte of the 16-bit external data memory |

|     |            | address when using an 8-bit MOVX command, effectively selecting a 256-byte page of |

|     |            | RAM.                                                                               |

|     |            | 0x00: 0x0000 to 0x00FF                                                             |

|     |            | 0x01: 0x0100 to 0x01FF                                                             |

|     |            |                                                                                    |

|     |            | 0xFE: 0xFE00 to 0xFEFF                                                             |

|     |            | 0xFF: 0xFF00 to 0xFFFF                                                             |

### SFR Definition 22.1. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

### SFR Address =0x8F; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | PSEE   | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE   | Program Store Write Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                                                                     |

#### SFR Definition 23.4. EEKEY: EEPROM Protect Key

| Bit   | 7 | 6                    | 1 | 0 |  |  |  |  |  |  |  |

|-------|---|----------------------|---|---|--|--|--|--|--|--|--|

| Name  |   | EEKEY EEPSTATE/EEKEY |   |   |  |  |  |  |  |  |  |

| Туре  |   | W R/W                |   |   |  |  |  |  |  |  |  |

| Reset | 0 | 0 0 0 0 0 0 0 0      |   |   |  |  |  |  |  |  |  |

SFR Address = 0xC6; SFR Page = F

| Bit | Name     | Description                                                                                                                      | Write                                                                              | Read                                                                                                                                                                 |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | EEKEY    | EEPROM Key.<br>Protects the EEPROM from<br>inadvertent writes and<br>erases.                                                     | The sequence 0x55<br>0xAA must be written to<br>enable EEPROM writes<br>and erases |                                                                                                                                                                      |

| 1:0 | EEPSTATE | <b>EEPROM Protection State.</b><br>These bytes show whether<br>Flash writes/erases have<br>been enabled, disabled, or<br>locked. |                                                                                    | 00: Write/Erase is not<br>enabled<br>01: The first key has<br>been written<br>10: Write/Erase is<br>enabled<br>11: EEPROM is locked<br>from further<br>writes/erases |

#### SFR Definition 25.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF; SFR Page = All Pages

| Bit   | Name       | Description                                                                                    | Write                                                                                                                                                                | Read                                                                                                                                           |

|-------|------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                        | Don't care.                                                                                                                                                          | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                        | N/A                                                                                                                                                                  | Set to 1 if Flash<br>read/write/erase error<br>caused the last reset.                                                                          |

| 5     | CORSEF     | Comparator0 Reset Enable and Flag.                                                             | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                                 | Writing a 1 forces a sys-<br>tem reset.                                                                                                                              | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                                   |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                     | N/A                                                                                                                                                                  | Set to 1 if Watchdog Timer overflow caused the last reset.                                                                                     |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                     | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                       | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor as a reset source.<br>Writing 1 to this bit before the $V_{DD}$ monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                             | N/A                                                                                                                                                                  | Set to 1 if RST pin caused the last reset.                                                                                                     |

| Note: | Do not use | read-modify-write operations on this                                                           | s register                                                                                                                                                           | 1                                                                                                                                              |

#### SFR Definition 27.1. CLKSEL: Clock Select

| Bit   | 7      | 6                                | 5   | 4   | 3 | 2 1 0 |     |     |  |

|-------|--------|----------------------------------|-----|-----|---|-------|-----|-----|--|

| Name  | CLKRDY | CLKDIV[2:0] Reserved CLKSEL[2:0] |     |     |   |       | ]   |     |  |

| Туре  | R      | R/W                              | R/W | R/W | R | R/W   | R/W | R/W |  |

| Reset | 0      | 0 0 0 0 0                        |     |     |   |       |     | 0   |  |

SFR Address = 0xBD; SFR Page= F

| Bit | Name        | Function                                                                                |

|-----|-------------|-----------------------------------------------------------------------------------------|

| 7   | CLKRDY      | System Clock Divider Clock Ready Flag.                                                  |

|     |             | 0: The selected clock divide setting has not been applied to the system clock.          |

|     |             | 1: The selected clock divide setting has been applied to the system clock.              |

| 6:4 | CLKDIV      | System Clock Divider Bits.                                                              |

|     |             | Selects the clock division to be applied to the selected source (internal or external). |

|     |             | 000: Selected clock is divided by 1.                                                    |

|     |             | 001: Selected clock is divided by 2.                                                    |

|     |             | 010: Selected clock is divided by 4.                                                    |

|     |             | 011: Selected clock is divided by 8.                                                    |

|     |             | 100: Selected clock is divided by 16.                                                   |

|     |             | 101: Selected clock is divided by 32.                                                   |

|     |             | 110: Selected clock is divided by 64.                                                   |

|     |             | 111: Selected clock is divided by 128.                                                  |

| 3   | Reserved    | Read = 0b. Must write 0b.                                                               |

| 2:0 | CLKSEL[2:0] | System Clock Select.                                                                    |

|     |             | Selects the oscillator to be used as the undivided system clock source.                 |

|     |             | 000: Internal Oscillator                                                                |

|     |             | 001: External Oscillator                                                                |

|     |             |                                                                                         |

|     |             | All other values reserved.                                                              |

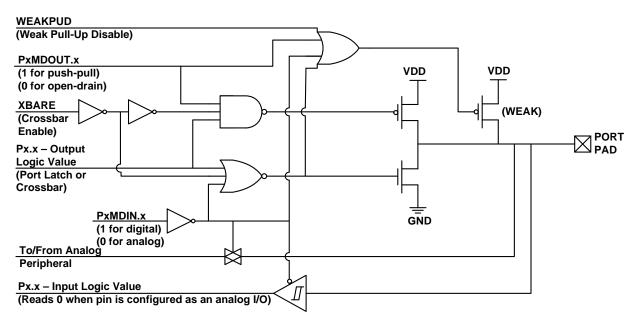

#### 28.1. Port I/O Modes of Operation

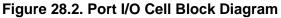

Port pins P0.0 - P6.5 use the Port I/O cell shown in Figure 28.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN registers. On reset, all Port I/O cells default to a high impedance state with weak pull-ups enabled. Until the crossbar is enabled (XBARE = 1), both the high and low port I/O drive circuits are explicitly disabled on all crossbar pins.

#### 28.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, Capacitive Sense input, external oscillator input/output, VREF output, or AGND connection should be configured for analog I/O (PnMDIN.n = 0). When a pin is configured for analog I/O, its weak pullup, digital driver, and digital receiver are disabled. Port pins configured for analog I/O will always read back a value of 0.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital I/O may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

#### 28.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external event trigger functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption, and they may be globally disabled by setting WEAKPUD to 1. The user should ensure that digital I/O are always internally or externally pulled or driven to a valid logic state to minimize power consumption. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

#### 28.4. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals.

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 28.8 for the PnMDIN register details.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a 0 to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to 1 enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Configuration Wizard utility of the Silicon Labs IDE software will determine the Port I/O pin-assignments based on the XBRn Register settings.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. Port output drivers are disabled while the Crossbar is disabled.

### SFR Definition 33.6. TH0: Timer 0 High Byte

| Bit   | 7            | 6             | 5             | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|--------------|---------------|---------------|---|---|---|---|---|--|--|--|--|

| Nam   | TH0[7:0]     |               |               |   |   |   |   |   |  |  |  |  |

| Туре  | ;            | R/W           |               |   |   |   |   |   |  |  |  |  |

| Rese  | et 0         | 0 0 0 0 0 0 0 |               |   |   |   |   |   |  |  |  |  |

| SFR A | ddress = 0x8 | C; SFR Page   | e = All Pages | 5 |   |   |   |   |  |  |  |  |

| Bit   | Name         | Function      |               |   |   |   |   |   |  |  |  |  |

| 7:0   | TH0[7:0]     | Timer 0 Hig   | h Ryta        |   |   |   |   |   |  |  |  |  |

### SFR Definition 33.7. TH1: Timer 1 High Byte

| Bit                                      | 7        | 6           | 5        | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------|----------|-------------|----------|---|---|---|---|---|

| Nam                                      | e        | TH1[7:0]    |          |   |   |   |   |   |

| Туре                                     | R/W      |             |          |   |   |   |   |   |

| <b>Reset</b> 0 0 0 0 0 0                 |          |             |          | 0 | 0 | 0 |   |   |

| SFR Address = 0x8D; SFR Page = All Pages |          |             |          |   |   |   |   |   |

| Bit                                      | Name     | Function    |          |   |   |   |   |   |

| 7:0                                      | TH1[7:0] | Timer 1 Hig | gh Byte. |   |   |   |   |   |

|  | The TH1 register is the high byte of the 16-bit Timer 1. |

|--|----------------------------------------------------------|

|--|----------------------------------------------------------|

#### 33.2.2. 8-bit Timers with Auto-Reload

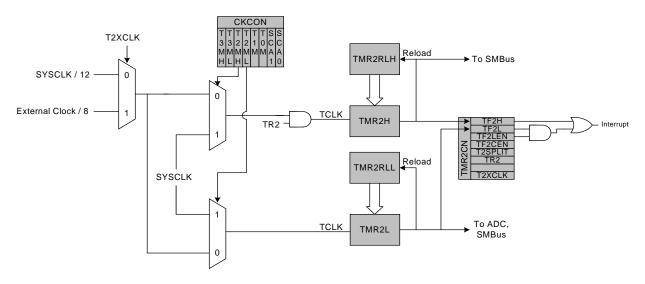

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 33.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |  |  |  |

|------|--------|--------------------|--|--|--|

| 0    | 0      | SYSCLK / 12        |  |  |  |

| 0    | 1      | External Clock / 8 |  |  |  |

| 1    | Х      | SYSCLK             |  |  |  |

| T2ML | T2XCLK | TMR2L Clock Source |  |  |  |

|------|--------|--------------------|--|--|--|

| 0    | 0      | SYSCLK / 12        |  |  |  |

| 0    | 1      | External Clock / 8 |  |  |  |

| 1    | Х      | SYSCLK             |  |  |  |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 33.5. Timer 2 8-Bit Mode Block Diagram

#### SFR Definition 33.8. TMR2CN: Timer 2 Control

| Bit   | 7            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5          | 4           | 3       | 2   | 1 | 0      |

|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|---------|-----|---|--------|

| Name  | TF2H         | TF2L                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TF2LEN     | TF2CEN      | T2SPLIT | TR2 |   | T2XCLK |

| Туре  | R/W          | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W        | R/W         | R/W     | R/W | R | R/W    |

| Reset | t 0          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0          | 0           | 0       | 0   | 0 | 0      |

| SFR A | ddress = 0xC | 8; SFR Page = All Pages; Bit-Addressable                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |             |         |     |   |        |

| Bit   | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |             |         |     |   |        |

| 7     | TF2H         | Timer 2 High Byte Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |             |         |     |   |        |

|       |              | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                               |            |             |         |     |   |        |

| 6     | TF2L         | Timer 2 Lov                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | w Byte Ove | rflow Flag. |         |     |   |        |

|       |              | Set by hardware when the Timer 2 low byte overflows from 0xFF to 0x00. TF2L will be set when the low byte overflows regardless of the Timer 2 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                            |            |             |         |     |   |        |

| 5     | TF2LEN       | Timer 2 Low Byte Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |             |         |     |   |        |

|       |              | When set to 1, this bit enables Timer 2 Low Byte interrupts. If Timer 2 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 2 overflows.                                                                                                                                                                                                                                                                                                       |            |             |         |     |   |        |

| 4     | TF2CEN       | Timer 2 Comparator Capture Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |             |         |     |   |        |

|       |              | When set to 1, this bit enables Timer 2 Comparator Capture Mode. If TF2CEN is set, on a rising edge of the Comparator0 output the current 16-bit timer value in TMR2H:TMR2L will be copied to TMR2RLH:TMR2RLL. If Timer 2 interrupts are also enabled, an interrupt will be generated on this event.                                                                                                                                                                              |            |             |         |     |   |        |

| 3     | T2SPLIT      | Timer 2 Split Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |             |         |     |   |        |

|       |              | When this bit is set, Timer 2 operates as two 8-bit timers with auto-reload.                                                                                                                                                                                                                                                                                                                                                                                                      |            |             |         |     |   |        |

|       |              | 0: Timer 2 operates in 16-bit auto-reload mode.                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |             |         |     |   |        |

|       | TDO          | 1: Timer 2 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                                                                                                                              |            |             |         |     |   |        |

| 2     | TR2          | <b>Timer 2 Run Control.</b><br>Timer 2 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR2H only; TMR2L is always enabled in split mode.                                                                                                                                                                                                                                                                                                        |            |             |         |     |   |        |

| 1     | Unused       | Read = 0b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |             |         |     |   |        |

| 0     | T2XCLK       | Timer 2 External Clock Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |             |         |     |   |        |

|       |              | This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock Select bits (T2MH and T2ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.<br>0: Timer 2 clock is the system clock divided by 12.<br>1: Timer 2 clock is the external clock divided by 8 (synchronized with SYSCLK). |            |             |         |     |   |        |