Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                          |

| Number of I/O              | 54                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | 32 x 8                                                         |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 16x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 64-TQFP                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f708-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 18.3. | EMIF Operating Modes                                             | 117 |

|--------------|------------------------------------------------------------------|-----|

|              | Non-multiplexed 16-bit MOVX Timing                               |     |

|              | Non-multiplexed 8-bit MOVX without Bank Select Timing            |     |

|              | Non-Multiplexed 8-Bit MOVX with Bank Select Timing               |     |

|              | Multiplexed 16-bit MOVX Timing                                   |     |

| Figure 18.8. | Multiplexed 8-Bit MOVX without Bank Select Timing                | 124 |

| -            | Multiplexed 8-Bit MOVX with Bank Select Timing                   |     |

| -            | EEPROM Block Diagram                                             |     |

|              | Reset Sources                                                    |     |

| Figure 25.2. | Power-On and VDD Monitor Reset Timing                            | 164 |

| Figure 27.1. | Oscillator Options                                               | 171 |

| Figure 27.2. | External 32.768 kHz Quartz Crystal Oscillator Connection Diagram | 178 |

| Figure 28.1. | Port I/O Functional Block Diagram                                | 180 |

|              | Port I/O Cell Block Diagram                                      |     |

|              | Port I/O Overdrive Current                                       |     |

| Figure 28.4. | Crossbar Priority Decoder—Possible Pin Assignments               | 186 |

|              | Crossbar Priority Decoder in Example Configuration—              |     |

| -            | No Pins Skipped                                                  | 187 |

| Figure 28.6. | Crossbar Priority Decoder in Example Configuration—              |     |

|              | 3 Pins Skipped                                                   |     |

| Figure 29.1. | CRC0 Block Diagram                                               | 211 |

| Figure 30.1. | SMBus Block Diagram                                              | 219 |

| Figure 30.2. | Typical SMBus Configuration                                      | 220 |

|              | SMBus Transaction                                                |     |

| Figure 30.4. | Typical SMBus SCL Generation                                     | 223 |

| Figure 30.5. | Typical Master Write Sequence                                    | 232 |

| Figure 30.6. | Typical Master Read Sequence                                     | 233 |

| Figure 30.7. | Typical Slave Write Sequence                                     | 234 |

| Figure 30.8. | Typical Slave Read Sequence                                      | 235 |

|              | SPI Block Diagram                                                |     |

|              | Multiple-Master Mode Connection Diagram                          |     |

|              | 3-Wire Single Master and Single Slave Mode Connection Diagram .  |     |

|              | 4-Wire Single Master Mode and Slave Mode Connection Diagram      |     |

|              | Master Mode Data/Clock Timing                                    |     |

|              | Slave Mode Data/Clock Timing (CKPHA = 0)                         |     |

| -            | Slave Mode Data/Clock Timing (CKPHA = 1)                         |     |

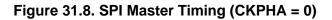

|              | SPI Master Timing (CKPHA = 0)                                    |     |

|              | SPI Master Timing (CKPHA = 1)                                    |     |

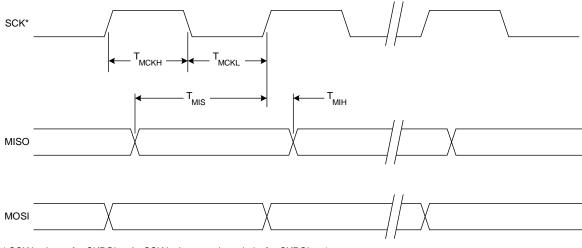

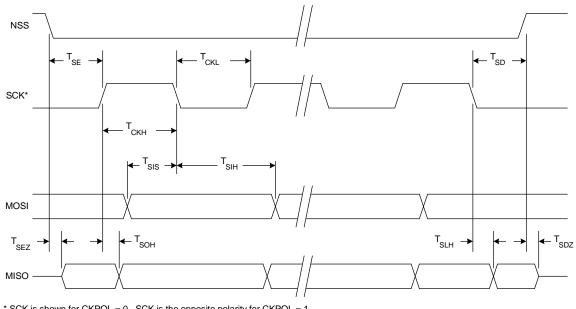

|              | ). SPI Slave Timing (CKPHA = 0)                                  |     |

|              | . SPI Slave Timing (CKPHA = 1)                                   |     |

|              | UART0 Block Diagram                                              |     |

|              | UART0 Baud Rate Logic                                            |     |

|              | UART Interconnect Diagram                                        |     |

|              | 8-Bit UART Timing Diagram                                        |     |

| Figure 32.5. | 9-Bit UART Timing Diagram                                        | 257 |

| SFR Definition 21.5. EIP1: Extended Interrupt Priority 1         | . 144 |

|------------------------------------------------------------------|-------|

| SFR Definition 21.6. EIP2: Extended Interrupt Priority 2         | . 145 |

| SFR Definition 21.7. IT01CF: INT0/INT1 Configuration             |       |

| SFR Definition 22.1. PSCTL: Program Store R/W Control            | . 153 |

| SFR Definition 22.2. FLKEY: Flash Lock and Key                   | . 154 |

| SFR Definition 23.1. EEADDR: EEPROM Byte Address                 |       |

| SFR Definition 23.2. EEDATA: EEPROM Byte Data                    |       |

| SFR Definition 23.3. EECNTL: EEPROM Control                      | . 158 |

| SFR Definition 23.4. EEKEY: EEPROM Protect Key                   |       |

| SFR Definition 24.1. PCON: Power Control                         | . 162 |

| SFR Definition 25.1. VDM0CN: VDD Monitor Control                 | . 166 |

| SFR Definition 25.2. RSTSRC: Reset Source                        |       |

| SFR Definition 26.1. WDTCN: Watchdog Timer Control               | . 170 |

| SFR Definition 27.1. CLKSEL: Clock Select                        | . 172 |

| SFR Definition 27.2. OSCICL: Internal H-F Oscillator Calibration | . 173 |

| SFR Definition 27.3. OSCICN: Internal H-F Oscillator Control     | . 174 |

| SFR Definition 27.4. OSCXCN: External Oscillator Control         | . 176 |

| SFR Definition 28.1. XBR0: Port I/O Crossbar Register 0          | . 190 |

| SFR Definition 28.2. XBR1: Port I/O Crossbar Register 1          |       |

| SFR Definition 28.3. P0MASK: Port 0 Mask Register                |       |

| SFR Definition 28.4. P0MAT: Port 0 Match Register                |       |

| SFR Definition 28.5. P1MASK: Port 1 Mask Register                |       |

| SFR Definition 28.6. P1MAT: Port 1 Match Register                |       |

| SFR Definition 28.7. P0: Port 0                                  | . 195 |

| SFR Definition 28.8. P0MDIN: Port 0 Input Mode                   | . 195 |

| SFR Definition 28.9. P0MDOUT: Port 0 Output Mode                 |       |

| SFR Definition 28.10. P0SKIP: Port 0 Skip                        |       |

| SFR Definition 28.11. P0DRV: Port 0 Drive Strength               | . 197 |

| SFR Definition 28.12. P1: Port 1                                 |       |

| SFR Definition 28.13. P1MDIN: Port 1 Input Mode                  | . 198 |

| SFR Definition 28.14. P1MDOUT: Port 1 Output Mode                |       |

| SFR Definition 28.15. P1SKIP: Port 1 Skip                        | . 199 |

| SFR Definition 28.16. P1DRV: Port 1 Drive Strength               |       |

| SFR Definition 28.17. P2: Port 2                                 |       |

| SFR Definition 28.18. P2MDIN: Port 2 Input Mode                  |       |

| SFR Definition 28.19. P2MDOUT: Port 2 Output Mode                |       |

| SFR Definition 28.20. P2SKIP: Port 2 Skip                        |       |

| SFR Definition 28.21. P2DRV: Port 2 Drive Strength               |       |

| SFR Definition 28.22. P3: Port 3                                 | . 202 |

| SFR Definition 28.23. P3MDIN: Port 3 Input Mode                  | . 203 |

| SFR Definition 28.24. P3MDOUT: Port 3 Output Mode                | . 203 |

| SFR Definition 28.25. P3DRV: Port 3 Drive Strength               |       |

| SFR Definition 28.26. P4: Port 4                                 |       |

| SFR Definition 28.27. P4MDIN: Port 4 Input Mode                  |       |

| SFR Definition 28.28. P4MDOUT: Port 4 Output Mode                |       |

|                                                                  | -     |

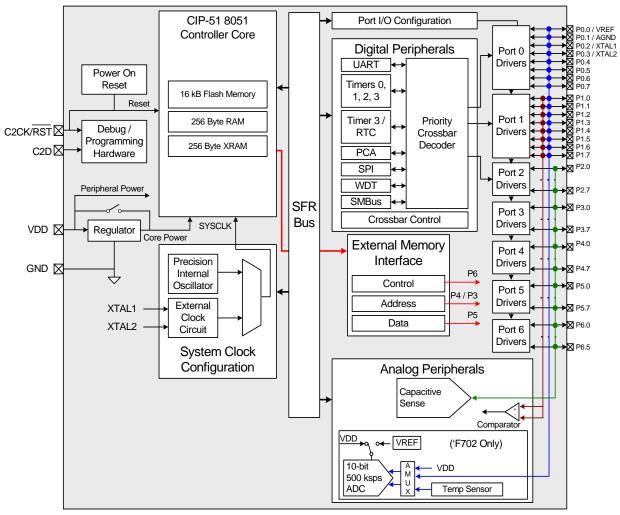

## 1. System Overview

C8051F70x/71x devices are fully integrated, system-on-a-chip, capacitive sensing mixed-signal MCUs. Highlighted features are listed below. Refer to Table 2.1 for specific product feature selection and part ordering numbers.

- High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Capacitive Sense interface with 38 input channels

- 10-bit 500 ksps single-ended ADC with 16 external channels and integrated temperature sensor

- Precision calibrated 24.5 MHz internal oscillator

- 16 kB of on-chip Flash memory

- 512 bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with three capture/compare modules

- On-chip internal voltage reference

- On-chip Watchdog timer

- On-chip Power-On Reset and Supply Monitor

- On-chip Voltage Comparator

- 54 general purpose I/O

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F70x/71x devices are truly stand-alone, system-on-a-chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The C8051F70x/71x processors include Silicon Laboratories' 2-Wire C2 Debug and Programming interface, which allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection of memory, viewing and modification of special function registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 1.8–3.6 V operation over the industrial temperature rang<u>e</u> (–45 to +85 °C). An internal LDO is used to supply the processor core voltage at 1.8 V. The Port I/O and RST pins are tolerant of input signals up to 2 V above the  $V_{DD}$  supply, with the exception of P0.3. See Table 2.1 for ordering information. Block diagrams of the devices in the C8051F70x/71x family are shown in Figure 1.1.

Figure 1.2. C8051F702/3 Block Diagram

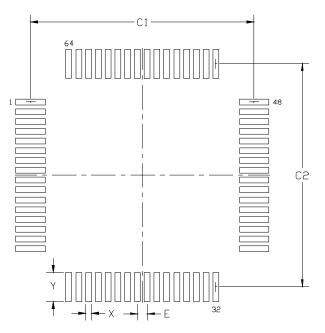

Figure 4.2. TQFP-64 PCB Land Pattern

#### Table 4.2. TQFP-64 PCB Land Pattern Dimensions

| Dimension | Min   | Мах   |

|-----------|-------|-------|

| C1        | 11.30 | 11.40 |

| C2        | 11.30 | 11.40 |

| E         | 0.50  | BSC   |

| X         | 0.20  | 0.30  |

| Y         | 1.40  | 1.50  |

Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This land pattern design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

#### Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

Card Assembly

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

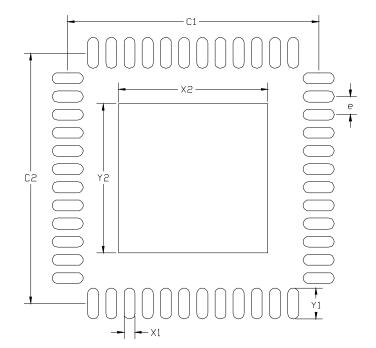

#### Figure 6.2. QFN-48 PCB Land Pattern

Table 6.2. QFN-48 PCB Land Pattern Dimensions

| Dimension | Min  | Max  |

|-----------|------|------|

| e         | 0.50 | BSC  |

| C1        | 6.80 | 6.90 |

| C2        | 6.80 | 6.90 |

| X1        | 0.20 | 0.30 |

| X2        | 4.00 | 4.10 |

| Y1        | 0.75 | 0.85 |

| Y2        | 4.00 | 4.10 |

Notes: General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-7351 guidelines.

- 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

Stencil Design

- 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 7. The stencil thickness should be 0.125 mm (5 mils).

- 8. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

9. A 3x3 array of 1.20 mm square openings on 1.40 mm pitch should be used for the center ground pad.

Card Assembly

- 10. A No-Clean, Type-3 solder paste is recommended.

- 11. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 9.2. Electrical Characteristics

#### **Table 9.2. Global Electrical Characteristics**

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                                               | Conditions                                                                                                                                                                                                                                                                                                                                                         | Min        | Тур                                    | Max                  | Units                            |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------|----------------------|----------------------------------|

| Supply Voltage <sup>1</sup>                                             | Regulator in Normal Mode<br>Regulator in Bypass Mode                                                                                                                                                                                                                                                                                                               | 1.8<br>1.7 | 3.0<br>1.8                             | 3.6<br>1.9           | V<br>V                           |

| Digital Supply Current with<br>CPU Active (Normal Mode <sup>2,3</sup> ) | $V_{DD} = 1.8 \text{ V}, \text{ Clock} = 25 \text{ MHz}$<br>$V_{DD} = 1.8 \text{ V}, \text{ Clock} = 1 \text{ MHz}$<br>$V_{DD} = 1.8 \text{ V}, \text{ Clock} = 32 \text{ kHz}$<br>$V_{DD} = 3.0 \text{ V}, \text{ Clock} = 25 \text{ MHz}$<br>$V_{DD} = 3.0 \text{ V}, \text{ Clock} = 1 \text{ MHz}$<br>$V_{DD} = 3.0 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ |            | 5.0<br>1.2<br>175<br>5.5<br>1.3<br>190 | 6.5<br>—<br>7.0<br>— | mA<br>mA<br>μA<br>mA<br>mA<br>μA |

| Digital Supply Current with<br>CPU Inactive (Idle Mode <sup>2,3</sup> ) | $V_{DD} = 1.8 \text{ V}, \text{ Clock} = 25 \text{ MHz}$<br>$V_{DD} = 1.8 \text{ V}, \text{ Clock} = 1 \text{ MHz}$<br>$V_{DD} = 1.8 \text{ V}, \text{ Clock} = 32 \text{ kHz}$<br>$V_{DD} = 3.0 \text{ V}, \text{ Clock} = 25 \text{ MHz}$<br>$V_{DD} = 3.0 \text{ V}, \text{ Clock} = 1 \text{ MHz}$<br>$V_{DD} = 3.0 \text{ V}, \text{ Clock} = 32 \text{ kHz}$ |            | 2.5<br>180<br>90<br>3.2<br>200<br>110  | 4.0<br>—<br>4.5<br>— | mA<br>μA<br>μA<br>mA<br>μA       |

| Digital Supply Current<br>(shutdown) <sup>3</sup>                       | Stop/suspend mode, Reg On, 25 °C                                                                                                                                                                                                                                                                                                                                   |            | 80                                     | 90                   | μA                               |

| (shuldown)*                                                             | Stop/suspend mode, Reg Bypass, 25 °C                                                                                                                                                                                                                                                                                                                               | —          | 2                                      | 4                    | μA                               |

| Digital Supply RAM Data<br>Retention Voltage                            |                                                                                                                                                                                                                                                                                                                                                                    | _          | 1.3                                    |                      | V                                |

| Specified Operating<br>Temperature Range                                |                                                                                                                                                                                                                                                                                                                                                                    | -40        | _                                      | +85                  | °C                               |

| SYSCLK<br>(system clock frequency)                                      | See Note 3.                                                                                                                                                                                                                                                                                                                                                        | 0          | —                                      | 25                   | MHz                              |

| Tsysl (SYSCLK low time)                                                 |                                                                                                                                                                                                                                                                                                                                                                    | 18         | _                                      |                      | ns                               |

| Tsysh (SYSCLK high time)                                                |                                                                                                                                                                                                                                                                                                                                                                    | 18         | _                                      |                      | ns                               |

2. Includes bias current for internal voltage regulator.

3. SYSCLK must be at least 32 kHz to enable debugging.

### Table 9.14. Comparator Electrical Characteristics

$V_{DD}$  = 3.0 V, –40 to +85 °C unless otherwise noted.

| Parameter                                         | Conditions             | Min   | Тур  | Max                    | Units |

|---------------------------------------------------|------------------------|-------|------|------------------------|-------|

| Response Time:                                    | CP0+ - CP0- = 100 mV   |       | 300  |                        | ns    |

| Mode 0, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  | _     | 200  | _                      | ns    |

| Response Time:                                    | CP0+ – CP0– = 100 mV   |       | 400  | _                      | ns    |

| Mode 1, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  | _     | 350  | _                      | ns    |

| Response Time:                                    | CP0+ – CP0– = 100 mV   | _     | 570  | _                      | ns    |

| Mode 2, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  |       | 870  | _                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV   |       | 1500 |                        | ns    |

| Mode 3, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  | _     | 4500 | _                      | ns    |

| Common-Mode Rejection Ratio                       |                        |       | 1    | 4                      | mV/V  |

| Positive Hysteresis 1                             | Mode 2, CP0HYP1–0 = 00 | _     | 0    | 1                      | mV    |

| Positive Hysteresis 2                             | Mode 2, CP0HYP1–0 = 01 | 2     | 5    | 10                     | mV    |

| Positive Hysteresis 3                             | Mode 2, CP0HYP1–0 = 10 | 7     | 10   | 20                     | mV    |

| Positive Hysteresis 4                             | Mode 2, CP0HYP1–0 = 11 | 10    | 20   | 30                     | mV    |

| Negative Hysteresis 1                             | Mode 2, CP0HYN1–0 = 00 | —     | 0    | 1                      | mV    |

| Negative Hysteresis 2                             | Mode 2, CP0HYN1–0 = 01 | 2     | 5    | 10                     | mV    |

| Negative Hysteresis 3                             | Mode 2, CP0HYN1–0 = 10 | 7     | 10   | 20                     | mV    |

| Negative Hysteresis 4                             | Mode 2, CP0HYN1–0 = 11 | 10    | 20   | 30                     | mV    |

| Inverting or Non-Inverting Input<br>Voltage Range |                        | -0.25 | _    | V <sub>DD</sub> + 0.25 | V     |

| Input Offset Voltage                              |                        | -7.5  | _    | 7.5                    | mV    |

| Power Specifications                              |                        |       |      |                        |       |

| Power Supply Rejection                            |                        | _     | 0.1  | _                      | mV/V  |

| Powerup Time                                      |                        | —     | 10   | —                      | μs    |

| Supply Current at DC                              | Mode 0                 | —     | 25   |                        | μA    |

|                                                   | Mode 1                 | —     | 10   | _                      | μA    |

|                                                   | Mode 2                 | —     | 3    | —                      | μA    |

|                                                   | Mode 3                 | —     | 0.5  | _                      | μA    |

| Note: Vcm is the common-mode vol                  | tage on CP0+ and CP0–. |       |      |                        |       |

# SFR Definition 13.1. REG0CN: Voltage Regulator Control

| Bit   | 7      | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------|--------|-----|-----|-----|-----|-----|-----|

| Name  | STOPCF | BYPASS |     |     |     |     |     |     |

| Туре  | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   |

### SFR Address = 0xB9; SFR Page = F

| Bit | Name     | Function                                                                                                                                                                                                                                                                                |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STOPCF   | Stop Mode Configuration.                                                                                                                                                                                                                                                                |

|     |          | This bit configures the regulator's behavior when the device enters STOP mode.<br>0: Regulator is still active in STOP mode. Any enabled reset source will reset the<br>device.<br>1: Regulator is shut down in STOP mode. Only the RST pin or power cycle can reset                    |

|     |          | the device.                                                                                                                                                                                                                                                                             |

| 6   | BYPASS   | Bypass Internal Regulator.                                                                                                                                                                                                                                                              |

|     |          | This bit places the regulator in bypass mode, allowing the core to run directly from the $V_{DD}$ supply pin.                                                                                                                                                                           |

|     |          | 0: Normal Mode—Regulator is on and regulates V <sub>DD</sub> down to the core voltage.                                                                                                                                                                                                  |

|     |          | 1: Bypass Mode—Regulator is in bypass mode, and the microcontroller core operates directly from the V <sub>DD</sub> supply voltage.                                                                                                                                                     |

|     |          | IMPORTANT: Bypass mode is for use with an external regulator as the supply voltage only. Never place the regulator in bypass mode when the $V_{DD}$ supply voltage is greater than the specifications given in Table 9.1 on page 47. Doing so may cause permanent damage to the device. |

| 5:0 | Reserved | Reserved. Must Write 000000b.                                                                                                                                                                                                                                                           |

| Mnemonic             | Description                                | Bytes | Clock<br>Cycles |  |

|----------------------|--------------------------------------------|-------|-----------------|--|

| XRL direct, #data    | Exclusive-OR immediate to direct byte      | 3     | 3               |  |

| CLR A                | Clear A                                    | 1     | 1               |  |

| CPL A                | Complement A                               | 1     | 1               |  |

| RL A                 | Rotate A left                              | 1     | 1               |  |

| RLC A                | Rotate A left through Carry                | 1     | 1               |  |

| RR A                 | Rotate A right                             | 1     | 1               |  |

| RRC A                | Rotate A right through Carry               | 1     | 1               |  |

| SWAP A               | Swap nibbles of A                          | 1     | 1               |  |

| Data Transfer        |                                            |       |                 |  |

| MOV A, Rn            | Move Register to A                         | 1     | 1               |  |

| MOV A, direct        | Move direct byte to A                      | 2     | 2               |  |

| MOV A, @Ri           | Move indirect RAM to A                     | 1     | 2               |  |

| MOV A, #data         | Move immediate to A                        | 2     | 2               |  |

| MOV Rn, A            | Move A to Register                         | 1     | 1               |  |

| MOV Rn, direct       | Move direct byte to Register               | 2     | 2               |  |

| MOV Rn, #data        | Move immediate to Register                 | 2     | 2               |  |

| MOV direct, A        | Move A to direct byte                      | 2     | 2               |  |

| MOV direct, Rn       | Move Register to direct byte               | 2     | 2               |  |

| MOV direct, direct   | Move direct byte to direct byte            | 3     | 3               |  |

| MOV direct, @Ri      | Move indirect RAM to direct byte           | 2     | 2               |  |

| MOV direct, #data    | Move immediate to direct byte              | 3     | 3               |  |

| MOV @Ri, A           | Move A to indirect RAM                     | 1     | 2               |  |

| MOV @Ri, direct      | Move direct byte to indirect RAM           | 2     | 2               |  |

| MOV @Ri, #data       | Move immediate to indirect RAM             | 2     | 2               |  |

| MOV DPTR, #data16    | Load DPTR with 16-bit constant             | 3     | 3               |  |

| MOVC A, @A+DPTR      | Move code byte relative DPTR to A          | 1     | 3               |  |

| MOVC A, @A+PC        | Move code byte relative PC to A            | 1     | 3               |  |

| MOVX A, @Ri          | Move external data (8-bit address) to A    | 1     | 3               |  |

| MOVX @Ri, A          | Move A to external data (8-bit address)    | 1     | 3               |  |

| MOVX A, @DPTR        | Move external data (16-bit address) to A   | 1     | 3               |  |

| MOVX @DPTR, A        | Move A to external data (16-bit address)   | 1     | 3               |  |

| PUSH direct          | Push direct byte onto stack                | 2     | 2               |  |

| POP direct           | Pop direct byte from stack                 | 2     | 2               |  |

| XCH A, Rn            | Exchange Register with A                   | 1     | 1               |  |

| XCH A, direct        | Exchange direct byte with A                | 2     | 2               |  |

| XCH A, @Ri           | Exchange indirect RAM with A               | 1     | 2               |  |

| XCHD A, @Ri          | Exchange low nibble of indirect RAM with A | 1     | 2               |  |

| Boolean Manipulation | 5                                          |       |                 |  |

| CLR C                | Clear Carry                                | 1     | 1               |  |

| CLR bit              | Clear direct bit                           | 2     | 2               |  |

| SETB C               | Set Carry                                  | 1     | 1               |  |

| SETB bit             | Set direct bit                             | 2     | 2               |  |

| CPL C                | Complement Carry                           | 1     | 1               |  |

| CPL bit              | Complement direct bit                      | 2     | 2               |  |

Table 16.1. CIP-51 Instruction Set Summary (Continued)

# **18. External Data Memory Interface and On-Chip XRAM**

For C8051F70x/71x devices, 256 B of RAM are included on-chip and mapped into the external data memory space (XRAM). Additionally, an External Memory Interface (EMIF) is available on the C8051F700/1/2/3/8/9 and C8051F710/1 devices, which can be used to access off-chip data memories and memory-mapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using the MOVX indirect addressing mode using R0 or R1. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMI0CN, shown in SFR Definition 18.1).

**Note:** The MOVX instruction can also be used for writing to the Flash memory. See Section "22. Flash Memory" on page 148 for details. The MOVX instruction accesses XRAM by default.

#### 18.1. Accessing XRAM

The XRAM memory space is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read from or written to. The second method uses R0 or R1 in combination with the EMI0CN register to generate the effective XRAM address. Examples of both of these methods are given below.

#### 18.1.1. 16-Bit MOVX Example

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

MOVDPTR, #1234h; load DPTR with 16-bit address to read (0x1234)MOVXA, @DPTR; load contents of 0x1234 into accumulator A

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 18.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of the EMI0CN SFR to determine the upper 8-bits of the effective address to be accessed and the contents of R0 or R1 to determine the lower 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x1234 into the accumulator A.

| MOV  | EMIOCN, #12h | ; load high byte of address into EMIOCN      |

|------|--------------|----------------------------------------------|

| MOV  | R0, #34h     | ; load low byte of address into R0 (or R1)   |

| MOVX | a, @R0       | ; load contents of 0x1234 into accumulator A |

### SFR Definition 28.6. P1MAT: Port 1 Match Register

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | P1MAT[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 1          |   |   |   |   |   |   |   |  |

SFR Address = 0xE1; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                                    |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MAT[7:0] | Port 1 Match Value.                                                                                                                                                                         |

|     |            | Match comparison value used on Port 1 for bits in P1MASK which are set to 1.<br>0: P1.n pin logic value is compared with logic LOW.<br>1: P1.n pin logic value is compared with logic HIGH. |

#### 28.6. Special Function Registers for Accessing and Configuring Port I/O

All Port I/O are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

Each Port has a corresponding PnSKIP register which allows its individual Port pins to be assigned to digital functions or skipped by the Crossbar. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

The Port input mode of the I/O pins is defined using the Port Input Mode registers (PnMDIN). Each Port cell can be configured for analog or digital I/O. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings.

# SFR Definition 28.17. P2: Port 2

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---------|---|---|---|---|---|---|---|--|--|--|

| Name  | P2[7:0] |   |   |   |   |   |   |   |  |  |  |

| Туре  | R/W     |   |   |   |   |   |   |   |  |  |  |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |

SFR Address = 0xA0; SFR Page = All Pages; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------|

| 7:0 | P2[7:0] | <b>Port 2 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. |       | 0: P2.n Port pin is logic<br>LOW.<br>1: P2.n Port pin is logic<br>HIGH. |

### SFR Definition 28.18. P2MDIN: Port 2 Input Mode

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-------------|---|---|---|---|---|---|---|--|--|--|

| Name  | P2MDIN[7:0] |   |   |   |   |   |   |   |  |  |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |  |  |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |  |  |

#### SFR Address = 0xF3; SFR Page = F

| Bit | Name        | Function                                                                                                    |

|-----|-------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDIN[7:0] | Analog Configuration Bits for P2.7–P2.0 (respectively).                                                     |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled. |

|     |             | 0: Corresponding P2.n pin is configured for analog mode.                                                    |

|     |             | 1: Corresponding P2.n pin is not configured for analog mode.                                                |

## SFR Definition 31.3. SPI0CKR: SPI0 Clock Rate

| Bit           | 7               | 6                                                                                                    | 5                                                                                                          | 4                                                                                       | 3                                                              | 2                                             | 1                                                                | 0                                |  |  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------|----------------------------------|--|--|--|--|

| Name SCR[7:0] |                 |                                                                                                      |                                                                                                            |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |  |  |

| Туре          |                 | R/W                                                                                                  |                                                                                                            |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |  |  |

| Reset         | 0 0 0 0 0 0 0 0 |                                                                                                      |                                                                                                            |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |  |  |

| SFR Ad        | ldress = 0xA2   | 2; SFR Page                                                                                          | e = F                                                                                                      |                                                                                         | I                                                              |                                               |                                                                  |                                  |  |  |  |  |

| Bit           | Name            |                                                                                                      | Function                                                                                                   |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |  |  |

| 7:0           | SCR[7:0]        | configured<br>sion of the<br>the system<br>register.<br>f <sub>SCK</sub> =<br>for 0 <= S<br>Example: | s determine<br>d for master<br>e system clo<br>n clock frequ<br>$\frac{SY}{2 \times (SPI00)}$<br>PI0CKR <= | mode opera<br>ck, and is giv<br>Jency and S<br>SCLK<br>CKR[7:0] +<br>255<br>= 2 MHz and | tion. The S(<br>ven in the fo<br>PIOCKR is t<br>$\overline{1}$ | CK clock fre<br>Illowing equ<br>he 8-bit valu | en the SPI0 r<br>quency is a d<br>ation, where<br>le held in the | ivided ver-<br>S <i>YSCLK</i> is |  |  |  |  |

## SFR Definition 31.4. SPI0DAT: SPI0 Data

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|--------------|---|---|---|---|---|---|---|--|--|--|

| Name  | SPI0DAT[7:0] |   |   |   |   |   |   |   |  |  |  |

| Туре  | R/W          |   |   |   |   |   |   |   |  |  |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xA3; SFR Page = 0

| Bit | Name         | Function                                                                                                                                                                                                                                     |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |

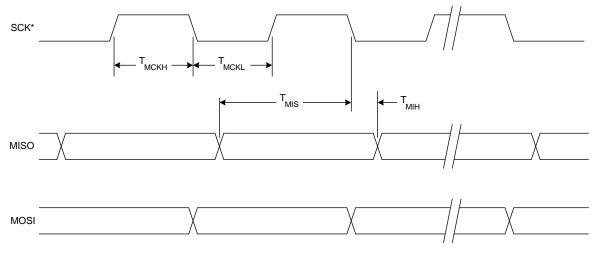

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

### Figure 31.9. SPI Master Timing (CKPHA = 1)

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

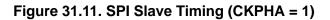

### 32.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 32.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 32.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "33.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 265). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK/4, SYSCLK/12, SYSCLK/48, the external oscillator clock/8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 32.1-A and Equation 32.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

### Equation 32.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "33. Timers" on page 262. A quick reference for typical baud rates and system clock frequencies is given in Table 32.1 through Table 32.2. The internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

## SFR Definition 32.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit     | 7            | 7         6         5         4         3         2         1         0 |             |    |   |   |   |   |  |  |  |  |

|---------|--------------|-------------------------------------------------------------------------|-------------|----|---|---|---|---|--|--|--|--|

| Name    | SBUF0[7:0]   |                                                                         |             |    |   |   |   |   |  |  |  |  |

| Туре    |              |                                                                         |             | R/ | W |   |   |   |  |  |  |  |

| Reset   | 0            | 0                                                                       | 0           | 0  | 0 | 0 | 0 | 0 |  |  |  |  |

| SFR Add | dress = 0x99 | ; SFR Page                                                              | = All Pages |    |   |   |   |   |  |  |  |  |

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                    |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SBUF0[7:0] | Serial Data Buffer Bits 7–0 (MSB–LSB).                                                                                                                                                                                                                                                                                      |

|     |            | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for<br>serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of<br>SBUF0 returns the contents of the receive latch. |

# SFR Definition 33.6. TH0: Timer 0 High Byte

| Bit   | 7            | 6             | 5             | 4 | 3        | 2 | 1 | 0 |  |  |  |  |

|-------|--------------|---------------|---------------|---|----------|---|---|---|--|--|--|--|

| Nam   | e            | ТН0[7:0]      |               |   |          |   |   |   |  |  |  |  |

| Туре  | ;            | R/W           |               |   |          |   |   |   |  |  |  |  |

| Rese  | et 0         | 0 0 0 0 0 0 0 |               |   |          |   |   |   |  |  |  |  |

| SFR A | ddress = 0x8 | C; SFR Page   | e = All Pages | 5 |          |   |   |   |  |  |  |  |

| Bit   | Name         |               |               |   | Function |   |   |   |  |  |  |  |

| 7:0   | TH0[7:0]     | Timer 0 Hig   | h Ryta        |   |          |   |   |   |  |  |  |  |

# SFR Definition 33.7. TH1: Timer 1 High Byte

| Bit                                      | 7             | 6                  | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------|---------------|--------------------|---|---|---|---|---|---|

| Nam                                      | Name TH1[7:0] |                    |   |   |   |   |   |   |

| Type R/W                                 |               |                    |   |   |   |   |   |   |

| Rese                                     | et 0          | 0                  | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0x8D; SFR Page = All Pages |               |                    |   |   |   |   |   |   |

| Bit                                      | Name          | Function           |   |   |   |   |   |   |

| 7:0                                      | TH1[7:0]      | Timer 1 High Byte. |   |   |   |   |   |   |

|  | The TH1 register is the high byte of the 16-bit Timer 1. |

|--|----------------------------------------------------------|

|--|----------------------------------------------------------|

# SFR Definition 34.5. PCA0L: PCA Counter/Timer Low Byte

| Bit                              | 7    | 6             | 5   | 4   | 3      | 2   | 1   | 0   |

|----------------------------------|------|---------------|-----|-----|--------|-----|-----|-----|

| Name                             |      |               |     | PCA | )[7:0] |     |     |     |

| Туре                             | R/W  | R/W           | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset                            | 0    | 0             | 0   | 0   | 0      | 0   | 0   | 0   |

| SFR Address = 0xF9; SFR Page = 0 |      |               |     |     |        |     |     |     |

| Bit                              | Name | Name Function |     |     |        |     |     |     |

| Bit | Name      | Function                                                                     |  |  |  |

|-----|-----------|------------------------------------------------------------------------------|--|--|--|

| 7:0 | PCA0[7:0] | PCA Counter/Timer Low Byte.                                                  |  |  |  |

|     |           | The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |  |  |  |

## SFR Definition 34.6. PCA0H: PCA Counter/Timer High Byte

| Bit   | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|-------|-----|-----|-----|------|--------|-----|-----|-----|

| Name  |     |     |     | PCA0 | [15:8] |     |     |     |

| Туре  | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

SFR Address = 0xFA; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | PCA0[15:8] | PCA Counter/Timer High Byte.                                                                                                                                                                                                                        |

|     |            | The PCA0H register holds the high byte (MSB) of the 16-bit PCA Counter/Timer.<br>Reads of this register will read the contents of a "snapshot" register, whose contents<br>are updated only when the contents of PCA0L are read (see Section 34.1). |