Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 54                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | 32 x 8                                                          |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 16x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f708-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 16.1.1. Instruction and CPU Timing                                 | 99  |

|--------------------------------------------------------------------|-----|

| 16.2. CIP-51 Register Descriptions                                 |     |

| 17. Memory Organization                                            |     |

| 17.1. Program Memory                                               |     |

| 17.1.1. MOVX Instruction and Program Memory                        |     |

| 17.2. EEPROM Memory                                                |     |

| 17.3. Data Memory                                                  |     |

| 17.3.1. Internal RAM                                               |     |

| 17.3.1.1. General Purpose Registers                                |     |

| 17.3.1.2. Bit Addressable Locations                                |     |

| 17.3.1.3. Stack                                                    |     |

| 18. External Data Memory Interface and On-Chip XRAM                |     |

| 18.1. Accessing XRAM                                               |     |

| 18.1.1. 16-Bit MOVX Example                                        |     |

| 18.1.2. 8-Bit MOVX Example                                         |     |

| 18.2. Configuring the External Memory Interface                    |     |

| 18.3. Port Configuration                                           | 112 |

| 18.4. Multiplexed and Non-multiplexed Selection                    |     |

| 18.4.1. Multiplexed Configuration                                  |     |

| 18.4.2. Non-multiplexed Configuration                              | 116 |

| 18.5. Memory Mode Selection                                        |     |

| 18.5.1. Internal XRAM Only                                         | 117 |

| 18.5.2. Split Mode without Bank Select                             |     |

| 18.5.3. Split Mode with Bank Select                                |     |

| 18.5.4. External Only                                              |     |

| 18.6. Timing                                                       |     |

| 18.6.1. Non-Multiplexed Mode                                       | 120 |

| 18.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111              | 120 |

| 18.6.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111 | 121 |

| 18.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110           | 122 |

| 18.6.2. Multiplexed Mode                                           | 123 |

| 18.6.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011              | 123 |

| 18.6.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011 | 124 |

| 18.6.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010           | 125 |

| 19. In-System Device Identification                                | 128 |

| 20. Special Function Registers                                     | 130 |

| 21. Interrupts                                                     | 137 |

| 21.1. MCU Interrupt Sources and Vectors                            | 138 |

| 21.1.1. Interrupt Priorities                                       | 138 |

| 21.1.2. Interrupt Latency                                          | 138 |

| 21.2. Interrupt Register Descriptions                              | 140 |

| 21.3. INTO and INT1 External Interrupts                            | 146 |

| 22. Flash Memory                                                   | 148 |

| 22.1. Programming The Flash Memory                                 |     |

| 22.1.1. Flash Lock and Key Functions                               | 148 |

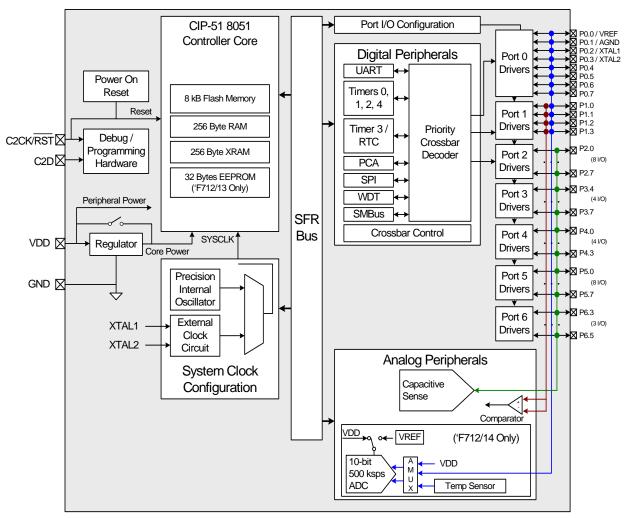

Figure 1.6. C8051F712/13/14/15 Block Diagram

| Name | TQFP64 | TQFP48<br>QFN48 | QFN32 | QFN24 | Туре             | Description                    |

|------|--------|-----------------|-------|-------|------------------|--------------------------------|

| P5.1 | 10     | 10              | 7     | _     | D I/O or<br>A In | Port 5.0.<br>CS0 input pin 26. |

| P5.2 | 7      | 7               | 6     | —     | D I/O or<br>A In | Port 5.2.<br>CS0 input pin 27  |

| P5.3 | 6      | 6               | 5     | _     | D I/O or<br>A In | Port 5.3.<br>CS0 input pin 28. |

| P5.4 | 5      | 5               | 4     | _     | D I/O or<br>A In | Port 5.4.<br>CS0 input pin 29. |

| P5.5 | 4      | 4               | 3     | _     | D I/O or<br>A In | Port 5.5.<br>CS0 input pin 30. |

| P5.6 | 3      | 3               | 2     | _     | D I/O or<br>A In | Port 5.6.<br>CS0 input pin 31. |

| P5.7 | 2      | 2               | 1     | _     | D I/O or<br>A In | Port 5.7.<br>CS0 input pin 32. |

| P6.0 | 1      | _               | _     | _     | D I/O            | Port 6.0.<br>CS0 input pin 33. |

| P6.1 | 64     | _               | _     | _     | D I/O            | Port 6.1.<br>CS0 input pin 34. |

| P6.2 | 63     | _               | _     | _     | D I/O            | Port 6.2.<br>CS0 input pin 35. |

| P6.3 | 62     | 1               | 32    | _     | D I/O            | Port 6.3.<br>CS0 input pin 36. |

| P6.4 | 61     | 48              | 31    | 1     | D I/O            | Port 6.4.<br>CS0 input pin 37. |

| P6.5 | 60     | 47              | 30    | 24    | D I/O            | Port 6.5.<br>CS0 input pin 38. |

Table 3.1. Pin Definitions for the C8051F70x/71x (Continued)

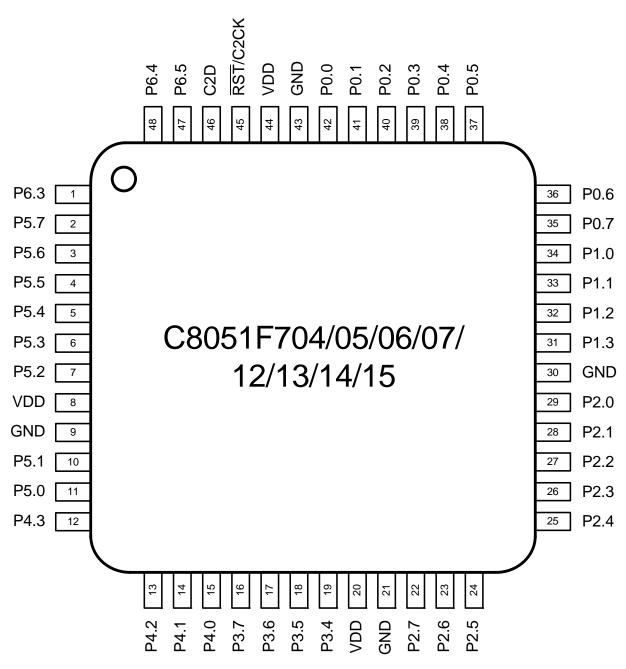

Figure 3.2. C8051F7xx-GQ QFP48 Pinout Diagram (Top View)

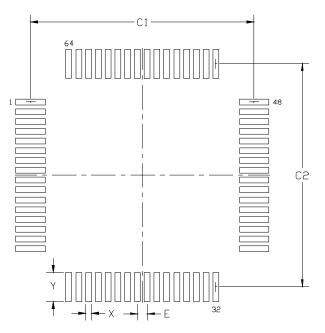

Figure 4.2. TQFP-64 PCB Land Pattern

#### Table 4.2. TQFP-64 PCB Land Pattern Dimensions

| Dimension | Min   | Мах   |

|-----------|-------|-------|

| C1        | 11.30 | 11.40 |

| C2        | 11.30 | 11.40 |

| E         | 0.50  | BSC   |

| X         | 0.20  | 0.30  |

| Y         | 1.40  | 1.50  |

Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This land pattern design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

#### Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

Card Assembly

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 12.1. External Voltage References

To use an external voltage reference, REFSL[1:0] should be set to 00. Bypass capacitors should be added as recommended by the manufacturer of the external voltage reference.

#### 12.2. Internal Voltage Reference Options

A 1.6 V high-speed reference is included on-chip. The high speed internal reference is selected by setting REFSL[1:0] to 11. When selected, the high-speed internal reference will be automatically enabled on an as-needed basis by ADC0.

For applications with a non-varying power supply voltage, using the power supply as the voltage reference can provide ADC0 with added dynamic range at the cost of reduced power supply noise rejection. To use the 1.8 to 3.6 V power supply voltage ( $V_{DD}$ ) or the 1.8 V regulated digital supply voltage as the reference source, REFSL[1:0] should be set to 01 or 10, respectively.

#### 12.3. Analog Ground Reference

To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for ADC0 is taken from the P0.1/AGND pin. Any external sensors sampled by ADC0 should be referenced to the P0.1/AGND pin. The separate analog ground reference option is enabled by setting REFGND to 1. Note that when using this option, P0.1/AGND must be connected to the same potential as GND.

#### 12.4. Temperature Sensor Enable

The TEMPE bit in register REF0CN enables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

## SFR Definition 16.3. SP: Stack Pointer

| Bit    | 7           | 6           | 5           | 4  | 3                | 2 | 1 | 0 |  |  |

|--------|-------------|-------------|-------------|----|------------------|---|---|---|--|--|

| Name   | SP[7:0]     |             |             |    |                  |   |   |   |  |  |

| Туре   |             |             |             | R/ | W                |   |   |   |  |  |

| Reset  | 0           | 0           | 0           | 0  | 0                | 1 | 1 | 1 |  |  |

| SFR Ad | dress = 0x8 | 1; SFR Page | = All Pages |    |                  |   |   |   |  |  |

| D:4    | Marria      |             |             |    | <b>F</b> unction |   |   |   |  |  |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

## SFR Definition 16.4. ACC: Accumulator

| Bit   | 7             | 6             | 5 4 3         |               | 2             | 1         | 0 |   |  |  |

|-------|---------------|---------------|---------------|---------------|---------------|-----------|---|---|--|--|

| Nam   | e             |               |               | ACC           | [7:0]         |           |   |   |  |  |

| Туре  | •             |               |               | R/            | W             |           |   |   |  |  |

| Rese  | et 0          | 0             | 0             | 0             | 0             | 0         | 0 | 0 |  |  |

| SFR A | Address = 0xE | E0; SFR Page  | e = All Pages | ; Bit-Addres  | sable         |           |   |   |  |  |

| Bit   | Name          |               |               |               |               |           |   |   |  |  |

| 7:0   | ACC[7:0]      | Accumulator.  |               |               |               |           |   |   |  |  |

|       |               | This register | is the accur  | mulator for a | rithmetic ope | erations. |   |   |  |  |

Rev. 1.0

## 21. Interrupts

The C8051F70x/71x includes an extended interrupt system supporting several interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE–EIE1). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

## 25.2. Power-Fail Reset / V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 25.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is enabled after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is disabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be disabled after the reset.

**Important Note:** If the  $V_{DD}$  monitor is being turned on from a disabled state, it should be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. In some applications, this reset may be undesirable. If this is not desirable in the application, a delay should be introduced between enabling the monitor and selecting it as a reset source. The procedure for enabling the  $V_{DD}$  monitor and configuring it as a reset source from a disabled state is shown below:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = 1).

- 2. If necessary, wait for the  $V_{DD}$  monitor to stabilize.

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 25.2 for V<sub>DD</sub> monitor timing; note that the power-on-reset delay is not incurred after a V<sub>DD</sub> monitor reset. See Section "9. Electrical Characteristics" on page 47 for complete electrical characteristics of the V<sub>DD</sub> monitor.

### 27.2. Programmable Internal High-Frequency (H-F) Oscillator

All C8051F70x/71x devices include a programmable internal high-frequency oscillator that defaults as the system clock after a system reset. The internal oscillator period can be adjusted via the OSCICL register as defined by SFR Definition 27.2.

On C8051F70x/71x devices, OSCICL is factory calibrated to obtain a 24.5 MHz base frequency.

The internal oscillator output frequency may be divided by 1, 2, 4, or 8, as defined by the IFCN bits in register OSCICN. The divide value defaults to 8 following a reset.

The precision oscillator supports a spread spectrum mode which modulates the output frequency in order to reduce the EMI generated by the system. When enabled (SSE = 1), the oscillator output frequency is modulated by a stepped triangle wave whose frequency is equal to the oscillator frequency divided by 384 (63.8 kHz using the factory calibration). The maximum deviation from the center frequency is  $\pm 0.75\%$ . The output frequency updates occur every 32 cycles and the step size is typically 0.25% of the center frequency.

### SFR Definition 27.2. OSCICL: Internal H-F Oscillator Calibration

| Bit                                       | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0      |  |  |

|-------------------------------------------|-------------|---|---|---|---|---|---|--------|--|--|

| Name                                      | OSCICL[6:0] |   |   |   |   |   |   |        |  |  |

| Туре                                      | R/W         |   |   |   |   |   |   |        |  |  |

| ResetVariesVariesVariesVariesVariesVaries |             |   |   |   |   |   |   | Varies |  |  |

|                                           |             |   |   |   |   |   |   |        |  |  |

#### SFR Address = 0xBF; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                   |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0 | OSCICL[7:0] | Internal Oscillator Calibration Bits.                                                                                                                                                                                                                                                                      |

|     |             | These bits determine the internal oscillator period. When set to 00000000b, the H-F oscillator operates at its fastest setting. When set to 11111111b, the H-F oscillator operates at its slowest setting. The reset value is factory calibrated to generate an internal oscillator frequency of 24.5 MHz. |

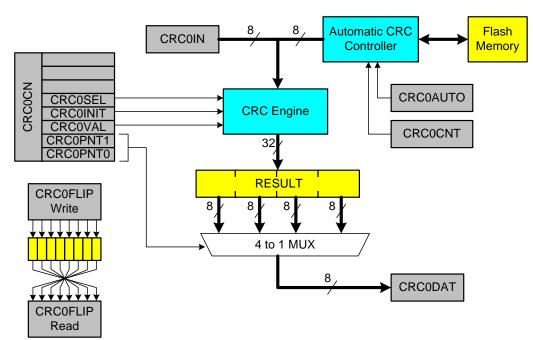

## 29. Cyclic Redundancy Check Unit (CRC0)

C8051F70x/71x devices include a cyclic redundancy check unit (CRC0) that can perform a CRC using a 16-bit or 32-bit polynomial. CRC0 accepts a stream of 8-bit data written to the CRC0IN register. CRC0 posts the 16-bit or 32-bit result to an internal register. The internal result register may be accessed indirectly using the CRC0PNT bits and CRC0DAT register, as shown in Figure 29.1. CRC0 also has a bit reverse register for quick data manipulation.

Figure 29.1. CRC0 Block Diagram

### 29.1. 16-bit CRC Algorithm

The C8051F70x/71x CRC unit calculates the 16-bit CRC MSB-first, using a poly of 0x1021. The following describes the 16-bit CRC algorithm performed by the hardware:

- 1. XOR the most-significant byte of the current CRC result with the input byte. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x0000 or 0xFFFF).

- 2. If the MSB of the CRC result is set, left-shift the CRC result, and then XOR the CRC result with the polynomial (0x1021).

- 3. If the MSB of the CRC result is not set, left-shift the CRC result.

- 4. Repeat at Step 2 for the number of input bits (8).

For example, the 16-bit C8051F70x/71x CRC algorithm can be described by the following code:

```

unsigned short UpdateCRC (unsigned short CRC_acc, unsigned char CRC_input) {

unsigned char i;

// loop counter

#define POLY 0x1021

// Create the CRC "dividend" for polynomial arithmetic (binary arithmetic

// with no carries)

CRC_acc = CRC_acc ^ (CRC_input << 8);</pre>

// "Divide" the poly into the dividend using CRC XOR subtraction

// CRC_acc holds the "remainder" of each divide

// Only complete this division for 8 bits since input is 1 byte

for (i = 0; i < 8; i++)

{

// Check if the MSB is set (if MSB is 1, then the POLY can "divide"

// into the "dividend")

if ((CRC_acc & 0x8000) == 0x8000)

{

// if so, shift the CRC value, and XOR "subtract" the poly

CRC_acc = CRC_acc << 1;</pre>

CRC_acc ^= POLY;

}

else

{

// if not, just shift the CRC value

CRC_acc = CRC_acc << 1;</pre>

}

}

return CRC_acc; // Return the final remainder (CRC value)

}

```

Table 29.1 lists example input values and the associated outputs using the 16-bit C8051F70x/71x CRC algorithm (an initial value of 0xFFFF is used):

| Input                        | Output |

|------------------------------|--------|

| 0x63                         | 0xBD35 |

| 0xAA, 0xBB, 0xCC             | 0x6CF6 |

| 0x00, 0x00, 0xAA, 0xBB, 0xCC | 0xB166 |

#### Table 29.1. Example 16-bit CRC Outputs

#### 30.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 30.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER indicates whether a device is the master or slave during the current transfer. TXMODE indicates whether the device is transmitting or receiving data for the current byte.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a 1 to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a 1 to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 30.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

#### 30.4.2.1. Software ACK Generation

When the EHACK bit in register SMB0ADM is cleared to 0, the firmware on the device must detect incoming slave addresses and ACK or NACK the slave address and incoming data bytes. As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received during the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

#### 30.4.2.2. Hardware ACK Generation

When the EHACK bit in register SMB0ADM is set to 1, automatic slave address recognition and ACK generation is enabled. More detail about automatic slave address recognition can be found in Section 30.4.3. As a receiver, the value currently specified by the ACK bit will be automatically sent on the bus during the ACK cycle of an incoming data byte. As a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. The ACKRQ bit is not used when hardware ACK generation is enabled. If a received slave address is NACKed by hardware, further slave events will be ignored until the next START is detected, and no interrupt will be generated.

Table 30.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 30.5 for SMBus status decoding using the SMB0CN register.

|                 | Valu             | es F  | Rea     | d   |                                                                                       |                                                 | Values to<br>Write |     |     | itus<br>bected                 |

|-----------------|------------------|-------|---------|-----|---------------------------------------------------------------------------------------|-------------------------------------------------|--------------------|-----|-----|--------------------------------|

| Mode            | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                                                   | Typical Response Options                        | STA                | STO | ACK | Next Status<br>Vector Expected |

|                 |                  | 0     | 0       | х   | A slave address + R/W was                                                             | If Write, Set ACK for first data byte.          | 0                  | 0   | 1   | 0000                           |

|                 |                  | Ū     | Ũ       |     | received; ACK sent.                                                                   | If Read, Load SMB0DAT with<br>data byte         | 0                  | 0   | Х   | 0100                           |

|                 | 0010             |       |         |     | Lost arbitration as master;<br>slave address + R/W received;<br>ACK sent.             | If Write, Set ACK for first data byte.          | 0                  | 0   | 1   | 0000                           |

| eiver           |                  | 0     | 1       | Х   |                                                                                       | If Read, Load SMB0DAT with data byte            | 0                  | 0   | Х   | 0100                           |

| ece             |                  |       |         |     |                                                                                       | Reschedule failed transfer                      | 1                  | 0   | Х   | 1110                           |

| Slave Receiver  | 0001             | 0     | 0       |     | A STOP was detected while<br>addressed as a Slave Trans-<br>nitter or Slave Receiver. | Clear STO.                                      | 0                  | 0   | Х   | —                              |

|                 |                  | 0     | 1       | х   | Lost arbitration while attempt-<br>ing a STOP.                                        | No action required (transfer complete/aborted). | 0                  | 0   | 0   | _                              |

|                 | 0000             | 0     | 0       | v   | A slave byte was received.                                                            | Set ACK for next data byte;<br>Read SMB0DAT.    | 0                  | 0   | 1   | 0000                           |

|                 | 0000             | 0     | 0       | ^   | A slave byle was received.                                                            | Set NACK for next data byte;<br>Read SMB0DAT.   | 0                  | 0   | 0   | 0000                           |

| on              | 0010             | 0     | 1       | х   | Lost arbitration while attempt-                                                       | Abort failed transfer.                          | 0                  | 0   | Х   | —                              |

| nditi           | 0010             |       | 1       | ~   | ing a repeated START.                                                                 | Reschedule failed transfer.                     | 1                  | 0   | Х   | 1110                           |

| Cor             | 0001             | 0     | 1       | х   | Lost arbitration due to a                                                             | Abort failed transfer.                          | 0                  | 0   | Х   | —                              |

| Error Condition | 0001             |       |         | ~   | detected STOP.                                                                        | Reschedule failed transfer.                     | 1                  | 0   | Х   | 1110                           |

| Ъ               | 0000             | 0     | 1       | х   | Lost arbitration while transmit-                                                      | Abort failed transfer.                          | 0                  | 0   | Х   | —                              |

| Bus             | 0000             |       |         | ~   | ting a data byte as master.                                                           | Reschedule failed transfer.                     | 1                  | 0   | Х   | 1110                           |

### 31.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

### 31.5. Serial Clock Phase and Polarity

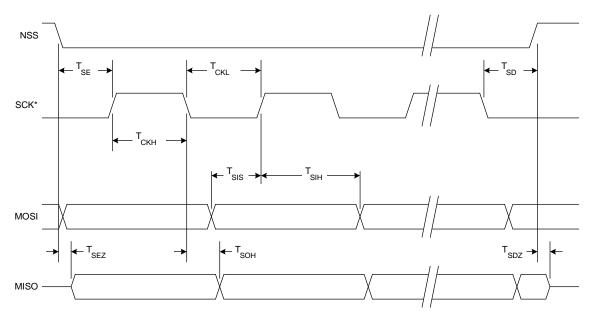

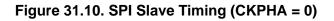

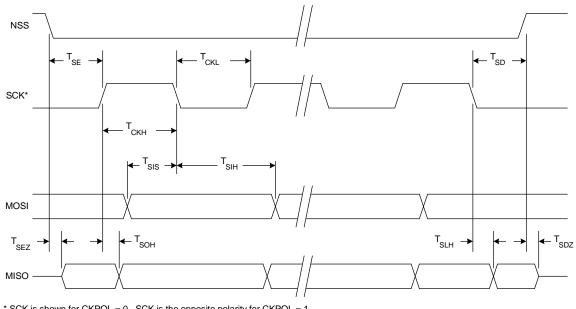

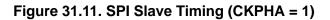

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 31.5. For slave mode, the clock and data relationships are shown in Figure 31.6 and Figure 31.7. CKPHA should be set to 0 on both the master and slave SPI when communicating between two Silicon Labs C8051 devices.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 31.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e., half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

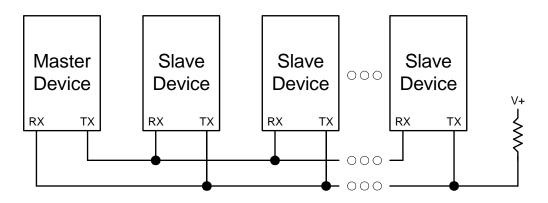

### 32.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 32.6. UART Multi-Processor Mode Interconnect Diagram

|                    |                                                                              | Frequency: 24.5 MHz    |                                |                       |                                                 |                  |                                  |  |  |  |

|--------------------|------------------------------------------------------------------------------|------------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|--|

|                    | Target<br>Baud Rate<br>(bps)                                                 | Baud<br>Rate%<br>Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |  |

|                    | 230400                                                                       | -0.32%                 | 106                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |  |  |  |

| . ء                | 115200                                                                       | -0.32%                 | 212                            | SYSCLK                | XX                                              | 1                | 0x96                             |  |  |  |

| from<br>Osc.       | 57600                                                                        | 0.15%                  | 426                            | SYSCLK                | XX                                              | 1                | 0x2B                             |  |  |  |

| × =                | 28800                                                                        | -0.32%                 | 848                            | SYSCLK/4              | 01                                              | 0                | 0x96                             |  |  |  |

| CLA                | 14400                                                                        | 0.15%                  | 1704                           | SYSCLK/12             | 00                                              | 0                | 0xB9                             |  |  |  |

| SYSCLK<br>Internal | 9600                                                                         | -0.32%                 | 2544                           | SYSCLK/12             | 00                                              | 0                | 0x96                             |  |  |  |

| s –                | 2400                                                                         | -0.32%                 | 10176                          | SYSCLK/48             | 10                                              | 0                | 0x96                             |  |  |  |

|                    | 1200                                                                         | 0.15%                  | 20448                          | SYSCLK/48             | 10                                              | 0                | 0x2B                             |  |  |  |

|                    | Notes:<br>1. SCA1–SCA0 and T1M bit definitions can be found in Section 33.1. |                        |                                |                       |                                                 |                  |                                  |  |  |  |

### Table 32.1. Timer Settings for Standard Baud Rates Using The Internal 24.5 MHz Oscillator

#### Table 32.2. Timer Settings for Standard Baud Rates Using an External 22.1184 MHz Oscillator

|                              |                              |                        | Frequ                          | uency: 22.1184        | MHz                                             |                  |                                  |

|------------------------------|------------------------------|------------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud<br>Rate%<br>Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | 0.00%                  | 96                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xD0                             |

| نه ع                         | 115200                       | 0.00%                  | 192                            | SYSCLK                | XX                                              | 1                | 0xA0                             |

| fron<br>Osc                  | 57600                        | 0.00%                  | 384                            | SYSCLK                | XX                                              | 1                | 0x40                             |

| al C                         | 28800                        | 0.00%                  | 768                            | SYSCLK / 12           | 00                                              | 0                | 0xE0                             |

| SYSCLK from<br>External Osc. | 14400                        | 0.00%                  | 1536                           | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

| YS<br>Xte                    | 9600                         | 0.00%                  | 2304                           | SYSCLK / 12           | 00                                              | 0                | 0xA0                             |

| ŚШ                           | 2400                         | 0.00%                  | 9216                           | SYSCLK / 48           | 10                                              | 0                | 0xA0                             |

|                              | 1200                         | 0.00%                  | 18432                          | SYSCLK / 48           | 10                                              | 0                | 0x40                             |

| ۶.                           | 230400                       | 0.00%                  | 96                             | EXTCLK / 8            | 11                                              | 0                | 0xFA                             |

| from<br>Osc.                 | 115200                       | 0.00%                  | 192                            | EXTCLK / 8            | 11                                              | 0                | 0xF4                             |

| Ϋ́                           | 57600                        | 0.00%                  | 384                            | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

| L<br>L<br>L<br>L             | 28800                        | 0.00%                  | 768                            | EXTCLK / 8            | 11                                              | 0                | 0xD0                             |

| SYSCLK<br>Internal           | 14400                        | 0.00%                  | 1536                           | EXTCLK / 8            | 11                                              | 0                | 0xA0                             |

| ω –                          | 9600                         | 0.00%                  | 2304                           | EXTCLK / 8            | 11                                              | 0                | 0x70                             |

| Notes:                       |                              |                        |                                |                       |                                                 |                  |                                  |

1. SCA1–SCA0 and T1M bit definitions can be found in Section 33.1.

2. X = Don't care.

## SFR Definition 33.1. CKCON: Clock Control

| Bit   | 7    | 6    | 5    | 4    | 3   | 2   | 1        | 0 |

|-------|------|------|------|------|-----|-----|----------|---|

| Name  | ТЗМН | T3ML | T2MH | T2ML | T1M | TOM | SCA[1:0] |   |

| Туре  | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W      |   |

| Reset | 0    | 0    | 0    | 0    | 0   | 0   | 0        | 0 |

#### SFR Address = 0x8E; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ТЗМН     | Timer 3 High Byte Clock Select.Selects the clock supplied to the Timer 3 high byte (split 8-bit timer mode only).0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN.1: Timer 3 high byte uses the system clock.                                                                                                                      |

| 6   | T3ML     | <ul> <li>Timer 3 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 3. Selects the clock supplied to the lower 8-bit timer in split 8-bit timer mode.</li> <li>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN.</li> <li>1: Timer 3 low byte uses the system clock.</li> </ul>                                    |

| 5   | T2MH     | Timer 2 High Byte Clock Select.Selects the clock supplied to the Timer 2 high byte (split 8-bit timer mode only).0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.1: Timer 2 high byte uses the system clock.                                                                                                                      |

| 4   | T2ML     | <ul> <li>Timer 2 Low Byte Clock Select.</li> <li>Selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer mode, this bit selects the clock supplied to the lower 8-bit timer.</li> <li>0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.</li> <li>1: Timer 2 low byte uses the system clock.</li> </ul> |

| 3   | T1       | <b>Timer 1 Clock Select.</b><br>Selects the clock source supplied to Timer 1. Ignored when C/T1 is set to 1.<br>0: Timer 1 uses the clock defined by the prescale bits SCA[1:0].<br>1: Timer 1 uses the system clock.                                                                                                                                     |

| 2   | ТО       | Timer 0 Clock Select.Selects the clock source supplied to Timer 0. Ignored when C/T0 is set to 1.0: Counter/Timer 0 uses the clock defined by the prescale bits SCA[1:0].1: Counter/Timer 0 uses the system clock.                                                                                                                                        |

| 1:0 | SCA[1:0] | Timer 0/1 Prescale Bits.These bits control the Timer 0/1 Clock Prescaler:00: System clock divided by 1201: System clock divided by 410: System clock divided by 4811: External clock divided by 8 (synchronized with the system clock)                                                                                                                    |

## SFR Definition 33.4. TL0: Timer 0 Low Byte

| Bit   | 7                                        | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------------------------------------|-------------------|---|---|---|---|---|---|--|

| Nam   | e                                        | TL0[7:0]          |   |   |   |   |   |   |  |

| Туре  | 9                                        | R/W               |   |   |   |   |   |   |  |

| Rese  | et 0                                     | 0                 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| SFR A | SFR Address = 0x8A; SFR Page = All Pages |                   |   |   |   |   |   |   |  |

| Bit   | Name                                     | Name Function     |   |   |   |   |   |   |  |

| 7:0   | TL0[7:0]                                 | Timer 0 Low Byte. |   |   |   |   |   |   |  |

| The TL0 register is the low byte of the 16-bit Timer 0. |

|---------------------------------------------------------|

|---------------------------------------------------------|

## SFR Definition 33.5. TL1: Timer 1 Low Byte

| Bit   | 7             | 6                                                       | 5           | 4 | 3 | 2 | 1 | 0 |  |

|-------|---------------|---------------------------------------------------------|-------------|---|---|---|---|---|--|

| Nam   | Name TL1[7:0] |                                                         |             |   |   |   |   |   |  |

| Туре  | Type R/W      |                                                         |             |   |   |   |   |   |  |

| Rese  | et O          | 0                                                       | 0           | 0 | 0 | 0 | 0 | 0 |  |

| SFR A | Address = 0x8 | B; SFR Page                                             | = All Pages | ; |   |   |   |   |  |

| Bit   | Name          | Name Function                                           |             |   |   |   |   |   |  |

| 7:0   | TL1[7:0]      | ] Timer 1 Low Byte.                                     |             |   |   |   |   |   |  |

|       |               | The TL1 register is the low byte of the 16-bit Timer 1. |             |   |   |   |   |   |  |