Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART      |

| Peripherals                | Cap Sense, POR, PWM, WDT                                       |

| Number of I/O              | 54                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | 32 x 8                                                         |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 64-TQFP                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f709-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

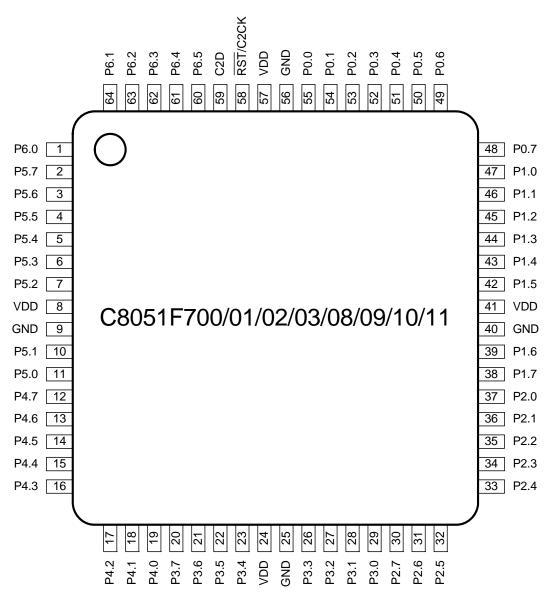

Figure 3.1. C8051F7xx-GQ TQFP64 Pinout Diagram (Top View)

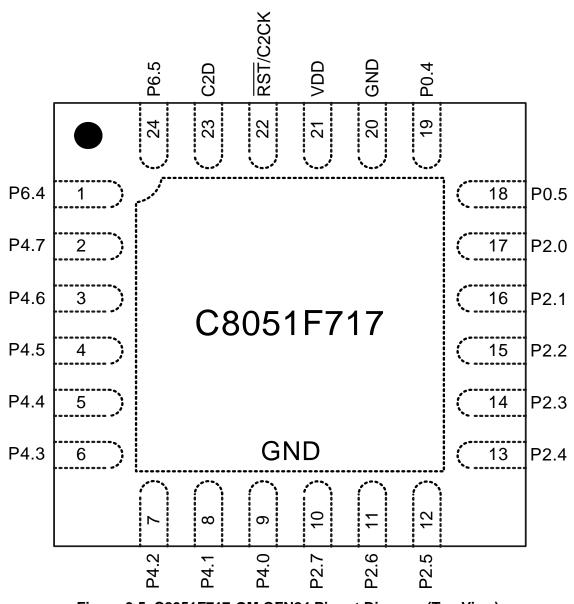

Figure 3.5. C8051F717-GM QFN24 Pinout Diagram (Top View)

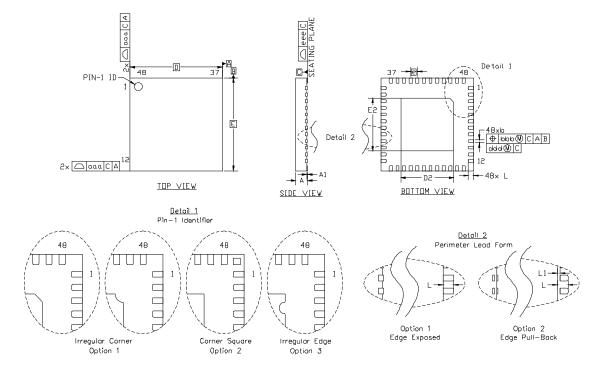

## 6. QFN-48 Package Specifications

Figure 6.1. QFN-48 Package Drawing

| Dimension | Min       | Nom  | Max  | Dimension | Min  | Nom  | Max  |

|-----------|-----------|------|------|-----------|------|------|------|

| A         | 0.80      | 0.90 | 1.00 | E2        | 3.90 | 4.00 | 4.10 |

| A1        | 0.00      | —    | 0.05 | L         | 0.30 | 0.40 | 0.50 |

| b         | 0.18      | 0.23 | 0.30 | L1        | 0.00 | —    | 0.10 |

| D         | 7.00 BSC. |      |      | aaa       | _    | —    | 0.10 |

| D2        | 3.90      | 4.00 | 4.10 | bbb       | _    | —    | 0.10 |

| е         | 0.50 BSC. |      |      | CCC       | _    | _    | 0.05 |

| E         | 7.00 BSC. |      |      | ddd       | _    | —    | 0.08 |

#### Table 6.1. QFN-48 Package Dimensions

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** 3. This drawing conforms to JEDEC outline MO-220, variation VKKD-4 except for features D2 and L which are toleranced per supplier designation.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## SFR Definition 10.9. ADC0MX: AMUX0 Channel Select

| Bit   | 7 | 6 | 5 | 4   | 3 | 2          | 1 | 0 |

|-------|---|---|---|-----|---|------------|---|---|

| Name  |   |   |   |     |   | AMX0P[4:0] |   |   |

| Туре  | R | R | R | R/W |   |            |   |   |

| Reset | 0 | 0 | 0 | 1   | 1 | 1          | 1 | 1 |

### SFR Address = 0xBB; SFR Page = 0

| Bit | Name       |                    | Fur            | nction            |                |

|-----|------------|--------------------|----------------|-------------------|----------------|

| 7:5 | Unused     | Read = 000b; Write | = Don't Care.  |                   |                |

| 4:0 | AMX0P[4:0] | AMUX0 Positive In  | put Selection. |                   |                |

|     |            |                    | 64-Pin Devices | 48-Pin Devices    | 32-Pin Devices |

|     |            | 00000              | P0.0           | P0.0              | —              |

|     |            | 00001              | P0.1           | P0.1              | _              |

|     |            | 00010              | P0.2           | P0.2              | _              |

|     |            | 00011              | P0.3           | P0.3              | P0.3           |

|     |            | 00100              | P0.4           | P0.4              | P0.4           |

|     |            | 00101              | P0.5           | P0.5              | P0.5           |

|     |            | 00110              | P0.6           | P0.6              | _              |

|     |            | 00111              | P0.7           | P0.7              | _              |

|     |            | 01000              | P1.0           | P1.0              | _              |

|     |            | 01001              | P1.1           | P1.1              | —              |

|     |            | 01010              | P1.2           | P1.2              | —              |

|     |            | 01011              | P1.3           | P1.3              | _              |

|     |            | 01100              | P1.4           | —                 | _              |

|     |            | 01101              | P1.5           | —                 | _              |

|     |            | 01110              | P1.6           | —                 | _              |

|     |            | 01111              | P1.7           | —                 | _              |

|     |            | 10000              | Temp Sensor    | Temp Sensor       | Temp Sensor    |

|     |            | 10001              | VREG Output    | VREG Output       | VREG Output    |

|     |            | 10010              | VDD            | VDD               | VDD            |

|     |            | 10011              | GND            | GND               | GND            |

|     |            | 10100–11111        |                | no input selected |                |

### 12.1. External Voltage References

To use an external voltage reference, REFSL[1:0] should be set to 00. Bypass capacitors should be added as recommended by the manufacturer of the external voltage reference.

#### 12.2. Internal Voltage Reference Options

A 1.6 V high-speed reference is included on-chip. The high speed internal reference is selected by setting REFSL[1:0] to 11. When selected, the high-speed internal reference will be automatically enabled on an as-needed basis by ADC0.

For applications with a non-varying power supply voltage, using the power supply as the voltage reference can provide ADC0 with added dynamic range at the cost of reduced power supply noise rejection. To use the 1.8 to 3.6 V power supply voltage ( $V_{DD}$ ) or the 1.8 V regulated digital supply voltage as the reference source, REFSL[1:0] should be set to 01 or 10, respectively.

#### 12.3. Analog Ground Reference

To prevent ground noise generated by switching digital logic from affecting sensitive analog measurements, a separate analog ground reference option is available. When enabled, the ground reference for ADC0 is taken from the P0.1/AGND pin. Any external sensors sampled by ADC0 should be referenced to the P0.1/AGND pin. The separate analog ground reference option is enabled by setting REFGND to 1. Note that when using this option, P0.1/AGND must be connected to the same potential as GND.

#### 12.4. Temperature Sensor Enable

The TEMPE bit in register REF0CN enables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

### **15.1. Configuring Port Pins as Capacitive Sense Inputs**

In order for a port pin to be measured by CS0, that port pin must be configured as an analog input (see "28. Port Input/Output"). Configuring the input multiplexer to a port pin not configured as an analog input will cause the capacitance-to-digital converter to output incorrect measurements.

- The port pin is accessible by the CS0 input multiplexer.

- The port pin is configured as an analog input.

- The port latch contains a 0.

#### 15.2. CS0 Gain Adjustment

The gain of the CS0 circuit can be adjusted in integer increments from 1x to 8x (8x is the default). High gain gives the best sensitivity and resolution for small capacitors, such as those typically implemented as touch-sensitive PCB features. To measure larger capacitance values, the gain can be lowered. However, lower gain values will affect the overall conversion time. SeeTable 15.1 for more details on the gain adjustment. The bits CS0CG[2:0] in register CS0MD1 set the gain value.

| CS0CG[2:0] (Gain) | Maximum Total Capacitance (pF) <sup>1</sup> | Conversion Time (μs) <sup>2</sup> |

|-------------------|---------------------------------------------|-----------------------------------|

| 000b (1x)         | 520                                         | 178                               |

| 001b (2x)         | 260                                         | 93                                |

| 010b (3x)         | 175                                         | 66                                |

| 011b (4x)         | 130                                         | 52                                |

| 100b (5x)         | 105                                         | 43                                |

| 101b (6x)         | 85                                          | 38                                |

| 110b (7x)         | 75                                          | 34                                |

| 111b (8x)         | 65                                          | 31                                |

Notes:

1. The maximum total capacitance values listed in this table are for guidance only, and are not a specification. The total measured capacitance will include internal capacitance as well as external parasitics, and the actual external capacitance being measured. Please refer to the Electrical Specifications for details on the maximum external capacitance.

2. Conversion times are nominal, and listed for 13-bit conversions with all other CS0 settings at their default values.

## 15.3. Capacitive Sense Start-Of-Conversion Sources

A capacitive sense conversion can be initiated in one of seven ways, depending on the programmed state of the CS0 start of conversion bits (CS0CF6:4). Conversions may be initiated by one of the following:

- 1. Writing a 1 to the CS0BUSY bit of register CS0CN

- 2. Timer 0 overflow

- 3. Timer 2 overflow

- 4. Timer 1 overflow

- 5. Timer 3 overflow

- 6. Convert continuously

- 7. Convert continuously with auto-scan enabled

**Note:** When CS0 begins a conversion to measure capacitance on a port pin, CS0 grounds all other port pins that meet the following requirements:

## SFR Definition 15.2. CS0CF: Capacitive Sense Configuration

| Bit   | 7 | 6   | 5          | 4   | 3 | 2   | 1          | 0   |

|-------|---|-----|------------|-----|---|-----|------------|-----|

| Name  |   |     | CS0CM[2:0] |     |   | (   | CS0ACU[2:0 | ]   |

| Туре  | R | R/W | R/W        | R/W | R | R/W | R/W        | R/W |

| Reset | 0 | 0   | 0          | 0   | 0 | 0   | 0          | 0   |

### SFR Address = 0x9E; SFR Page = 0

| Bit | Name        | Description                                                                            |  |  |  |  |

|-----|-------------|----------------------------------------------------------------------------------------|--|--|--|--|

| 7   | Unused      | Read = 0b; Write = Don't care                                                          |  |  |  |  |

| 6:4 | CS0CM[2:0]  | CS0 Start of Conversion Mode Select.                                                   |  |  |  |  |

|     |             | 000: Conversion initiated on every write of 1 to CS0BUSY.                              |  |  |  |  |

|     |             | 001: Conversion initiated on overflow of Timer 0.                                      |  |  |  |  |

|     |             | 010: Conversion initiated on overflow of Timer 2.                                      |  |  |  |  |

|     |             | 011: Conversion initiated on overflow of Timer 1.                                      |  |  |  |  |

|     |             | 100: Conversion initiated on overflow of Timer 3.                                      |  |  |  |  |

|     |             | 101: Reserved.                                                                         |  |  |  |  |

|     |             | 110: Conversion initiated continuously after writing 1 to CS0BUSY.                     |  |  |  |  |

|     |             | 111: Auto-scan enabled, conversions initiated continuously after writing 1 to CS0BUSY. |  |  |  |  |

| 3   | Unused      | Read = 0b; Write = Don't care                                                          |  |  |  |  |

| 2:0 | CS0ACU[2:0] | CS0 Accumulator Mode Select.                                                           |  |  |  |  |

|     |             | 000: Accumulate 1 sample.                                                              |  |  |  |  |

|     |             | 001: Accumulate 4 samples.                                                             |  |  |  |  |

|     |             | 010: Accumulate 8 samples.                                                             |  |  |  |  |

|     |             | 011: Accumulate 16 samples                                                             |  |  |  |  |

|     |             | 100: Accumulate 32 samples.                                                            |  |  |  |  |

|     |             | 101: Accumulate 64 samples.                                                            |  |  |  |  |

|     |             | 11x: Reserved.                                                                         |  |  |  |  |

## Table 20.2. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Page      | Description                       | Page |

|----------|---------|-----------|-----------------------------------|------|

| PCA0CPM0 | 0xDA    | F         | PCA Module 0 Mode Register        | 298  |

| PCA0CPM1 | 0xDB    | F         | PCA Module 1 Mode Register        | 298  |

| PCA0CPM2 | 0xDC    | F         | PCA Module 2 Mode Register        | 298  |

| PCA0H    | 0xFA    | 0         | PCA Counter High                  | 299  |

| PCA0L    | 0xF9    | 0         | PCA Counter Low                   | 299  |

| PCA0MD   | 0xED    | F         | PCA Mode                          | 296  |

| PCA0PWM  | 0xA1    | F         | PCA PWM Configuration             | 297  |

| PCON     | 0x87    | All Pages | Power Control                     | 162  |

| PSCTL    | 0x8F    | All Pages | Program Store R/W Control         | 153  |

| PSW      | 0xD0    | All Pages | Program Status Word               | 107  |

| REF0CN   | 0xD2    | F         | Voltage Reference Control         | 71   |

| REG0CN   | 0xB9    | F         | Voltage Regulator Control         | 73   |

| REVID    | 0xAD    | F         | Revision ID                       | 129  |

| RSTSRC   | 0xEF    | All Pages | Reset Source Configuration/Status | 168  |

| SBUF0    | 0x99    | All Pages | UART0 Data Buffer                 | 260  |

| SCON0    | 0x98    | All Pages | UART0 Control                     | 259  |

| SFRPAGE  | 0xA7    | All Pages | SFR Page                          | 132  |

| SMB0ADM  | 0xBB    | F         | SMBus Slave Address mask          | 230  |

| SMB0ADR  | 0xBA    | F         | SMBus Slave Address               | 229  |

| SMB0CF   | 0xC1    | 0         | SMBus Configuration               | 225  |

| SMB0CN   | 0xC0    | All Pages | SMBus Control                     | 227  |

| SMB0DAT  | 0xC2    | 0         | SMBus Data                        | 231  |

| SP       | 0x81    | All Pages | Stack Pointer                     | 105  |

| SPI0CFG  | 0xA1    | 0         | SPI0 Configuration                | 248  |

| SPIOCKR  | 0xA2    | F         | SPI0 Clock Rate Control           | 250  |

| SPIOCN   | 0xF8    | All Pages | SPI0 Control                      | 249  |

| SPIODAT  | 0xA3    | 0         | SPI0 Data                         | 250  |

| TCON     | 0x88    | All Pages | Timer/Counter Control             | 268  |

| TH0      | 0x8C    | All Pages | Timer/Counter 0 High              | 271  |

| TH1      | 0x8D    | All Pages | Timer/Counter 1 High              | 271  |

| TL0      | 0x8A    | All Pages | Timer/Counter 0 Low               | 270  |

| TL1      | 0x8B    | All Pages | Timer/Counter 1 Low               | 270  |

| TMOD     | 0x89    | All Pages | Timer/Counter Mode                | 269  |

| TMR2CN   | 0xC8    | All Pages | Timer/Counter 2 Control           | 275  |

| TMR2H    | 0xCD    | 0         | Timer/Counter 2 High              | 277  |

| TMR2L    | 0xCC    | 0         | Timer/Counter 2 Low               | 277  |

| TMR2RLH  | 0xCB    | 0         | Timer/Counter 2 Reload High       | 276  |

| TMR2RLL  | 0xCA    | 0         | Timer/Counter 2 Reload Low        | 276  |

## SFR Definition 21.4. EIE2: Extended Interrupt Enable 2

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |

|-------|---|---|---|---|---|---|--------|--------|

| Name  |   |   |   |   |   |   | ECSGRT | ECSCPT |

| Туре  | R | R | R | R | R | R | R/W    | R/W    |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0      |

#### SFR Address = 0xE7; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                  |  |  |  |  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:2 | Unused | ead = 000000b; Write = don't care.                                                                                                                                                                        |  |  |  |  |

| 1   | ECSGRT | Enable Capacitive Sense Greater Than Comparator Interrupt.<br>0: Disable Capacitive Sense Greater Than Comparator interrupt.<br>1: Enable interrupt requests generated by CS0CMPF.                        |  |  |  |  |

| 0   | ECSCPT | <ul> <li>Enable Capacitive Sense Conversion Complete Interrupt.</li> <li>0: Disable Capacitive Sense Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by CS0INT.</li> </ul> |  |  |  |  |

## 21.3. INTO and INT1 External Interrupts

The INTO and INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "33.1. Timer 0 and Timer 1" on page 264) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INT0 and INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 21.7). Note that INT0 and INT0 Port pin assignments are independent of any Crossbar assignments. INT0 and INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INT0 and/or INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see Section "28.3. Priority Crossbar Decoder" on page 185 for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT1 external interrupts, respectively. If an INT0 or INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

Rev. 1.0

## 25.2. Power-Fail Reset / V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 25.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid. The  $V_{DD}$  monitor is enabled after power-on resets. Its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  monitor is disabled by code and a software reset is performed, the  $V_{DD}$  monitor will still be disabled after the reset.

**Important Note:** If the  $V_{DD}$  monitor is being turned on from a disabled state, it should be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  monitor as a reset source before it is enabled and stabilized may cause a system reset. In some applications, this reset may be undesirable. If this is not desirable in the application, a delay should be introduced between enabling the monitor and selecting it as a reset source. The procedure for enabling the  $V_{DD}$  monitor and configuring it as a reset source from a disabled state is shown below:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDM0CN = 1).

- 2. If necessary, wait for the  $V_{DD}$  monitor to stabilize.

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 25.2 for V<sub>DD</sub> monitor timing; note that the power-on-reset delay is not incurred after a V<sub>DD</sub> monitor reset. See Section "9. Electrical Characteristics" on page 47 for complete electrical characteristics of the V<sub>DD</sub> monitor.

## SFR Definition 25.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF; SFR Page = All Pages

| Bit   | Name       | Description                                                                                    | Write                                                                                                                                                                | Read                                                                                                                                           |

|-------|------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                        | Don't care.                                                                                                                                                          | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                        | N/A                                                                                                                                                                  | Set to 1 if Flash<br>read/write/erase error<br>caused the last reset.                                                                          |

| 5     | CORSEF     | Comparator0 Reset Enable and Flag.                                                             | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                                 | Writing a 1 forces a sys-<br>tem reset.                                                                                                                              | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                                   |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                     | N/A                                                                                                                                                                  | Set to 1 if Watchdog Timer overflow caused the last reset.                                                                                     |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                     | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                       | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor as a reset source.<br>Writing 1 to this bit before the $V_{DD}$ monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                             | N/A                                                                                                                                                                  | Set to 1 if RST pin caused the last reset.                                                                                                     |

| Note: | Do not use | read-modify-write operations on this                                                           | s register                                                                                                                                                           | 1                                                                                                                                              |

| Analog Function                                       | Potentially Assignable<br>Port Pins | SFR(s) used for<br>Assignment   |

|-------------------------------------------------------|-------------------------------------|---------------------------------|

| ADC Input                                             | P0.0-P1.7                           | AMX0P, AMX0N,<br>PnSKIP, PnMDIN |

| Comparator0 Input                                     | P1.0-P1.7                           | CPT0MX, PnSKIP,<br>PnMDIN       |

| CS0 Input                                             | P2.0–P6.5                           | PnMDIN                          |

| Voltage Reference (VREF0)                             | P0.0                                | REF0CN, P0SKIP,<br>PnMDIN       |

| Ground Reference (AGND)                               | P0.1                                | REF0CN, P0SKIP                  |

| External Oscillator in Crystal Mode (XTAL1)           | P0.2                                | OSCXCN, POSKIP,<br>POMDIN       |

| External Oscillator in RC, C, or Crystal Mode (XTAL2) | P0.3                                | OSCXCN, POSKIP,<br>POMDIN       |

Table 28.1. Port I/O Assignment for Analog Functions

## 28.3. Priority Crossbar Decoder

The Priority Crossbar Decoder assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource (excluding UART0, which is always at pins 4 and 5). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. The potential crossbar pin assignments are shown in Figure 28.4. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin. Figure 28.5 shows an example crossbar configuration with no pins skipped. Figure 28.6 shows the same example with pins P0.2, P0.3 and P1.0 skipped.

If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to P0.0 if VREF is used, P0.1 if AGND is used, P0.3 and/or P0.2 if the external oscillator circuit is enabled, P0.6 if the ADC is configured to use the external conversion start signal (CNVSTR), and any selected ADC or Comparator inputs. It is also important to skip any pins that do not exist for the package being used.

Registers XBR0 and XBR1 are used to assign the digital I/O resources to the physical I/O Port pins. When the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when the UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.4; UART RX0 is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, pending the state of the NSS-MD1–NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

## SFR Definition 28.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7       | 6     | 5   | 4   | 3    | 2 | 1           | 0   |

|-------|---------|-------|-----|-----|------|---|-------------|-----|

| Name  | WEAKPUD | XBARE | T1E | T0E | ECIE |   | PCA0ME[1:0] |     |

| Туре  | R/W     | R/W   | R/W | R/W | R/W  | R | R/W         | R/W |

| Reset | 0       | 0     | 0   | 0   | 0    | 0 | 0           | 0   |

## SFR Address = 0xE2; SFR Page = F

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | WEAKPUD     | Port I/O Weak Pullup Disable.                                                 |

|     |             | 0: Weak Pullups enabled (except for Ports whose I/O are configured for analog |

|     |             | mode).                                                                        |

|     |             | 1: Weak Pullups disabled.                                                     |

| 6   | XBARE       | Crossbar Enable.                                                              |

|     |             | 0: Crossbar disabled.                                                         |

|     |             | 1: Crossbar enabled.                                                          |

| 5   | T1E         | T1 Enable.                                                                    |

|     |             | 0: T1 unavailable at Port pin.                                                |

|     |             | 1: T1 routed to Port pin.                                                     |

| 4   | T0E         | T0 Enable.                                                                    |

|     |             | 0: T0 unavailable at Port pin.                                                |

|     |             | 1: T0 routed to Port pin.                                                     |

| 3   | ECIE        | PCA0 External Counter Input Enable.                                           |

|     |             | 0: ECI unavailable at Port pin.                                               |

|     |             | 1: ECI routed to Port pin.                                                    |

| 2   | Unused      | Read = 0b; Write = Don't Care.                                                |

| 1:0 | PCA0ME[1:0] | PCA Module I/O Enable Bits.                                                   |

|     |             | 00: All PCA I/O unavailable at Port pins.                                     |

|     |             | 01: CEX0 routed to Port pin.                                                  |

|     |             | 10: CEX0, CEX1 routed to Port pins.                                           |

|     |             | 11: CEX0, CEX1, CEX2 routed to Port pins.                                     |

## 31.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

#### 31.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

#### 31.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

#### 31.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 31.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- 1. NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- 3. NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 31.2, Figure 31.3, and Figure 31.4 for typical connection diagrams of the various operational modes. **Note that the setting of NSSMD bits affects the pinout of the device.** When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "28. Port Input/Output" on page 180 for general purpose port I/O and crossbar information.

#### 31.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic

#### 31.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

#### 31.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 31.5. For slave mode, the clock and data relationships are shown in Figure 31.6 and Figure 31.7. CKPHA should be set to 0 on both the master and slave SPI when communicating between two Silicon Labs C8051 devices.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 31.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e., half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

## SFR Definition 31.3. SPI0CKR: SPI0 Clock Rate

| Bit           | t 7 6 5 4 3 2 1 |                                                                                                      |                                                                                                            |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------|----------------------------------|--|--|

| Name SCR[7:0] |                 |                                                                                                      |                                                                                                            |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |

| Type R/W      |                 |                                                                                                      |                                                                                                            |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |

| Reset         | 0               | 0                                                                                                    | 0                                                                                                          | 0                                                                                       | 0                                                              |                                               |                                                                  |                                  |  |  |

| SFR Ad        | ldress = 0xA2   | 2; SFR Page                                                                                          | e = F                                                                                                      |                                                                                         | I                                                              |                                               |                                                                  |                                  |  |  |

| Bit           | Name            | Function                                                                                             |                                                                                                            |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |

| 7:0           | SCR[7:0]        | configured<br>sion of the<br>the system<br>register.<br>f <sub>SCK</sub> =<br>for 0 <= S<br>Example: | s determine<br>d for master<br>e system clo<br>n clock frequ<br>$\frac{SY}{2 \times (SPI00)}$<br>PI0CKR <= | mode opera<br>ck, and is giv<br>Jency and S<br>SCLK<br>CKR[7:0] +<br>255<br>= 2 MHz and | tion. The S(<br>ven in the fo<br>PIOCKR is t<br>$\overline{1}$ | CK clock fre<br>Illowing equ<br>he 8-bit valu | en the SPI0 r<br>quency is a d<br>ation, where<br>le held in the | ivided ver-<br>S <i>YSCLK</i> is |  |  |

## SFR Definition 31.4. SPI0DAT: SPI0 Data

| Bit   | 7            | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |  |

|-------|--------------|---|---|----|---|---|---|---|--|--|--|

| Name  | SPI0DAT[7:0] |   |   |    |   |   |   |   |  |  |  |

| Туре  |              |   |   | R/ | W |   |   |   |  |  |  |

| Reset | 0            | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xA3; SFR Page = 0

| Bit | Name         | Function                                                                                                                                                                                                                                     |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |

## SFR Definition 33.4. TL0: Timer 0 Low Byte

| Bit   | 7             | 7 6 5 4 3 2 1 0 |                  |   |   |   |   |   |  |  |  |

|-------|---------------|-----------------|------------------|---|---|---|---|---|--|--|--|

| Nam   | e             | TL0[7:0]        |                  |   |   |   |   |   |  |  |  |

| Туре  | 9             | R/W             |                  |   |   |   |   |   |  |  |  |

| Rese  | et O          | 0               | 0                | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR A | Address = 0x8 | A; SFR Page     | = All Pages      |   |   |   |   |   |  |  |  |

| Bit   | Name          |                 |                  |   |   |   |   |   |  |  |  |

| 7:0   | TL0[7:0]      | Timer 0 Lov     | ïmer 0 Low Byte. |   |   |   |   |   |  |  |  |

| The TL0 register is the low byte of the 16-bit Timer 0. |

|---------------------------------------------------------|

|---------------------------------------------------------|

## SFR Definition 33.5. TL1: Timer 1 Low Byte

| Bit   | 7             | 6           | 6         5         4         3         2         1         0 |               |               |       |   |   |  |  |

|-------|---------------|-------------|---------------------------------------------------------------|---------------|---------------|-------|---|---|--|--|

| Nam   | е             | TL1[7:0]    |                                                               |               |               |       |   |   |  |  |

| Туре  | 9             | R/W         |                                                               |               |               |       |   |   |  |  |

| Rese  | et O          | 0           | 0                                                             | 0             | 0             | 0     | 0 | 0 |  |  |

| SFR A | Address = 0x8 | B; SFR Page | e = All Pages                                                 | 5             |               |       |   |   |  |  |

| Bit   | Name          |             |                                                               |               | Function      |       |   |   |  |  |

| 7:0   | TL1[7:0]      | Timer 1 Lo  | w Byte.                                                       |               |               |       |   |   |  |  |

|       |               | The TL1 reg | gister is the lo                                              | ow byte of th | ne 16-bit Tim | er 1. |   |   |  |  |

## DOCUMENT CHANGE LIST

### **Revision 0.5 to Revision 1.0**

- Updated "Electrical Characteristics" on page 47.

- Updated "Port Input/Output" on page 180.

### **Revision 0.4 to Revision 0.5**

- Removed Incorrect Pin Connections in Figure 1.4 on page 21 and Figure 1.6 on page 23.

- Updated Specifications in Section "9. Electrical Characteristics" on page 47.

- Updated Section "15. Capacitive Sense (CS0)" on page 80 for clarity.

- Corrected "CJNE A, direct, rel" instruction timing in Table 16.1.

- Noted that a minimum SYSCLK speed is required for Flash writes or erases in Section "22.1. Programming The Flash Memory" on page 148, and for EEPROM writes in Section "23.3. Interfacing with the EEPROM" on page 155.

- Corrected P0.3 overvoltage capabilities throughout document.

#### **Revision 0.3 to Revision 0.4**

- Updated Section "15. Capacitive Sense (CS0)" on page 80 to reflect Revision B enhancements.

- Added C8051F716 and C8051F717 devices, package information, and features.

- Updated Register 19.1, "HWID: Hardware Identification Byte," on page 128.

- Corrected minor typographical and formatting errors throughout document.

#### **Revision 0.2 to Revision 0.3**

- Corrected Dimension D in the QFN-48 Package Specifications.

- Updated Table 9.1 on page 47.

- Updated Register 10.1, "ADC0CF: ADC0 Configuration," on page 59.

- Updated Register 14.3, "CPT0MX: Comparator0 MUX Selection," on page 79.

- Updated Section "28.1.1. Port Pins Configured for Analog I/O" on page 181.

- Updated Register 35.2, "DEVICEID: C2 Device ID," on page 302.