Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | Cap Sense, POR, PWM, WDT                                        |

| Number of I/O              | 54                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | 32 x 8                                                          |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f709-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 30.4. Hardware Address Recognition Examples (EHACK = 1)        | 229 |

|----------------------------------------------------------------------|-----|

| Table 30.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) | 236 |

| Table 30.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1)  | 238 |

| Table 31.1. SPI Slave Timing Parameters                              | 253 |

| Table 32.1. Timer Settings for Standard Baud Rates                   |     |

| Using The Internal 24.5 MHz Oscillator                               | 261 |

| Table 32.2. Timer Settings for Standard Baud Rates                   |     |

| Using an External 22.1184 MHz Oscillator                             | 261 |

| Table 34.1. PCA Timebase Input Options                               | 285 |

| Table 34.2. PCA0CPM and PCA0PWM Bit Settings for PCA Modules         | 287 |

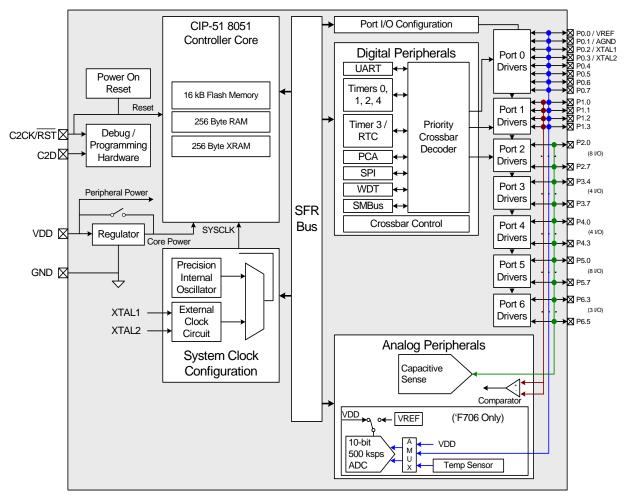

Figure 1.4. C8051F706/07 Block Diagram

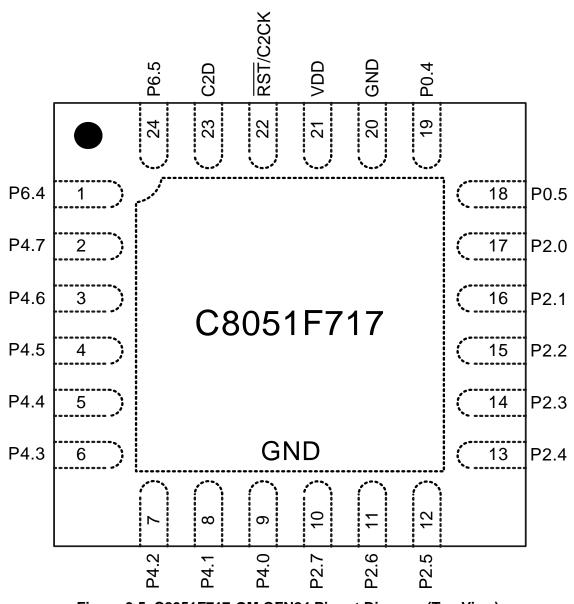

Figure 3.5. C8051F717-GM QFN24 Pinout Diagram (Top View)

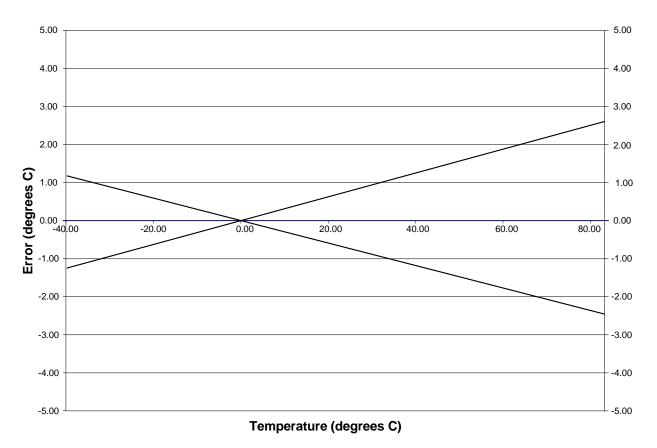

Parameters that affect ADC measurement, in particular the voltage reference value, will also affect temperature measurement.

Figure 11.2. Temperature Sensor Error with 1-Point Calibration at 0 Celsius

If CS0BUSY is used to initiate conversions, and then polled to determine if the conversion is finished, at least one clock cycle must be inserted between setting CS0BUSY to 1 and polling the CS0BUSY bit.

Conversions can be configured to be initiated continuously through one of two methods. CS0 can be configured to convert at a single channel continuously or it can be configured to convert continuously with auto-scan enabled. When configured to convert continuously, conversions will begin after the CS0BUSY bit in CS0CF has been set. An interrupt will be generated if CS0 conversion complete interrupts are enabled by setting the ECSCPT bit (EIE2.0).

The CS0 module uses a method of successive approximation to determine the value of an external capacitance. The number of bits the CS0 module converts is adjustable using the CS0CR bits in register CS0MD2. Conversions are 13 bits long by default, but they can be adjusted to 12, 13, 14, or 16 bits depending on the needs of the application. Unconverted bits will be set to 0. Shorter conversion lengths produce faster conversion rates, and vice-versa. Applications can take advantage of faster conversion rates when the unconverted bits fall below the noise floor.

**Note:** CS0 conversion complete interrupt behavior depends on the settings of the CS0 accumulator. If CS0 is configured to accumulate multiple conversions on an input channel, a CS0 conversion complete interrupt will be generated only after the last conversion completes.

# SFR Definition 20.1. SFRPAGE: SFR Page

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|--------------|---|---|---|---|---|---|--|--|--|

| Name  |   | SFRPAGE[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W          |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0xA7; SFR Page = All Pages

| Bit | Name         | Description                                                                      |

|-----|--------------|----------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page Bits.                                                                   |

|     |              | Represents the SFR Page the C8051 core uses when reading or modifying SFRs.      |

|     |              | Write: Sets the SFR Page.<br>Read: Byte is the SFR page the C8051 core is using. |

### Table 20.2. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Page      | Description                       | Page |

|----------|---------|-----------|-----------------------------------|------|

| ACC      | 0xE0    | All Pages | Accumulator                       | 105  |

| ADC0CF   | 0xBC    | F         | ADC0 Configuration                | 59   |

| ADC0CN   | 0xE8    | All Pages | ADC0 Control                      | 61   |

| ADC0GTH  | 0xC4    | 0         | ADC0 Greater-Than Compare High    | 62   |

| ADC0GTL  | 0xC3    | 0         | ADC0 Greater-Than Compare Low     | 62   |

| ADC0H    | 0xBE    | 0         | ADC0 High                         | 60   |

| ADC0L    | 0xBD    | 0         | ADC0 Low                          | 60   |

| ADC0LTH  | 0xC6    | 0         | ADC0 Less-Than Compare Word High  | 63   |

| ADC0LTL  | 0xC5    | 0         | ADC0 Less-Than Compare Word Low   | 63   |

| ADC0MX   | 0xBB    | 0         | AMUX0 Multiplexer Channel Select  | 66   |

| В        | 0xF0    | All Pages | B Register                        | 106  |

| CKCON    | 0x8E    | All Pages | Clock Control                     | 263  |

| CLKSEL   | 0xBD    | F         | Clock Select                      | 263  |

| CPT0CN   | 0x9B    | 0         | Comparator0 Control               | 76   |

| CPT0MD   | 0x9D    | 0         | Comparator0 Mode Selection        | 77   |

| CPT0MX   | 0x9F    | 0         | Comparator0 MUX Selection         | 79   |

| CRC0AUTO | 0x96    | F         | CRC0 Automatic Control Register   | 217  |

| CRC0CN   | 0x91    | F         | CRC0 Control                      | 215  |

| CRC0CNT  | 0x97    | F         | CRC0 Automatic Flash Sector Count | 217  |

| CRC0DATA | 0xD9    | F         | CRC0 Data Output                  | 216  |

| CRC0FLIP | 0x95    | F         | CRC0 Bit Flip                     | 218  |

| CRCOIN   | 0x94    | F         | CRC Data Input                    | 216  |

### Table 20.2. Special Function Registers (Continued)

| Register | Address | Page      | Description                      | Page |

|----------|---------|-----------|----------------------------------|------|

| POMDIN   | 0xF1    | F         | Port 0 Input Mode Configuration  | 195  |

| POMDOUT  | 0xA4    | F         | Port 0 Output Mode Configuration | 196  |

| P0SKIP   | 0xD4    | F         | Port 0 Skip                      | 196  |

| P1       | 0x90    | All Pages | Port 1 Latch                     | 197  |

| P1DRV    | 0xFA    | F         | Port 1 Drive Strength            | 199  |

| P1MASK   | 0xE2    | 0         | P0 Mask                          | 193  |

| P1MAT    | 0xE1    | 0         | P1 Match                         | 194  |

| P1MDIN   | 0xF2    | F         | Port 1 Input Mode Configuration  | 198  |

| P1MDOUT  | 0xA5    | F         | Port 1 Output Mode Configuration | 198  |

| P1SKIP   | 0xD5    | F         | Port 1 Skip                      | 199  |

| P2       | 0xA0    | All Pages | Port 2 Latch                     | 200  |

| P2DRV    | 0xFB    | F         | Port 2 Drive Strength            | 202  |

| P2MDIN   | 0xF3    | F         | Port 2 Input Mode Configuration  | 200  |

| P2MDOUT  | 0xA6    | F         | Port 2 Output Mode Configuration | 201  |

| P2SKIP   | 0xD6    | F         | Port 2 Skip                      | 201  |

| P3       | 0xB0    | All Pages | Port 3 Latch                     | 202  |

| P3DRV    | 0xFC    | F         | Port 3 Drive Strength            | 204  |

| P3MDIN   | 0xF4    | F         | Port 3 Input Mode Configuration  | 203  |

| P3MDOUT  | 0xAF    | F         | Port 3 Output Mode Configuration | 203  |

| P4       | 0xAC    | All Pages | Port 4 Latch                     | 204  |

| P4DRV    | 0xFD    | F         | Port 4 Drive Strength            | 206  |

| P4MDIN   | 0xF5    | F         | Port 4 Input Mode Configuration  | 205  |

| P4MDOUT  | 0x9A    | F         | Port 4 Output Mode Configuration | 205  |

| P5       | 0xB3    | All Pages | Port 5 Latch                     | 206  |

| P5DRV    | 0xFE    | F         | Port 5 Drive Strength            | 208  |

| P5MDIN   | 0xF6    | F         | Port 5 Input Mode Configuration  | 207  |

| P5MDOUT  | 0x9B    | F         | Port 5 Output Mode Configuration | 207  |

| P6       | 0xB2    | All Pages | Port 6 Latch                     | 208  |

| P6DRV    | 0xC1    | F         | Port 6 Drive Strength            | 210  |

| P6MDIN   | 0xF7    | F         | Port 6 Input Mode Configuration  | 209  |

| P6MDOUT  | 0x9C    | F         | Port 6 Output Mode Configuration | 209  |

| PCA0CN   | 0xD8    | All Pages | PCA Control                      | 295  |

| PCA0CPH0 | 0xFC    | 0         | PCA Capture 0 High               | 300  |

| PCA0CPH1 | 0xEA    | 0         | PCA Capture 1 High               | 300  |

| PCA0CPH2 | 0xEC    | 0         | PCA Capture 2 High               | 300  |

| PCA0CPL0 | 0xFB    | 0         | PCA Capture 0 Low                | 300  |

| PCA0CPL1 | 0xE9    | 0         | PCA Capture 1 Low                | 300  |

| PCA0CPL2 | 0xEB    | 0         | PCA Capture 2 Low                | 300  |

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Interrupt Source               | Interrupt<br>Vector | Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|--------------------------------|---------------------|-------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                          | 0x0000              | Тор   | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(INT0) | 0x0003              | 0     | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow               | 0x000B              | 1     | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(INT1) | 0x0013              | 2     | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow               | 0x001B              | 3     | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                          | 0x0023              | 4     | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow               | 0x002B              | 5     | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                           | 0x0033              | 6     | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                |                | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                           | 0x003B              | 7     | SI (SMB0CN.0)                                                              | Y                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| Port Match                     | 0x0043              | 8     | None                                                                       | N/A              | N/A            | EMAT<br>(EIE1.1)   | PMAT<br>(EIP1.1)    |

| ADC0<br>Window Compare         | 0x004B              | 9     | ADOWINT (ADC0CN.3)                                                         | Y                | N              | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| ADC0 Conversion<br>Complete    | 0x0053              | 10    | AD0INT (ADC0CN.5)                                                          | Y                | N              | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)   |

| Programmable<br>Counter Array  | 0x005B              | 11    | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                           | Y                | N              | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)   |

| Comparator0                    | 0x0063              | 12    | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N                | N              | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)    |

| RESERVED                       |                     |       |                                                                            |                  |                |                    |                     |

| Timer 3 Overflow               | 0x0073              | 14    | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N                | N              | ET3<br>(EIE1.7)    | PT3<br>(EIP1.7)     |

| CS0 Conversion<br>Complete     | 0x007B              | 15    | CS0INT (CS0CN.5)                                                           | N                | N              | ECSCPT<br>(EIE2.0) | PSCCPT<br>(EIP2.0)  |

| CS0 Greater Than<br>Compare    | 0x0083              | 16    | CS0CMPF (CS0CN.0)                                                          | N                | N              | ECSGRT<br>(EIE2.1) | PSCGRT<br>(EIP2.1)  |

## Table 21.1. Interrupt Summary

# SFR Definition 28.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7       | 6     | 5   | 4   | 3    | 2 | 1           | 0   |

|-------|---------|-------|-----|-----|------|---|-------------|-----|

| Name  | WEAKPUD | XBARE | T1E | T0E | ECIE |   | PCA0ME[1:0] |     |

| Туре  | R/W     | R/W   | R/W | R/W | R/W  | R | R/W         | R/W |

| Reset | 0       | 0     | 0   | 0   | 0    | 0 | 0           | 0   |

## SFR Address = 0xE2; SFR Page = F

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | WEAKPUD     | Port I/O Weak Pullup Disable.                                                 |

|     |             | 0: Weak Pullups enabled (except for Ports whose I/O are configured for analog |

|     |             | mode).                                                                        |

|     |             | 1: Weak Pullups disabled.                                                     |

| 6   | XBARE       | Crossbar Enable.                                                              |

|     |             | 0: Crossbar disabled.                                                         |

|     |             | 1: Crossbar enabled.                                                          |

| 5   | T1E         | T1 Enable.                                                                    |

|     |             | 0: T1 unavailable at Port pin.                                                |

|     |             | 1: T1 routed to Port pin.                                                     |

| 4   | T0E         | T0 Enable.                                                                    |

|     |             | 0: T0 unavailable at Port pin.                                                |

|     |             | 1: T0 routed to Port pin.                                                     |

| 3   | ECIE        | PCA0 External Counter Input Enable.                                           |

|     |             | 0: ECI unavailable at Port pin.                                               |

|     |             | 1: ECI routed to Port pin.                                                    |

| 2   | Unused      | Read = 0b; Write = Don't Care.                                                |

| 1:0 | PCA0ME[1:0] | PCA Module I/O Enable Bits.                                                   |

|     |             | 00: All PCA I/O unavailable at Port pins.                                     |

|     |             | 01: CEX0 routed to Port pin.                                                  |

|     |             | 10: CEX0, CEX1 routed to Port pins.                                           |

|     |             | 11: CEX0, CEX1, CEX2 routed to Port pins.                                     |

## SFR Definition 28.29. P4DRV: Port 4 Drive Strength

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|-----|---|---|---|---|---|---|--|--|

| Name  | P4DRV[7:0] |     |   |   |   |   |   |   |  |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |  |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xFD; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P4DRV[7:0] | Drive Strength Configuration Bits for P4.7–P4.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P4.n Output has low output drive strength.<br>1: Corresponding P4.n Output has high output drive strength. |

### SFR Definition 28.30. P5: Port 5

| Bit   | 7       | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---------|-----|---|---|---|---|---|---|--|--|

| Name  | P5[7:0] |     |   |   |   |   |   |   |  |  |

| Туре  |         | R/W |   |   |   |   |   |   |  |  |

| Reset | 1       | 1   | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

SFR Address = 0xB3; SFR Page = All Pages

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P5[7:0] | <b>Port 5 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P5.n Port pin is logic<br>LOW.<br>1: P5.n Port pin is logic<br>HIGH. |

## SFR Definition 28.33. P5DRV: Port 5 Drive Strength

| Bit   | 7 6 5 4 3 2 1 0 |  |  |    |   |  |  |  |

|-------|-----------------|--|--|----|---|--|--|--|

| Name  | P5DRV[7:0]      |  |  |    |   |  |  |  |

| Туре  |                 |  |  | R/ | W |  |  |  |

| Reset | 0 0 0 0 0 0 0 0 |  |  |    |   |  |  |  |

SFR Address = 0xFE; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P5DRV[7:0] | Drive Strength Configuration Bits for P5.7–P5.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P5.n Output has low output drive strength.<br>1: Corresponding P5.n Output has high output drive strength. |

### SFR Definition 28.34. P6: Port 6

| Bit   | 7 | 6 | 5       | 4         | 3  | 2 | 1 | 0 |  |  |

|-------|---|---|---------|-----------|----|---|---|---|--|--|

| Name  |   |   | P6[5:0] |           |    |   |   |   |  |  |

| Туре  | R | R |         |           | R/ | W |   |   |  |  |

| Reset | 0 | 0 | 1       | 1 1 1 1 1 |    |   |   |   |  |  |

SFR Address = 0xB2; SFR Page = All Pages

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:6 | Unused  | Read = 00b; Write = Don't Ca                                                                                                                  | re                                                                            |                                                                         |

| 5:0 | P6[5:0] | <b>Port 6 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P6.n Port pin is logic<br>LOW.<br>1: P6.n Port pin is logic<br>HIGH. |

# SFR Definition 30.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1          | 0 |

|-------|-------|-----|------|---------|--------|--------|------------|---|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBCS[1:0] |   |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/W        |   |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0          | 0 |

### SFR Address = 0xC1; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB      | SMBus Enable.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                                             |

| 6   | INH        | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                    |

| 5   | BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                |

| 4   | EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | This bit controls the SDA setup and hold times according to Table 30.2.                                                                                                                                                                                                                                                                                                                                                               |

|     |            | 0: SDA Extended Setup and Hold Times disabled.                                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | 1: SDA Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces<br>Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |

| 2   | SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                              |

| 1:0 | SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | These two bits select the SMBus clock source, which is used to generate the SMBus bit rate. The selected device should be configured according to Equation 30.1.                                                                                                                                                                                                                                                                      |

|     |            | 00: Timer 0 Overflow                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | 01: Timer 1 Overflow                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | 10: Timer 2 High Byte Overflow                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | 11: Timer 2 Low Byte Overflow                                                                                                                                                                                                                                                                                                                                                                                                         |

# SFR Definition 30.4. SMB0ADM: SMBus Slave Address Mask

| Bit   | 7 6 5 4 3 2 1 |  |  |  |  |  |  |  |  |

|-------|---------------|--|--|--|--|--|--|--|--|

| Name  | SLVM[6:0]     |  |  |  |  |  |  |  |  |

| Туре  | R/W           |  |  |  |  |  |  |  |  |

| Reset | 1 1 1 1 1 1   |  |  |  |  |  |  |  |  |

#### SFR Address = 0xBB; SFR Page = F

| Bit | Name      | Function                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM[6:0] | SMBus Slave Address Mask.                                                                                                                                                                                                                                                          |

|     |           | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM[6:0] enables comparisons with the corresponding bit in SLV[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                       |

|     |           | <ul><li>Enables hardware acknowledgement of slave address and received data bytes.</li><li>0: Firmware must manually acknowledge all incoming address and data bytes.</li><li>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.</li></ul>                |

Table 30.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (Continued)

|                 | Valu             | es I  | Rea     | d   |                                  |                             |     | lues<br>Vrit |     | Status<br>Expected     |

|-----------------|------------------|-------|---------|-----|----------------------------------|-----------------------------|-----|--------------|-----|------------------------|

| Mode            | Status<br>Vector | ACKRQ | ARBLOST | ACK | Current SMbus State              | Typical Response Options    | STA | STO          | ACK | Next Sta<br>Vector Exp |

| uo              | 0010             | 0     | 1       | х   | Lost arbitration while attempt-  | Abort failed transfer.      | 0   | 0            | Х   | —                      |

| diti            | 0010             | 0     | 1       |     | ing a repeated START.            | Reschedule failed transfer. | 1   | 0            | Х   | 1110                   |

| Con             | 0001             | 0     | 1       | x   | Lost arbitration due to a        | Abort failed transfer.      | 0   | 0            | Х   | —                      |

| Error Condition | 0001             | 0     | 1       | ^   | detected STOP.                   | Reschedule failed transfer. | 1   | 0            | Х   | 1110                   |

|                 | 0000             | 1     | 1       | x   | Lost arbitration while transmit- | Abort failed transfer.      | 0   | 0            | 0   | —                      |

| Bus             | 0000             |       |         | ^   | ting a data byte as master.      | Reschedule failed transfer. | 1   | 0            | 0   | 1110                   |

### Table 30.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1)

|                    | v               | Values Read |       |         |     | Values to<br>Write                                 |                                                                                                                        |     | Status<br>Expected |     |                              |

|--------------------|-----------------|-------------|-------|---------|-----|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------------------------------|

| Mode               | Status          | Vector      | ACKRQ | ARBLOST | АСК | Current SMbus State                                | Typical Response Options                                                                                               | STA | STO                | ACK | Next Status<br>Vector Expect |

|                    | 11 <sup>.</sup> | 10          | 0     | 0       | х   | A master START was gener-<br>ated.                 | Load slave address + R/W into SMB0DAT.                                                                                 | 0   | 0                  | Х   | 1100                         |

|                    |                 |             | _     | _       | _   | A master data or address byte                      | Set STA to restart transfer.                                                                                           | 1   | 0                  | Х   | 1110                         |

| r                  |                 |             | 0     | 0       | 0   | was transmitted; NACK received.                    | Abort transfer.                                                                                                        | 0   | 1                  | Х   | —                            |

| smitte             |                 |             |       |         |     |                                                    | Load next data byte into<br>SMB0DAT.                                                                                   | 0   | 0                  | Х   | 1100                         |

| Tan                |                 |             |       |         |     |                                                    | End transfer with STOP.                                                                                                | 0   | 1                  | Х   | —                            |

| Master Transmitter | 11(             | 00          | 0     | 0       | 1   | A master data or address byte was transmitted; ACK | End transfer with STOP and start another transfer.                                                                     | 1   | 1                  | Х   | —                            |

| Ë                  |                 |             | •     | Ū       |     | received.                                          | Send repeated START.                                                                                                   | 1   | 0                  | Х   | 1110                         |

|                    |                 |             |       |         |     |                                                    | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT). Set ACK for initial<br>data byte. | 0   | 0                  | 1   | 1000                         |

### 32.1. Enhanced Baud Rate Generation

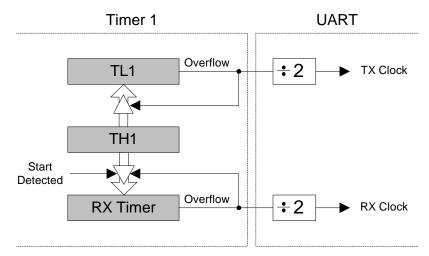

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 32.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 32.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "33.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 265). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK/4, SYSCLK/12, SYSCLK/48, the external oscillator clock/8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 32.1-A and Equation 32.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

### Equation 32.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "33. Timers" on page 262. A quick reference for typical baud rates and system clock frequencies is given in Table 32.1 through Table 32.2. The internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

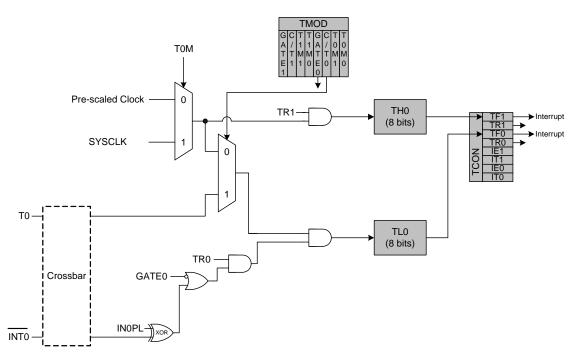

### 33.1. Timer 0 and Timer 1

Each timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (Section "21.2. Interrupt Register Descriptions" on page 140); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section "21.2. Interrupt Register (Section "21.2. Interrupt Register (Section "21.2. Interrupt Register Descriptions" on page 140); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section "21.2. Interrupt Register Descriptions" on page 140). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 33.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 in TCON is set and an interrupt will occur if Timer 0 interrupts are enabled.

The C/T0 bit in the TMOD register selects the counter/timer's clock source. When C/T0 is set to logic 1, high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register (Refer to Section "28.3. Priority Crossbar Decoder" on page 185 for information on selecting and configuring external I/O pins). Clearing C/T selects the clock defined by the T0M bit in register CKCON. When T0M is set, Timer 0 is clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON (see SFR Definition 33.1).

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 in the TMOD register is logic 0 or the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see SFR Definition 21.7). Setting GATE0 to 1 allows the timer to be controlled by the external input signal INT0 (see Section "21.2. Interrupt Register Descriptions" on page 140), facilitating pulse width measurements

| TR0                  | GATE0 | INT0 | Counter/Timer |  |  |  |  |  |  |

|----------------------|-------|------|---------------|--|--|--|--|--|--|

| 0                    | Х     | Х    | Disabled      |  |  |  |  |  |  |

| 1                    | 0     | Х    | Enabled       |  |  |  |  |  |  |

| 1                    | 1     | 0    | Disabled      |  |  |  |  |  |  |

| 1                    | 1     | 1    | Enabled       |  |  |  |  |  |  |

| Note: X = Don't Care |       |      |               |  |  |  |  |  |  |

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal INT1 is used with Timer 1; the INT1 polarity is defined by bit IN1PL in register IT01CF (see SFR Definition 21.7).

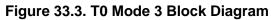

### 33.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 33.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |  |  |

|------|--------|--------------------|--|--|

| 0    | 0      | SYSCLK / 12        |  |  |

| 0    | 1      | External Clock / 8 |  |  |

| 1    | Х      | SYSCLK             |  |  |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 33.5. Timer 2 8-Bit Mode Block Diagram

## SFR Definition 33.14. TMR3RLL: Timer 3 Reload Register Low Byte

| Bit   | 7                                | 6           | 5                                 | 4     | 3        | 2 | 1 | 0 |

|-------|----------------------------------|-------------|-----------------------------------|-------|----------|---|---|---|

| Nam   | e                                |             |                                   | TMR3F | RLL[7:0] |   |   |   |

| Туре  | e R/W                            |             |                                   |       |          |   |   |   |

| Rese  | et O                             | 0           | 0                                 | 0     | 0        | 0 | 0 | 0 |

| SFR A | SFR Address = 0x92; SFR Page = 0 |             |                                   |       |          |   |   |   |

| Bit   | Name                             |             | Function                          |       |          |   |   |   |

| 7:0   | TMR3RLL[7:0                      | ] Timer 3 I | Timer 3 Reload Register Low Byte. |       |          |   |   |   |

|       |                                  |             |                                   |       |          |   |   |   |

# TMR3RLL holds the low byte of the reload value for Timer 3.

## SFR Definition 33.15. TMR3RLH: Timer 3 Reload Register High Byte

| Bit                              | 7    | 6            | 5        | 4 | 3 | 2 | 1 | 0 |

|----------------------------------|------|--------------|----------|---|---|---|---|---|

| Nam                              | e    | TMR3RLH[7:0] |          |   |   |   |   |   |

| Туре                             | )    | R/W          |          |   |   |   |   |   |

| Rese                             | et 0 | 0            | 0        | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0x93; SFR Page = 0 |      |              |          |   |   |   |   |   |

| Bit                              | Name |              | Function |   |   |   |   |   |

|                                  |      |              |          |   |   |   |   |   |

|     | . taile      |                                                              |

|-----|--------------|--------------------------------------------------------------|

| 7:0 | TMR3RLH[7:0] | Timer 3 Reload Register High Byte.                           |

|     |              | TMR3RLH holds the high byte of the reload value for Timer 3. |

# SFR Definition 34.3. PCA0PWM: PCA PWM Configuration

| Bit   | 7     | 6    | 5    | 4 | 3 | 2 | 1    | 0      |

|-------|-------|------|------|---|---|---|------|--------|

| Name  | ARSEL | ECOV | COVF |   |   |   | CLSE | L[1:0] |

| Туре  | R/W   | R/W  | R/W  | R | R | R | R/W  |        |

| Reset | 0     | 0    | 0    | 0 | 0 | 0 | 0    | 0      |

### SFR Address = 0xA1; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   | ARSEL      | Auto-Reload Register Select.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|     |            | This bit selects whether to read and write the normal PCA capture/compare registers (PCA0CPn), or the Auto-Reload registers at the same SFR addresses. This function is used to define the reload value for 9, 10, and 11-bit PWM modes. In all other modes, the Auto-Reload registers have no function.<br>0: Read/Write Capture/Compare Registers at PCA0CPHn and PCA0CPLn.<br>1: Read/Write Auto-Reload Registers at PCA0CPHn and PCA0CPLn. |  |  |  |  |  |

| 6   | ECOV       | Cycle Overflow Interrupt Enable.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|     |            | This bit sets the masking of the Cycle Overflow Flag (COVF) interrupt.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|     |            | 0: COVF will not generate PCA interrupts.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|     |            | 1: A PCA interrupt will be generated when COVF is set.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 5   | COVF       | Cycle Overflow Flag.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|     |            | This bit indicates an overflow of the 8th, 9th, 10th, or 11th bit of the main PCA counter (PCA0). The specific bit used for this flag depends on the setting of the Cycle Length Select bits. The bit can be set by hardware or software, but must be cleared by software.                                                                                                                                                                     |  |  |  |  |  |

|     |            | 0: No overflow has occurred since the last time this bit was cleared.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|     |            | 1: An overflow has occurred since the last time this bit was cleared.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 4:2 | Unused     | Read = 000b; Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 1:0 | CLSEL[1:0] |                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|     |            | <ul> <li>When 16-bit PWM mode is not selected, these bits select the length of the PWM cycle, between 8, 9, 10, or 11 bits. This affects all channels configured for PWM which are not using 16-bit PWM mode. These bits are ignored for individual channels configured to16-bit PWM mode.</li> <li>00: 8 bits.</li> <li>01: 9 bits.</li> <li>10: 10 bits.</li> <li>11: 11 bits.</li> </ul>                                                    |  |  |  |  |  |