Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | EBI/EMI, SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART       |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 54                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 16x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 64-TQFP                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f710-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1. System Overview                                     | 17 |

|--------------------------------------------------------|----|

| 2. Ordering Information                                | 26 |

| 3. Pin Definitions                                     |    |

| 4. TQFP-64 Package Specifications                      | 37 |

| 5. TQFP-48 Package Specifications                      | 39 |

| 6. QFN-48 Package Specifications                       | 41 |

| 7. QFN-32 Package Specifications                       | 43 |

| 8. QFN-24 Package Specifications                       | 45 |

| 9. Electrical Characteristics                          | 47 |

| 9.1. Absolute Maximum Specifications                   | 47 |

| 9.2. Electrical Characteristics                        | 48 |

| 10. 10-Bit ADC (ADC0)                                  | 55 |

| 10.1. Output Code Formatting                           | 56 |

| 10.2. 8-Bit Mode                                       |    |

| 10.3. Modes of Operation                               |    |

| 10.3.1. Starting a Conversion                          | 56 |

| 10.3.2. Tracking Modes                                 | 57 |

| 10.3.3. Settling Time Requirements                     | 58 |

| 10.4. Programmable Window Detector                     | 62 |

| 10.4.1. Window Detector Example                        | 64 |

| 10.5. ADC0 Analog Multiplexer                          | 65 |

| 11. Temperature Sensor                                 | 67 |

| 11.1. Calibration                                      | 67 |

| 12. Voltage and Ground Reference Options               |    |

| 12.1. External Voltage References                      |    |

| 12.2. Internal Voltage Reference Options               |    |

| 12.3. Analog Ground Reference                          |    |

| 12.4. Temperature Sensor Enable                        |    |

| 13. Voltage Regulator (REG0)                           |    |

| 14. Comparator0                                        |    |

| 14.1. Comparator Multiplexer                           |    |

| 15. Capacitive Sense (CS0)                             |    |

| 15.1. Configuring Port Pins as Capacitive Sense Inputs |    |

| 15.2. CS0 Gain Adjustment                              | 81 |

| 15.3. Capacitive Sense Start-Of-Conversion Sources     |    |

| 15.4. Automatic Scanning                               |    |

| 15.5. CS0 Comparator                                   |    |

| 15.6. CS0 Conversion Accumulator                       |    |

| 15.7. CS0 Pin Monitor                                  |    |

| 15.8. Adjusting CS0 For Special Situations             |    |

| 15.9. Capacitive Sense Multiplexer                     |    |

| 16. CIP-51 Microcontroller                             |    |

| 16.1. Instruction Set                                  | 99 |

| SFR Definition 21.5. EIP1: Extended Interrupt Priority 1         | . 144 |

|------------------------------------------------------------------|-------|

| SFR Definition 21.6. EIP2: Extended Interrupt Priority 2         | . 145 |

| SFR Definition 21.7. IT01CF: INT0/INT1 Configuration             |       |

| SFR Definition 22.1. PSCTL: Program Store R/W Control            | . 153 |

| SFR Definition 22.2. FLKEY: Flash Lock and Key                   | . 154 |

| SFR Definition 23.1. EEADDR: EEPROM Byte Address                 |       |

| SFR Definition 23.2. EEDATA: EEPROM Byte Data                    |       |

| SFR Definition 23.3. EECNTL: EEPROM Control                      | . 158 |

| SFR Definition 23.4. EEKEY: EEPROM Protect Key                   |       |

| SFR Definition 24.1. PCON: Power Control                         | . 162 |

| SFR Definition 25.1. VDM0CN: VDD Monitor Control                 | . 166 |

| SFR Definition 25.2. RSTSRC: Reset Source                        |       |

| SFR Definition 26.1. WDTCN: Watchdog Timer Control               | . 170 |

| SFR Definition 27.1. CLKSEL: Clock Select                        | . 172 |

| SFR Definition 27.2. OSCICL: Internal H-F Oscillator Calibration | . 173 |

| SFR Definition 27.3. OSCICN: Internal H-F Oscillator Control     | . 174 |

| SFR Definition 27.4. OSCXCN: External Oscillator Control         | . 176 |

| SFR Definition 28.1. XBR0: Port I/O Crossbar Register 0          | . 190 |

| SFR Definition 28.2. XBR1: Port I/O Crossbar Register 1          |       |

| SFR Definition 28.3. P0MASK: Port 0 Mask Register                |       |

| SFR Definition 28.4. P0MAT: Port 0 Match Register                |       |

| SFR Definition 28.5. P1MASK: Port 1 Mask Register                |       |

| SFR Definition 28.6. P1MAT: Port 1 Match Register                |       |

| SFR Definition 28.7. P0: Port 0                                  | . 195 |

| SFR Definition 28.8. P0MDIN: Port 0 Input Mode                   | . 195 |

| SFR Definition 28.9. P0MDOUT: Port 0 Output Mode                 |       |

| SFR Definition 28.10. P0SKIP: Port 0 Skip                        |       |

| SFR Definition 28.11. P0DRV: Port 0 Drive Strength               | . 197 |

| SFR Definition 28.12. P1: Port 1                                 |       |

| SFR Definition 28.13. P1MDIN: Port 1 Input Mode                  | . 198 |

| SFR Definition 28.14. P1MDOUT: Port 1 Output Mode                |       |

| SFR Definition 28.15. P1SKIP: Port 1 Skip                        | . 199 |

| SFR Definition 28.16. P1DRV: Port 1 Drive Strength               |       |

| SFR Definition 28.17. P2: Port 2                                 |       |

| SFR Definition 28.18. P2MDIN: Port 2 Input Mode                  |       |

| SFR Definition 28.19. P2MDOUT: Port 2 Output Mode                |       |

| SFR Definition 28.20. P2SKIP: Port 2 Skip                        |       |

| SFR Definition 28.21. P2DRV: Port 2 Drive Strength               |       |

| SFR Definition 28.22. P3: Port 3                                 | . 202 |

| SFR Definition 28.23. P3MDIN: Port 3 Input Mode                  | . 203 |

| SFR Definition 28.24. P3MDOUT: Port 3 Output Mode                | . 203 |

| SFR Definition 28.25. P3DRV: Port 3 Drive Strength               |       |

| SFR Definition 28.26. P4: Port 4                                 |       |

| SFR Definition 28.27. P4MDIN: Port 4 Input Mode                  |       |

| SFR Definition 28.28. P4MDOUT: Port 4 Output Mode                |       |

|                                                                  | -     |

# 5. TQFP-48 Package Specifications

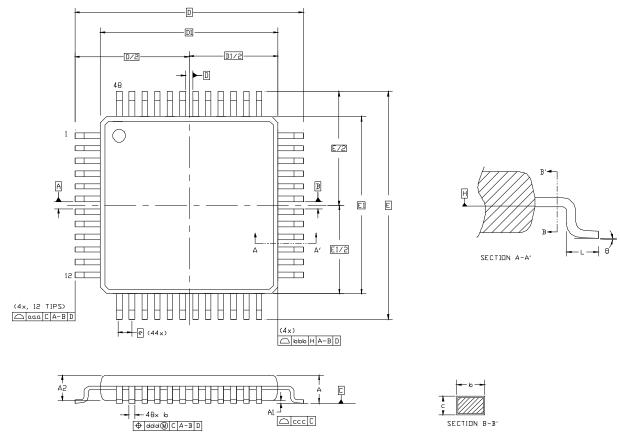

Figure 5.1. TQFP-48 Package Drawing

| Dimension | Min       | Nom  | Max  |  | Dimension | Min  | Nom       | Max  |

|-----------|-----------|------|------|--|-----------|------|-----------|------|

| A         | _         | —    | 1.20 |  | E         |      | 9.00 BSC. |      |

| A1        | 0.05      |      | 0.15 |  | E1        |      | 7.00 BSC. |      |

| A2        | 0.95      | 1.00 | 1.05 |  | L         | 0.45 | 0.60      | 0.75 |

| b         | 0.17      | 0.22 | 0.27 |  | aaa       |      | 0.20      |      |

| С         | 0.09      | —    | 0.20 |  | bbb       |      | 0.20      |      |

| D         | 9.00 BSC. |      |      |  | CCC       |      | 0.08      |      |

| D1        | 7.00 BSC. |      |      |  | ddd       |      | 0.08      |      |

| е         | 0.50 BSC. |      |      |  | Θ         | 0°   | 3.5°      | 7°   |

# Table 5.1. TQFP-48 Package Dimensions

#### Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS-026, variation ABC.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

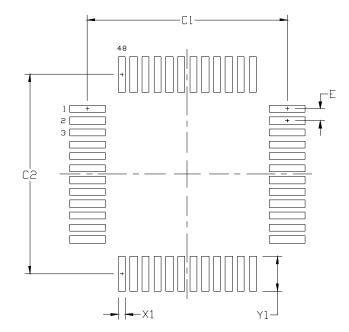

Figure 5.2. TQFP-48 PCB Land Pattern

| Table 5.2. TQFP-48 PCB I | Land Pattern Dimensions |

|--------------------------|-------------------------|

|--------------------------|-------------------------|

| Dimension | Min  | Мах  |

|-----------|------|------|

| C1        | 8.30 | 8.40 |

| C2        | 8.30 | 8.40 |

| Ē         | 0.50 | BSC  |

| X1        | 0.20 | 0.30 |

| Y1        | 1.40 | 1.50 |

Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This land pattern design is based on the IPC-7351 guidelines.

Solder Mask Design

**3.** All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all pads.

Card Assembly

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# SFR Definition 10.2. ADC0H: ADC0 Data Word MSB

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|-----|---|---|---|---|---|---|

| Name  | ADC0H[7:0] |     |   |   |   |   |   |   |

| Туре  |            | R/W |   |   |   |   |   |   |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xBE; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                     |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                                                                                              |

|     |            | For AD0LJST = 0: Bits 7:2 will read 000000b. Bits 1–0 are the upper 2 bits of the 10-<br>bit ADC0 Data Word.                                                                 |

|     |            | For AD0LJST = 1: Bits 7:0 are the most-significant bits of the 10-bit ADC0 Data Word.<br><b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0H holds the 8-bit data word. |

## SFR Definition 10.3. ADC0L: ADC0 Data Word LSB

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | ADC0L[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xBD; SFR Page = 0

| Bit | Name       | Function                                                                                             |

|-----|------------|------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0L[7:0] | ADC0 Data Word Low-Order Bits.                                                                       |

|     |            | For AD0LJST = 0: Bits 7:0 are the lower 8 bits of the 10-bit Data Word.                              |

|     |            | For AD0LJST = 1: Bits 7:6 are the lower 2 bits of the 10-bit Data Word. Bits 5–0 will always read 0. |

|     |            | <b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0L will read back 0000000b.                    |

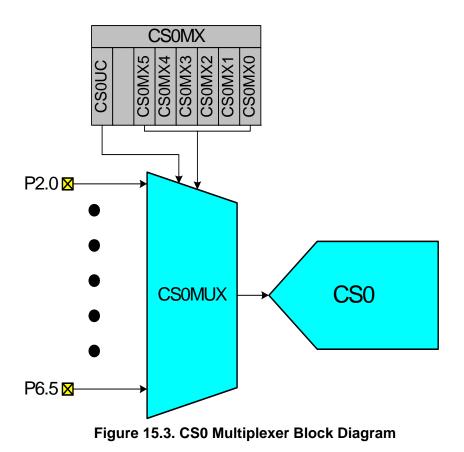

# **15.9. Capacitive Sense Multiplexer**

The input multiplexer can be controlled through two methods. The CSOMX register can be written to through firmware, or the register can be configured automatically using the modules auto-scan functionality (see "15.4. Automatic Scanning").

# SFR Definition 16.3. SP: Stack Pointer

| Bit                                      | 7 | 6   | 5 | 4   | 3    | 2 | 1 | 0 |

|------------------------------------------|---|-----|---|-----|------|---|---|---|

| Name                                     |   |     |   | SP[ | 7:0] |   |   |   |

| Туре                                     |   | R/W |   |     |      |   |   |   |

| Reset                                    | 0 | 0   | 0 | 0   | 0    | 1 | 1 | 1 |

| SFR Address = 0x81; SFR Page = All Pages |   |     |   |     |      |   |   |   |

| D:4                                      |   |     |   |     |      |   |   |   |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

# SFR Definition 16.4. ACC: Accumulator

| Bit   | 7             | 6                                                           | 5             | 4            | 3        | 2 | 1 | 0 |  |  |  |

|-------|---------------|-------------------------------------------------------------|---------------|--------------|----------|---|---|---|--|--|--|

| Nam   | e             |                                                             | [7:0]         |              |          |   |   |   |  |  |  |

| Туре  | R/W           |                                                             |               |              |          |   |   |   |  |  |  |

| Rese  | et 0          | 0                                                           | 0             | 0            | 0        | 0 | 0 | 0 |  |  |  |

| SFR A | Address = 0xE | E0; SFR Page                                                | e = All Pages | ; Bit-Addres | sable    |   |   |   |  |  |  |

| Bit   | Name          |                                                             |               |              | Function |   |   |   |  |  |  |

| 7:0   | ACC[7:0]      | Accumulator.                                                |               |              |          |   |   |   |  |  |  |

|       |               | This register is the accumulator for arithmetic operations. |               |              |          |   |   |   |  |  |  |

Rev. 1.0

| Addr | SFR<br>Page | 0(8)   | 1(9)               | 2(A)             | 3(B)              | 4(C)                | 5(D)              | 6(E)               | 7(F)              |

|------|-------------|--------|--------------------|------------------|-------------------|---------------------|-------------------|--------------------|-------------------|

| F8   | 0<br>F      | SPIOCN | PCA0L<br>P0DRV     | PCA0H<br>P1DRV   | PCA0CPL0<br>P2DRV | PCA0CPH0<br>P3DRV   | P4DRV             | P5DRV              | VDM0CN            |

| F0   | 0<br>F      | В      | POMDIN             | P1MDIN           | P0MAT<br>P2MDIN   | P0MASK<br>P3MDIN    | P4MDIN            | P5MDIN             | P6MDIN            |

| E8   | 0<br>F      | ADC0CN | PCA0CPL1           | PCA0CPH1         | PCA0CPL2          | PCA0CPH2<br>DERIVID | PCA0MD            | EMIOTC             | RSTSRC            |

| E0   | 0<br>F      | ACC    | P1MAT<br>XBR0      | P1MASK<br>XBR1   | WDTCN             | IT01CF              |                   | EIE1               | EIE2              |

| D8   | 0<br>F      | PCA0CN | CRC0DATA           | PCA0CPM0         | PCA0CPM1          | PCA0CPM2            |                   |                    |                   |

| D0   | 0<br>F      | PSW    | EEDATA             | REF0CN           |                   | P0SKIP              | P1SKIP            | P2SKIP             |                   |

| C8   | 0<br>F      | TMR2CN |                    | TMR2RLL          | TMR2RLH           | TMR2L               | TMR2H             | EIP1               | EIP2              |

| C0   | 0<br>F      | SMB0CN | SMB0CF<br>P6DRV    | SMB0DAT          | ADC0GTL           | ADC0GTH<br>HWID     | ADC0LTL<br>EECNTL | ADC0LTH<br>EEKEY   | EMI0CF            |

| B8   | 0<br>F      | IP     | REG0CN             | SMB0ADR          | ADC0MX<br>SMB0ADM | ADC0CF              | ADC0L<br>CLKSEL   | ADC0H<br>CS0MD2    | OSCICL            |

| B0   | 0<br>F      | P3     |                    | P6               | P5                |                     | OSCXCN            | EEADDR             | FLKEY             |

| A8   | 0<br>F      | IE     | CS0DL<br>OSCICN    | CS0DH<br>EMI0CN  |                   | P4                  | CS0MD1<br>REVID   |                    | P3MDOUT           |

| A0   | 0<br>F      | P2     | SPI0CFG<br>PCA0PWM | SPI0CKR          | SPI0DAT           | POMDOUT             | P1MDOUT           | P2MDOUT            | SFRPAGE           |

| 98   | 0<br>F      | SCON0  | SBUF0              | CS0CN<br>P4MDOUT | CPT0CN<br>P5MDOUT | CS0MX<br>P6MDOUT    | CPT0MD            | CS0CF              | CPT0MX<br>CS0PM   |

| 90   | 0<br>F      | P1     | TMR3CN<br>CRC0CN   | TMR3RLL<br>CS0SS | TMR3RLH<br>CS0SE  | TMR3L<br>CRC0IN     | TMR3H<br>CRC0FLIP | CS0THL<br>CRC0AUTO | CS0THH<br>CRC0CNT |

| 88   | 0<br>F      | TCON   | TMOD               | TL0              | TL1               | TH0                 | TH1               | CKCON              | PSCTL             |

| 80   | 0<br>F      | P0     | SP                 | DPL              | DPH               |                     |                   |                    | PCON              |

|      |             | 0(8)   | 1(9)               | 2(A)             | 3(B)              | 4(C)                | 5(D)              | 6(E)               | 7(F)              |

| Table 20.1. | Special Fu | Inction F  | Register   | (SFR) | Memory      | Man |

|-------------|------------|------------|------------|-------|-------------|-----|

| Table 20.1. | Special Fu | IIICUOII I | vegisiei i | (SER) | INICITIOT Y | wap |

#### Notes:

1. SFR addresses ending in 0x0 or 0x8 (leftmost column) are bit-addressable.

2. SFRs indicated with bold lettering and shaded cells are available on both SFR Page 0 and F.

# Table 20.2. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Page      | Description                        | Page |

|----------|---------|-----------|------------------------------------|------|

| CS0CN    | 0x9A    | 0         | CS0 Control                        | 88   |

| CS0DH    | 0xAA    | 0         | CS0 Data High                      | 90   |

| CS0DL    | 0xA9    | 0         | CS0 Data Low                       | 90   |

| CS0CF    | 0x9E    | 0         | CS0 Configuration                  | 89   |

| CS0MD1   | 0xAD    | 0         | CS0 Mode 1                         | 94   |

| CS0MD2   | 0xBE    | F         | CS0 Mode 2                         | 95   |

| CSOMX    | 0x9C    | 0         | CS0 Mux                            | 97   |

| CS0PM    | 0x9F    | F         | CS0 Pin Monitor                    | 93   |

| CS0SE    | 0x93    | F         | Auto Scan End Channel              | 91   |

| CS0SS    | 0x92    | F         | Auto Scan Start Channel            | 91   |

| CS0THH   | 0x97    | 0         | CS0 Digital Compare Threshold High | 92   |

| CS0THL   | 0x96    | 0         | CS0 Digital Compare Threshold Low  | 92   |

| DERIVID  | 0xEC    | F         | Derivative Identification          | 128  |

| DPH      | 0x83    | All Pages | Data Pointer High                  | 104  |

| DPL      | 0x82    | All Pages | Data Pointer Low                   | 104  |

| EEADDR   | 0xB6    | All Pages | EEPROM Byte Address                | 156  |

| EECNTL   | 0xC5    | F         | EEPROM Control                     | 158  |

| EEDATA   | 0xD1    | All Pages | EEPROM Byte Data                   | 157  |

| EEKEY    | 0xC6    | F         | EEPROM Protect Key                 | 159  |

| EIE1     | 0xE6    | All Pages | Extended Interrupt Enable 1        | 142  |

| EIE2     | 0xE7    | All Pages | Extended Interrupt Enable 2        | 143  |

| EIP1     | 0xCE    | F         | Extended Interrupt Priority 1      | 144  |

| EIP2     | 0xCF    | F         | Extended Interrupt Priority 2      | 145  |

| EMI0CF   | 0xC7    | F         | EMIF Configuration                 | 114  |

| EMIOCN   | 0xAA    | F         | EMIF Control                       | 113  |

| EMIOTC   | 0xEE    | F         | EMIF Timing Control                | 119  |

| FLKEY    | 0xB7    | All Pages | Flash Lock And Key                 | 154  |

| HWID     | 0xC4    | F         | Hardware Identification            | 128  |

| IE       | 0xA8    | All Pages | Interrupt Enable                   | 140  |

| IP       | 0xB8    | All Pages | Interrupt Priority                 | 141  |

| IT01CF   | 0xE4    | F         | INT0/INT1 Configuration            | 147  |

| OSCICL   | 0xBF    | F         | Internal Oscillator Calibration    | 173  |

| OSCICN   | 0xA9    | F         | Internal Oscillator Control        | 174  |

| OSCXCN   | 0xB5    | F         | External Oscillator Control        | 176  |

| P0       | 0x80    | All Pages | Port 0 Latch                       | 195  |

| P0DRV    | 0xF9    | F         | Port 0 Drive Strength              | 197  |

| POMASK   | 0xF4    | 0         | Port 0 Mask                        | 192  |

| POMAT    | 0xF3    | 0         | Port 0 Match                       | 193  |

- 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- 7. Clear the PSWE and PSEE bits.

- 8. Restore previous interrupt state.

Steps 4–6 must be repeated for each 512-byte page to be erased.

**Note:** Flash security settings may prevent erasure of some Flash pages, such as the reserved area and the page containing the lock bytes. For a summary of Flash security settings and restrictions affecting Flash erase operations, please see Section "22.3. Security Options" on page 149.

#### 22.1.3. Flash Write Procedure

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed should be erased before a new value is written.

The recommended procedure for writing a single byte in Flash is as follows:

- 1. Save current interrupt state and disable interrupts.

- 2. Ensure that the Flash byte has been erased (has a value of 0xFF).

- 3. Set the PSWE bit (register PSCTL).

- 4. Clear the PSEE bit (register PSCTL).

- 5. Write the first key code to FLKEY: 0xA5.

- 6. Write the second key code to FLKEY: 0xF1.

- 7. Using the MOVX instruction, write a single data byte to the desired location within the 512-byte sector.

- 8. Clear the PSWE bit.

- 9. Restore previous interrupt state.

Steps 5–7 must be repeated for each byte to be written.

**Note:** Flash security settings may prevent writes to some areas of Flash, such as the reserved area. For a summary of Flash security settings and restrictions affecting Flash write operations, please see Section "22.3. Security Options" on page 149.

#### 22.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction.

Note: MOVX read instructions always target XRAM.

#### 22.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, and erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock all Flash pages, starting at page 0, by writing a non-0xFF value to the lock byte. Note that writing a non-0xFF value to the lock byte will lock all pages of FLASH from reads, writes, and erases, including the page containing the lock byte.

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on

# 24. Power Management Modes

The C8051F70x/71x devices have three software programmable power management modes: Idle, Stop, and Suspend. Idle mode and Stop mode are part of the standard 8051 architecture, while Suspend mode is an enhanced power-saving mode implemented by the high-speed oscillator peripheral.

Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Suspend mode is similar to Stop mode in that the internal oscillator and CPU are halted, but the device can wake on events such as a Port Mismatch, Comparator low output, or a Timer 3 overflow. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode and Suspend mode consume the least power because the majority of the device is shut down with no clocks active. SFR Definition 24.1 describes the Power Control Register (PCON) used to control the C8051F70x/71x's Stop and Idle power management modes. Suspend mode is controlled by the SUSPEND bit in the OSCICN register (SFR Definition 27.3).

Although the C8051F70x/71x has Idle, Stop, and Suspend modes available, more control over the device power can be achieved by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off oscillators lowers power consumption considerably, at the expense of reduced functionality.

## 24.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the hardware to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

**Note:** If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Therefore, instructions that set the IDLE bit should be followed by an instruction that has two or more opcode bytes, for example:

| // in `C':<br>PCON  = 0x01;<br>PCON = PCON;        | <pre>// set IDLE bit // followed by a 3-cycle dummy instruction</pre> |

|----------------------------------------------------|-----------------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction           |

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "26. Watchdog Timer" on page 169 for more information on the use and configuration of the WDT.

# SFR Definition 27.1. CLKSEL: Clock Select

| Bit   | 7      | 6           | 5   | 4   | 3        | 2           | 1   | 0   |  |

|-------|--------|-------------|-----|-----|----------|-------------|-----|-----|--|

| Name  | CLKRDY | CLKDIV[2:0] |     |     | Reserved | CLKSEL[2:0] |     |     |  |

| Туре  | R      | R/W         | R/W | R/W | R        | R/W         | R/W | R/W |  |

| Reset | 0      | 0           | 0   | 0   | 0        | 0           | 0   | 0   |  |

SFR Address = 0xBD; SFR Page= F

| Bit | Name        | Function                                                                                |

|-----|-------------|-----------------------------------------------------------------------------------------|

| 7   | CLKRDY      | System Clock Divider Clock Ready Flag.                                                  |

|     |             | 0: The selected clock divide setting has not been applied to the system clock.          |

|     |             | 1: The selected clock divide setting has been applied to the system clock.              |

| 6:4 | CLKDIV      | System Clock Divider Bits.                                                              |

|     |             | Selects the clock division to be applied to the selected source (internal or external). |

|     |             | 000: Selected clock is divided by 1.                                                    |

|     |             | 001: Selected clock is divided by 2.                                                    |

|     |             | 010: Selected clock is divided by 4.                                                    |

|     |             | 011: Selected clock is divided by 8.                                                    |

|     |             | 100: Selected clock is divided by 16.                                                   |

|     |             | 101: Selected clock is divided by 32.                                                   |

|     |             | 110: Selected clock is divided by 64.                                                   |

|     |             | 111: Selected clock is divided by 128.                                                  |

| 3   | Reserved    | Read = 0b. Must write 0b.                                                               |

| 2:0 | CLKSEL[2:0] | System Clock Select.                                                                    |

|     |             | Selects the oscillator to be used as the undivided system clock source.                 |

|     |             | 000: Internal Oscillator                                                                |

|     |             | 001: External Oscillator                                                                |

|     |             |                                                                                         |

|     |             | All other values reserved.                                                              |

| Table 30.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

|                    | V               | alu    | es F  | Rea     | d   |                                                    |                                                                                                |     | lues<br>Nrit |     | tus<br>ected                   |

|--------------------|-----------------|--------|-------|---------|-----|----------------------------------------------------|------------------------------------------------------------------------------------------------|-----|--------------|-----|--------------------------------|

| Mode               | Status          | Vector | ACKRQ | ARBLOST | ACK | Current SMbus State                                | Typical Response Options                                                                       | STA | STO          | ACK | Next Status<br>Vector Expected |

|                    | 11 <sup>.</sup> | 10     | 0     | 0       | х   | A master START was gener-<br>ated.                 | Load slave address + R/W into SMB0DAT.                                                         | 0   | 0            | Х   | 1100                           |

|                    |                 |        | 0     | 0       | 0   | A master data or address byte                      | Set STA to restart transfer.                                                                   | 1   | 0            | Х   | 1110                           |

| er                 |                 |        | 0     | 0       | 0   | was transmitted; NACK received.                    | Abort transfer.                                                                                | 0   | 1            | Х   | —                              |

| Master Transmitter |                 |        |       |         |     |                                                    | Load next data byte into<br>SMB0DAT.                                                           | 0   | 0            | Х   | 1100                           |

| . Tra              | 11(             | 20     |       |         |     |                                                    | End transfer with STOP.                                                                        | 0   | 1            | Х   |                                |

| Master             |                 | 00     | 0     | 0       | 1   | A master data or address byte was transmitted; ACK | End transfer with STOP and start another transfer.                                             | 1   | 1            | Х   | —                              |

|                    |                 |        |       |         |     | received.                                          | Send repeated START.                                                                           | 1   | 0            | Х   | 1110                           |

|                    |                 |        |       |         |     |                                                    | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT).           | 0   | 0            | Х   | 1000                           |

|                    |                 |        |       |         |     |                                                    | Acknowledge received byte;<br>Read SMB0DAT.                                                    | 0   | 0            | 1   | 1000                           |

|                    |                 |        |       |         |     |                                                    | Send NACK to indicate last byte, and send STOP.                                                | 0   | 1            | 0   | —                              |

| ver                |                 |        |       |         |     |                                                    | Send NACK to indicate last byte,<br>and send STOP followed by<br>START.                        | 1   | 1            | 0   | 1110                           |

| ster Receiver      | 10              | 00     | 1     | 0       | х   | A master data byte was received; ACK requested.    | Send ACK followed by repeated START.                                                           | 1   | 0            | 1   | 1110                           |

| Master             |                 |        |       |         |     |                                                    | Send NACK to indicate last byte, and send repeated START.                                      | 1   | 0            | 0   | 1110                           |

|                    |                 |        |       |         |     |                                                    | Send ACK and switch to Master<br>Transmitter Mode (write to<br>SMB0DAT before clearing SI).    | 0   | 0            | 1   | 1100                           |

|                    |                 |        |       |         |     |                                                    | Send NACK and switch to Mas-<br>ter Transmitter Mode (write to<br>SMB0DAT before clearing SI). | 0   | 0            | 0   | 1100                           |

# 31.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

### 31.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

### 31.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

### 31.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 31.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- 1. NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- 3. NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 31.2, Figure 31.3, and Figure 31.4 for typical connection diagrams of the various operational modes. **Note that the setting of NSSMD bits affects the pinout of the device.** When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "28. Port Input/Output" on page 180 for general purpose port I/O and crossbar information.

## 31.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic

## 31.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

All of the following bits must be cleared by software.

- The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

## 31.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 31.5. For slave mode, the clock and data relationships are shown in Figure 31.6 and Figure 31.7. CKPHA should be set to 0 on both the master and slave SPI when communicating between two Silicon Labs C8051 devices.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 31.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e., half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

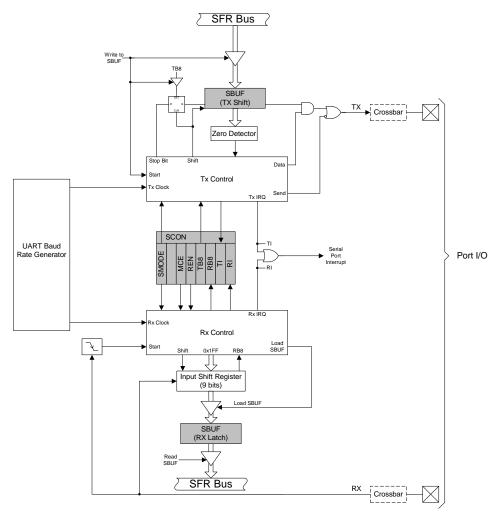

# 32. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in Section "32.1. Enhanced Baud Rate Generation" on page 255). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UART0 has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Writes to SBUF0 always access the Transmit register. Reads of SBUF0 always access the buffered Receive register; it is not possible to read data from the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

Figure 32.1. UART0 Block Diagram

## 32.2. Operational Modes

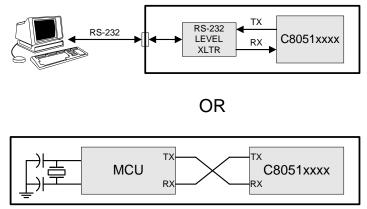

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown in Figure 32.3.

Figure 32.3. UART Interconnect Diagram

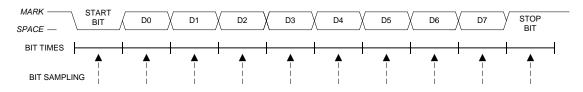

## 32.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 32.4. 8-Bit UART Timing Diagram

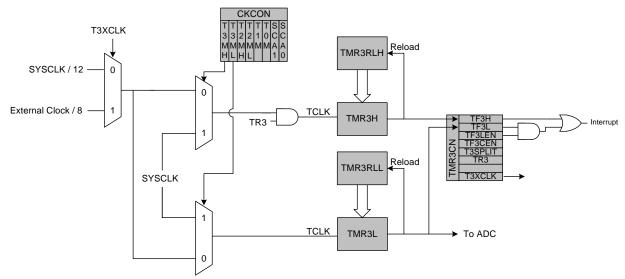

### 33.3.2. 8-bit Timers with Auto-Reload

When T3SPLIT is set, Timer 3 operates as two 8-bit timers (TMR3H and TMR3L). Both 8-bit timers operate in auto-reload mode as shown in Figure 33.8. TMR3RLL holds the reload value for TMR3L; TMR3RLH holds the reload value for TMR3H. The TR3 bit in TMR3CN handles the run control for TMR3H. TMR3L is always running when configured for 8-bit Mode. Timer 3 can also be used in capture mode to capture rising edges of the Comparator 0 output.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 3 clock select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bits (T3XCLK in TMR3CN), as follows:

| ТЗМН | T3XCLK | TMR3H Clock<br>Source |

|------|--------|-----------------------|

| 0    | 0      | SYSCLK / 12           |

| 0    | 1      | External Clock / 8    |

| 1    | Х      | SYSCLK                |

| T3ML | T3XCLK | TMR3L Clock<br>Source |

|------|--------|-----------------------|

| 0    | 0      | SYSCLK / 12           |

| 0    | 1      | External Clock / 8    |

| 1    | Х      | SYSCLK                |

The TF3H bit is set when TMR3H overflows from 0xFF to 0x00; the TF3L bit is set when TMR3L overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled, an interrupt is generated each time TMR3H overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TMR3L or TMR3H overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 33.8. Timer 3 8-Bit Mode Block Diagram

# 34.4. Register Descriptions for PCA0

Following are detailed descriptions of the special function registers related to the operation of the PCA.

# SFR Definition 34.1. PCA0CN: PCA Control

| Bit   | 7   | 6   | 5 | 4 | 3 | 2    | 1    | 0    |

|-------|-----|-----|---|---|---|------|------|------|

| Name  | CF  | CR  |   |   |   | CCF2 | CCF1 | CCF0 |

| Туре  | R/W | R/W | R | R | R | R/W  | R/W  | R/W  |

| Reset | 0   | 0   | 0 | 0 | 0 | 0    | 0    | 0    |

SFR Address = 0xD8; SFR Page = All Pages; Bit-Addressable

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                           |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CF       | PCA Counter/Timer Overflow Flag.                                                                                                                                                                                                                                                                                   |

|     |          | Set by hardware when the PCA Counter/Timer overflows from 0xFFFF to 0x0000.<br>When the Counter/Timer Overflow (CF) interrupt is enabled, setting this bit causes the<br>CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared<br>by hardware and must be cleared by software. |

| 6   | CR       | PCA Counter/Timer Run Control.                                                                                                                                                                                                                                                                                     |

|     |          | This bit enables/disables the PCA Counter/Timer.                                                                                                                                                                                                                                                                   |

|     |          | 0: PCA Counter/Timer disabled.                                                                                                                                                                                                                                                                                     |

|     |          | 1: PCA Counter/Timer enabled.                                                                                                                                                                                                                                                                                      |

| 5:3 | Unused   | Read = 000b; Write = Don't care                                                                                                                                                                                                                                                                                    |

| 2:0 | CCF[2:0] | PCA Module n Capture/Compare Flag.                                                                                                                                                                                                                                                                                 |

|     |          | These bits are set by hardware when a match or capture occurs in the associated PCA Module n. When the CCFn interrupt is enabled, setting this bit causes the CPU to vector to the PCA interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.               |

# DOCUMENT CHANGE LIST

## **Revision 0.5 to Revision 1.0**

- Updated "Electrical Characteristics" on page 47.

- Updated "Port Input/Output" on page 180.

## **Revision 0.4 to Revision 0.5**

- Removed Incorrect Pin Connections in Figure 1.4 on page 21 and Figure 1.6 on page 23.

- Updated Specifications in Section "9. Electrical Characteristics" on page 47.

- Updated Section "15. Capacitive Sense (CS0)" on page 80 for clarity.

- Corrected "CJNE A, direct, rel" instruction timing in Table 16.1.

- Noted that a minimum SYSCLK speed is required for Flash writes or erases in Section "22.1. Programming The Flash Memory" on page 148, and for EEPROM writes in Section "23.3. Interfacing with the EEPROM" on page 155.

- Corrected P0.3 overvoltage capabilities throughout document.

## **Revision 0.3 to Revision 0.4**

- Updated Section "15. Capacitive Sense (CS0)" on page 80 to reflect Revision B enhancements.

- Added C8051F716 and C8051F717 devices, package information, and features.

- Updated Register 19.1, "HWID: Hardware Identification Byte," on page 128.

- Corrected minor typographical and formatting errors throughout document.

## **Revision 0.2 to Revision 0.3**

- Corrected Dimension D in the QFN-48 Package Specifications.

- Updated Table 9.1 on page 47.

- Updated Register 10.1, "ADC0CF: ADC0 Configuration," on page 59.

- Updated Register 14.3, "CPT0MX: Comparator0 MUX Selection," on page 79.

- Updated Section "28.1.1. Port Pins Configured for Analog I/O" on page 181.

- Updated Register 35.2, "DEVICEID: C2 Device ID," on page 302.