# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 39                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | 32 x 8                                                          |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 48-QFN (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f712-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 31.5. Serial Clock Phase and Polarity                               |     |

|---------------------------------------------------------------------|-----|

| 31.6. SPI Special Function Registers                                |     |

| 32. UART0                                                           |     |

| 32.1. Enhanced Baud Rate Generation                                 |     |

| 32.2. Operational Modes                                             |     |

| 32.2.1. 8-Bit UART                                                  |     |

| 32.2.2. 9-Bit UART                                                  |     |

| 32.3. Multiprocessor Communications                                 |     |

| 33. Timers                                                          |     |

| 33.1. Timer 0 and Timer 1                                           |     |

| 33.1.1. Mode 0: 13-bit Counter/Timer                                |     |

| 33.1.2. Mode 1: 16-bit Counter/Timer                                |     |

| 33.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload                |     |

| 33.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)             |     |

| 33.2. Timer 2                                                       |     |

| 33.2.1. 16-bit Timer with Auto-Reload                               |     |

| 33.2.2. 8-bit Timers with Auto-Reload                               |     |

| 33.3. Timer 3                                                       |     |

| 33.3.1. 16-bit Timer with Auto-Reload                               |     |

| 33.3.2. 8-bit Timers with Auto-Reload                               |     |

| 34. Programmable Counter Array                                      | 284 |

| 34.1. PCA Counter/Timer                                             |     |

| 34.2. PCA0 Interrupt Sources                                        |     |

| 34.3. Capture/Compare Modules                                       | 286 |

| 34.3.1. Edge-triggered Capture Mode                                 | 288 |

| 34.3.2. Software Timer (Compare) Mode                               |     |

| 34.3.3. High-Speed Output Mode                                      |     |

| 34.3.4. Frequency Output Mode                                       |     |

| 34.3.5. 8-bit, 9-bit, 10-bit and 11-bit Pulse Width Modulator Modes |     |

| 34.3.5.1. 8-bit Pulse Width Modulator Mode                          |     |

| 34.3.5.2. 9/10/11-bit Pulse Width Modulator Mode                    |     |

| 34.3.6. 16-Bit Pulse Width Modulator Mode                           |     |

| 34.4. Register Descriptions for PCA0                                |     |

| 35. C2 Interface                                                    |     |

| 35.1. C2 Interface Registers                                        |     |

| 35.2. C2CK Pin Sharing                                              |     |

| Document Change List                                                |     |

| Contact Information                                                 | 306 |

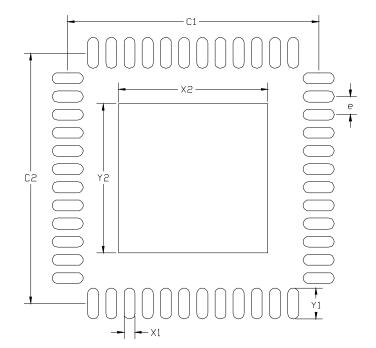

### Figure 6.2. QFN-48 PCB Land Pattern

Table 6.2. QFN-48 PCB Land Pattern Dimensions

| Dimension | Min  | Max  |

|-----------|------|------|

| e         | 0.50 | BSC  |

| C1        | 6.80 | 6.90 |

| C2        | 6.80 | 6.90 |

| X1        | 0.20 | 0.30 |

| X2        | 4.00 | 4.10 |

| Y1        | 0.75 | 0.85 |

| Y2        | 4.00 | 4.10 |

Notes: General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on IPC-SM-7351 guidelines.

- 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

Stencil Design

- 6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 7. The stencil thickness should be 0.125 mm (5 mils).

- 8. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

9. A 3x3 array of 1.20 mm square openings on 1.40 mm pitch should be used for the center ground pad.

Card Assembly

- 10. A No-Clean, Type-3 solder paste is recommended.

- 11. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

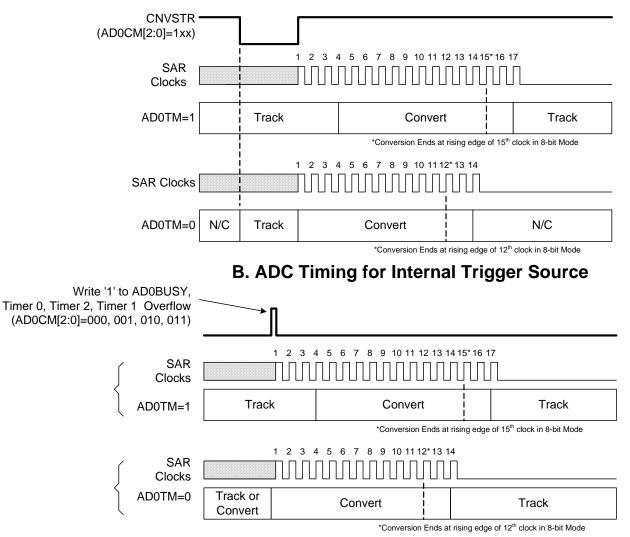

#### 10.3.2. Tracking Modes

The AD0TM bit in register ADC0CN enables "delayed conversions", and will delay the actual conversion start by three SAR clock cycles, during which time the ADC will continue to track the input. If AD0TM is left at logic 0, a conversion will begin immediately, without the extra tracking time. For internal start-of-conversion sources, the ADC will track anytime it is not performing a conversion. When the CNVSTR signal is used to initiate conversions, ADC0 will track either when AD0TM is logic 1, or when AD0TM is logic 0 and CNVSTR is held low. See Figure 10.2 for track and convert timing details. Delayed conversion mode is useful when AMUX settings are frequently changed, due to the settling time requirements described in Section "10.3.3. Settling Time Requirements" on page 58.

Figure 10.2. 10-Bit ADC Track and Conversion Example Timing

## SFR Definition 10.2. ADC0H: ADC0 Data Word MSB

| Bit   | 7          | 6 | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|----|---|---|---|---|--|--|

| Name  | ADC0H[7:0] |   |   |    |   |   |   |   |  |  |

| Туре  |            |   |   | R/ | W |   |   |   |  |  |

| Reset | 0          | 0 | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xBE; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                     |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                                                                                              |

|     |            | For AD0LJST = 0: Bits 7:2 will read 000000b. Bits 1–0 are the upper 2 bits of the 10-<br>bit ADC0 Data Word.                                                                 |

|     |            | For AD0LJST = 1: Bits 7:0 are the most-significant bits of the 10-bit ADC0 Data Word.<br><b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0H holds the 8-bit data word. |

### SFR Definition 10.3. ADC0L: ADC0 Data Word LSB

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | ADC0L[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xBD; SFR Page = 0

| Bit | Name       | Function                                                                                             |

|-----|------------|------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0L[7:0] | ADC0 Data Word Low-Order Bits.                                                                       |

|     |            | For AD0LJST = 0: Bits 7:0 are the lower 8 bits of the 10-bit Data Word.                              |

|     |            | For AD0LJST = 1: Bits 7:6 are the lower 2 bits of the 10-bit Data Word. Bits 5–0 will always read 0. |

|     |            | <b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0L will read back 0000000b.                    |

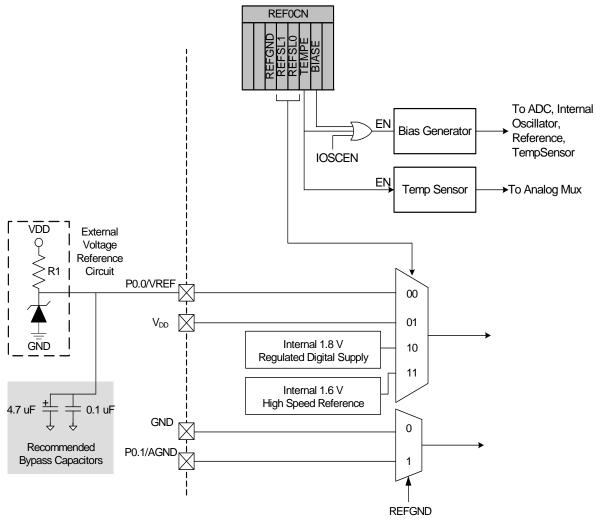

## 12. Voltage and Ground Reference Options

The voltage reference MUX is configurable to use an externally connected voltage reference, the on-chip voltage reference, or one of two power supply voltages (see Figure 12.1). The ground reference MUX allows the ground reference for ADC0 to be selected between the ground pin (GND) or a port pin dedicated to analog ground (P0.1/AGND).

The voltage and ground reference options are configured using the REF0CN SFR described on page 71. Electrical specifications are can be found in the Electrical Specifications Chapter.

**Important Note About the V<sub>REF</sub> and AGND Inputs:** Port pins are used as the external V<sub>REF</sub> and AGND inputs. When using an external voltage reference, P0.0/VREF should be configured as an analog input and skipped by the Digital Crossbar. When using AGND as the ground reference to ADC0, P0.1/AGND should be configured as an analog input and skipped by the Digital Crossbar. Refer to Section "28. Port Input/Output" on page 180 for complete Port I/O configuration details. The external reference voltage must be within the range  $0 \le V_{REF} \le V_{DD}$  and the external ground reference must be at the same DC voltage potential as GND.

Figure 12.1. Voltage Reference Functional Block Diagram

## SFR Definition 18.3. EMI0TC: External Memory Timing Control

| Bit   | 7                                        | 6                          | 5            | 4          | 3       | 2 | 1   | 0  |  |  |  |

|-------|------------------------------------------|----------------------------|--------------|------------|---------|---|-----|----|--|--|--|

| Nam   | e EA                                     | S[1:0]                     |              |            |         |   |     |    |  |  |  |

| Туре  | <b>,</b> F                               | R/W                        |              | R          | /W      |   | R/W |    |  |  |  |

| Rese  | et 1                                     |                            |              |            |         |   | 1   | 1  |  |  |  |

| SFR A | ddress = 0xE                             | EE; SFR Page               | e = F        |            |         |   |     | II |  |  |  |

| Bit   | Name                                     |                            |              |            |         |   |     |    |  |  |  |

| 7:6   | 6 EAS[1:0] EMIF Address Setup Time Bits. |                            |              |            |         |   |     |    |  |  |  |

|       |                                          | 00: Address                | setup time = | = 0 SYSCLK | cycles. |   |     |    |  |  |  |

|       |                                          | 01: Address                | setup time = | = 1 SYSCLK | cycle.  |   |     |    |  |  |  |

|       |                                          | 10: Address                | •            |            | •       |   |     |    |  |  |  |

|       |                                          | 11: Address                | setup time = | = 3 SYSCLK | cycles. |   |     |    |  |  |  |

| 5:2   | EWR[3:0]                                 | EMIF WR an                 |              |            |         |   |     |    |  |  |  |

|       |                                          | 0000: WR ar                |              |            |         |   |     |    |  |  |  |

|       |                                          | 0001: <u>WR</u> ar         |              |            |         |   |     |    |  |  |  |

|       |                                          | 0010: WR ar                |              |            |         |   |     |    |  |  |  |

|       |                                          | 0011: WR ar<br>0100: WR ar |              |            | •       |   |     |    |  |  |  |

|       |                                          | 0100: WR an                |              |            |         |   |     |    |  |  |  |

|       |                                          | 0110: WR ar                |              |            | •       |   |     |    |  |  |  |

|       |                                          | 0111: WR an                |              |            | •       |   |     |    |  |  |  |

|       |                                          | 1000: WR ar                |              |            | •       |   |     |    |  |  |  |

|       |                                          | 1001: <u>WR</u> ar         |              |            |         |   |     |    |  |  |  |

|       |                                          | 1010: WR ar                |              |            | •       |   |     |    |  |  |  |

|       |                                          | 1011: WR ar<br>1100: WR ar |              |            |         |   |     |    |  |  |  |

|       |                                          | 1100. WR an<br>1101: WR ar |              |            |         |   |     |    |  |  |  |

|       |                                          | 1110: WR an                |              |            |         |   |     |    |  |  |  |

|       |                                          | 1111: WR an                |              |            |         |   |     |    |  |  |  |

| 1:0   | EAH[1:0]                                 | EMIF Addre                 | ss Hold Tin  | ne Bits.   |         |   |     |    |  |  |  |

|       |                                          | 00: Address                |              |            | •       |   |     |    |  |  |  |

|       |                                          | 01: Address                |              |            | •       |   |     |    |  |  |  |

|       |                                          | 10: Address                |              |            | •       |   |     |    |  |  |  |

|       |                                          | 11: Address                | nola time =  | 3 SYSULK C | cycles. |   |     |    |  |  |  |

## SFR Definition 20.1. SFRPAGE: SFR Page

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------|---|---|---|---|---|---|---|--|--|

| Name  | SFRPAGE[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W          |   |   |   |   |   |   |   |  |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xA7; SFR Page = All Pages

| Bit | Name         | Description                                                                      |

|-----|--------------|----------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page Bits.                                                                   |

|     |              | Represents the SFR Page the C8051 core uses when reading or modifying SFRs.      |

|     |              | Write: Sets the SFR Page.<br>Read: Byte is the SFR page the C8051 core is using. |

### Table 20.2. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Page      | Description                       | Page |

|----------|---------|-----------|-----------------------------------|------|

| ACC      | 0xE0    | All Pages | Accumulator                       | 105  |

| ADC0CF   | 0xBC    | F         | ADC0 Configuration                | 59   |

| ADC0CN   | 0xE8    | All Pages | ADC0 Control                      | 61   |

| ADC0GTH  | 0xC4    | 0         | ADC0 Greater-Than Compare High    | 62   |

| ADC0GTL  | 0xC3    | 0         | ADC0 Greater-Than Compare Low     | 62   |

| ADC0H    | 0xBE    | 0         | ADC0 High                         | 60   |

| ADC0L    | 0xBD    | 0         | ADC0 Low                          | 60   |

| ADC0LTH  | 0xC6    | 0         | ADC0 Less-Than Compare Word High  | 63   |

| ADC0LTL  | 0xC5    | 0         | ADC0 Less-Than Compare Word Low   | 63   |

| ADC0MX   | 0xBB    | 0         | AMUX0 Multiplexer Channel Select  | 66   |

| В        | 0xF0    | All Pages | B Register                        | 106  |

| CKCON    | 0x8E    | All Pages | Clock Control                     | 263  |

| CLKSEL   | 0xBD    | F         | Clock Select                      | 263  |

| CPT0CN   | 0x9B    | 0         | Comparator0 Control               | 76   |

| CPT0MD   | 0x9D    | 0         | Comparator0 Mode Selection        | 77   |

| CPT0MX   | 0x9F    | 0         | Comparator0 MUX Selection         | 79   |

| CRC0AUTO | 0x96    | F         | CRC0 Automatic Control Register   | 217  |

| CRC0CN   | 0x91    | F         | CRC0 Control                      | 215  |

| CRC0CNT  | 0x97    | F         | CRC0 Automatic Flash Sector Count | 217  |

| CRC0DATA | 0xD9    | F         | CRC0 Data Output                  | 216  |

| CRC0FLIP | 0x95    | F         | CRC0 Bit Flip                     | 218  |

| CRCOIN   | 0x94    | F         | CRC Data Input                    | 216  |

## 21. Interrupts

The C8051F70x/71x includes an extended interrupt system supporting several interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE–EIE1). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

## SFR Definition 21.4. EIE2: Extended Interrupt Enable 2

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |

|-------|---|---|---|---|---|---|--------|--------|

| Name  |   |   |   |   |   |   | ECSGRT | ECSCPT |

| Туре  | R | R | R | R | R | R | R/W    | R/W    |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0      |

#### SFR Address = 0xE7; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                           |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b; Write = don't care.                                                                                                                                                                                |

| 1   | ECSGRT | <ul> <li>Enable Capacitive Sense Greater Than Comparator Interrupt.</li> <li>0: Disable Capacitive Sense Greater Than Comparator interrupt.</li> <li>1: Enable interrupt requests generated by CS0CMPF.</li> </ul> |

| 0   | ECSCPT | <ul> <li>Enable Capacitive Sense Conversion Complete Interrupt.</li> <li>0: Disable Capacitive Sense Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by CS0INT.</li> </ul>          |

## SFR Definition 22.1. PSCTL: Program Store R/W Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|-------|---|---|---|---|---|---|------|------|

| Name  |   |   |   |   |   |   | PSEE | PSWE |

| Туре  | R | R | R | R | R | R | R/W  | R/W  |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

## SFR Address =0x8F; SFR Page = All Pages

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused | Read = 000000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | PSEE   | Program Store Erase Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit (in combination with PSWE) allows an entire page of Flash program memory to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.</li> <li>0: Flash program memory erasure disabled.</li> <li>1: Flash program memory erasure enabled.</li> </ul> |

| 0   | PSWE   | Program Store Write Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |        | <ul> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul>                                                                                                                                                     |

## SFR Definition 24.1. PCON: Power Control

| Bit   | 7 | 6 | 5   | 4    | 3    | 2 | 1 | 0 |

|-------|---|---|-----|------|------|---|---|---|

| Name  |   |   |     | STOP | IDLE |   |   |   |

| Туре  |   |   | R/W | R/W  |      |   |   |   |

| Reset | 0 | 0 | 0   | 0    | 0    | 0 | 0 | 0 |

SFR Address = 0x87; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                                                                                                                   |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | GF[5:0] | General Purpose Flags 5–0.                                                                                                                                                                                                                                                 |

|     |         | These are general purpose flags for use under software control.                                                                                                                                                                                                            |

| 1   | STOP    | Stop Mode Select.                                                                                                                                                                                                                                                          |

|     |         | Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.<br>1: CPU goes into Stop mode (internal oscillator stopped).                                                                                                                       |

| 0   | IDLE    | <b>IDLE: Idle Mode Select.</b><br>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.<br>1: CPU goes into Idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts, Serial Ports, and Analog Peripherals are still active.) |

| Analog Function                                       | Potentially Assignable<br>Port Pins | SFR(s) used for<br>Assignment   |

|-------------------------------------------------------|-------------------------------------|---------------------------------|

| ADC Input                                             | P0.0–P1.7                           | AMX0P, AMX0N,<br>PnSKIP, PnMDIN |

| Comparator0 Input                                     | P1.0-P1.7                           | CPT0MX, PnSKIP,<br>PnMDIN       |

| CS0 Input                                             | P2.0–P6.5                           | PnMDIN                          |

| Voltage Reference (VREF0)                             | P0.0                                | REF0CN, P0SKIP,<br>PnMDIN       |

| Ground Reference (AGND)                               | P0.1                                | REF0CN, P0SKIP                  |

| External Oscillator in Crystal Mode (XTAL1)           | P0.2                                | OSCXCN, POSKIP,<br>POMDIN       |

| External Oscillator in RC, C, or Crystal Mode (XTAL2) | P0.3                                | OSCXCN, POSKIP,<br>POMDIN       |

Table 28.1. Port I/O Assignment for Analog Functions

## SFR Definition 28.15. P1SKIP: Port 1 Skip

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-------------|---|---|---|---|---|---|

| Name  |   | P1SKIP[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W         |   |   |   |   |   |   |

| Reset | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xD5; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                                                                                                                              |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1SKIP[7:0] | Port 1 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                     |

|     |             | These bits select Port 1 pins to be skipped by the Crossbar Decoder. Port pins<br>used for analog, special functions or GPIO should be skipped by the Crossbar.<br>0: Corresponding P1.n pin is not skipped by the Crossbar.<br>1: Corresponding P1.n pin is skipped by the Crossbar. |

## SFR Definition 28.16. P1DRV: Port 1 Drive Strength

| Bit   | 7   | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-----------------|---|---|---|---|---|---|

| Name  |     | P1DRV[7:0]      |   |   |   |   |   |   |

| Туре  | R/W |                 |   |   |   |   |   |   |

| Reset | 0   | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

#### SFR Address = 0xFA; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |

## SFR Definition 30.4. SMB0ADM: SMBus Slave Address Mask

| Bit   | 7         | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|-----|---|---|---|---|---|---|

| Name  | SLVM[6:0] |     |   |   |   |   |   |   |

| Туре  |           | R/W |   |   |   |   |   |   |

| Reset | 1         | 1   | 1 | 1 | 1 | 1 | 1 | 0 |

#### SFR Address = 0xBB; SFR Page = F

| Bit | Name      | Function                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM[6:0] | SMBus Slave Address Mask.                                                                                                                                                                                                                                                          |

|     |           | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM[6:0] enables comparisons with the corresponding bit in SLV[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                       |

|     |           | <ul><li>Enables hardware acknowledgement of slave address and received data bytes.</li><li>0: Firmware must manually acknowledge all incoming address and data bytes.</li><li>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.</li></ul>                |

### 32.2. Operational Modes

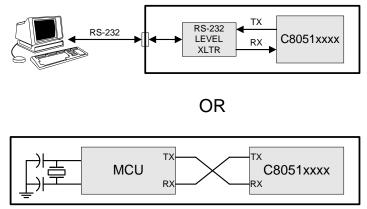

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown in Figure 32.3.

Figure 32.3. UART Interconnect Diagram

#### 32.2.1. 8-Bit UART

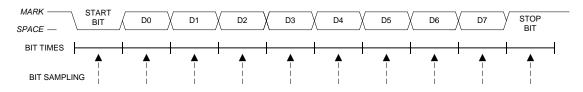

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 32.4. 8-Bit UART Timing Diagram

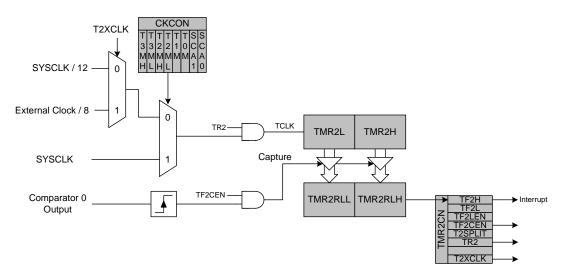

#### 33.2.3. Comparator 0 Capture Mode

The capture mode in Timer 2 allows Comparator 0 rising edges to be captured with the timer clocking from the system clock or the system clock divided by 12. Timer 2 capture mode is enabled by setting TF2CEN to 1 and T2SPLIT to 0.

When capture mode is enabled, a capture event will be generated on every Comparator 0 rising edge. When the capture event occurs, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set (triggering an interrupt if Timer 2 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 0 period can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading.

This mode allows software to determine the time between consecutive Comparator 0 rising edges, which can be used for detecting changes in the capacitance of a capacitive switch, or measuring the frequency of a low-level analog signal.

Figure 33.6. Timer 2 Capture Mode Block Diagram

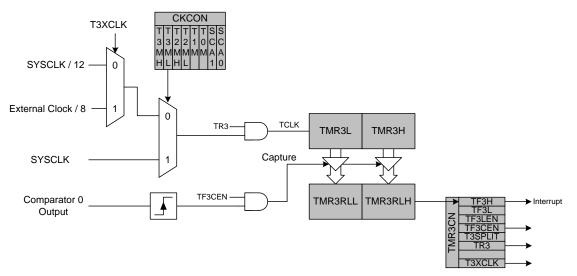

#### 33.3.3. Comparator 0 Capture Mode

The capture mode in Timer 3 allows Comparator 0 rising edges to be captured with the timer clocking from the system clock or the system clock divided by 12. Timer 3 capture mode is enabled by setting TF3CEN to 1 and T3SPLIT to 0.

When capture mode is enabled, a capture event will be generated on every Comparator 0 rising edge. When the capture event occurs, the contents of Timer 3 (TMR3H:TMR3L) are loaded into the Timer 3 reload registers (TMR3RLH:TMR3RLL) and the TF3H flag is set (triggering an interrupt if Timer 3 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 0 period can be determined with respect to the Timer 3 clock. The Timer 3 clock should be much faster than the capture clock to achieve an accurate reading.

This mode allows software to determine the time between consecutive Comparator 0 rising edges, which can be used for detecting changes in the capacitance of a capacitive switch, or measuring the frequency of a low-level analog signal.

Figure 33.9. Timer 3 Capture Mode Block Diagram

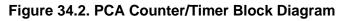

## 34.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2–CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 34.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2                                                                                 | CPS1 | CPS0 | Timebase                                                              |

|--------------------------------------------------------------------------------------|------|------|-----------------------------------------------------------------------|

| 0                                                                                    | 0    | 0    | System clock divided by 12                                            |

| 0                                                                                    | 0    | 1    | System clock divided by 4                                             |

| 0                                                                                    | 1    | 0    | Timer 0 overflow                                                      |

| 0                                                                                    | 1    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |

| 1                                                                                    | 0    | 0    | System clock                                                          |

| 1                                                                                    | 0    | 1    | External oscillator source divided by 8                               |

| 1                                                                                    | 1    | х    | Reserved                                                              |

| Note: External oscillator source divided by 8 is synchronized with the system clock. |      |      |                                                                       |

### Table 34.1. PCA Timebase Input Options

IDLE PCA0MD PCA0CN D L To SFR Bus PCA0I read Snapshot Register SYSCLK/12 000 SYSCLK/4 001 Timer 0 Overflow 010 Overflow PCA0L PCA0H To PCA Interrupt System ECI 011 SYSCLK CF 100 External Clock/8 101 To PCA Modules

#### 34.3.6. 16-Bit Pulse Width Modulator Mode

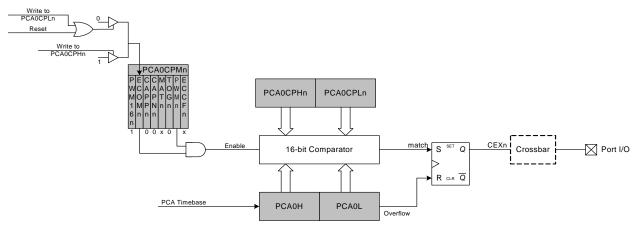

A PCA module may also be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8/9/10/11-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 34.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(65536 - PCA0CPn)}{65536}$$

Equation 34.4. 16-Bit PWM Duty Cycle

Using Equation 34.4, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 34.10. PCA 16-Bit PWM Mode