# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                           |

| Number of I/O              | 39                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | 32 x 8                                                          |

| RAM Size                   | 512 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                     |

| Data Converters            | A/D 12x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f712-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

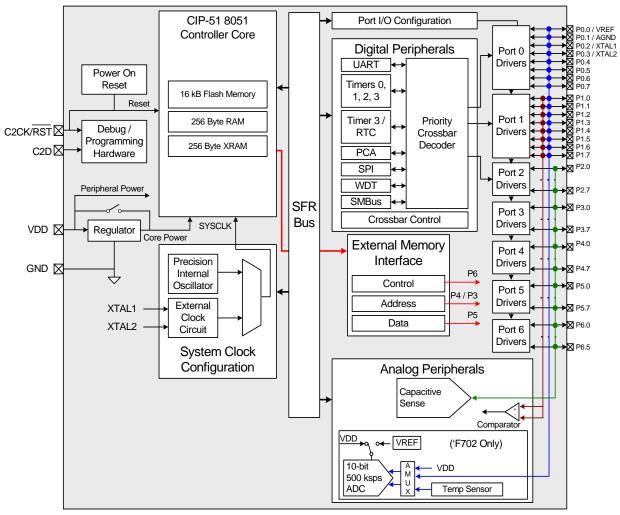

Figure 1.2. C8051F702/3 Block Diagram

## 3. Pin Definitions

| Name            | TQFP64           | TQFP48<br>QFN48  | QFN32  | QFN24 | Туре             | Description                                                                     |

|-----------------|------------------|------------------|--------|-------|------------------|---------------------------------------------------------------------------------|

| V <sub>DD</sub> | 8, 24,<br>41, 57 | 8, 20, 44        | 27     | 21    |                  | Power Supply Voltage.                                                           |

| GND             | 9, 25,<br>40, 56 | 9, 21,<br>30, 43 | Center | 20    |                  | Ground.                                                                         |

| RST /           | 58               | 45               | 28     | 22    | D I/O            | Device Reset. Open-drain output of internal POR or V <sub>DD</sub> monitor.     |

| C2CK            |                  |                  |        |       | D I/O            | Clock signal for the C2 Debug Interface.                                        |

| C2D             | 59               | 46               | 29     | 23    | D I/O            | Bi-directional data signal for the C2 Debug Interface.                          |

| P0.0 /          | 55               | 42               | _      | —     | D I/O or<br>A In | Port 0.0.<br>ADC0 Input.                                                        |

| VREF            |                  |                  |        |       | A In             | External VREF input.                                                            |

| P0.1/           | 54               | 41               | —      | —     | D I/O or<br>A In | Port 0.1.<br>ADC0 Input.                                                        |

| AGND            |                  |                  |        |       |                  | External AGND input.                                                            |

| P0.2 /          | 53               | 40               | _      | —     | D I/O or<br>A In | Port 0.2.<br>ADC0 Input.                                                        |

| XTAL1           |                  |                  |        |       | A In             | External Clock Pin. This pin can be used for crystal clock mode.                |

| P0.3 /          | 52               | 39               | 26     | —     | D I/O or<br>A In | Port 0.3.<br>ADC0 Input.                                                        |

| XTAL2           |                  |                  |        |       | A I/O or<br>D In | External Clock Pin. This pin can be used for RC, crystal, and CMOS clock modes. |

| P0.4            | 51               | 38               | 25     | 19    | D I/O or<br>A In | Port 0.4.<br>ADC0 Input.                                                        |

| P0.5            | 50               | 37               | 24     | 18    | D I/O or<br>A In | Port 0.5.<br>ADC0 Input.                                                        |

| P0.6            | 49               | 36               | _      | —     | D I/O or<br>A In | Port 0.6.<br>ADC0 Input.                                                        |

#### Table 3.1. Pin Definitions for the C8051F70x/71x

## SFR Definition 13.1. REG0CN: Voltage Regulator Control

| Bit   | 7      | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------|--------|-----|-----|-----|-----|-----|-----|

| Name  | STOPCF | BYPASS |     |     |     |     |     |     |

| Туре  | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0   | 0   | 0   | 0   |

### SFR Address = 0xB9; SFR Page = F

| Bit | Name     | Function                                                                                                                                                                                                                                                                                |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STOPCF   | Stop Mode Configuration.                                                                                                                                                                                                                                                                |

|     |          | This bit configures the regulator's behavior when the device enters STOP mode.<br>0: Regulator is still active in STOP mode. Any enabled reset source will reset the<br>device.<br>1: Regulator is shut down in STOP mode. Only the RST pin or power cycle can reset                    |

|     |          | the device.                                                                                                                                                                                                                                                                             |

| 6   | BYPASS   | Bypass Internal Regulator.                                                                                                                                                                                                                                                              |

|     |          | This bit places the regulator in bypass mode, allowing the core to run directly from the $V_{DD}$ supply pin.                                                                                                                                                                           |

|     |          | 0: Normal Mode—Regulator is on and regulates V <sub>DD</sub> down to the core voltage.                                                                                                                                                                                                  |

|     |          | 1: Bypass Mode—Regulator is in bypass mode, and the microcontroller core operates directly from the V <sub>DD</sub> supply voltage.                                                                                                                                                     |

|     |          | IMPORTANT: Bypass mode is for use with an external regulator as the supply voltage only. Never place the regulator in bypass mode when the $V_{DD}$ supply voltage is greater than the specifications given in Table 9.1 on page 47. Doing so may cause permanent damage to the device. |

| 5:0 | Reserved | Reserved. Must Write 000000b.                                                                                                                                                                                                                                                           |

#### SFR Definition 15.5. CS0SS: Capacitive Sense Auto-Scan Start Channel

| Bit   | 7 | 6 | 5 | 4          | 3 | 2 | 1 | 0 |  |

|-------|---|---|---|------------|---|---|---|---|--|

| Name  |   |   |   | CS0SS[5:0] |   |   |   |   |  |

| Туре  | R | R |   | R/W        |   |   |   |   |  |

| Reset | 0 | 0 | 0 | 0          | 0 | 0 | 0 | 0 |  |

#### SFR Address = 0x92; SFR Page = F

| Bit | Name       | Description                                                                                                                                                                                                                                                                                           |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b; Write = Don't care                                                                                                                                                                                                                                                                        |

| 5:0 | CS0SS[5:0] | Starting Channel for Auto-Scan.                                                                                                                                                                                                                                                                       |

|     |            | Sets the first CS0 channel to be selected by the mux for Capacitive Sense conver-<br>sion when auto-scan is enabled and active. All channels detailed in CS0MX SFR<br>Definition 15.12 are possible choices for this register.<br>When auto-scan is enabled, a write to CS0SS will also update CS0MX. |

## SFR Definition 15.6. CS0SE: Capacitive Sense Auto-Scan End Channel

| Bit   | 7 | 6 | 5 | 4          | 3 | 2 | 1 | 0 |  |

|-------|---|---|---|------------|---|---|---|---|--|

| Name  |   |   |   | CS0SE[5:0] |   |   |   |   |  |

| Туре  | R | R |   | R/W        |   |   |   |   |  |

| Reset | 0 | 0 | 0 | 0          | 0 | 0 | 0 | 0 |  |

#### SFR Address = 0x93; SFR Page = F

| Bit | Name       | Description                                                                                                                                                                                                           |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 000b; Write = Don't care                                                                                                                                                                                       |

| 5:0 | CS0SE[5:0] | Ending Channel for Auto-Scan.                                                                                                                                                                                         |

|     |            | Sets the last CS0 channel to be selected by the mux for Capacitive Sense conversion when auto-scan is enabled and active. All channels detailed in CS0MX SFR Definition 15.12 are possible choices for this register. |

## SFR Definition 18.2. EMI0CF: External Memory Configuration

| Bit   | 7 | 6 | 5 | 4    | 3   | 2             | 1         | 0 |  |

|-------|---|---|---|------|-----|---------------|-----------|---|--|

| Name  |   |   |   | EMD2 | EMD | <b>[</b> 1:0] | EALE[1:0] |   |  |

| Туре  | R |   |   | R/W  |     |               |           |   |  |

| Reset | 0 | 0 | 0 | 0    | 0   | 0             | 1         | 1 |  |

#### SFR Address = 0xC7; SFR Page = F

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused    | Read = 000b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | EMD2      | EMIF Multiplex Mode Select Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |           | 0: EMIF operates in multiplexed address/data mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           | 1: EMIF operates in non-multiplexed mode (separate address and data pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3:2 | EMD[1:0]  | EMIF Operating Mode Select Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |           | 00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses alias to<br>on-chip memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |           | <ul> <li>01: Split Mode without Bank Select: Accesses below the 256 B boundary are directed on-chip. Accesses above the 256 B boundary are directed off-chip. 8-bit off-chip MOVX operations use current contents of the Address high port latches to resolve the upper address byte. To access off chip space, EMI0CN must be set to a page that is not contained in the on-chip address space.</li> <li>10: Split Mode with Bank Select: Accesses below the 256 B boundary are directed on-chip. Accesses above the 256 B boundary are directed off-chip. 8-bit off-chip MOVX operations uses the contents of EMI0CN to determine the high-byte of the address.</li> <li>11: External Only: MOVX accesses off-chip XRAM only. On-chip XRAM is not visible to the CPU.</li> </ul> |

| 1:0 | EALE[1:0] | ALE Pulse-Width Select Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |           | These bits only have an effect when $EMD2 = 0$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |           | 00: ALE high and ALE low pulse width = 1 SYSCLK cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |           | 01: ALE high and ALE low pulse width = 2 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |           | 10: ALE high and ALE low pulse width = 3 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |           | 11: ALE high and ALE low pulse width = 4 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

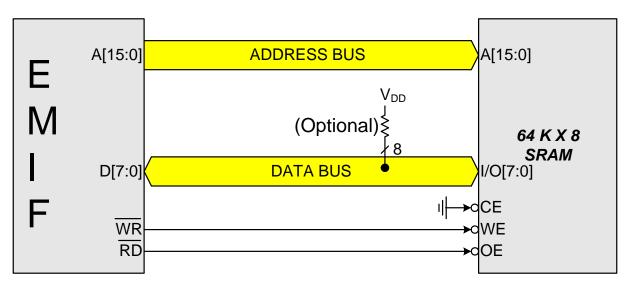

#### 18.4.2. Non-multiplexed Configuration

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Nonmultiplexed Configuration is shown in Figure 18.2. See Section "18.6.1. Non-Multiplexed Mode" on page 120 for more information about Non-multiplexed operation.

Figure 18.2. Non-multiplexed Configuration Example

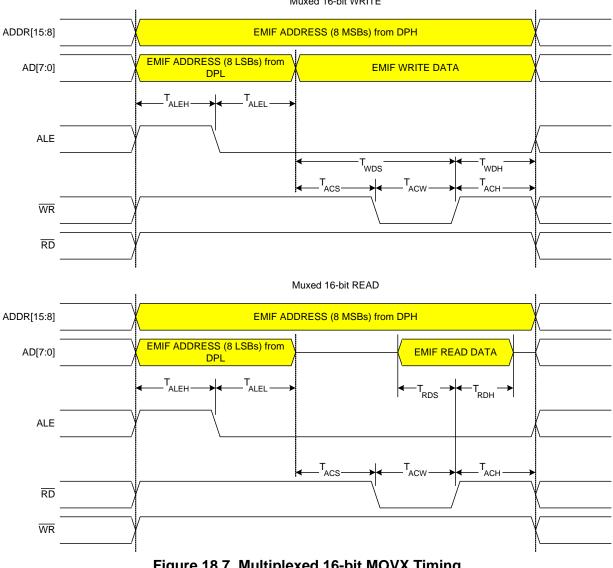

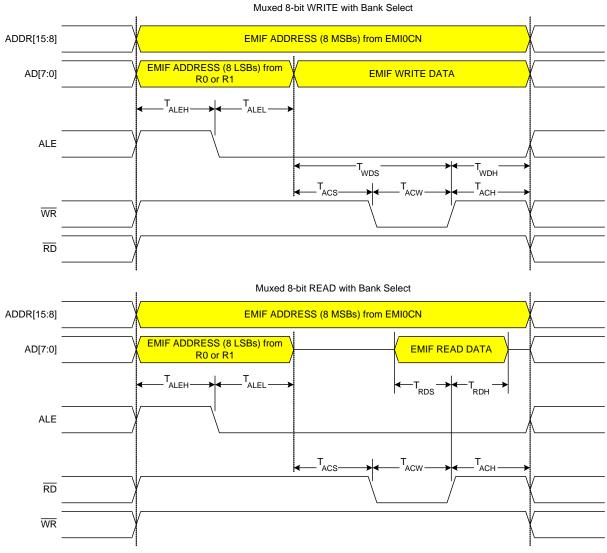

#### 18.6.2. Multiplexed Mode 18.6.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011

Muxed 16-bit WRITE

Figure 18.9. Multiplexed 8-Bit MOVX with Bank Select Timing

## SFR Definition 21.5. EIP1: Extended Interrupt Priority 1

| Bit   | 7   | 6        | 5    | 4     | 3     | 2      | 1    | 0     |

|-------|-----|----------|------|-------|-------|--------|------|-------|

| Name  | PT3 | Reserved | PCP0 | PPCA0 | PADC0 | PWADC0 | PMAT | PSMB0 |

| Туре  | R/W | R/W      | R/W  | R/W   | R/W   | R/W    | R/W  | R/W   |

| Reset | 0   | 0        | 0    | 0     | 0     | 0      | 0    | 0     |

#### SFR Address = 0xCE; SFR Page = F

| Bit | Name     | Function                                                                     |

|-----|----------|------------------------------------------------------------------------------|

| 7   | PT3      | Timer 3 Interrupt Priority Control.                                          |

|     |          | This bit sets the priority of the Timer 3 interrupt.                         |

|     |          | 0: Timer 3 interrupt set to low priority level.                              |

|     |          | 1: Timer 3 interrupt set to high priority level.                             |

| 6   | Reserved | Must write 0b.                                                               |

| 5   | PCP0     | Comparator0 (CP0) Interrupt Priority Control.                                |

|     |          | This bit sets the priority of the CP0 rising edge or falling edge interrupt. |

|     |          | 0: CP0 interrupt set to low priority level.                                  |

|     |          | 1: CP0 interrupt set to high priority level.                                 |

| 4   | PPCA0    | Programmable Counter Array (PCA0) Interrupt Priority Control.                |

|     |          | This bit sets the priority of the PCA0 interrupt.                            |

|     |          | 0: PCA0 interrupt set to low priority level.                                 |

|     |          | 1: PCA0 interrupt set to high priority level.                                |

| 3   | PADC0    | ADC0 Conversion Complete Interrupt Priority Control.                         |

|     |          | This bit sets the priority of the ADC0 Conversion Complete interrupt.        |

|     |          | 0: ADC0 Conversion Complete interrupt set to low priority level.             |

|     |          | 1: ADC0 Conversion Complete interrupt set to high priority level.            |

| 2   | PWADC0   | ADC0 Window Comparator Interrupt Priority Control.                           |

|     |          | This bit sets the priority of the ADC0 Window interrupt.                     |

|     |          | 0: ADC0 Window interrupt set to low priority level.                          |

|     |          | 1: ADC0 Window interrupt set to high priority level.                         |

| 1   | PMAT     | Port Match Interrupt Priority Control.                                       |

|     |          | This bit sets the priority of the Port Match Event interrupt.                |

|     |          | 0: Port Match interrupt set to low priority level.                           |

|     |          | 1: Port Match interrupt set to high priority level.                          |

| 0   | PSMB0    | SMBus (SMB0) Interrupt Priority Control.                                     |

|     |          | This bit sets the priority of the SMB0 interrupt.                            |

|     |          | 0: SMB0 interrupt set to low priority level.                                 |

|     |          | 1: SMB0 interrupt set to high priority level.                                |

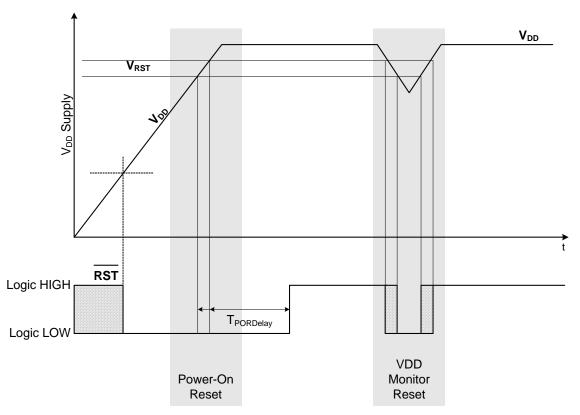

### 25.1. Power-On Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. A delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 25.2. plots the power-on and V<sub>DD</sub> monitor reset timing. The maximum V<sub>DD</sub> ramp time is 1 ms; slower ramp times may cause the device to be released from reset before V<sub>DD</sub> reaches the V<sub>RST</sub> level. For ramp times less than 1 ms, the power-on reset delay (T<sub>PORDelay</sub>) is typically less than 10 ms.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is enabled following a power-on reset.

Figure 25.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

## SFR Definition 27.4. OSCXCN: External Oscillator Control

| Bit   | 7      | 6 | 5         | 4  | 3 | 2         | 0 |  |  |

|-------|--------|---|-----------|----|---|-----------|---|--|--|

| Name  | XTLVLD | × | OSCMD[2:0 | )] |   | XFCN[2:0] |   |  |  |

| Туре  | R      |   | R/W       |    | R | R/W       |   |  |  |

| Reset | 0      | 0 | 0         | 0  | 0 | 0         | 0 |  |  |

#### SFR Address = 0xB5; SFR Page = F

| Bit | Name        |         |                                                        | Function                                  |                 |  |  |  |  |  |  |  |  |

|-----|-------------|---------|--------------------------------------------------------|-------------------------------------------|-----------------|--|--|--|--|--|--|--|--|

| 7   | XTLVLD      | Crystal | Oscillator Valid Flag.                                 |                                           |                 |  |  |  |  |  |  |  |  |

|     |             | (Read o | nly when XOSCMD = 11                                   | x.)                                       |                 |  |  |  |  |  |  |  |  |

|     |             | -       | al Oscillator is unused or                             | •                                         |                 |  |  |  |  |  |  |  |  |

|     |             |         | al Oscillator is running ar                            |                                           |                 |  |  |  |  |  |  |  |  |

| 6:4 | XOSCMD[2:0] | Externa | I Oscillator Mode Selec                                | ct.                                       |                 |  |  |  |  |  |  |  |  |

|     |             |         | ernal Oscillator circuit of                            |                                           |                 |  |  |  |  |  |  |  |  |

|     |             |         | ternal CMOS Clock Mode                                 |                                           |                 |  |  |  |  |  |  |  |  |

|     |             |         | External CMOS Clock Mode with divide by 2 stage.       |                                           |                 |  |  |  |  |  |  |  |  |

|     |             |         | RC Oscillator Mode.                                    |                                           |                 |  |  |  |  |  |  |  |  |

|     |             |         | Capacitor Oscillator Mode.<br>Crystal Oscillator Mode. |                                           |                 |  |  |  |  |  |  |  |  |

|     |             | -       | I: Crystal Oscillator Mode with divide by 2 stage.     |                                           |                 |  |  |  |  |  |  |  |  |

| 3   | Unused      | -       | ead = 0; Write = Don't Care                            |                                           |                 |  |  |  |  |  |  |  |  |

| -   |             |         |                                                        | <u> </u>                                  |                 |  |  |  |  |  |  |  |  |

| 2:0 | XFCN[2:0]   |         | I Oscillator Frequency                                 |                                           |                 |  |  |  |  |  |  |  |  |

|     |             |         | U                                                      | uency for Crystal or RC r                 | node.           |  |  |  |  |  |  |  |  |

|     |             |         | ording to the desired K F                              |                                           |                 |  |  |  |  |  |  |  |  |

|     |             | XFCN    | Crystal Mode                                           | RC Mode                                   | C Mode          |  |  |  |  |  |  |  |  |

|     |             | 000     | f ≤ 32 kHz                                             | f ≤ 25 kHz                                | K Factor = 0.87 |  |  |  |  |  |  |  |  |

|     |             | 001     | 32 kHz < f ≤ 84 kHz                                    | 25 kHz < f ≤ 50 kHz                       | K Factor = 2.6  |  |  |  |  |  |  |  |  |

|     |             | 010     | 84 kHz < f ≤ 225 kHz                                   | 50 kHz < f ≤ 100 kHz                      | K Factor = 7.7  |  |  |  |  |  |  |  |  |

|     |             | 011     | 225 kHz < f ≤ 590 kHz                                  | 100 kHz < f ≤ 200 kHz                     | K Factor = 22   |  |  |  |  |  |  |  |  |

|     |             | 100     | 590 kHz $<$ f $\leq$ 1.5 MHz                           | 200 kHz $<$ f $\leq$ 400 kHz              | K Factor = 65   |  |  |  |  |  |  |  |  |

|     |             | 101     | $1.5 \text{ MHz} < f \le 4 \text{ MHz}$                | 400 kHz < f ≤ 800 kHz                     | K Factor = 180  |  |  |  |  |  |  |  |  |

|     |             | 110     | $4 \text{ MHz} < f \le 10 \text{ MHz}$                 | 800 kHz $<$ f $\leq$ 1.6 MHz              | K Factor = 664  |  |  |  |  |  |  |  |  |

|     |             | 111     | 10 MHz < f ≤ 30 MHz                                    | $1.6 \text{ MHz} < f \le 3.2 \text{ MHz}$ | K Factor = 1590 |  |  |  |  |  |  |  |  |

## SFR Definition 28.19. P2MDOUT: Port 2 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|--------------|---|---|---|---|---|---|---|--|--|--|--|

| Name  | P2MDOUT[7:0] |   |   |   |   |   |   |   |  |  |  |  |

| Туре  | R/W          |   |   |   |   |   |   |   |  |  |  |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

#### SFR Address = 0xA6; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDOUT[7:0] | Output Configuration Bits for P2.7–P2.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P2MDIN is logic 0.<br>0: Corresponding P2.n Output is open-drain.<br>1: Corresponding P2.n Output is push-pull. |

#### SFR Definition 28.20. P2SKIP: Port 2 Skip

| Bit   | 7           | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|-------|-------------|-----------------|---|---|---|---|---|---|--|--|--|--|--|

| Name  | P2SKIP[7:0] |                 |   |   |   |   |   |   |  |  |  |  |  |

| Туре  |             | R/W             |   |   |   |   |   |   |  |  |  |  |  |

| Reset | 0           | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |  |  |

SFR Address = 0xD6; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2SKIP[3:0] | Port 2 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 2 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P2.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P2.n pin is skipped by the Crossbar.</li> </ul> |

### 29.3. Preparing for a CRC Calculation

To prepare CRC0 for a CRC calculation, software should select the desired polynomial and set the initial value of the result. Two polynomials are available: 0x1021 (16-bit) and 0x04C11DB7 (32-bit). The CRC0 result may be initialized to one of two values: 0x00000000 or 0xFFFFFFFF. The following steps can be used to initialize CRC0.

- 1. Select a polynomial (Set CRC0SEL to 0 for 32-bit or 1 for 16-bit).

- 2. Select the initial result value (Set CRC0VAL to 0 for 0x0000000 or 1 for 0xFFFFFFF).

- 3. Set the result to its initial value (Write 1 to CRC0INIT).

#### 29.4. Performing a CRC Calculation

Once CRC0 is initialized, the input data stream is sequentially written to CRC0IN, one byte at a time. The CRC0 result is automatically updated after each byte is written. The CRC engine may also be configured to automatically perform a CRC on one or more Flash sectors. The following steps can be used to automatically perform a CRC on Flash memory.

- 1. Prepare CRC0 for a CRC calculation as shown above.

- 2. Write the index of the starting page to CRC0AUTO.

- 3. Set the AUTOEN bit in CRC0AUTO.

- 4. Write the number of Flash sectors to perform in the CRC calculation to CRC0CNT.

**Note:** Each Flash sector is 512 bytes.

- 5. Write any value to CRC0CN (or OR its contents with 0x00) to initiate the CRC calculation. The CPU will not execute code any additional code until the CRC operation completes.

- 6. Clear the AUTOEN bit in CRC0AUTO.

- 7. Read the CRC result using the procedure below.

#### 29.5. Accessing the CRC0 Result

The internal CRC0 result is 32-bits (CRC0SEL = 0b) or 16-bits (CRC0SEL = 1b). The CRC0PNT bits select the byte that is targeted by read and write operations on CRC0DAT and increment after each read or write. The calculation result will remain in the internal CR0 result register until it is set, overwritten, or additional data is written to CRC0IN.

## SFR Definition 29.1. CRC0CN: CRC0 Control

| Bit   | 7   | 6   | 5   | 4       | 3        | 2       | 1            | 0 |  |  |

|-------|-----|-----|-----|---------|----------|---------|--------------|---|--|--|

| Name  |     |     |     | CRC0SEL | CRC0INIT | CRC0VAL | CRC0PNT[1:0] |   |  |  |

| Туре  | R/W | R/W | R/W | R/W     | R/W      | R/W     | R/W          |   |  |  |

| Reset | 0   | 0   | 0   | 0       | 0        | 0       | 0            | 0 |  |  |

SFR Address = 0x91; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                                                                                 |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Unused       | Read = 000b; Write = Don't Care.                                                                                                                                                                                                         |

| 4   | CRC0SEL      | CRC0 Polynomial Select Bit.                                                                                                                                                                                                              |

|     |              | This bit selects the CRC0 polynomial and result length (32-bit or 16-bit).<br>0: CRC0 uses the 32-bit polynomial 0x04C11DB7 for calculating the CRC result.<br>1: CRC0 uses the 16-bit polynomial 0x1021 for calculating the CRC result. |

| 3   | CRC0INIT     | CRC0 Result Initialization Bit.                                                                                                                                                                                                          |

|     |              | Writing a 1 to this bit initializes the entire CRC result based on CRC0VAL.                                                                                                                                                              |

| 2   | CRC0VAL      | CRC0 Set Value Initialization Bit.                                                                                                                                                                                                       |

|     |              | This bit selects the set value of the CRC result.                                                                                                                                                                                        |

|     |              | 0: CRC result is set to 0x00000000 on write of 1 to CRC0INIT.                                                                                                                                                                            |

|     |              | 1: CRC result is set to 0xFFFFFFF on write of 1 to CRC0INIT.                                                                                                                                                                             |

| 1:0 | CRC0PNT[1:0] | CRC0 Result Pointer.                                                                                                                                                                                                                     |

|     |              | Specifies the byte of the CRC result to be read/written on the next access to CRC0DAT. The value of these bits will auto-increment upon each read or write. For CRC0SEL = 0:                                                             |

|     |              | 00: CRC0DAT accesses bits 7–0 of the 32-bit CRC result.                                                                                                                                                                                  |

|     |              | 01: CRC0DAT accesses bits 15–8 of the 32-bit CRC result.                                                                                                                                                                                 |

|     |              | 10: CRC0DAT accesses bits 23–16 of the 32-bit CRC result.                                                                                                                                                                                |

|     |              | 11: CRC0DAT accesses bits 31–24 of the 32-bit CRC result.<br>For CRC0SEL = 1:                                                                                                                                                            |

|     |              | 00: CRC0DAT accesses bits 7–0 of the 16-bit CRC result.                                                                                                                                                                                  |

|     |              | 01: CRC0DAT accesses bits 15–8 of the 16-bit CRC result.                                                                                                                                                                                 |

|     |              | 10: CRC0DAT accesses bits 7–0 of the 16-bit CRC result.                                                                                                                                                                                  |

|     |              | 11: CRC0DAT accesses bits 15–8 of the 16-bit CRC result.                                                                                                                                                                                 |

Table 30.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (Continued)

|                 | Valu             | es I | Rea | d                           |                                  |                             |     | lues<br>Vrit |                      | Status<br>Expected |  |

|-----------------|------------------|------|-----|-----------------------------|----------------------------------|-----------------------------|-----|--------------|----------------------|--------------------|--|

| Mode            | Status<br>Vector |      |     | Current SMbus State         | Typical Response Options         | STA                         | STO | ACK          | Next St<br>Vector Ex |                    |  |

| uo              | 0010             | 0    | 1   | х                           | Lost arbitration while attempt-  | Abort failed transfer.      | 0   | 0            | Х                    | —                  |  |

| diti            | 0010             | 0    | 1   |                             | ing a repeated START.            | Reschedule failed transfer. | 1   | 0            | Х                    | 1110               |  |

| Con             | 0001             | 0    | 1   | x                           | Lost arbitration due to a        | Abort failed transfer.      | 0   | 0            | Х                    | —                  |  |

| Error Condition | 0001             | 0    | 1   | ^                           | detected STOP.                   | Reschedule failed transfer. | 1   | 0            | Х                    | 1110               |  |

|                 | 0000             | 1    | 1   | x                           | Lost arbitration while transmit- | Abort failed transfer.      | 0   | 0            | 0                    | —                  |  |

| Bus             | 0000             |      |     | ting a data byte as master. |                                  | Reschedule failed transfer. | 1   | 0            | 0                    | 1110               |  |

### Table 30.6. SMBus Status Decoding: Hardware ACK Enabled (EHACK = 1)

|                    | v               | alu    | es F  | Rea     | d         |                                                    |                                                                                                                        |     | lues<br>Vrit |      | Status<br>Expected           |

|--------------------|-----------------|--------|-------|---------|-----------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------|------|------------------------------|

| Mode               | Status          | Vector | ACKRQ | ARBLOST | АСК       | Current SMbus State                                | Typical Response Options                                                                                               | STA | STO          | ACK  | Next Status<br>Vector Expect |

|                    | 11 <sup>.</sup> | 10     | 0     | 0       | х         | A master START was gener-<br>ated.                 | Load slave address + R/W into SMB0DAT.                                                                                 | 0   | 0            | Х    | 1100                         |

|                    |                 |        | _     | _       | _         | A master data or address byte                      | Set STA to restart transfer.                                                                                           | 1   | 0            | Х    | 1110                         |

| r                  |                 |        | 0     | 0       | 0         | was transmitted; NACK received.                    | Abort transfer.                                                                                                        | 0   | 1            | Х    | —                            |

| smitte             |                 |        |       |         |           |                                                    | Load next data byte into<br>SMB0DAT.                                                                                   | 0   | 0            | Х    | 1100                         |

| Tan                |                 |        |       |         |           |                                                    | End transfer with STOP.                                                                                                | 0   | 1            | Х    | —                            |

| Master Transmitter | 11(             | 00     | 0     | 0       | 1         | A master data or address byte was transmitted; ACK | End transfer with STOP and start another transfer.                                                                     | 1   | 1            | Х    | —                            |

| Ë                  | Ma              | •      | Ū     |         | received. | Send repeated START.                               | 1                                                                                                                      | 0   | Х            | 1110 |                              |

|                    |                 |        |       |         |           |                                                    | Switch to Master Receiver Mode<br>(clear SI without writing new data<br>to SMB0DAT). Set ACK for initial<br>data byte. | 0   | 0            | 1    | 1000                         |

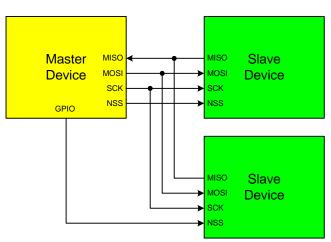

Figure 31.4. 4-Wire Single Master Mode and Slave Mode Connection Diagram

## 31.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted through the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. The NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 31.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 31.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

## SFR Definition 33.11. TMR2L: Timer 2 Low Byte

| Bit                              | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|----------------------------------|-----------------|---|---|---|---|---|---|---|--|--|--|--|--|

| Name                             | TMR2L[7:0]      |   |   |   |   |   |   |   |  |  |  |  |  |

| Туре                             | R/W             |   |   |   |   |   |   |   |  |  |  |  |  |

| Reset                            | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |  |  |  |  |  |

| SFR Address = 0xCC; SFR Page = 0 |                 |   |   |   |   |   |   |   |  |  |  |  |  |

Bit

Name

Function

7:0

TMR2L[7:0]

Timer 2 Low Byte. In 16-bit mode, the TMR2L register contains the low byte of the 16-bit Timer 2. In 8bit mode, TMR2L contains the 8-bit low byte timer value.

#### SFR Definition 33.12. TMR2H Timer 2 High Byte

| Bit    | 7                                | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|--------|----------------------------------|---|---|---|---|---|---|---|--|--|--|--|--|

| Name   | TMR2H[7:0]                       |   |   |   |   |   |   |   |  |  |  |  |  |

| Туре   | R/W                              |   |   |   |   |   |   |   |  |  |  |  |  |

| Reset  | 0 0 0 0 0 0 0 0                  |   |   |   |   |   |   |   |  |  |  |  |  |

| SFR Ad | SFR Address = 0xCD; SFR Page = 0 |   |   |   |   |   |   |   |  |  |  |  |  |

| Bit | Name       | Function                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR2H[7:0] | Timer 2 Low Byte.                                                                                                                                   |

|     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8-<br>bit mode, TMR2H contains the 8-bit high byte timer value. |

## SFR Definition 33.13. TMR3CN: Timer 3 Control

| Bit   | 7    | 6    | 5      | 4      | 3       | 2   | 1 | 0      |

|-------|------|------|--------|--------|---------|-----|---|--------|

| Name  | TF3H | TF3L | TF3LEN | TF3CEN | T3SPLIT | TR3 |   | T3XCLK |

| Туре  | R/W  | R/W  | R/W    | R/W    | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0      | 0       | 0   | 0 | 0      |

#### SFR Address = 0x91; SFR Page = 0

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7   | TF3H    | <b>Timer 3 High Byte Overflow Flag.</b><br>Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine. This bit is not automatically cleared by hardware.                                                                                                                                                      |  |  |  |  |

| 6   | TF3L    | <b>Timer 3 Low Byte Overflow Flag.</b><br>Set by hardware when the Timer 3 low byte overflows from 0xFF to 0x00. TF3L will be set when the low byte overflows regardless of the Timer 3 mode. This bit is not automatically cleared by hardware.                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 5   | TF3LEN  | <b>Timer 3 Low Byte Interrupt Enable.</b><br>When set to 1, this bit enables Timer 3 Low Byte interrupts. If Timer 3 interrupts are also enabled, an interrupt will be generated when the low byte of Timer 3 overflows                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 4   | TF3CEN  | Timer 3 Comparator Capture Enable.<br>When set to 1, this bit enables Timer 3 Comparator Capture Mode. If TF3CEN is set,<br>on a rising edge of the Comparator0 output the current 16-bit timer value in<br>TMR3H:TMR3L will be copied to TMR3RLH:TMR3RLL. If Timer 3 interrupts are also<br>enabled, an interrupt will be generated on this event.                                                                                                                                                                                 |  |  |  |  |

| 3   | T3SPLIT | Timer 3 Split Mode Enable.When this bit is set, Timer 3 operates as two 8-bit timers with auto-reload.0: Timer 3 operates in 16-bit auto-reload mode.1: Timer 3 operates as two 8-bit auto-reload timers.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 2   | TR3     | <b>Timer 3 Run Control.</b><br>Timer 3 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR3H only; TMR3L is always enabled in split mode.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 1   | Unused  | Read = 0b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 0   | T3XCLK  | <ul> <li>Timer 3 External Clock Select.</li> <li>This bit selects the external clock source for Timer 3. If Timer 3 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 3 Clock Select bits (T3MH and T3ML in register CKCON) may still be used to select between the external clock and the system clock for either timer.</li> <li>0: System clock divided by 12.</li> <li>1: External clock divided by 8 (synchronized with SYSCLK when not in suspend).</li> </ul> |  |  |  |  |

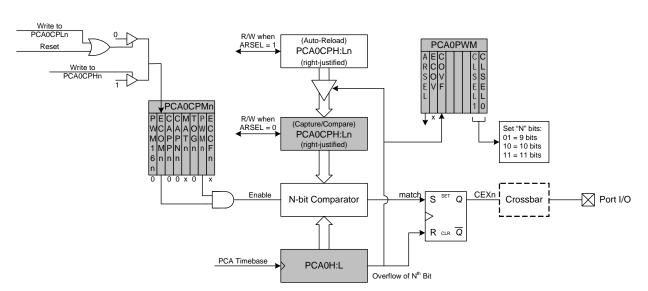

#### 34.3.5.2. 9/10/11-bit Pulse Width Modulator Mode

The duty cycle of the PWM output signal in 9/10/11-bit PWM mode should be varied by writing to an "Auto-Reload" Register, which is dual-mapped into the PCA0CPHn and PCA0CPLn register locations. The data written to define the duty cycle should be right-justified in the registers. The auto-reload registers are accessed (read or written) when the bit ARSEL in PCA0PWM is set to 1. The capture/compare registers are accessed when ARSEL is set to 0.

When the least-significant N bits of the PCA0 counter match the value in the associated module's capture/compare register (PCA0CPn), the output on CEXn is asserted high. When the counter overflows from the Nth bit, CEXn is asserted low (see Figure 34.9). Upon an overflow from the Nth bit, the COVF flag is set, and the value stored in the module's auto-reload register is loaded into the capture/compare register. The value of N is determined by the CLSEL bits in register PCA0PWM.

The 9, 10 or 11-bit PWM mode is selected by setting the ECOMn and PWMn bits in the PCA0CPMn register, and setting the CLSEL bits in register PCA0PWM to the desired cycle length (other than 8-bits). If the MATn bit is set to 1, the CCFn flag for the module will be set each time a comparator match (rising edge) occurs. The COVF flag in PCA0PWM can be used to detect the overflow (falling edge), which will occur every 512 (9-bit), 1024 (10-bit) or 2048 (11-bit) PCA clock cycles. The duty cycle for 9/10/11-Bit PWM Mode is given in Equation 34.2, where N is the number of bits in the PWM cycle.

**Important Note About PCA0CPHn and PCA0CPLn Registers**: When writing a 16-bit value to the PCA0CPn registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(2^N - PCA0CPn)}{2^N}$$

Equation 34.3. 9, 10, and 11-Bit PWM Duty Cycle

A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 34.9. PCA 9, 10 and 11-Bit PWM Mode Diagram

## SFR Definition 34.2. PCA0MD: PCA Mode

| Bit   | 7    | 6 | 5 | 4 | 3    | 2    | 1    | 0   |

|-------|------|---|---|---|------|------|------|-----|

| Name  | CIDL |   |   |   | CPS2 | CPS1 | CPS0 | ECF |

| Туре  | R/W  | R | R | R | R/W  | R/W  | R/W  | R/W |

| Reset | 0    | 0 | 0 | 0 | 0    | 0    | 0    | 0   |

#### SFR Address = 0xED; SFR Page = F

| Bit | Name     | Function                                                                                        |

|-----|----------|-------------------------------------------------------------------------------------------------|

| 7   | CIDL     | PCA Counter/Timer Idle Control.                                                                 |

|     |          | Specifies PCA behavior when CPU is in Idle Mode.                                                |

|     |          | 0: PCA continues to function normally while the system controller is in Idle Mode.              |

|     |          | 1: PCA operation is suspended while the system controller is in Idle Mode.                      |

| 6:4 | Unused   | Read = 000b, Write = don't care.                                                                |

| 3:1 | CPS[2:0] | PCA Counter/Timer Pulse Select.                                                                 |

|     |          | These bits select the timebase source for the PCA counter                                       |

|     |          | 000: System clock divided by 12                                                                 |

|     |          | 001: System clock divided by 4                                                                  |

|     |          | 010: Timer 0 overflow                                                                           |

|     |          | 011: High-to-low transitions on ECI (max rate = system clock divided by 4)<br>100: System clock |

|     |          | 101: External clock divided by 8 (synchronized with the system clock)                           |

|     |          | 110-111: Reserved                                                                               |

| 0   | ECF      | PCA Counter/Timer Overflow Interrupt Enable.                                                    |

|     |          | This bit sets the masking of the PCA Counter/Timer Overflow (CF) interrupt.                     |

|     |          | 0: Disable the CF interrupt.                                                                    |

|     |          | 1: Enable a PCA Counter/Timer Overflow interrupt request when CF (PCA0CN.7) is set.             |