# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, WDT                                       |

| Number of I/O              | 39                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | 32 x 8                                                         |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 48-QFN (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f713-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SFR Definition 10.9. ADC0MX: AMUX0 Channel Select

| Bit   | 7 | 6 | 5 | 4          | 3 | 2 | 1 | 0 |  |

|-------|---|---|---|------------|---|---|---|---|--|

| Name  |   |   |   | AMX0P[4:0] |   |   |   |   |  |

| Туре  | R | R | R | R/W        |   |   |   |   |  |

| Reset | 0 | 0 | 0 | 1 1 1 1 1  |   |   |   |   |  |

#### SFR Address = 0xBB; SFR Page = 0

| Bit | Name       |                    | Fur            | nction            |                |

|-----|------------|--------------------|----------------|-------------------|----------------|

| 7:5 | Unused     | Read = 000b; Write | = Don't Care.  |                   |                |

| 4:0 | AMX0P[4:0] | AMUX0 Positive In  | put Selection. |                   |                |

|     |            |                    | 64-Pin Devices | 48-Pin Devices    | 32-Pin Devices |

|     |            | 00000              | P0.0           | P0.0              | —              |

|     |            | 00001              | P0.1           | P0.1              | _              |

|     |            | 00010              | P0.2           | P0.2              | _              |

|     |            | 00011              | P0.3           | P0.3              | P0.3           |

|     |            | 00100              | P0.4           | P0.4              | P0.4           |

|     |            | 00101              | P0.5           | P0.5              | P0.5           |

|     |            | 00110              | P0.6           | P0.6              | —              |

|     |            | 00111              | P0.7           | P0.7              | _              |

|     |            | 01000              | P1.0           | P1.0              | _              |

|     |            | 01001              | P1.1           | P1.1              | —              |

|     |            | 01010              | P1.2           | P1.2              | —              |

|     |            | 01011              | P1.3           | P1.3              | —              |

|     |            | 01100              | P1.4           | —                 | —              |

|     |            | 01101              | P1.5           | —                 | _              |

|     |            | 01110              | P1.6           | —                 | _              |

|     |            | 01111              | P1.7           | —                 | _              |

|     |            | 10000              | Temp Sensor    | Temp Sensor       | Temp Sensor    |

|     |            | 10001              | VREG Output    | VREG Output       | VREG Output    |

|     |            | 10010              | VDD            | VDD               | VDD            |

|     |            | 10011              | GND            | GND               | GND            |

|     |            | 10100–11111        |                | no input selected |                |

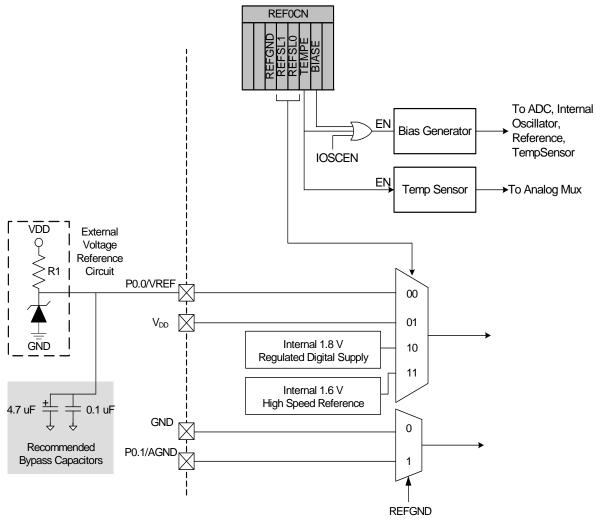

## 12. Voltage and Ground Reference Options

The voltage reference MUX is configurable to use an externally connected voltage reference, the on-chip voltage reference, or one of two power supply voltages (see Figure 12.1). The ground reference MUX allows the ground reference for ADC0 to be selected between the ground pin (GND) or a port pin dedicated to analog ground (P0.1/AGND).

The voltage and ground reference options are configured using the REF0CN SFR described on page 71. Electrical specifications are can be found in the Electrical Specifications Chapter.

**Important Note About the V<sub>REF</sub> and AGND Inputs:** Port pins are used as the external V<sub>REF</sub> and AGND inputs. When using an external voltage reference, P0.0/VREF should be configured as an analog input and skipped by the Digital Crossbar. When using AGND as the ground reference to ADC0, P0.1/AGND should be configured as an analog input and skipped by the Digital Crossbar. Refer to Section "28. Port Input/Output" on page 180 for complete Port I/O configuration details. The external reference voltage must be within the range  $0 \le V_{REF} \le V_{DD}$  and the external ground reference must be at the same DC voltage potential as GND.

Figure 12.1. Voltage Reference Functional Block Diagram

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

### 16.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 16.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 16.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

## SFR Definition 16.3. SP: Stack Pointer

| Bit    | 7           | 6               | 5           | 4 | 3                | 2 | 1 | 0 |  |  |

|--------|-------------|-----------------|-------------|---|------------------|---|---|---|--|--|

| Name   | SP[7:0]     |                 |             |   |                  |   |   |   |  |  |

| Туре   |             | R/W             |             |   |                  |   |   |   |  |  |

| Reset  | 0           | 0 0 0 0 0 1 1 1 |             |   |                  |   |   |   |  |  |

| SFR Ad | dress = 0x8 | 1; SFR Page     | = All Pages |   |                  |   |   |   |  |  |

| D:4    | Marria      |                 |             |   | <b>F</b> unction |   |   |   |  |  |

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

## SFR Definition 16.4. ACC: Accumulator

| Bit   | 7                    | 6         5         4         3         2         1         0 |               |              |       |  |  |  |  |  |  |

|-------|----------------------|---------------------------------------------------------------|---------------|--------------|-------|--|--|--|--|--|--|

| Nam   | e ACC[7:0]           |                                                               |               |              |       |  |  |  |  |  |  |

| Туре  | •                    | R/W                                                           |               |              |       |  |  |  |  |  |  |

| Rese  | eset 0 0 0 0 0 0 0 0 |                                                               |               |              |       |  |  |  |  |  |  |

| SFR A | Address = 0xE        | E0; SFR Page                                                  | e = All Pages | ; Bit-Addres | sable |  |  |  |  |  |  |

| Bit   | Name                 |                                                               |               |              |       |  |  |  |  |  |  |

| 7:0   | ACC[7:0]             | Accumulator.                                                  |               |              |       |  |  |  |  |  |  |

|       |                      | This register is the accumulator for arithmetic operations.   |               |              |       |  |  |  |  |  |  |

Rev. 1.0

## SFR Definition 20.1. SFRPAGE: SFR Page

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|--|

| Name  |   | SFRPAGE[7:0]    |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |

SFR Address = 0xA7; SFR Page = All Pages

| Bit | Name         | Description                                                                      |

|-----|--------------|----------------------------------------------------------------------------------|

| 7:0 | SFRPAGE[7:0] | SFR Page Bits.                                                                   |

|     |              | Represents the SFR Page the C8051 core uses when reading or modifying SFRs.      |

|     |              | Write: Sets the SFR Page.<br>Read: Byte is the SFR page the C8051 core is using. |

#### Table 20.2. Special Function Registers

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | Page      | Description                       | Page |

|----------|---------|-----------|-----------------------------------|------|

| ACC      | 0xE0    | All Pages | Accumulator                       | 105  |

| ADC0CF   | 0xBC    | F         | ADC0 Configuration                | 59   |

| ADC0CN   | 0xE8    | All Pages | ADC0 Control                      | 61   |

| ADC0GTH  | 0xC4    | 0         | ADC0 Greater-Than Compare High    | 62   |

| ADC0GTL  | 0xC3    | 0         | ADC0 Greater-Than Compare Low     | 62   |

| ADC0H    | 0xBE    | 0         | ADC0 High                         | 60   |

| ADC0L    | 0xBD    | 0         | ADC0 Low                          | 60   |

| ADC0LTH  | 0xC6    | 0         | ADC0 Less-Than Compare Word High  | 63   |

| ADC0LTL  | 0xC5    | 0         | ADC0 Less-Than Compare Word Low   | 63   |

| ADC0MX   | 0xBB    | 0         | AMUX0 Multiplexer Channel Select  | 66   |

| В        | 0xF0    | All Pages | B Register                        | 106  |

| CKCON    | 0x8E    | All Pages | Clock Control                     | 263  |

| CLKSEL   | 0xBD    | F         | Clock Select                      | 263  |

| CPT0CN   | 0x9B    | 0         | Comparator0 Control               | 76   |

| CPT0MD   | 0x9D    | 0         | Comparator0 Mode Selection        | 77   |

| CPT0MX   | 0x9F    | 0         | Comparator0 MUX Selection         | 79   |

| CRC0AUTO | 0x96    | F         | CRC0 Automatic Control Register   | 217  |

| CRC0CN   | 0x91    | F         | CRC0 Control                      | 215  |

| CRC0CNT  | 0x97    | F         | CRC0 Automatic Flash Sector Count | 217  |

| CRC0DATA | 0xD9    | F         | CRC0 Data Output                  | 216  |

| CRC0FLIP | 0x95    | F         | CRC0 Bit Flip                     | 218  |

| CRCOIN   | 0x94    | F         | CRC Data Input                    | 216  |

| Interrupt Source               | Interrupt<br>Vector | Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|--------------------------------|---------------------|-------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                          | 0x0000              | Тор   | None                                                                       | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(INT0) | 0x0003              | 0     | IE0 (TCON.1)                                                               | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow               | 0x000B              | 1     | TF0 (TCON.5)                                                               | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(INT1) | 0x0013              | 2     | IE1 (TCON.3)                                                               | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow               | 0x001B              | 3     | TF1 (TCON.7)                                                               | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                          | 0x0023              | 4     | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow               | 0x002B              | 5     | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                           | 0x0033              | 6     | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y                |                | ESPI0<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                           | 0x003B              | 7     | SI (SMB0CN.0)                                                              | Y                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| Port Match                     | 0x0043              | 8     | None                                                                       | N/A              | N/A            | EMAT<br>(EIE1.1)   | PMAT<br>(EIP1.1)    |

| ADC0<br>Window Compare         | 0x004B              | 9     | ADOWINT (ADC0CN.3)                                                         | Y                | N              | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| ADC0 Conversion<br>Complete    | 0x0053              | 10    | AD0INT (ADC0CN.5)                                                          | Y                | N              | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)   |

| Programmable<br>Counter Array  | 0x005B              | 11    | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                           | Y                | N              | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)   |

| Comparator0                    | 0x0063              | 12    | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N                | N              | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)    |

| RESERVED                       |                     |       |                                                                            |                  |                |                    |                     |

| Timer 3 Overflow               | 0x0073              | 14    | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N                | N              | ET3<br>(EIE1.7)    | PT3<br>(EIP1.7)     |

| CS0 Conversion<br>Complete     | 0x007B              | 15    | CS0INT (CS0CN.5)                                                           | N                | N              | ECSCPT<br>(EIE2.0) | PSCCPT<br>(EIP2.0)  |

| CS0 Greater Than<br>Compare    | 0x0083              | 16    | CS0CMPF (CS0CN.0)                                                          | N                | N              | ECSGRT<br>(EIE2.1) | PSCGRT<br>(EIP2.1)  |

## Table 21.1. Interrupt Summary

## SFR Definition 21.2. IP: Interrupt Priority

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Туре  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

#### SFR Address = 0xB8; SFR Page = All Pages; Bit-Addressable

| Bit | Name   | Function                                                                                                                                                                                                                 |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused | Read = 1b, Write = Don't Care.                                                                                                                                                                                           |

| 6   | PSPI0  | Serial Peripheral Interface (SPI0) Interrupt Priority Control.<br>This bit sets the priority of the SPI0 interrupt.<br>0: SPI0 interrupt set to low priority level.<br>1: SPI0 interrupt set to high priority level.     |

| 5   | PT2    | Timer 2 Interrupt Priority Control.This bit sets the priority of the Timer 2 interrupt.0: Timer 2 interrupt set to low priority level.1: Timer 2 interrupt set to high priority level.                                   |

| 4   | PS0    | UART0 Interrupt Priority Control.<br>This bit sets the priority of the UART0 interrupt.<br>0: UART0 interrupt set to low priority level.<br>1: UART0 interrupt set to high priority level.                               |

| 3   | PT1    | Timer 1 Interrupt Priority Control.This bit sets the priority of the Timer 1 interrupt.0: Timer 1 interrupt set to low priority level.1: Timer 1 interrupt set to high priority level.                                   |

| 2   | PX1    | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt.<br>0: External Interrupt 1 set to low priority level.<br>1: External Interrupt 1 set to high priority level. |

| 1   | PT0    | Timer 0 Interrupt Priority Control.This bit sets the priority of the Timer 0 interrupt.0: Timer 0 interrupt set to low priority level.1: Timer 0 interrupt set to high priority level.                                   |

| 0   | PX0    | External Interrupt 0 Priority Control.<br>This bit sets the priority of the External Interrupt 0 interrupt.<br>0: External Interrupt 0 set to low priority level.<br>1: External Interrupt 0 set to high priority level. |

### SFR Definition 21.6. EIP2: Extended Interrupt Priority 2

| Bit   | 7        | 6        | 5        | 4        | 3        | 2        | 1      | 0      |

|-------|----------|----------|----------|----------|----------|----------|--------|--------|

| Name  | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | PSCGRT | PSCCPT |

| Туре  | R        | R        | R        | R        | R        | R        | R/W    | R/W    |

| Reset | 0        | 0        | 0        | 0        | 0        | 0        | 0      | 0      |

#### SFR Address = 0xCF; SFR Page = F

| Bit | Name     | Function                                                                                                                                                                                                                                                                                             |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Reserved | Must Write 000000b.                                                                                                                                                                                                                                                                                  |

| 1   | PSCGRT   | Capacitive Sense Greater Than Comparator Priority Control.                                                                                                                                                                                                                                           |

|     |          | <ul><li>This bit sets the priority of the Capacitive Sense Greater Than Comparator interrupt.</li><li>0: CS0 Greater Than Comparator interrupt set to low priority level.</li><li>1: CS0 Greater Than Comparator set to high priority level.</li></ul>                                               |

| 0   | PSCCPT   | <ul> <li>Capacitive Sense Conversion Complete Priority Control.</li> <li>This bit sets the priority of the Capacitive Sense Conversion Complete interrupt.</li> <li>0: CS0 Conversion Complete set to low priority level.</li> <li>1: CS0 Conversion Complete set to high priority level.</li> </ul> |

## SFR Definition 22.2. FLKEY: Flash Lock and Key

FLKEY from software.

00: Flash is write/erase locked.

Read:

| Bit             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6            | 5             | 4       | 3        | 2 | 1 | 0 |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|---------|----------|---|---|---|--|

| Name FLKEY[7:0] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |               |         |          |   |   |   |  |

| Type R/W        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |               |         |          |   |   |   |  |

| Rese            | et O                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0            | 0             | 0       | 0        | 0 | 0 | 0 |  |

| SFR A           | Address = 0xE                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37; SFR Page | e = All Pages | 6       |          |   |   |   |  |

| Bit             | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |               |         | Function |   |   |   |  |

| 7:0             | FLKEY[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Flash Lock   | and Key Re    | gister. |          |   |   |   |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Write:       |               |         |          |   |   |   |  |

|                 | Write:<br>This register provides a lock and key function for Flash erasures and writes. Flash<br>writes and erases are enabled by writing 0xA5 followed by 0xF1 to the FLKEY regis-<br>ter. Flash writes and erases are automatically disabled after the next write or erase is<br>complete. If any writes to FLKEY are performed incorrectly, or if a Flash write or erase<br>operation is attempted while these operations are disabled, the Flash will be perma-<br>nently |              |               |         |          |   |   |   |  |

When read, bits 1–0 indicate the current Flash lock state.

01: The first key code has been written (0xA5).10: Flash is unlocked (writes/erases allowed).11: Flash writes/erases disabled until the next reset.

locked from writes or erasures until the next device reset. If an application never writes to Flash, it can intentionally lock the Flash by writing a non-0xA5 value to

### SFR Definition 28.9. P0MDOUT: Port 0 Output Mode

| Bit   | 7 | 6            | 5 | 4  | 3 | 2 | 1 | 0 |

|-------|---|--------------|---|----|---|---|---|---|

| Name  |   | P0MDOUT[7:0] |   |    |   |   |   |   |

| Туре  |   |              |   | R/ | W |   |   |   |

| Reset | 0 | 0            | 0 | 0  | 0 | 0 | 0 | 0 |

SFR Address = 0xA4; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDOUT[7:0] | Output Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P0MDIN is logic 0.<br>0: Corresponding P0.n Output is open-drain.<br>1: Corresponding P0.n Output is push-pull. |

#### SFR Definition 28.10. P0SKIP: Port 0 Skip

| Bit   | 7 | 6           | 5 | 4  | 3 | 2 | 1 | 0 |

|-------|---|-------------|---|----|---|---|---|---|

| Name  |   | P0SKIP[7:0] |   |    |   |   |   |   |

| Туре  |   |             |   | R/ | W |   |   |   |

| Reset | 0 | 0           | 0 | 0  | 0 | 0 | 0 | 0 |

SFR Address = 0xD4; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0SKIP[7:0] | Port 0 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 0 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P0.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P0.n pin is skipped by the Crossbar.</li> </ul> |

## SFR Definition 30.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1          | 0 |

|-------|-------|-----|------|---------|--------|--------|------------|---|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBCS[1:0] |   |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/         | W |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0          | 0 |

#### SFR Address = 0xC1; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB      | SMBus Enable.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                                                                                                             |

| 6   | INH        | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                                                                                                    |

| 5   | BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                                                                                                                |

| 4   | EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | This bit controls the SDA setup and hold times according to Table 30.2.                                                                                                                                                                                                                                                                                                                                                               |

|     |            | 0: SDA Extended Setup and Hold Times disabled.                                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | 1: SDA Extended Setup and Hold Times enabled.                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |            | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces<br>Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |

| 2   | SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                                                                                                              |

| 1:0 | SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | These two bits select the SMBus clock source, which is used to generate the SMBus bit rate. The selected device should be configured according to Equation 30.1.<br>00: Timer 0 Overflow<br>01: Timer 1 Overflow                                                                                                                                                                                                                      |

|     |            | 10: Timer 2 High Byte Overflow<br>11: Timer 2 Low Byte Overflow                                                                                                                                                                                                                                                                                                                                                                       |

|     |            |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

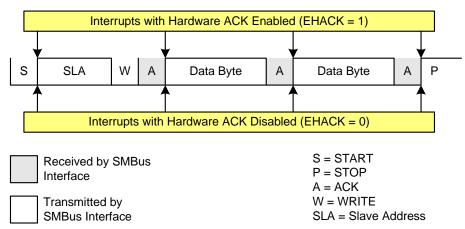

### 30.5. SMBus Transfer Modes

The SMBus interface may be configured to operate as master and/or slave. At any particular time, it will be operating in one of the following four modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. The SMBus interface enters Master Mode any time a START is generated, and remains in Master Mode until it loses an arbitration or generates a STOP. An SMBus interrupt is generated at the end of all SMBus byte frames. The position of the ACK interrupt when operating as a receiver depends on whether hardware ACK generation is enabled. As a receiver, the interrupt for an ACK occurs **before** the ACK with hardware ACK generation disabled, and **after** the ACK when hardware ACK generation is enabled. As a transmitter, interrupts occur **after** the ACK, regardless of whether hardware ACK generation is enabled or not.

#### 30.5.1. Write Sequence (Master)

During a write sequence, an SMBus master writes data to a slave device. The master in this transfer will be a transmitter during the address byte, and a transmitter during all data bytes. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 0 (WRITE). The master then transmits one or more bytes of serial data. After each byte is transmitted, an acknowledge bit is generated by the slave. The transfer is ended when the STO bit is set and a STOP is generated. The interface will switch to Master Receiver Mode if SMB0DAT is not written following a Master Transmitter interrupt. Figure 30.5 shows a typical master write sequence. Two transmit data bytes are shown, though any number of bytes may be transmitted. Notice that all of the "data byte transferred" interrupts occur **after** the ACK cycle in this mode, regardless of whether hardware ACK generation is enabled.

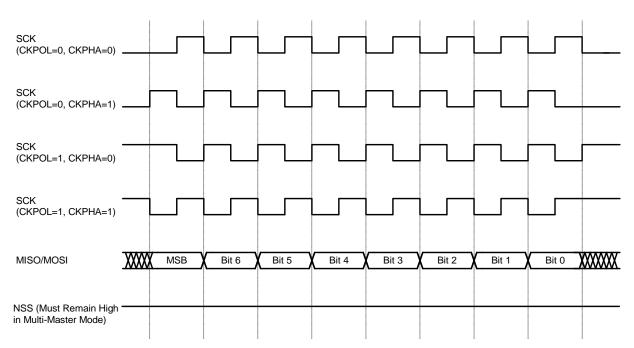

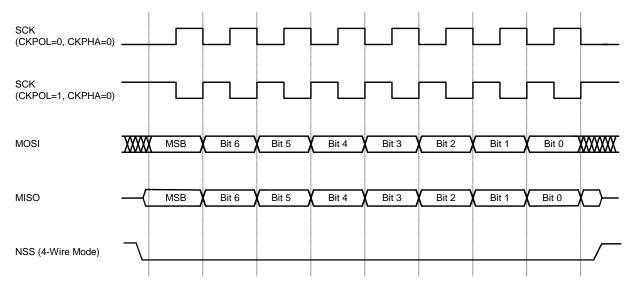

Figure 31.7. Slave Mode Data/Clock Timing (CKPHA = 1)

### **31.6. SPI Special Function Registers**

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

## SFR Definition 31.3. SPI0CKR: SPI0 Clock Rate

| Bit                              | 7        | 6                                                                                                    | 5                                                                                                          | 4                                                                                       | 3                                                              | 2                                             | 1                                                                | 0                                |  |  |

|----------------------------------|----------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------|----------------------------------|--|--|

| Name                             |          |                                                                                                      | SCR[7:0]                                                                                                   |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |

| Туре                             |          |                                                                                                      |                                                                                                            | R                                                                                       | /W                                                             |                                               |                                                                  |                                  |  |  |

| Reset                            | 0        | 0                                                                                                    | 0                                                                                                          | 0                                                                                       | 0                                                              | 0                                             | 0                                                                | 0                                |  |  |

| SFR Address = 0xA2; SFR Page = F |          |                                                                                                      |                                                                                                            |                                                                                         |                                                                |                                               |                                                                  |                                  |  |  |

| Bit                              | Name     |                                                                                                      |                                                                                                            |                                                                                         | Functior                                                       | )                                             |                                                                  |                                  |  |  |

| 7:0                              | SCR[7:0] | configured<br>sion of the<br>the system<br>register.<br>f <sub>SCK</sub> =<br>for 0 <= S<br>Example: | s determine<br>d for master<br>e system clo<br>n clock frequ<br>$\frac{SY}{2 \times (SPI00)}$<br>PI0CKR <= | mode opera<br>ck, and is giv<br>Jency and S<br>SCLK<br>CKR[7:0] +<br>255<br>= 2 MHz and | tion. The S(<br>ven in the fo<br>PIOCKR is t<br>$\overline{1}$ | CK clock fre<br>Illowing equ<br>he 8-bit valu | en the SPI0 r<br>quency is a d<br>ation, where<br>le held in the | ivided ver-<br>S <i>YSCLK</i> is |  |  |

## SFR Definition 31.4. SPI0DAT: SPI0 Data

| Bit   | 7 | 6            | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|-------|---|--------------|---|----|---|---|---|---|--|--|

| Name  |   | SPI0DAT[7:0] |   |    |   |   |   |   |  |  |

| Туре  |   |              |   | R/ | W |   |   |   |  |  |

| Reset | 0 | 0            | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

SFR Address = 0xA3; SFR Page = 0

| Bit | Name         | Function                                                                                                                                                                                                                                     |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPI0DAT[7:0] | SPI0 Transmit and Receive Data.                                                                                                                                                                                                              |

|     |              | The SPI0DAT register is used to transmit and receive SPI0 data. Writing data to SPI0DAT places the data into the transmit buffer and initiates a transfer when in Master Mode. A read of SPI0DAT returns the contents of the receive buffer. |

| Parameter                | Description                                           | Min                          | Max                     | Units |

|--------------------------|-------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mode              | Timing (See Figure 31.8 and Figure 31.9)              |                              |                         | I     |

| Т <sub>МСКН</sub>        | SCK High Time                                         | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MCKL</sub>        | SCK Low Time                                          | 1 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>MIS</sub>         | MISO Valid to SCK Shift Edge                          | 1 x T <sub>SYSCLK</sub> + 20 |                         | ns    |

| Т <sub>МІН</sub>         | SCK Shift Edge to MISO Change                         | 0                            |                         | ns    |

| Slave Mode               | Timing (See Figure 31.10 and Figure 31.11)            |                              |                         |       |

| T <sub>SE</sub>          | NSS Falling to First SCK Edge                         | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SD</sub>          | Last SCK Edge to NSS Rising                           | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SEZ</sub>         | NSS Falling to MISO Valid                             | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>         | NSS Rising to MISO High-Z                             | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| Т <sub>СКН</sub>         | SCK High Time                                         | 5 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>CKL</sub>         | SCK Low Time                                          | 5 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SIS</sub>         | MOSI Valid to SCK Sample Edge                         | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SIH</sub>         | SCK Sample Edge to MOSI Change                        | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SOH</sub>         | SCK Shift Edge to MISO Change                         | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>         | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)      | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| Note: T <sub>SYSCL</sub> | K is equal to one period of the device system clock ( | SYSCLK).                     |                         | l     |

## Table 31.1. SPI Slave Timing Parameters

#### 33.2.3. Comparator 0 Capture Mode

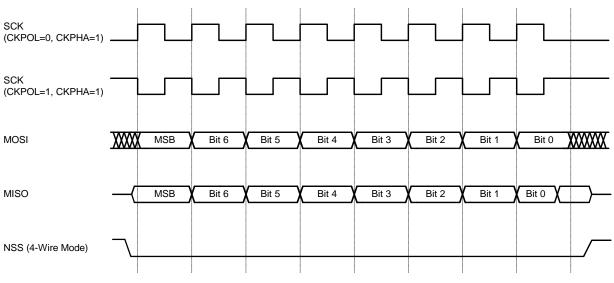

The capture mode in Timer 2 allows Comparator 0 rising edges to be captured with the timer clocking from the system clock or the system clock divided by 12. Timer 2 capture mode is enabled by setting TF2CEN to 1 and T2SPLIT to 0.

When capture mode is enabled, a capture event will be generated on every Comparator 0 rising edge. When the capture event occurs, the contents of Timer 2 (TMR2H:TMR2L) are loaded into the Timer 2 reload registers (TMR2RLH:TMR2RLL) and the TF2H flag is set (triggering an interrupt if Timer 2 interrupts are enabled). By recording the difference between two successive timer capture values, the Comparator 0 period can be determined with respect to the Timer 2 clock. The Timer 2 clock should be much faster than the capture clock to achieve an accurate reading.

This mode allows software to determine the time between consecutive Comparator 0 rising edges, which can be used for detecting changes in the capacitance of a capacitive switch, or measuring the frequency of a low-level analog signal.

Figure 33.6. Timer 2 Capture Mode Block Diagram

## 34. Programmable Counter Array

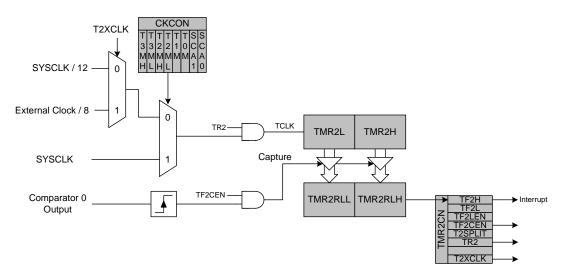

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled. The counter/timer is driven by a programmable timebase that can select between seven sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflows, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8 to 11-Bit PWM, or 16-Bit PWM (each mode is described in Section "34.3. Capture/Compare Modules" on page 286). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 34.1

Figure 34.1. PCA Block Diagram

## SFR Definition 34.5. PCA0L: PCA Counter/Timer Low Byte

| Bit                              | 7    | 6             | 5   | 4   | 3      | 2   | 1   | 0   |

|----------------------------------|------|---------------|-----|-----|--------|-----|-----|-----|

| Name                             |      |               |     | PCA | )[7:0] |     |     |     |

| Туре                             | R/W  | R/W           | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset                            | 0    | 0             | 0   | 0   | 0      | 0   | 0   | 0   |

| SFR Address = 0xF9; SFR Page = 0 |      |               |     |     |        |     |     |     |

| Bit                              | Name | Name Function |     |     |        |     |     |     |

| Bit | Name      | Function                                                                     |  |  |  |  |

|-----|-----------|------------------------------------------------------------------------------|--|--|--|--|

| 7:0 | PCA0[7:0] | PCA Counter/Timer Low Byte.                                                  |  |  |  |  |

|     |           | The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |  |  |  |  |

### SFR Definition 34.6. PCA0H: PCA Counter/Timer High Byte

| Bit   | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | PCA0[15:8] |     |     |     |     |     |     |     |

| Туре  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xFA; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                                                                                            |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | PCA0[15:8] | PCA Counter/Timer High Byte.                                                                                                                                                                                                                        |

|     |            | The PCA0H register holds the high byte (MSB) of the 16-bit PCA Counter/Timer.<br>Reads of this register will read the contents of a "snapshot" register, whose contents<br>are updated only when the contents of PCA0L are read (see Section 34.1). |

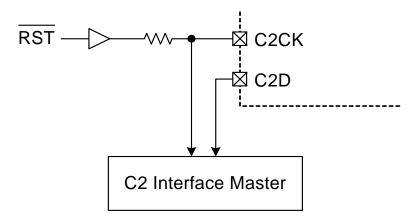

### 35.2. C2CK Pin Sharing

The C2CK pin is shared with the  $\overline{\text{RST}}$  signal on this device family. If the  $\overline{\text{RST}}$  pin is used by other parts of the system, debugging and programming the device can still be accomplished without disrupting the rest of the system. If this is desired, it is normally necessary to add a resistor to isolate the system's reset line from the C2CK signal. This external resistors would not be necessary for production boards, where debugging capabilities are not needed. A typical isolation configuration is shown in Figure 35.1.

Figure 35.1. Typical C2CK Pin Sharing

The configuration in Figure 35.1 assumes the  $\overline{RST}$  pin on the target device is used as an input only. Additional resistors may be necessary depending on the specific application.