# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | Cap Sense, POR, PWM, Temp Sensor, WDT                          |

| Number of I/O              | 39                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 12x10b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f714-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 9.14. Comparator Electrical Characteristics

$V_{DD}$  = 3.0 V, –40 to +85 °C unless otherwise noted.

| Parameter                                         | Conditions             | Min   | Тур  | Max                    | Units |

|---------------------------------------------------|------------------------|-------|------|------------------------|-------|

| Response Time:                                    | CP0+ - CP0- = 100 mV   |       | 300  |                        | ns    |

| Mode 0, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  | _     | 200  | _                      | ns    |

| Response Time:                                    | CP0+ – CP0– = 100 mV   |       | 400  | _                      | ns    |

| Mode 1, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  | _     | 350  | _                      | ns    |

| Response Time:                                    | CP0+ – CP0– = 100 mV   | _     | 570  | _                      | ns    |

| Mode 2, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  |       | 870  | _                      | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV   |       | 1500 |                        | ns    |

| Mode 3, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV  |       | 4500 | _                      | ns    |

| Common-Mode Rejection Ratio                       |                        |       | 1    | 4                      | mV/V  |

| Positive Hysteresis 1                             | Mode 2, CP0HYP1–0 = 00 | _     | 0    | 1                      | mV    |

| Positive Hysteresis 2                             | Mode 2, CP0HYP1–0 = 01 | 2     | 5    | 10                     | mV    |

| Positive Hysteresis 3                             | Mode 2, CP0HYP1–0 = 10 | 7     | 10   | 20                     | mV    |

| Positive Hysteresis 4                             | Mode 2, CP0HYP1–0 = 11 | 10    | 20   | 30                     | mV    |

| Negative Hysteresis 1                             | Mode 2, CP0HYN1–0 = 00 | —     | 0    | 1                      | mV    |

| Negative Hysteresis 2                             | Mode 2, CP0HYN1–0 = 01 | 2     | 5    | 10                     | mV    |

| Negative Hysteresis 3                             | Mode 2, CP0HYN1–0 = 10 | 7     | 10   | 20                     | mV    |

| Negative Hysteresis 4                             | Mode 2, CP0HYN1–0 = 11 | 10    | 20   | 30                     | mV    |

| Inverting or Non-Inverting Input<br>Voltage Range |                        | -0.25 | _    | V <sub>DD</sub> + 0.25 | V     |

| Input Offset Voltage                              |                        | -7.5  | _    | 7.5                    | mV    |

| Power Specifications                              |                        |       |      |                        |       |

| Power Supply Rejection                            |                        | _     | 0.1  | _                      | mV/V  |

| Powerup Time                                      |                        | —     | 10   | —                      | μs    |

| Supply Current at DC                              | Mode 0                 | —     | 25   |                        | μA    |

|                                                   | Mode 1                 | —     | 10   | _                      | μA    |

|                                                   | Mode 2                 | —     | 3    | —                      | μA    |

|                                                   | Mode 3                 | —     | 0.5  | —                      | μA    |

| Note: Vcm is the common-mode vol                  | tage on CP0+ and CP0   |       |      |                        |       |

## SFR Definition 10.2. ADC0H: ADC0 Data Word MSB

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|--|

| Name  |   | ADC0H[7:0]      |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |

SFR Address = 0xBE; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                     |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0H[7:0] | ADC0 Data Word High-Order Bits.                                                                                                                                              |

|     |            | For AD0LJST = 0: Bits 7:2 will read 000000b. Bits 1–0 are the upper 2 bits of the 10-<br>bit ADC0 Data Word.                                                                 |

|     |            | For AD0LJST = 1: Bits 7:0 are the most-significant bits of the 10-bit ADC0 Data Word.<br><b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0H holds the 8-bit data word. |

#### SFR Definition 10.3. ADC0L: ADC0 Data Word LSB

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|--|

| Name  |   | ADC0L[7:0]      |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |

SFR Address = 0xBD; SFR Page = 0

| Bit | Name       | Function                                                                                             |

|-----|------------|------------------------------------------------------------------------------------------------------|

| 7:0 | ADC0L[7:0] | ADC0 Data Word Low-Order Bits.                                                                       |

|     |            | For AD0LJST = 0: Bits 7:0 are the lower 8 bits of the 10-bit Data Word.                              |

|     |            | For AD0LJST = 1: Bits 7:6 are the lower 2 bits of the 10-bit Data Word. Bits 5–0 will always read 0. |

|     |            | <b>Note:</b> In 8-bit mode AD0LJST is ignored, and ADC0L will read back 0000000b.                    |

## SFR Definition 12.1. REF0CN: Voltage Reference Control

| Bit   | 7 | 6 | 5      | 4   | 3   | 2     | 1     | 0 |

|-------|---|---|--------|-----|-----|-------|-------|---|

| Name  |   |   | REFGND | REI | FSL | TEMPE | BIASE |   |

| Туре  | R | R | R/W    | R/W | R/W | R/W   | R/W   | R |

| Reset | 0 | 0 | 0      | 1   | 0   | 0     | 0     | 0 |

### SFR Address = 0xD2; SFR Page = F

| Bit | Name   | Function                                                                           |

|-----|--------|------------------------------------------------------------------------------------|

| 7:6 | Unused | Read = 00b; Write = Don't Care.                                                    |

| 5   | REFGND | Analog Ground Reference.                                                           |

|     |        | Selects the ADC0 ground reference.                                                 |

|     |        | 0: The ADC0 ground reference is the GND pin.                                       |

|     |        | 1: The ADC0 ground reference is the P0.1/AGND pin.                                 |

| 4:3 | REFSL  | Voltage Reference Select.                                                          |

|     |        | Selects the ADC0 voltage reference.                                                |

|     |        | 00: The ADC0 voltage reference is the P0.0/VREF pin.                               |

|     |        | 01: The ADC0 voltage reference is the VDD pin.                                     |

|     |        | 10: The ADC0 voltage reference is the internal 1.8 V digital supply voltage.       |

|     |        | 11: The ADC0 voltage reference is the internal 1.6 V high-speed voltage reference. |

| 2   | TEMPE  | Temperature Sensor Enable.                                                         |

|     |        | Enables/Disables the internal temperature sensor.                                  |

|     |        | 0: Temperature Sensor Disabled.                                                    |

|     |        | 1: Temperature Sensor Enabled.                                                     |

| 1   | BIASE  | Internal Analog Bias Generator Enable Bit.                                         |

|     |        | 0: Internal Bias Generator off.                                                    |

|     |        | 1: Internal Bias Generator on.                                                     |

| 0   | Unused | Read = 0b; Write = Don't Care.                                                     |

### 16.2. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should always be written to the value indicated in the SFR description. Future product versions may use these bits to implement new features in which case the reset value of the bit will be the indicated value, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

#### SFR Definition 16.1. DPL: Data Pointer Low Byte

| Bit           | 7                                                    | 6            | 5           | 4  | 3 | 2 | 1 | 0 |  |  |  |  |

|---------------|------------------------------------------------------|--------------|-------------|----|---|---|---|---|--|--|--|--|

| Name DPL[7:0] |                                                      |              |             |    |   |   |   |   |  |  |  |  |

| Type R/W      |                                                      |              |             |    |   |   |   |   |  |  |  |  |

| Rese          | et 0                                                 | 0            | 0           | 0  | 0 | 0 | 0 | 0 |  |  |  |  |

| SFR A         | Address = 0x8                                        | 32; SFR Page | = All Pages | i. |   |   |   |   |  |  |  |  |

| Bit           | Name                                                 |              |             |    |   |   |   |   |  |  |  |  |

| 7:0           | 7:0 DPL[7:0] Data Pointer Low.                       |              |             |    |   |   |   |   |  |  |  |  |

|               | The DPL register is the low byte of the 16-bit DPTR. |              |             |    |   |   |   |   |  |  |  |  |

#### SFR Definition 16.2. DPH: Data Pointer High Byte

| Bit     | 7                                        | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------------------------------------------|----------|---|---|---|---|---|---|--|--|--|

| Name    |                                          | DPH[7:0] |   |   |   |   |   |   |  |  |  |

| Туре    |                                          | R/W      |   |   |   |   |   |   |  |  |  |

| Reset   | 0 0 0 0 0 0 0 0                          |          |   |   |   |   |   |   |  |  |  |

| SFR Add | SFR Address = 0x83; SFR Page = All Pages |          |   |   |   |   |   |   |  |  |  |

| 01107 |          |                                                       |

|-------|----------|-------------------------------------------------------|

| Bit   | Name     | Function                                              |

| 7:0   | DPH[7:0] | Data Pointer High.                                    |

|       |          | The DPH register is the high byte of the 16-bit DPTR. |

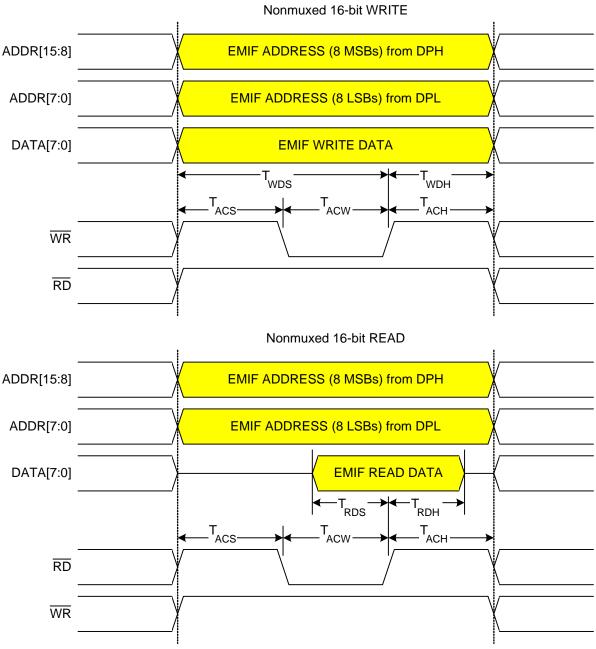

#### 18.6.1. Non-Multiplexed Mode

18.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111

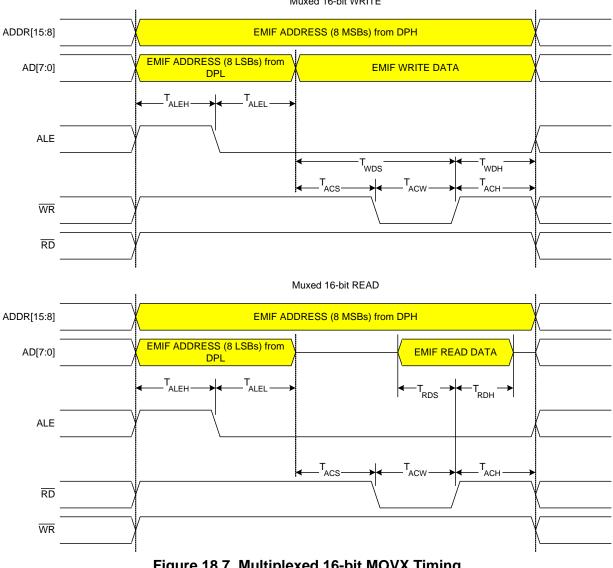

### 18.6.2. Multiplexed Mode 18.6.2.1. 16-bit MOVX: EMI0CF[4:2] = 001, 010, or 011

Muxed 16-bit WRITE

- 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- 7. Clear the PSWE and PSEE bits.

- 8. Restore previous interrupt state.

Steps 4–6 must be repeated for each 512-byte page to be erased.

**Note:** Flash security settings may prevent erasure of some Flash pages, such as the reserved area and the page containing the lock bytes. For a summary of Flash security settings and restrictions affecting Flash erase operations, please see Section "22.3. Security Options" on page 149.

#### 22.1.3. Flash Write Procedure

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed should be erased before a new value is written.

The recommended procedure for writing a single byte in Flash is as follows:

- 1. Save current interrupt state and disable interrupts.

- 2. Ensure that the Flash byte has been erased (has a value of 0xFF).

- 3. Set the PSWE bit (register PSCTL).

- 4. Clear the PSEE bit (register PSCTL).

- 5. Write the first key code to FLKEY: 0xA5.

- 6. Write the second key code to FLKEY: 0xF1.

- 7. Using the MOVX instruction, write a single data byte to the desired location within the 512-byte sector.

- 8. Clear the PSWE bit.

- 9. Restore previous interrupt state.

Steps 5–7 must be repeated for each byte to be written.

**Note:** Flash security settings may prevent writes to some areas of Flash, such as the reserved area. For a summary of Flash security settings and restrictions affecting Flash write operations, please see Section "22.3. Security Options" on page 149.

#### 22.2. Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction.

Note: MOVX read instructions always target XRAM.

#### 22.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, and erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock all Flash pages, starting at page 0, by writing a non-0xFF value to the lock byte. Note that writing a non-0xFF value to the lock byte will lock all pages of FLASH from reads, writes, and erases, including the page containing the lock byte.

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on

#### 22.4.3. System Clock

- 12. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 13. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories web site.

## SFR Definition 23.2. EEDATA: EEPROM Byte Data

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|--|

| Name  |   | EEDATA[7:0]     |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W             |   |   |   |   |   |   |  |  |  |

| Reset | 1 | 1 1 1 1 1 1 1 1 |   |   |   |   |   |   |  |  |  |

SFR Address = 0xD1; SFR Page = All Pages

| Bit | Name        | Description                                                                                                                     | Write                                     | Read                                                |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------|

| 7:0 | EEDATA[7:0] | <b>E2PROM Data</b><br>The EEDATA register is<br>used to read bytes from the<br>EEPROM space and write<br>bytes to EEPROM space. | Writes byte to location stored in EEADDR. | Returns contents at loca-<br>tion stored in EEADDR. |

## 24. Power Management Modes

The C8051F70x/71x devices have three software programmable power management modes: Idle, Stop, and Suspend. Idle mode and Stop mode are part of the standard 8051 architecture, while Suspend mode is an enhanced power-saving mode implemented by the high-speed oscillator peripheral.

Idle mode halts the CPU while leaving the peripherals and clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the internal oscillator is stopped (analog peripherals remain in their selected states; the external oscillator is not affected). Suspend mode is similar to Stop mode in that the internal oscillator and CPU are halted, but the device can wake on events such as a Port Mismatch, Comparator low output, or a Timer 3 overflow. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode and Suspend mode consume the least power because the majority of the device is shut down with no clocks active. SFR Definition 24.1 describes the Power Control Register (PCON) used to control the C8051F70x/71x's Stop and Idle power management modes. Suspend mode is controlled by the SUSPEND bit in the OSCICN register (SFR Definition 27.3).

Although the C8051F70x/71x has Idle, Stop, and Suspend modes available, more control over the device power can be achieved by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers or serial buses, draw little power when they are not in use. Turning off oscillators lowers power consumption considerably, at the expense of reduced functionality.

#### 24.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the hardware to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

**Note:** If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Therefore, instructions that set the IDLE bit should be followed by an instruction that has two or more opcode bytes, for example:

| // in `C':<br>PCON  = 0x01;<br>PCON = PCON;        | <pre>// set IDLE bit // followed by a 3-cycle dummy instruction</pre> |

|----------------------------------------------------|-----------------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction           |

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section "26. Watchdog Timer" on page 169 for more information on the use and configuration of the WDT.

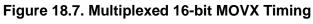

### 25.1. Power-On Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. A delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 25.2. plots the power-on and V<sub>DD</sub> monitor reset timing. The maximum V<sub>DD</sub> ramp time is 1 ms; slower ramp times may cause the device to be released from reset before V<sub>DD</sub> reaches the V<sub>RST</sub> level. For ramp times less than 1 ms, the power-on reset delay (T<sub>PORDelay</sub>) is typically less than 10 ms.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> monitor is enabled following a power-on reset.

Figure 25.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

## SFR Definition 25.2. RSTSRC: Reset Source

| Bit   | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| Name  |   | FERROR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | 0 | Varies |

SFR Address = 0xEF; SFR Page = All Pages

| Bit   | Name       | Description                                                                                    | Write                                                                                                                                                                | Read                                                                                                                                           |

|-------|------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Unused     | Unused.                                                                                        | Don't care.                                                                                                                                                          | 0                                                                                                                                              |

| 6     | FERROR     | Flash Error Reset Flag.                                                                        | N/A                                                                                                                                                                  | Set to 1 if Flash<br>read/write/erase error<br>caused the last reset.                                                                          |

| 5     | CORSEF     | Comparator0 Reset Enable and Flag.                                                             | Writing a 1 enables<br>Comparator0 as a reset<br>source (active-low).                                                                                                | Set to 1 if Comparator0 caused the last reset.                                                                                                 |

| 4     | SWRSF      | Software Reset Force and Flag.                                                                 | Writing a 1 forces a sys-<br>tem reset.                                                                                                                              | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                                   |

| 3     | WDTRSF     | Watchdog Timer Reset Flag.                                                                     | N/A                                                                                                                                                                  | Set to 1 if Watchdog Timer overflow caused the last reset.                                                                                     |

| 2     | MCDRSF     | Missing Clock Detector<br>Enable and Flag.                                                     | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                       | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                        |

| 1     | PORSF      | Power-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the $V_{DD}$ monitor as a reset source.<br>Writing 1 to this bit before the $V_{DD}$ monitor is enabled and stabilized may cause a system reset. | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate. |

| 0     | PINRSF     | HW Pin Reset Flag.                                                                             | N/A                                                                                                                                                                  | Set to 1 if RST pin caused the last reset.                                                                                                     |

| Note: | Do not use | read-modify-write operations on this                                                           | s register                                                                                                                                                           | 1                                                                                                                                              |

### 28.1. Port I/O Modes of Operation

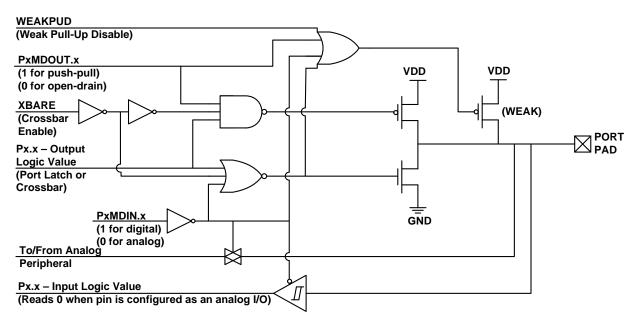

Port pins P0.0 - P6.5 use the Port I/O cell shown in Figure 28.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN registers. On reset, all Port I/O cells default to a high impedance state with weak pull-ups enabled. Until the crossbar is enabled (XBARE = 1), both the high and low port I/O drive circuits are explicitly disabled on all crossbar pins.

#### 28.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC input, Capacitive Sense input, external oscillator input/output, VREF output, or AGND connection should be configured for analog I/O (PnMDIN.n = 0). When a pin is configured for analog I/O, its weak pullup, digital driver, and digital receiver are disabled. Port pins configured for analog I/O will always read back a value of 0.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital I/O may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

#### 28.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external event trigger functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VDD or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VDD supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption, and they may be globally disabled by setting WEAKPUD to 1. The user should ensure that digital I/O are always internally or externally pulled or driven to a valid logic state to minimize power consumption. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

## SFR Definition 28.11. P0DRV: Port 0 Drive Strength

| Bit   | 7          | 6 | 5 | 4  | 3 | 2 | 1 | 0 |

|-------|------------|---|---|----|---|---|---|---|

| Name  | P0DRV[7:0] |   |   |    |   |   |   |   |

| Туре  |            |   |   | R/ | W |   |   |   |

| Reset | 0          | 0 | 0 | 0  | 0 | 0 | 0 | 0 |

#### SFR Address = 0xF9; SFR Page = F

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0DRV[7:0] | Drive Strength Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P0.n Output has low output drive strength.<br>1: Corresponding P0.n Output has high output drive strength. |

### SFR Definition 28.12. P1: Port 1

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P1[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Address = 0x90; SFR Page = All Pages; Bit Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read                                                                    |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7:0 | P1[7:0] | <b>Port 1 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | 0: P1.n Port pin is logic<br>LOW.<br>1: P1.n Port pin is logic<br>HIGH. |

## SFR Definition 28.23. P3MDIN: Port 3 Input Mode

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P3MDIN[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

#### SFR Address = 0xF4; SFR Page = F

| Bit | Name        | Function                                                                                                                                                                |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P3MDIN[7:0] | Analog Configuration Bits for P3.7–P3.0 (respectively).                                                                                                                 |

|     |             | Port pins configured for analog mode have their weak pullup, digital driver, and digital receiver disabled.<br>0: Corresponding P3.n pin is configured for analog mode. |

|     |             | 1: Corresponding P3.n pin is not configured for analog mode.                                                                                                            |

### SFR Definition 28.24. P3MDOUT: Port 3 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P3MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xAF; SFR Page = F

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P3MDOUT[7:0] | Output Configuration Bits for P3.7–P3.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P3MDIN is logic 0.<br>0: Corresponding P3.n Output is open-drain.<br>1: Corresponding P3.n Output is push-pull. |

### **30.1. Supporting Documents**

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I<sup>2</sup>C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification—Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification—Version 1.1, SBS Implementers Forum.

#### **30.2. SMBus Configuration**

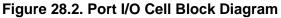

Figure 30.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 V and 5.0 V; different devices on the bus may operate at different voltage levels. The bi-directional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pullup resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

Figure 30.2. Typical SMBus Configuration

#### 30.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. It is not necessary to specify one device as the Master in a system; any device who transmits a START and a slave address becomes the master for the duration of that transfer.

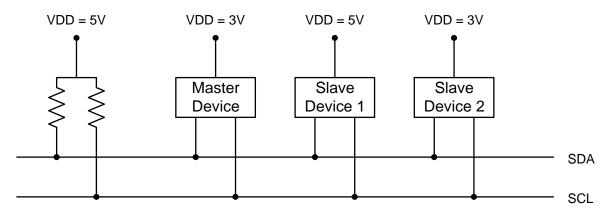

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Bytes that are received (by a master or slave) are acknowledged (ACK) with a low SDA during a high SCL (see Figure 30.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

The direction bit (R/W) occupies the least-significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 30.3 illustrates a typical SMBus transaction.

Figure 30.3. SMBus Transaction

#### 30.3.1. Transmitter Vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 30.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "30.3.5. SCL High (SMBus Free) Timeout" on page 222). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### 30.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 30.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to

## SFR Definition 30.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

#### SFR Address = 0xC0; SFR Page = All Pages; Bit-Addressable

| Bit | Name    | Description                                                                                                                                                                                               | Read                                                                                                                       | Write                                                                                                                                                                                |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                                              | 0: SMBus operating in<br>slave mode.<br>1: SMBus operating in<br>master mode.                                              | N/A                                                                                                                                                                                  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                                        | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                                          | N/A                                                                                                                                                                                  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                                         | 0: No Start or repeated<br>Start detected.<br>1: Start or repeated Start<br>detected.                                      | 0: No Start generated.<br>1: When Configured as a<br>Master, initiates a START<br>or repeated START.                                                                                 |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                                          | 0: No Stop condition<br>detected.<br>1: Stop condition detected<br>(if in Slave Mode) or pend-<br>ing (if in Master Mode). | 0: No STOP condition is<br>transmitted.<br>1: When configured as a<br>Master, causes a STOP<br>condition to be transmit-<br>ted after the next ACK<br>cycle.<br>Cleared by Hardware. |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                                             | 0: No Ack requested<br>1: ACK requested                                                                                    | N/A                                                                                                                                                                                  |

| 2   | ARBLOST | SMBus Arbitration Lost<br>Indicator.                                                                                                                                                                      | 0: No arbitration error.<br>1: Arbitration Lost                                                                            | N/A                                                                                                                                                                                  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                                        | 0: NACK received.<br>1: ACK received.                                                                                      | 0: Send NACK<br>1: Send ACK                                                                                                                                                          |

| 0   | SI      | SMBus Interrupt Flag.<br>This bit is set by hardware<br>under the conditions listed in<br>Table 15.3. SI must be cleared<br>by software. While SI is set,<br>SCL is held low and the<br>SMBus is stalled. | 0: No interrupt pending<br>1: Interrupt Pending                                                                            | <ul><li>0: Clear interrupt, and initiate next state machine event.</li><li>1: Force interrupt.</li></ul>                                                                             |

| Parameter                | Description                                           | Min                          | Max                     | Units |

|--------------------------|-------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mode              | Timing (See Figure 31.8 and Figure 31.9)              |                              |                         | I     |

| Т <sub>МСКН</sub>        | SCK High Time                                         | 1 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>MCKL</sub>        | SCK Low Time                                          | 1 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>MIS</sub>         | MISO Valid to SCK Shift Edge                          | 1 x T <sub>SYSCLK</sub> + 20 |                         | ns    |

| Т <sub>МІН</sub>         | SCK Shift Edge to MISO Change                         | 0                            |                         | ns    |

| Slave Mode               | Timing (See Figure 31.10 and Figure 31.11)            |                              |                         |       |

| T <sub>SE</sub>          | NSS Falling to First SCK Edge                         | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SD</sub>          | Last SCK Edge to NSS Rising                           | 2 x T <sub>SYSCLK</sub>      | —                       | ns    |

| T <sub>SEZ</sub>         | NSS Falling to MISO Valid                             | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>         | NSS Rising to MISO High-Z                             | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| Т <sub>СКН</sub>         | SCK High Time                                         | 5 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>CKL</sub>         | SCK Low Time                                          | 5 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SIS</sub>         | MOSI Valid to SCK Sample Edge                         | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SIH</sub>         | SCK Sample Edge to MOSI Change                        | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SOH</sub>         | SCK Shift Edge to MISO Change                         | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>         | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)      | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| Note: T <sub>SYSCL</sub> | K is equal to one period of the device system clock ( | SYSCLK).                     |                         | l     |

## Table 31.1. SPI Slave Timing Parameters

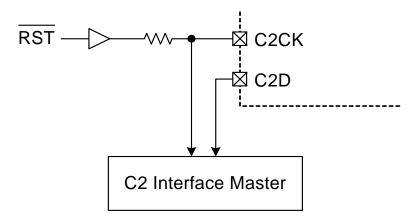

### 35.2. C2CK Pin Sharing

The C2CK pin is shared with the  $\overline{\text{RST}}$  signal on this device family. If the  $\overline{\text{RST}}$  pin is used by other parts of the system, debugging and programming the device can still be accomplished without disrupting the rest of the system. If this is desired, it is normally necessary to add a resistor to isolate the system's reset line from the C2CK signal. This external resistors would not be necessary for production boards, where debugging capabilities are not needed. A typical isolation configuration is shown in Figure 35.1.

Figure 35.1. Typical C2CK Pin Sharing

The configuration in Figure 35.1 assumes the  $\overline{RST}$  pin on the target device is used as an input only. Additional resistors may be necessary depending on the specific application.